Изобретение относится к вычислительной технике и может быть использовано для отображения информации на телевизионном индикаторе.

Цель изобретения - повышение точности и быстродействия устройства.

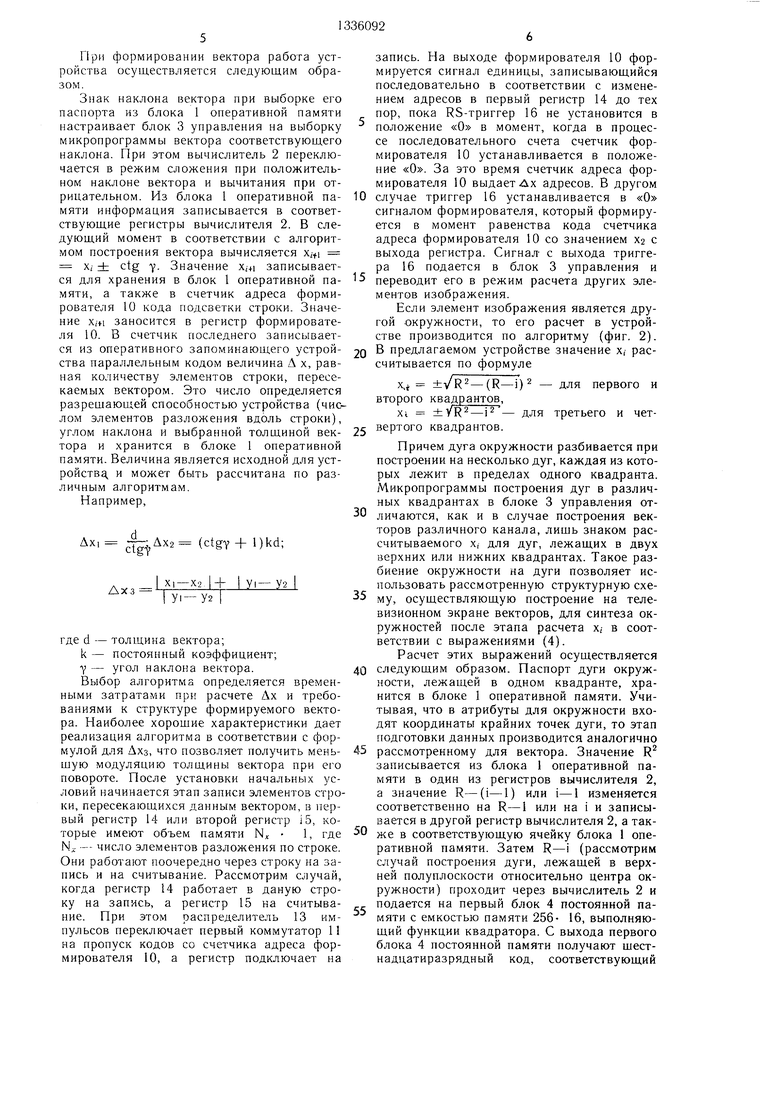

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - алгоритм работы устройства.

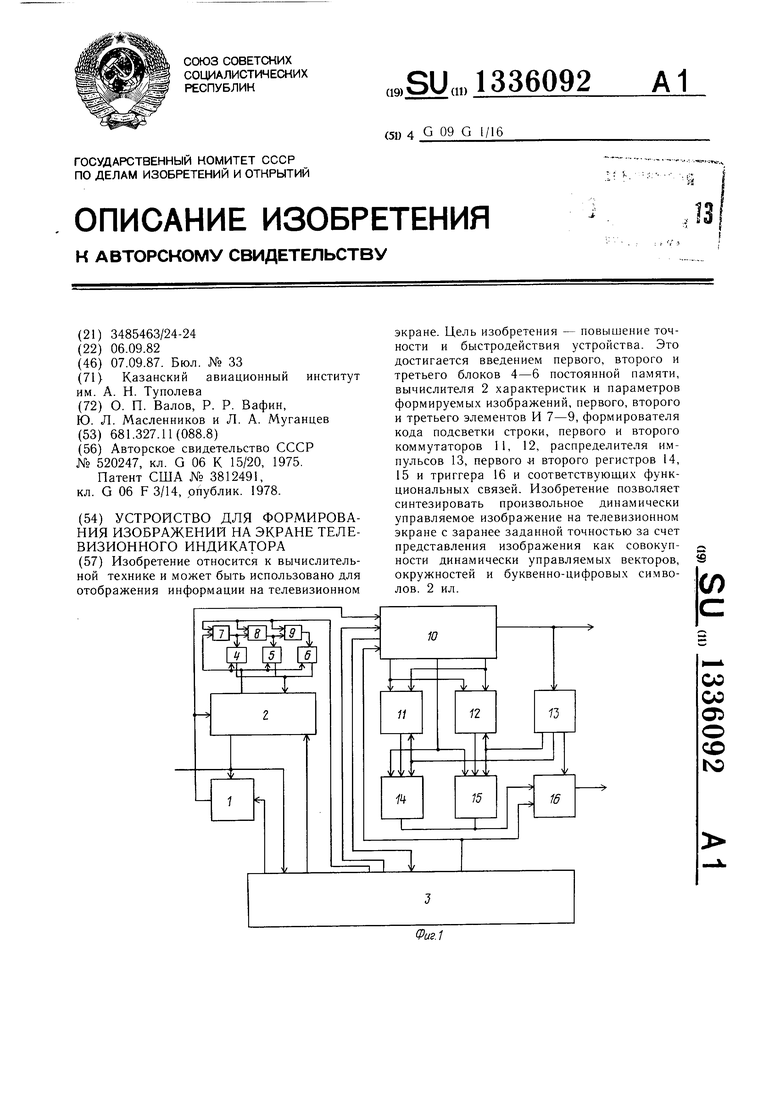

Устройство содержит блок 1 оперативной памяти, вычислитель 2 характеристик и параметров формируемых изображений, блок 3 управления, первый 4, второй 5 и третий 6 блоки постоянной памяти, первый 7, второй 8 и третий 9 элементы И, формирователь 10 кода подсветки строки, первый 11 и второй 12 коммутаторы, распределитель 13 импульсов, первый 14 и второй 15 регистры и триггер 16.

Устройство работает следующим образом.

Файл, содержащий информацию, необходимую для фор.мирования элементов изображения, может записываться в блок 1 оперативной памяти синхронно с частотой кадров растрового разложения, возможна также и асинхронная запись. Вычислитель 2 характеристик и параметров формируемых изображений служит для реализации девяти микропрограмм (фиг. 2), в том числе подготовки начальных условий (2 микропрограммы), расчета точек синтезируемых векторов (2 микропрограммы), дуг окружностей (4 микропрограммы), микропрограмма обеспечения работы знакогенератора.

Блок 1 оперативной памяти может быть организован следующим образом. Общий объем памяти должен быть порядка двух килобайт, где каждая ячейка памяти с 10-12-разрядным адресом должна иметь длину записываемого слова в 2 байта. Ячейки с адресами, где в старших разрядах адреса, начиная с девятого, записаны нули, хранят паспорта и атрибуты синтезируемых элементов изображения. Номер, записанный в паспорте, соответствует номеру подпрограммы для расчета того или иного элемента изображения (вектора, дуги окружности, строки буквенно-цифровых символов). Атри- буты включают в себя информацию о цвете воспроизводимого элемента изображения, признак наличия или отсутствия мигания символа, знак наклона воспроизводимого элемента, который определяет конкретный номер микропрограммы: одной из двух при формировании векторов различного наклона и одной из четырех при формировании дуги окружности. В ячейках с адресами, где в старших разрядах, начиная с девятого, записаны коды, отличные от «О, хранится объектный модуль с адресом, соответствующим паспорту элемента изображения. Здесь хранятся значения координат начала и конца векторов и промежуточная информация.

0

5

0

5

0 г

0

5

0

5

необходимая для расчета координат точек элементов изображения. Устройство предназначено для создания изображения на растре с разрещающей способностью 256 X X 256, 512 X 512, 1024 X 1024 элементов разложения, но точность для такого рода индикаторов достаточна при задании координат элементов изображения восьмиразрядными двоичными числами. При этом две координаты, например для вектора по оси ординат, могут быть записаны в одну ячейку блока 1 оперативной памяти.

Началу работы по расчету точек элементов изображения в строке предшествует этап подготовки данных, циклически повторяющийся каждые восемь строк. Этот этап заключается в следующем (микропрограмма подготовки данных, фиг. 2). Учитывая, что число паспортов формируемых элементов изображения может быть достаточно большим (от 128 до 1024), необходимо исключить перебор в каждой строке всех паспортов, требующий больших затрат времени. При этом необходимо учесть, что число паспортов с элементами изображений, ординаты которых удовлетворяют условию YI- Утек. Уг (где Yj- Yt - ординаты крайних точек элемента изображения, утек - текущее значение ординаты на экране индикатора), как правило, не превышает более 10-30°/о от всех выводимых на экран. Большие затраты времени при переборе всех паспортов обусловлены большим временем выборки ординат элементов изображения из блока 1 оперативной памяти, так как объем памяти должен быть достаточно большим, что не позволяет использовать память с малым временем выборки.

С целью согласования быстродействия блока 1 оперативной памяти и вычислителя 2 в устройстве применен следующий алгоритм подготовки данных. С помош.ью блока 3 управления производится опрос ячеек в блоке 1 оперативной памяти, где записаны координаты У,„ , 2п, и по шестнадцатиразрядной щине данных с блока 3 управления они записываются в один из регистров вычислителя 2, а адрес исследуемой ячейки памяти, соответствующий номеру выбранного элемента изображения, записывается в младшие разряды другого регистра вычислителя, представляющего собой шестнадцатиразрядный сдвиговый регистр с параллельной записью информации. В следующий момент времени вычислитель 2 производит сравнение в соответствии с двойным неравенством Y,Ti-Y.re YZ , так как цикл повторяется каждые восемь строк, то при постоянных Y,4 , Yin происходит восьмикратное сравнение этих ординат с Утек, последовательно изменяющимся от ent (YTeK/g) до ent (YTeK/8) + 8.

По окончании 8-кратного цикла сравнения в регистре сдвига вычислителя 2 в

восьми младших разрядах записан позиционный код, соответствующий наличию в случае одного из неравенств или отсутствию составляющих формируемого элемента изображения в данной строке. Номер этого элемента изображения после восьмикратного сдвига записан в старших восьми разрядах регистра сдвига вычислителя 2. В случае, когда число паспортов в блоке 1 оперативной памяти равно 512, то такой анализ при организации блока 1 оперативной памяти в два байта на каждую ячейку необходимо проводить для семи строк, а в случае 1024 паспортов - для щести строк, так как суммарное число бит запоминающего кода и адреса элемента изображения не может превышать 16-разрядность ячеек блока 1 оперативной памяти. Затем информация, записанная в регистре сдвига вычислителя 2, переписывается в специально отведенную область блока 1 оперативной памяти и данная процедура последовательно повторяется для всех элементов изображения.

В случае, если в позиционном коде, записанном в регистре сдвига вычислителя 2, для воспроизводимого элемента изображения записались все нули, т. е. элемент изображения не пересекается данными строками, перезапись информации с регистра сдвига вычислителя 2 в блок 1 памяти не производится. После проведения рассмотренной процедуры в отведенной области блока 1 оперативной памяти информация записывается в О-40 ячейках. Учитывая, что процедуры сравнения и записи в регистре сдвига вычислителя 2 занимают небольшое время, то процесс восьмикратного сравнения и записи его результата может составлять время, равное времени выборки из блока 1 оперативной памяти, тем самым время, затрачиваемое на подготовку данных, уменьшается в несколько раз и может составлять время меньше длительности двух строк. Б течение времени, приходяш.егося на остальные семь строк, этап подготовки данных не повторяется. При небольшом объеме исходных данных (число синтезируемых элементов изображения) можно отказаться от этапа подготовки данных и производить в каждой строке последовательный перебор ординат для всех синтезируемых элементов изображения, то такой алгоритм требует больщих временных затрат.

В известном устройстве рассматривается алгоритм с еще большими требованиями к устройству по быстродействию, так как при его реализации необходима последовательная перестановка паспортов элементов изображения, например для векторов, в соответствии с углами их наклона. Для окружностей алгоритм подготовки данных в ообще не производится, хотя он, в принципе, должен отличаться от случая формирования вектора. В предлагаемом устройстве такие отли10

чия отсутствуют. После этапа подготовки данных происходит последовательпый расчет элементов изображений в восьми строках, для которых эти данные проана. щзироващя. г Расчет элементов изображения вычислителем 2 производится в соответствии с блок- схемой алгоритма (фиг. 2). Д.чя этого с по.мощью блока 3 управления из соответствующих ячеек блока 1 оперативной памяти последовательно выбирается содержимое ячеек памяти, записанных на этапе подготовки данных, т. е. из соответствуюп1.ей ячейки выбирается шестнадцатиразрядный код, где в восьми разрядах записан номер символа, определяющий адрес нахождения пас- J5 порта этого символа, а также восемь разрядов позиционного кода, записанные в эти ячейки памяти единицы определяют наличие элементов данного символа в соответствующей строке. Эти восемь разрядов, предварительно записанные в один из регистров 0 вычислителя 2, по команде с блока 3 управления проверяются на совпадение с кодом, поступающим с блока 3 управления, в котором единственное значение единицы находится в позиции, соответствующей номеру

5 одной из восьми строк. При совпадении единиц в данном разряде, что соответствует наличию элементов данного символа в рассматриваемой строке, вычислитель 2 вырабатывает сигнал, который передается в блок 3 упраВоЧения, вырабатывающий коман ду выборки паспорта символа из блока 1 оперативной памяти с адресом, равным номеру элемента изображения, записанному в старших разрядах соответствующего регистра вычислителя 2. Если этот паспорт соответствует вектору, то дальнейпшя работа устройства идет в соответствии с блок- схемой алгоритма вычисления вектора (фиг. 2). Данный алгоритм реализуется в известном устройстве, управление отдельных узлов схемы, для последовательного

0 выполнения алгоритма обеспечивается управляющими сигналами с блока 3 управления, в соответствии с которыми вычислитель 2 производит однократное суммирование при формировании координаты x,i вектора для i + l строки растра по известной

координате х,- для i-й строки. При этом используется реккурентное соотнои ение

Хж X,- -f ctg

где у - угол наклона вектора с осью X. 0Координаты рассчитываются по выражению (1) вычислителем 2 только для тех векторов, для которых выполняются условия

х, хоС2)

илиу; yi;у,., у2 .,(3)

где Х Х2, У| У2 - координаты вектора. Как указывалось, проверка условия (3) производится на этапе подготовки данных. Проверка условия (2) осуществляется в формирователе 10 кода подсветки строки.

5

запись. На выходе формирователя 10 формируется сигнал единицы, записывающийся последовательно в соответствии с изменением адресов в первый регистр 14 до тех пор, пока RS-триггер 16 не установится в положение «О в момент, когда в процессе последовательного счета счетчик формирователя 10 устанавливается в положение «О. За это время счетчик адреса формирователя 10 выдает Дх адресов. В другом

При формировании вектора работа устройства осуществляется следующим образом.

Знак наклона вектора при выборке его паспорта из блока 1 оперативной памяти настраивает блок 3 управления на выборку микропрограммы вектора соответствующего наклона. При этом вычислитель 2 переключается в режим сложения при положительном наклоне вектора и вычитания при отрицательном. Из блока 1 оперативной па- 10 случае триггер 16 устанавливается в мяти информация записывается в соответ- сигналом формирователя, который формируется в момент равенства кода счетчика адреса формирователя 10 со значением Х2 с выхода регистра. Сигнал- с выхода триггера 16 подается в блок 3 управления и переводит его в режим расчета других элементов изображения.

Если элемент изображения является другой окружности, то его расчет в устройстве производится по алгоритму (фиг. 2). ся из оперативного запоминающего устрой- 20 предлагаемом устройстве значение х,- рас- ства параллельным кодом величина А х, рав-считывается по формуле

ная количеству элементов строки, пересекаемых вектором. Это число определяется разрешающей способностью устройства (числом элементов разложения вдоль строки).

ствующие регистры вычислителя 2. В следующий момент в соответствии с алгоритмом построения вектора вычисляется X; ± ctg 7- Значение х,ч1 записывается для хранения в блок 1 оперативной па- 5 мяти, а также в счетчик адреса формирователя 10 кода подсветки строки. Значение х,ч1 заносится в регистр формирователя 10. В счетчик последнего записываетпервого и

X,i ±УН2-(R -i) 2 - ДЛЯ

второго квадрантов,

Xi ±VR2-i - для третьего и чет- углом наклона и выбранной толщиной век- 25 вертого квадрантов, тора и хранится в блоке 1 оперативнойПричем дуга окружности разбивается при

памяти. Величина является исходной для устройства, и может быть рассчитана по разпостроении на несколько дуг, каждая из которых лежит в пределах одного квадранта. Микропрограммы построения дуг в различных квадрантах в блоке 3 управления отличаются, как и в случае построения векторов различного канала, лишь знаком рассчитываемого X, для дуг, лежащих в двух верхних или нижних квадрантах. Такое разбиение окружности на дуги позволяет использовать рассмотренную структурную схему, осуществляющую построение на телевизионном экране векторов, для синтеза окружностей после этапа расчета х,- в соответствии с выражениями (4).

личным алгоритмам. Например,

Axi ;,Дх2 (ctgY + l)kd;

& f

Лхз

I Xl-Х2 1+ I У|- У2 I У|- У2 I

построении на несколько дуг, каждая из которых лежит в пределах одного квадранта. Микропрограммы построения дуг в различных квадрантах в блоке 3 управления отличаются, как и в случае построения векторов различного канала, лишь знаком рассчитываемого X, для дуг, лежащих в двух верхних или нижних квадрантах. Такое разбиение окружности на дуги позволяет использовать рассмотренную структурную схему, осуществляющую построение на телевизионном экране векторов, для синтеза окружностей после этапа расчета х,- в соответствии с выражениями (4).

Расчет этих выражений осуществляется 40 следующим образом. Паспорт дуги окружности, лежащей в одном квадранте, хранится в блоке 1 оперативной памяти. Учитывая, что в атрибуты для окружности входят координаты крайних точек дуги, то этап подготовки данных производится аналогично

где d - толщина вектора;

k - постоянный коэффициент; у - угол наклона вектора. Выбор алгоритма определяется временными затратами при расчете Ах и требованиями к структуре формируемого вектора. Наиболее хорощие характеристики дает реализация алгоритма в соответствии с формулой для Ахз, что позволяет получить мень- 45 рассмотренному для вектора. Значение R щую модуляцию толщины вектора при егозаписывается из блока 1 оперативной паповороте. После установки начальных ус-мяти в один из регистров вычислителя 2,

ловий начинается этап записи элементов стро- а значение R-(i-1) или i-1 изменяется ки, пересекающихся данным вектором, в пер-соответственно на R-1 или на i и записывый регистр 14 или второй регистр i5, ко-вается в другой регистр вычислителя 2, а такторые имеют объем памяти N 1, где 0 же в соответствующую ячейку блока 1 опе- Ni- - число элементов разложения по строке.ративной памяти. Затем R-i (рассмотрим

случай построения дуги, лежащей в верхней полуплоскости относительно центра окружности) проходит через вычислитель 2 и подается на первый блок 4 постоянной памяти с емкостью памяти 256- 16, выполняющий функции квадратора. С выхода первого блока 4 постоянной памяти получают щестОни работают поочередно через строку на запись и на считывание. Рассмотрим случай, когда регистр 14 работает в даную строку на запись, а регистр 15 на считывание. При этом распределитель 13 импульсов переключает первый коммутатор 1 на пропуск кодов со счетчика адреса формирователя 10, а регистр подключает на

55

надцатиразрядныи код, соответствующий

запись. На выходе формирователя 10 формируется сигнал единицы, записывающийся последовательно в соответствии с изменением адресов в первый регистр 14 до тех пор, пока RS-триггер 16 не установится в положение «О в момент, когда в процессе последовательного счета счетчик формирователя 10 устанавливается в положение «О. За это время счетчик адреса формирователя 10 выдает Дх адресов. В другом

случае триггер 16 устанавливается в сигналом формирователя, который формируется в момент равенства кода счетчика адреса формирователя 10 со значением Х2 с выхода регистра. Сигнал- с выхода триггера 16 подается в блок 3 управления и переводит его в режим расчета других элементов изображения.

первого и

0

построении на несколько дуг, каждая из которых лежит в пределах одного квадранта. Микропрограммы построения дуг в различных квадрантах в блоке 3 управления отличаются, как и в случае построения векторов различного канала, лишь знаком рассчитываемого X, для дуг, лежащих в двух верхних или нижних квадрантах. Такое разбиение окружности на дуги позволяет использовать рассмотренную структурную схему, осуществляющую построение на телевизионном экране векторов, для синтеза окружностей после этапа расчета х,- в соответствии с выражениями (4).

Расчет этих выражений осуществляется 0 следующим образом. Паспорт дуги окружности, лежащей в одном квадранте, хранится в блоке 1 оперативной памяти. Учитывая, что в атрибуты для окружности входят координаты крайних точек дуги, то этап подготовки данных производится аналогично

5

5 рассмотренному для вектора. Значение R записывается из блока 1 оперативной панадцатиразрядныи код, соответствующий

(R-1), который записывается в регистр вычислителя 2. Затем последний производит расчет подкоренного выражения в соответствии с формулами (4). Затем производится вычисление подкоренного выражения. Задача нахождения радикала осложняется большой разрядностью исходного числа. В устройстве предлагается решение, основанное на том, что точность нахождения значения радикала конечна и ограничивается значением наиболее близкого целого числа, т.е. при условии задания значения подкоренного выражения произвольным целым числом в интервале 0,2 значения подкоренного выражения берутся также целыми значениями в интервале 0,2) в соот- ветствии с правилом

а(а + А) (а + 1)2, где а - целое число в инервале 0,2, Д 1.

Если Д 0,5, принимают а + Д а, Д 0,5-1- .

Двоичное число а 0,2 можно записать

fQ

a xo2° + x,...-X72 где Xi(l, значение а, возведя в квадрат можно представить

а2 2°хоI II III

+ 1 хо О . +2 ОХо XI О

.-|-2(Хо -Xl+Xi)XiХ21+Х

.+2(ХоХ2)Х2ХзХ|

.+.2(:ХоХз + XiX2 + Х2) . .ХзХ4Х2

.+ 2(ХоХ4 + Х1Хз)Х4Х5Хз

.И- 2(ХоХ5-|-Х1Х4 + Х2Хз + Хз)Х5ХбХ4

.+ 2(ХоХб-|-Х1Х54-Х2Х4) . . ХбХуXs

.+ 2®(ХоХ7-(-Х|Хб + Х2Х5 +

+ ХЗХ4 + Х4) . . . . Х7Хб

. + 2(...XlX7- -ХзХб+Х4Х5+

-j-Xs)Х7

. +2 °(....Х2Х7 + ХзХб + Х4Х5 + Х5)

. +2(ХзХ7 + Х4Хб)

. +2 (Х4Х7 + Х5Хб + Хб)

- +2 3(Х5Х7)

. +2 (Х6Х7 + Х7)

. .

Число (а + 1) отличается от а на 2а+1, что в соответствии с нашим представлением числа в двоичной форме изменяет коэффициенты перед степенями, как показано в первой колонке, число (a+Д), где Д 0,5, отличается от а на а -f 0,25, так как дробной величиной можно пренебречь, учитывая, что работают с целыми числами, это изменяет коэффициенты перед степенями, как показано во второй колонке. Млад- ший разряд в двоичном представлении для равен соответствующему коэффициенту при а, а второй разряд гюлучается всегда нулевым. Увеличение а на единицу приводит к инвертированию значения хо. Следовательно, сложение с а некоторого Д мо- жет привести к ситуациям, когда в младшем разряде Хо или хо. В случае инверсии Хо это соответствует увеличению а на

единицу, а при неизменном хо это может означать, что либо Д ; 0,5 и необходимо принять решение а+д а, либо ,5 и а +А -- а + 2.

Для кода (а -f 2) изменение значений для коэффициентов происходит в соответствии с третьей колонкой. Задача минимизации объема блока полупостоянной памяти преобразующего а заключается в выборе наименьшего числа старших разрядов а, позволяющих разделить все возможные значения для а. На основе рассмотренного можно показать, что при выборе границы раздела на восьмом разряде это разделение оказывается возможным для всех чисел от 16 до 256. Эта возможность заключается в том, что перенос в восьмом разряде, который может возникнуть при сложении с а числа а (вторая колонка), может привести к меньшему или равному коду в разрядах от восьмого до пятнадцатого с кодом для а -f 2а и не может быть равным для а2 + 4а + 4 (третья колонка). Это объясняется тем, что в числе а коэффициенты при разрядах от двух до восьми не могут быть равными все единице, что приводит к «затуханию переносов. Быстрое преобразование осуществляется элементами И 7-9 и блоками 5 и 6 постоянной памяти. При этом разрядность блока 5 постоянной памяти может выбираться не менее 256 X 3, а блока 6 постоянной памяти - 256 X 8. Учитывая, что младшие разряды чисел a и а равны, их можно не хранить в блоке постоянной памяти, а сразу же подавать на выход, а также использовать в качестве адресного разряда для блока 6 постоянной памяти, так как его семиразрядный входной код соответствует двум значениям а и а + 1, а коэффициент при младшем разряде Xfl дает конкретное значение а. На практике удобно использовать оба кристалла постоянной памяти одинаковой разрядности. В этом случае четыре старших разряда входного шестнадцатиразрядного двоичного кода соответствующего подкоренному выражению, подается на инвертирующие входы первого элемента И 7, если во всех разрядах записаны «О, то на выходе второго элемента И 8 формируется сигнал единицы, разрешающий считывание информации в момент прихода сигнала считывания на первые входы элементов И 7-9 и запрещающий считывание с третьего блока 6 постоянной памяти. В противном случае, когда в старщих четырех разрядах где-либо записана единица, считывание ведется с третьего блока 6 постоянной памяти. В качестве адреса на вход второго блока 5 постоянной памяти подаются следующие разряды кода числа подкоренного выражения А-Хв, X.,, Xs, Хе, Ху. х, Хз, Xjo, х, а для третьего блока 6 постоянной памяти х,, х,,

Xj, Xje, Xjj , Xi4, Xi, Хи, X.

Данный подход нахождения с ограниченной точностью значений аргумента может быть применен и для других монотонных функций. Значение радикала, полученного с выходов второго или третьего блоков постоянной памяти, записывается в один из регистров вычислителя 2, а в другой регистр записывается из блока 1 оперативной памяти значение координаты х,, окружности, затем вычислитель 2 определяет значение .f Ху ± Xt, которое затем записывается в соответствующий регистр вычислителя. После этого вычисляется значение дхг, которое, как и в случае для вектора, может вычисляться несколькими способами. Например, просто рассчитывается дхс xi-Xi-j или в случае построения дуги с переменной толщиной контура считается значение х V (К-d) --l(R-d) -i), где d определяет л х по формуле дх хс - Xt. Такой алгоритм увеличивает время расчета элементов изображения, включающих дуги окружностей, но при этом значительно улучшается качество формируемого изображения. Работа формирователя 10 кода подсветки строки для случая формирования дуги окружности не отличается от ранее рассмотренной для формирования вектора. В счетчик формирователя заносится значение &х. В регистр формирователя заносится значение х, определяющее координату по оси X нижней точки дуги. В счетчик адреса формирователя заносится значение X, ± х; и затем уже по рассмотренному алгоритму для вектора происходит запись в первый регистр 14 или второй регистр 15. В том случае, когда после подготовки данных при опросе блока 1 оперативной памяти встречается паспорт на построение строки, пересекающей знаки (буквы, цифры, мнемосимволы), их формирование обеспечивается при воздействии управляющих команд с блока 3 управления знакогенератором формирователя, который с приходом из блока 1 памяти кодов знаков и номера строки развертки для знака или группы знаков, записанных в строку, последовательно производит выдачу позиционного код.а знака. Номер строки развертки (координата Yi) предварительно из блока 1 оперативной памяти записывается в регистр формирователя. В это время формирователь пропускает сигнал с выхода знакогенератора. При построении вектора и окружностей формирователь пропускает сигнал с выхода триггера 16. Счетчик адреса формирователя служит для последовательного задания адресов первого регистра 14 или второго регистра 15, который работает в этот момент на считывание синхронно с ходом развертки телевизионного индикатора.

Триггер 16 служит для хранения информации с первого регистра 14 или второго регистра 15, так как после считывания ин0

5

0

5

0

5

0

5

0

5

формации в триггер 16 каждая из ячеек этих регистров под действием сигнала с распределителя 13 импульсов обнуляется, чем осуществляется подготовка ее к записи в следующей строке. Импульс, управляющий временем записи информации, в триггер 16 поступает с формирователя 10. Распределитель 13 импульсов служит для распределения этих импульсов под действием сигнала с блока управления на регистры 14 и 15 в качестве стирающих и для триггера в качестве записывающих.

Формула изобретения

Устройство для формирования изображений на экране телевизионного индикатора, содержащее блок управления, первый выход которого подключен к входу записи- чтения блока оперативной памяти, информационный вход которого является информационным входом устройства и соединен с информационным входом блока управления и первым выходом вычислителя характеристик и параметров формируемых изображений, первый информационный вход которого подключен к выходу блока оперативной памяти, а управляющий вход - к второму выходу блока управления, отличающееся тем, что, с целью повышения точности и быстродействия устройства, оно содержит первый, второй и третий блоки постоянной памяти, выходы и адресные входы которых подключены соответственно к второму информационному входу и второму выходу вычислителя характеристик и параметров формируемых изображений, первый, второй и третий элементы И, первые входы которых соединены с третьим выходом блока управления, выходы - с входами чтения первого, второго и третьего блоков постоянной памяти соответственно, а вторые входы - с вторым выходом вычислителя характеристик и параметров формируемых изображений, выходом первого и выходом второго элементов И соответственно, формирователь кода подсветки строки, информационный вход которого подключен к выходу блока оперативной памяти, а первый управляющий вход - к четвертому выходу блока управления, первый и второй коммутаторы, информационные входы которых соединены с первым и вторым информационными выходами формирователя кода подсветки строки, син- хровход которого подключен к пятому выходу блока управления, распределитель импульсов, вход которого соединен с третьим информационным выходом формирователя кода подсветки строки и является информационным выходом устройства, первый и второй регистры, информационные входы которых подключены к выходам первого и второго коммутаторов соответственно, синхро- входы - к первому и второму выходам распределителя импульсов соответственно, а управляющие входы - к первому управляющему выходу формирователя кода подсветки строки, второй управляющий выход которого соединен с вторым информационным входом блока управления и триггер, информа- ционный вход которого подключен к выходам соответствующих разрядов первого и второго регистров, синхровход - к третьему выходу распределителя импульсов, а управляющий вход - к пятому выходу блока управления, причем выход триггера является стробирующим выходом устройства, а управляющие входы первого и второго коммутаторов соединены с первым и вторым выходами распределителя импульсов соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения графической информации на газоразрядной индикаторной панели | 1982 |

|

SU1108488A1 |

| Устройство для преобразования Хо изображения | 1990 |

|

SU1785004A1 |

| Устройство обработки изображений | 1989 |

|

SU1817108A1 |

| Устройство для отображения информации | 1987 |

|

SU1462405A1 |

| Устройство для отображения информации на экране цветного видеоконтрольного блока | 1988 |

|

SU1529280A1 |

| Устройство для формирования векторов на экране телевизионного индикатора | 1988 |

|

SU1506477A1 |

| Устройство для отображения графическойиНфОРМАции | 1978 |

|

SU805298A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ АВТОНОМНЫМ РОБОТОМ | 2008 |

|

RU2424105C2 |

| Устройство для отображения графической информации | 1988 |

|

SU1566339A1 |

| Устройство для отображения информации | 1985 |

|

SU1354183A1 |

Изобретение относится к вычислительной технике и может быть использовано для отображения информации на телевизионном экране. Цель изобретения - повышение точности и быстродействия устройства. Это достигается введением первого, второго и третьего блоков 4-6 постоянной памяти, вычислителя 2 характеристик и параметров формируемых изображений, первого, второго и третьего элементов И 7-9, формирователя кода подсветки строки, первого и второго коммутаторов 11, 12, распределителя импульсов 13, первого л второго регистров 14, 15 и триггера 16 и соответствующих функциональных связей. Изобретение позволяет синтезировать произвольное динамически управляемое изображение на телевизионном экране с заранее заданной точностью за счет представления изображения как совокупности динамически управляемых векторов, окружностей и буквенно-цифровых символов. 2 ил. (О со (jO Oi о со ND

програпна,, nadzomooKu с/анньи

Подпрограппа дуга

Запись номера cufidoaa

Ьь/зов i Вычисление i ifi

бызоВ R бы исление К

дt / /ucлe/ ue X eiip- VR -L

вй/зо8 Ху

Е ЫЧиСЛ. Хохр- .

бы зоб Хл

6ы fUC/l. dX Xn - Холр

Определение л при о три ц. лх

( Нонец

J

пересылка

npozpCMfibi построений синёолоё

( Конец3

Подпрограмма Вентор

бызоб ctgf

X

дызод 5

9f

ciyj

( )

| Устройство для установки деревянных штифтов | 1974 |

|

SU520247A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 3812491, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

Авторы

Даты

1987-09-07—Публикация

1982-09-06—Подача