Изобретение относится к вычислительной технике, предназначено для решения задач обработки изображений, задач размещения, распознавания образов, машинной графики.

Цель изобретения - увеличение скорости и точности выполнения поворотов и сжатий изображений

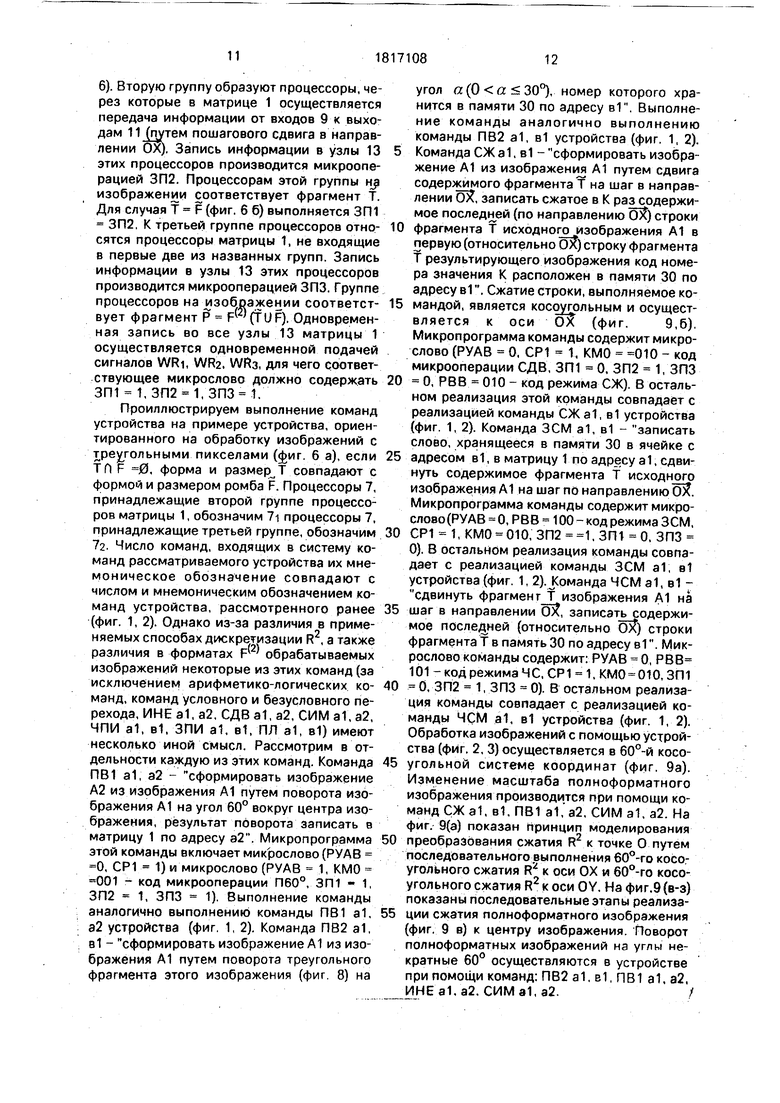

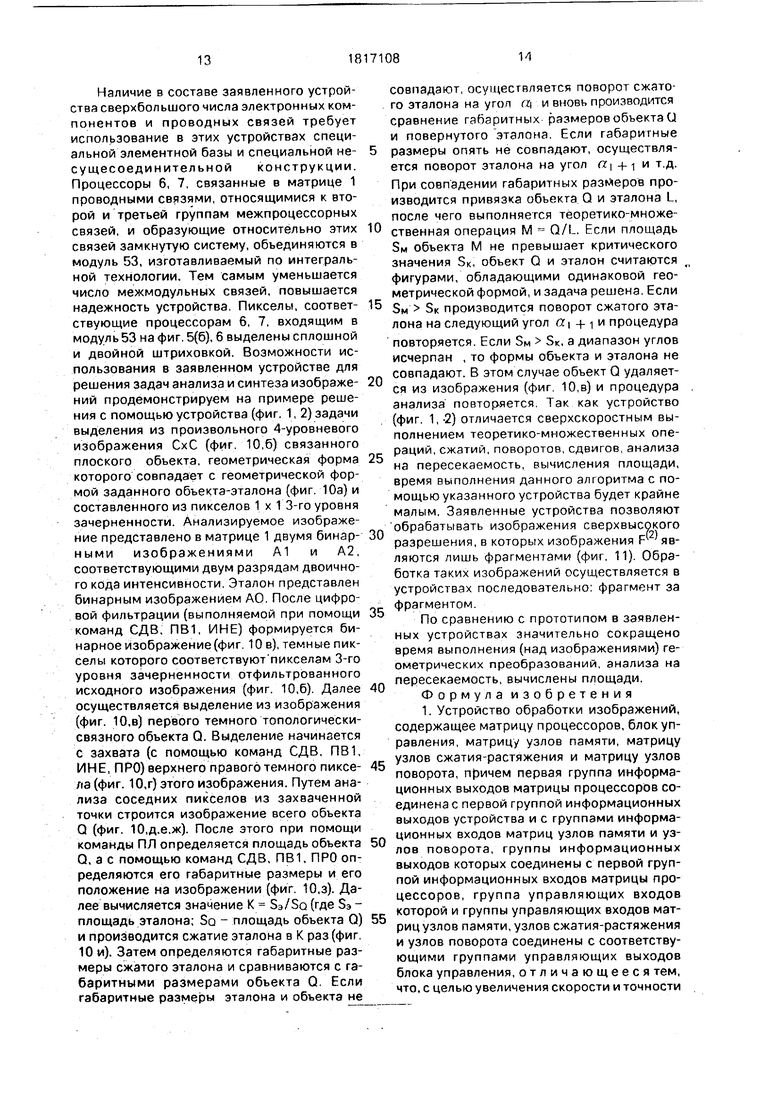

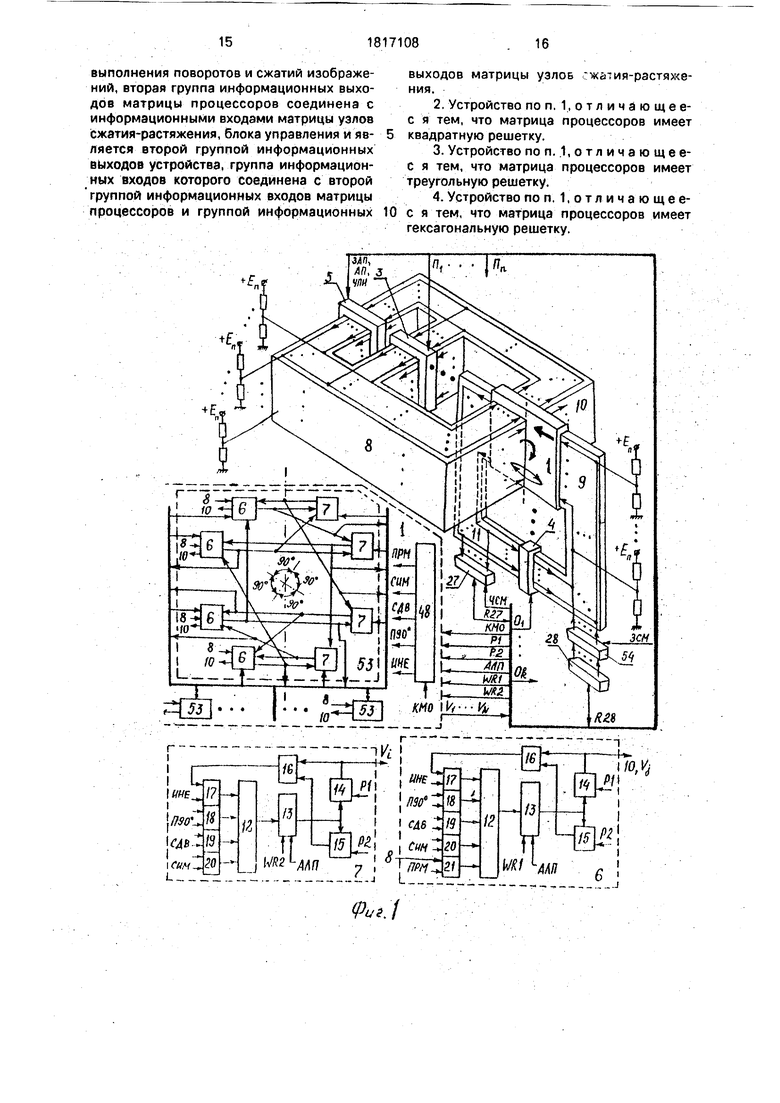

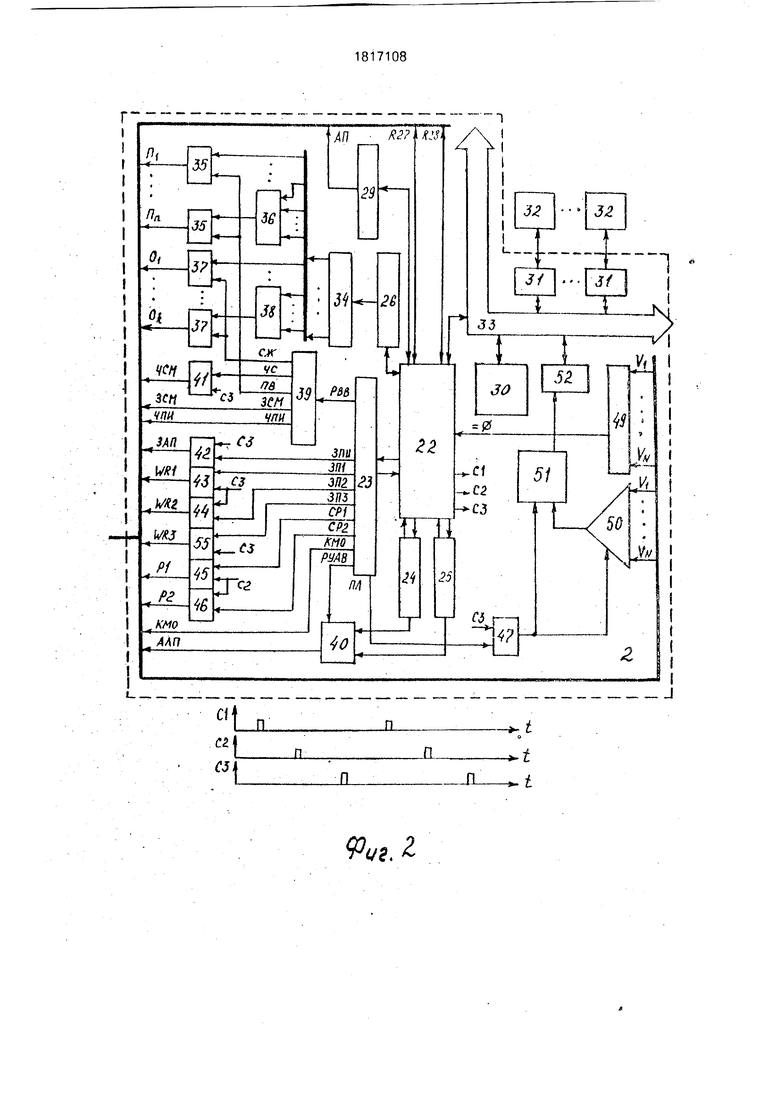

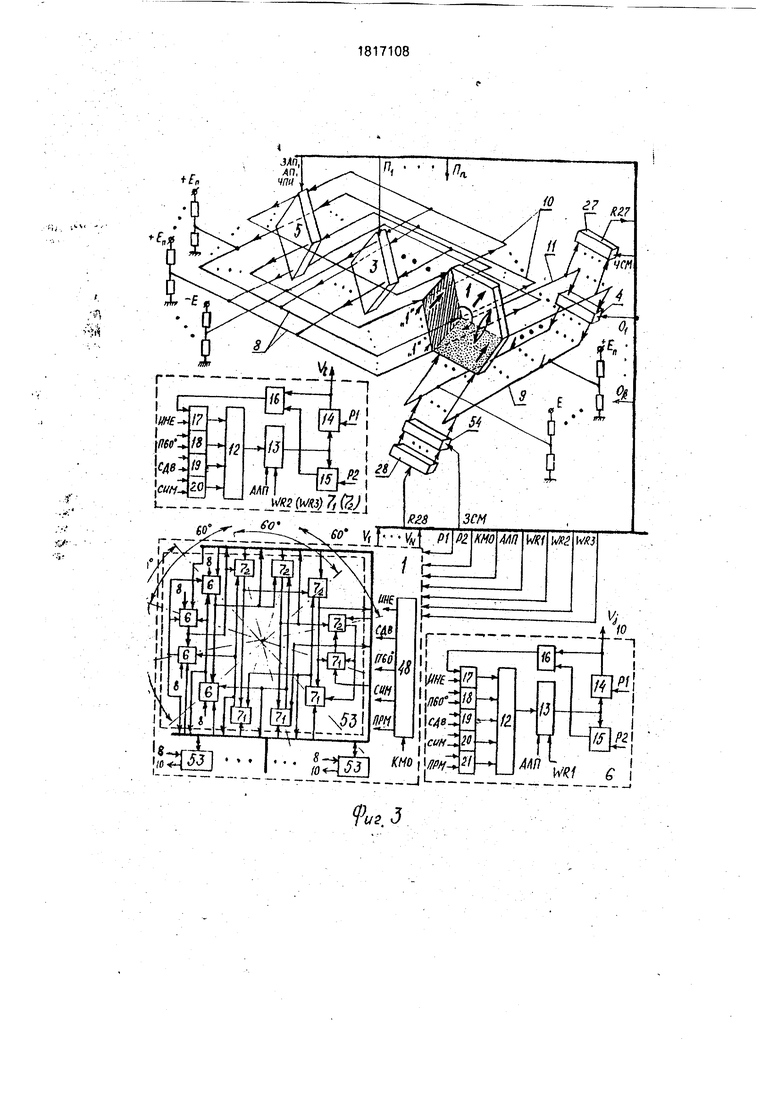

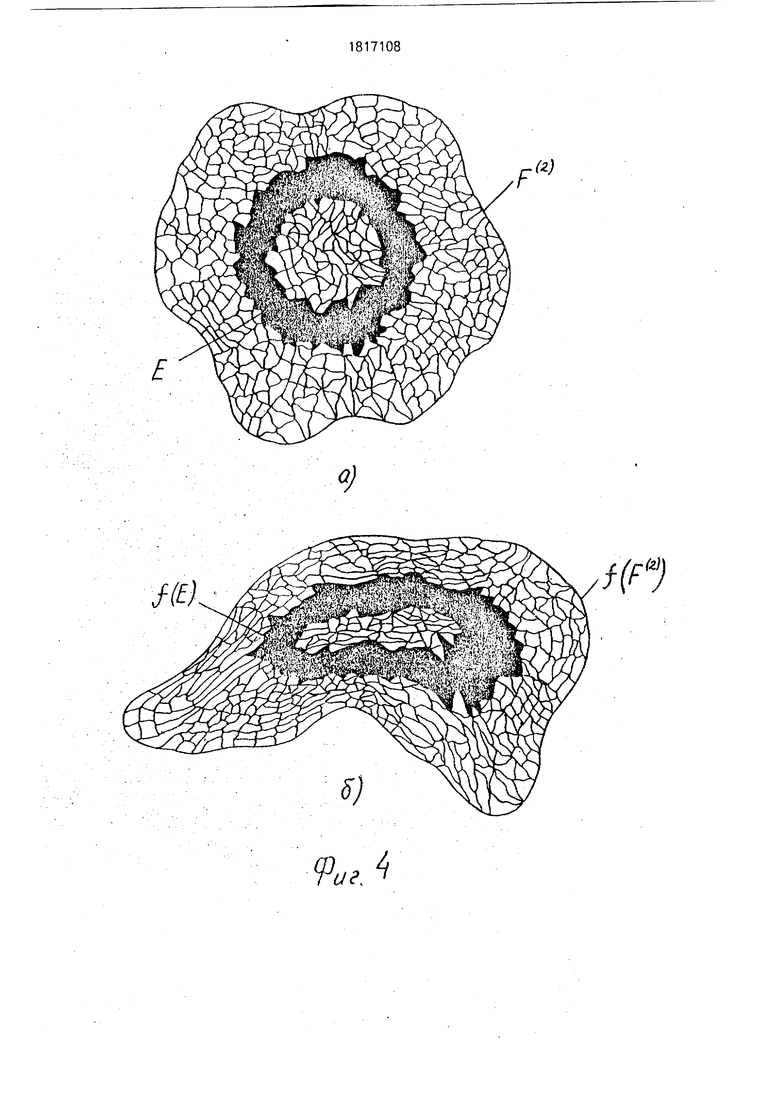

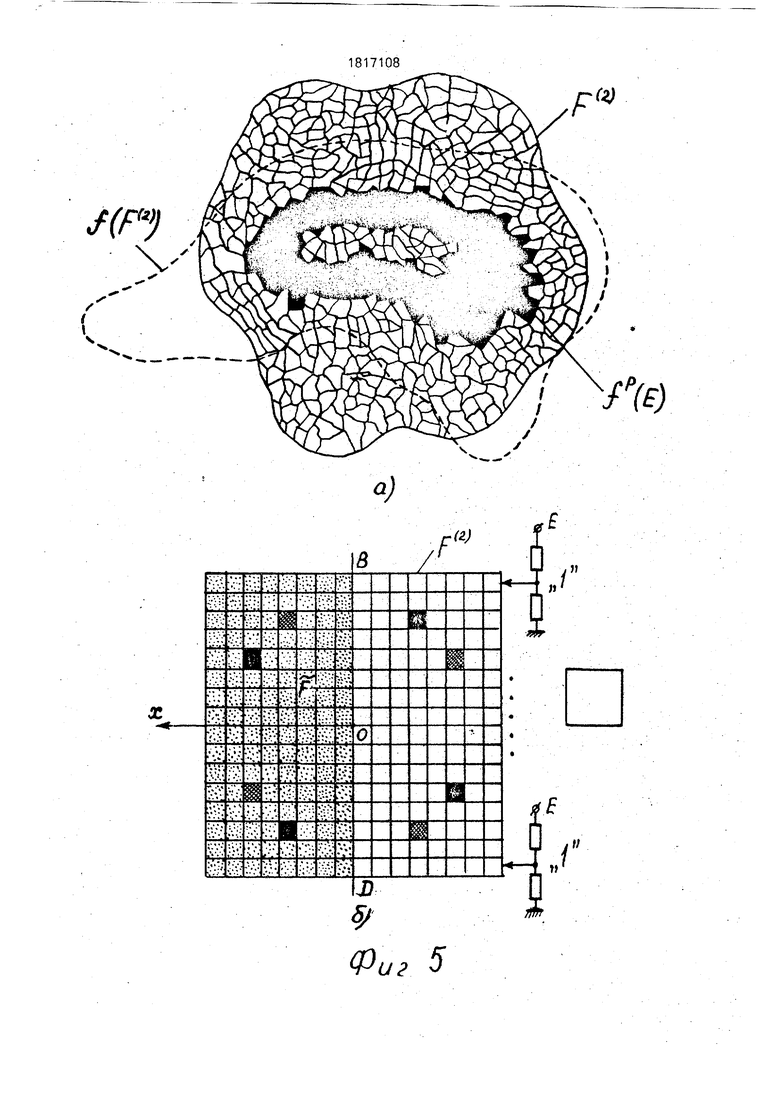

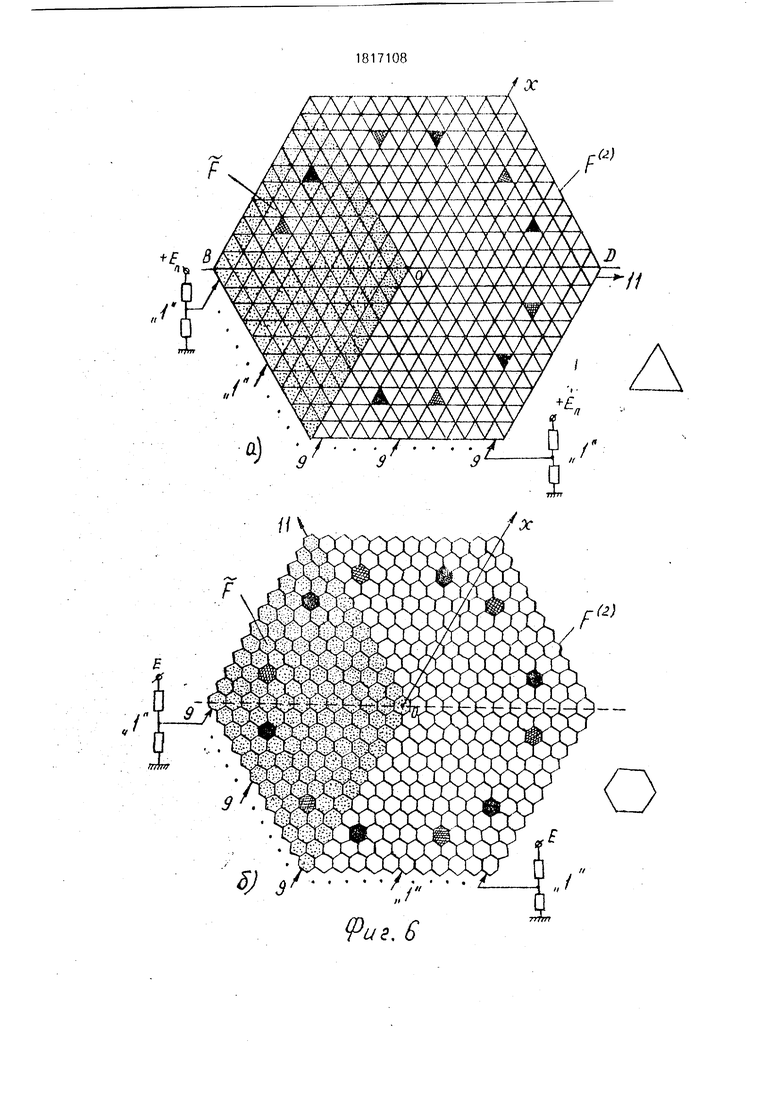

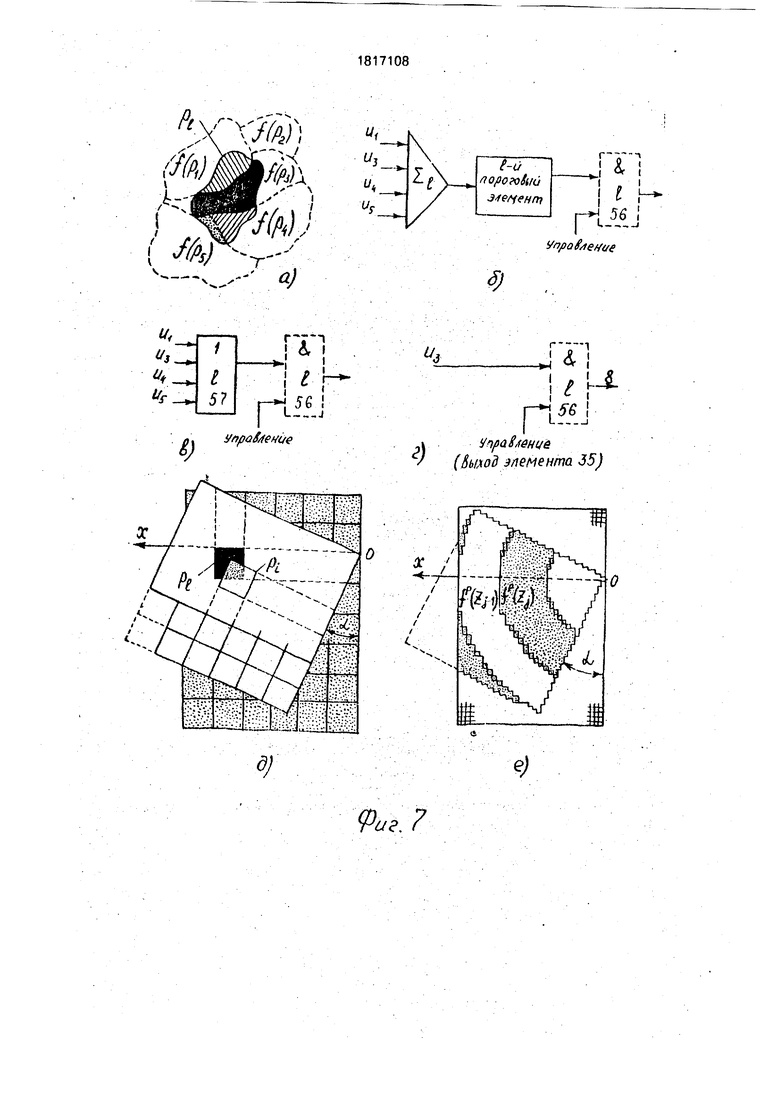

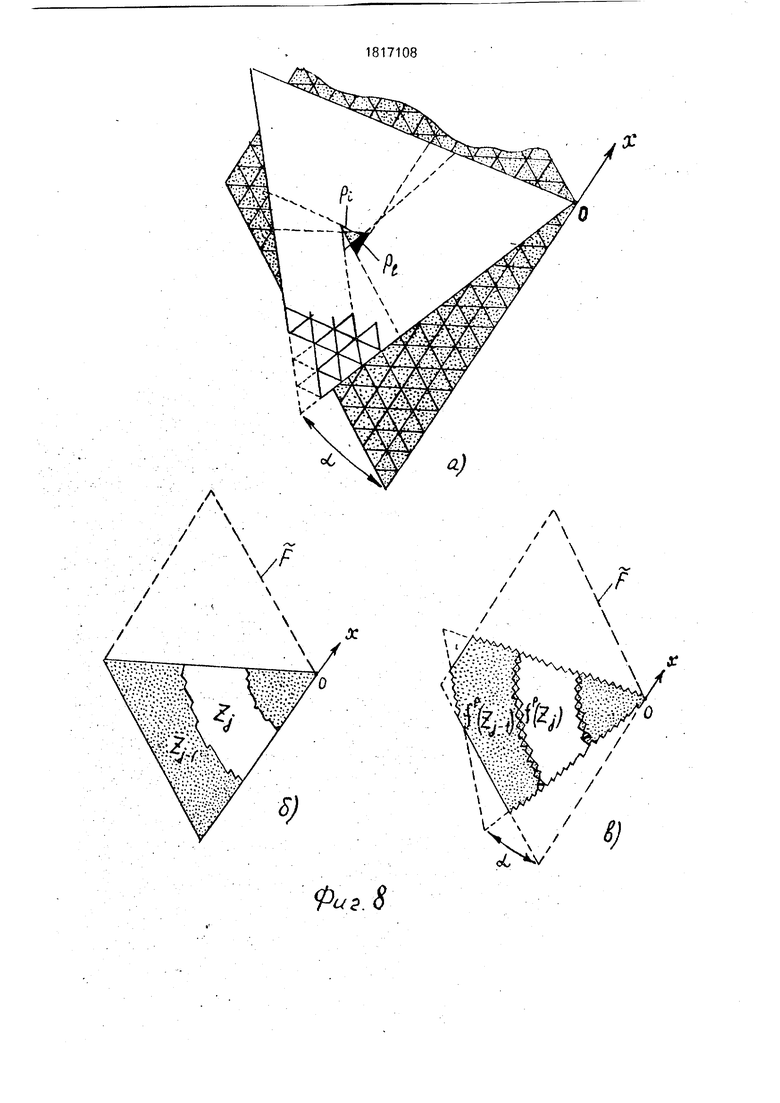

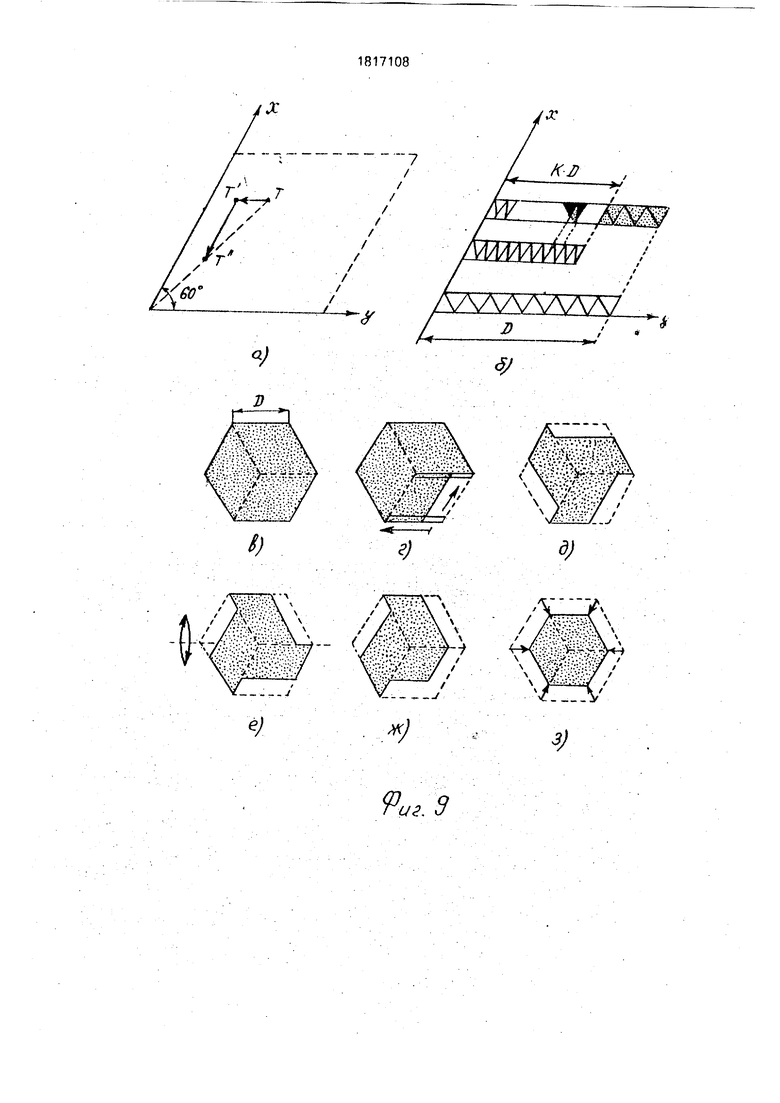

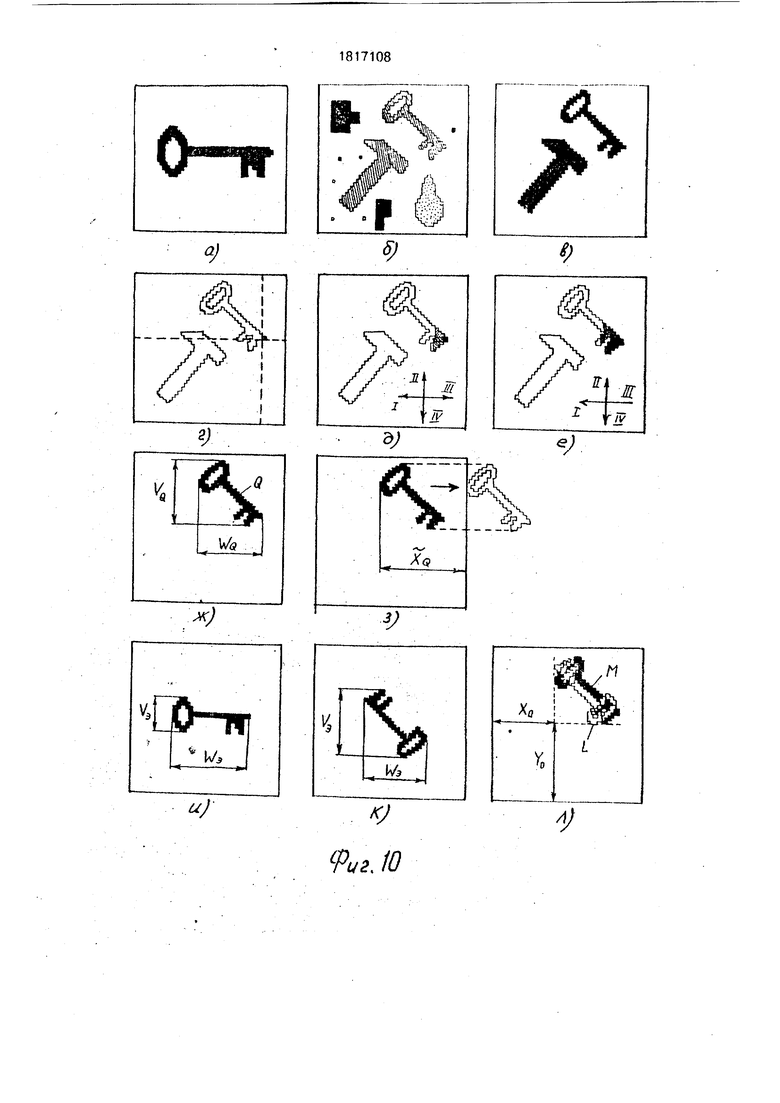

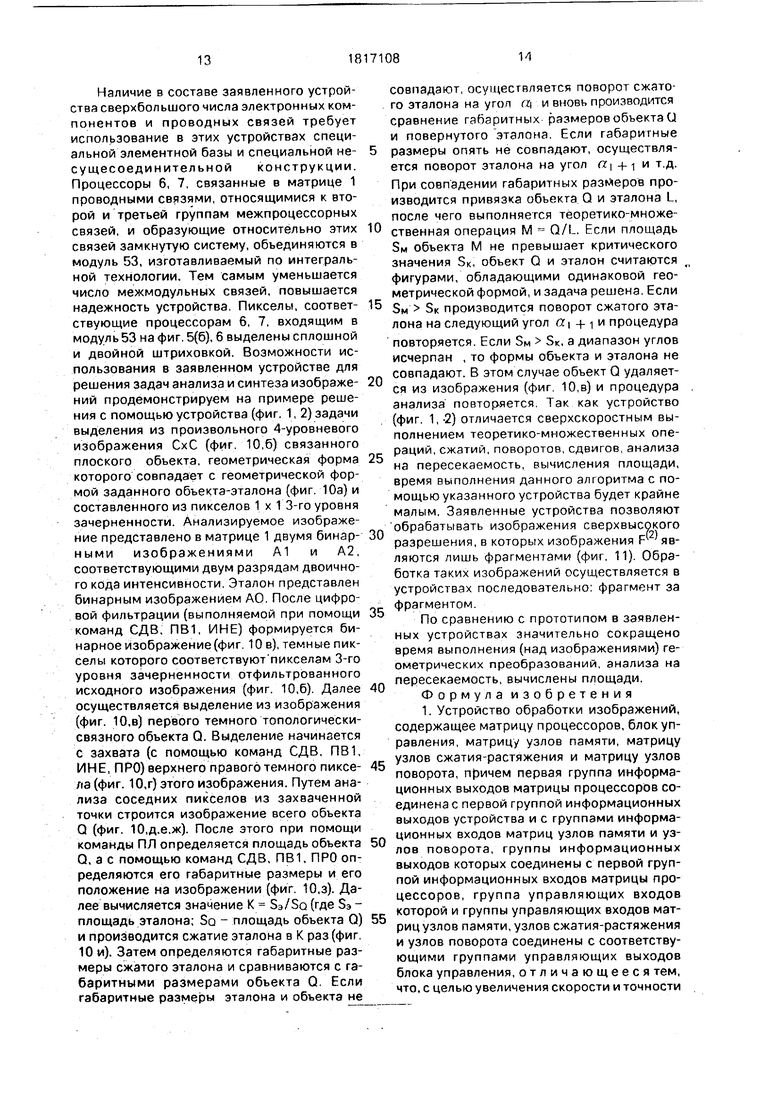

На фиг. 1 и 2 изображено устройство с квадратной процессорной матрицей. На фиг. 2 показана функциональная схема блока управления. На фиг. 2.3 изображено устройство с гексагональной процессорной матрицей. На фиг. 4-6 показаны различные способы дискретизации пространства R2, поясняется общий принцип высокоскоростного моделирования геометрических преобразований. На фиг. 7, 8 - особенности реализации высокоскоростного поворота изображений в заявленных устройствах. На фиг. 9 - особенности реализации высокоскоростного сжатия изображений в заявленном устройстве. На фиг. 10 изображен вариант решения с помощью заявленного устройства одной из задач анализа изображений. На фиг. 11 - поясняет способ использования заявленных устройств для обработки изображений сверхвысокого разрешения.

Устройство имеет матрицу 1 процессоров, блок 2 управления, узлы 3 поворота, узлы 4 сжатия-растяжения, узлы 5 памяти. Матрица 1 состоит их взаимосвязанных процессоров 6, 7. и имеет внешние входы 8, 9 и внешние выходы 10,11. Каждый процессор 6, 7 содержит многовходовый элемент ИЛИ 12, одноразрядную память 12, два одноразрядных регистра 14, 15, элемент ИЛИ-НЕ 16, двухвходовые элементы И 17- 20. Блок 2 управления включает в себя микропрограммный управляющий процессор 2 с регистром 23 микрослова и программно- адресуемыми регистрами 24 - память 30 программ и данных, контроллеры 31 внешних устройств 32. Связь между отдельными узлами блока 2 осуществляется посредством интерфейса 33. Кроме того в блок 2 входят дешифратор 34, элементы И 35 и ИЛИ 36 выбора узлов поворота, элементов И 37, ИЛИ 38 выбора узлов сжатия, дешиф00 vj

О 00

ратор 39 кода режима ввода-вывода, мультиплексор 40 адреса; элементы И 41-47. дешифратор 48 кода микрооперации, узел определения площади, состоящий из N-exo- довой схемы ИЛИ 49, N-входового аналогового сумматора 50, импульсного вольтметра 51 с контроллером 52, Процессоры б, 7, отображающиеся друг в друга при поворотах матрицы 1 вокруг ее центра на углы кратные у0, а также при преобразовании осевой симметрии относительно прямой, проходящей через центр решетки матрицы, функционально объединены в модуль 53, Регистр 28 связан с входами 9 посредством блока 54 двухвходовых элементов И. Блок 2 устройства (фиг. 2, 3) может дополнительно содержать элемент И 55. Узлы 3 состоят из двухвходовых элементов И 56 (негативная логика), узлы 4 - из элементов 56 и многовхо- довых элементов ИЛИ 57 (негативная логика)........

Устройство работает следующим образом.

В памяти 30 хранятся программы обработки, представляющие собой последовательности команд. Каждая команда перед ее выполнением извлекается из памяти 30 и размещается в регистрах процессора 22, при этом адрес первого операнда размещается в регистре 24. адрес второго операнда - в регистре 25. Далее дешифрируется код операции извлеченной команды, после чего блоком микропрограммного управления вырабатываются сигналы микроопераций, необходимые для выполнения данной команды, Содержимое одноразрядных слов, хранящееся во всех памятях 13 по одному и тому же адресу, образует плоское бинарное изображение. Каждое из двух заявленных устройств оперирует изображениями, отличающимися форматом и формой пикселов. Так устройство, изображённое на фиг. 1. 2, предназначено для параллельной обработки изображений квадратного формата С х С (где С D), составленных из квадратных пикселов 1x1 (фиг. 5,6). Устройство, изображенное на фиг. 2, 3, предназначено для параллельной обработки изображений, ограниченных правильным шестиугольником и составленных либо из конгруэнтных равносторонних треугольников (фиг. 6 а), либо из конгруэнтных правильных шестиугольников (фиг. 6 б). Система команд каждого из заявленных устройств включает в себя арифметико-логические команды, команды условного и безусловного перехода, команды управления матрицей 1, Назначение и структура всех арифметико-логических команд, команд условного и

безусловного перехода полностью определяются выбранной конструкцией процессора 22, памяти 30, интерфейса 33 связи, которые выполняются по одной из известных схем (в частности, за их основу могут быть взяты центральный процессор, оперативная память и интерфейс ЭВМ Электроника-100/25 /. Назначение и структура команд управления матрицей 1 определя0 ются архитектурой межпроцессорных связей матрицы 1, составом процессорных элементов 6, 7, Узлы 3, 4 в заявленных устройствах служат для высокоскоростного вы- полнения вычислительных процедур,

5 моделирующих геометрические преобразования поворота и сжатия двухмерного евк- лидового пространства R соответственно. Принцип моделирования геометрических преобразований, реализованный в устрой0 стве заключается в одновременном (параллельном) формировании значений ФгСРе О уровней зачерненности пикселов Ре результирующего (преобразованного) бинарного изображения из значений Ф|(РгО

5 уровней зачерненности пикселов Рр2 исходного (преобразуемого)бинарного изображения. При этом из объекта Е, входящего в состав исходного бинарного изображения

(фиг. 4а) формируется объект fp(E) UPi

(2)

ifsidi . га 4/vjjjivn4|jyс i т vjwociv -J W e

0ISLE

(фиг, 5 a), являющийся дискретной (пиксель- ной) моделью образца f(E) (фиг. 4 б), где f;R2- R - моделируемое геометрическое преобразование. Разница между реализа5 цией поворота в устройстве реализацией поворота в узлах 3 заявленного устройства заключается в способе формирования дискретной модели гр (Е): в узлах 3 в формировании каждого Ф(Ре О участвует значение

0 Ф(Р| ) не более одного пиксела Р/2 удовлетворяющего условию Ре f(Pr20 0 . В результате изменения способа формирования f (Е) отпадает необходимость в использовании в узлах 3 сверхбольшого числа много5 входовых элементов ИЛИ (фиг. 7 в), или сверхбольшого числа аналоговых сумматоров и пороговых элементов (фиг. 7 б) - функцию этих элементов в заявленных устройствах выполняют обычные провод0 ные связи (фиг. 7 г), существенным образом уменьшаются яркостные искажения при реализации высокоскоростного поворота полутоновых изображений. Новый способ формирования f (Е) приводит, строго гово5 ря, к некоторому снижению точности геометрического воспроизведения f(E), однако эти искажения крайне незначительны, а выигрыш в оборудовании и энергозатратах велик, Процессоры 6,7, имеющие с пикселами обрабатываемого изображения взаимнооднозначное соответствие, связаны между собой в матрице 1 тремя группами межпроцессорных связей:

1) группой связей, реализующих перенос изображения на шаг в направлении век- тора Ох (фиг. 5, 6),

2) группой связей, реализующих поворот изображения на угол вокруг центра изображения,

3) группой связей, реализующих над со- держимым изображения преобразование осевой симметрии относительно прямой, проходящей через центр изображения и параллельной стороне формата Р изображения.

В отличие от процессора 7 процессор б каждого из устройств дополнительно связан (по входу 8 и выходу 10) с узлами 3 и 5. При этом вход 8 процессора 6, выход узла 3 и выход узла 5 соединены между собой ме- тодом монтажное ИЛИ (фиг. 1, 3). Пикселы, соответствующие процессорам 6, на изображении образуют фрагмент F. Фрагмент F для устройства, изображенного на фиг. 1, 2, имеет форму прямоугольника С х С/2 (фиг. 5 б), для устройства, изображенного на фиг. 2,3-форму ромба (фиг. 6). Бинарное содержимое фрагмента F является адресуемой информационной единицей памяти 5. Сжатие изображения осуществляет- ся в узлах 4 построчно. Назначением сумматора 50 и цифрового импульсного вольтметра 51 каждого из устройств является формирование цифрового кода значения площади одноцветного содержимого бинарного изображения, хранящегося в регистрах 14 матрицы 1. Назначением N-вхо- довой схемы 49 является выработка сигнала признака содержимое бинарного изображения, хранящегося в регистрах 14, пус- то/не пусто для организации микроветвлений. Рассмотрим подробно работу устройства, изображенного на фиг, 1, 2. В систему команд этого устройства входят следующие команды управления матрицей 1:

1) команда И-НЕ а1, а2 - сформировать бинарное изображение из двух бинарных изображений А1 и А2, хранящихся в узлах 13 матрицы 1 по адресам а1 и а2 соответст- венно, путем выполнения над ними теоретико-множественной операций А1 А А2, полученное изображение записать в матрицу 1 по адресу а2.

2) команда СДВ а1, а2 - сформировать изображение А2 из изображения А1, хранящегося в узлах 13 по адресу а1, путем переноса А1 на шаг в направлении (W, результат переноса записать по адресу а2,

3) команда ПВ1 а1, а2 - сформировать изображение А2 из А1 путем поворота изображения А1 на угол 90° вокруг центра изображения,

4) команда СИМ а1. а2 -- сформировать изображение А2 из изображения А1 путем выполнения над А1 преобразования осевой симметрии относительно прямой BD (фиг, 5 б),

5) команда ПВ2 а1, а2 - сформировать изображение А1 изА1 путем поворота квадранта исходного изображения на угол а

(0° «S45°), номер которого хранится в памяти 30 по адресу в1 (фиг. 7 д.е),

6) команда СЖ а1, в1 - сформировать изображение А1 из изображения А1 путем сдвига этого изображения на шаг в направлении ОХ, записать сжатое в К раз содержимое последней (относительно ОХ), строки С х 1 исходного изображения в первую (относительно ОХ) строку С х 1 результирующего изображения А1, код номера значения К расположен в памяти 30 по адресу в1,

7) команда ПЛ а1, в1 - сформировать код значения площади единичного содержимого изображения А1, записать сформированный код в память 30 по адресу в1,

8)соманда ЗПИ а1, в1 - записать фрагмент F изображения А1 в память 5 по адресу, код которого хранится в памяти 30 по адресует1,

9)оманда ЧПИ а1, в1 - записать фрагмент F, хранящийся в памяти 5 по адресу, код которого находится в ячейке памяти 30 по адресу в1, в матрицу 1 по адресу э1,

10) команда ЗС М а1, в1 - сдвинуть изображение А1 на шаг в направлении ОХ, записать в первую (относительноОХ) строку С х 1 содержимое ячейки памяти 30 с адресом в1,

11) команда ЧСМ а1, в1 - сдвинуть(изо- бражение А1 на шаг в направлении ОХ, записать содержимое последней (относительно ОХ) строки С х 1 исходного изображения в памяти 30 по адресу в1.

В систему команд устройства также входят:

- команда ПРО в1 - передать управление команде, хранящейся в памяти 30 по адресу в1, если сигнал с выхода схемы 49 равен 0, в противном случае перейти к следующей (по порядку) команде,

- команда ПР1 в1 - передать управление команде, хранящейся в память 30 по адресу в1, если сигнал с выхода схемы 49 равен 1, в противном случае перейти к следующей (по порядку) команде.

Каждой команде соответствует своя микропрограмма - последовательность

микрокоманд, выполнение которых приводит к выполнению операции, заданной в команде. После дешифрации кода операции адрес начального микрословэ команды записывается в регистр микроадреса процессора 22. По этому микроадресу из памяти микропрограмм процессора 22 извлекается управляющее микрослово и загружается в регистр 23 микрослова, Это микрослово содержит управляющее поле, разряды которого используются для генерации сигналов требуемых микроопераций, а также поле следующего микроадреса и поле кода микроветвления. Поле следующего микроадреса содержит базовый микроадрес, который указывает на следующее микрослово при естественной последовательности выборки микрослов. Этот базовый микроадрес может быть модифицирован с целью микровет- вления по е кода микроветвления определяет какие признаки необходимо проверить и использовать для модификации микроадреса. Часть управляющего поля микрослова образует поле управления матрицей 1, в это поле входят: три разряда кода РВВ, один разряд ЗЛИ, один разряд ЗП1, один разряд ЗП2, один разряд ЗПЗ, разряд СР1, разряд СР2, три разряда кода КМО, разряд РУАВ, разряд ПЛ. Рассмотрим выполнение каждой из перечисленных команд управления матрицей. При этом будет считать, что преобразуемые геометрические объекты представлены в бинарных изображениях в негативном виде (т.е. логическим О - низким уровнем).

Команда ИНЕ а1, а2 Начальное микрослово этой команды содержит следующую информацию: РУАВ О, СР 1, По синхросигналу С1 (фиг. 2), вырабатываемому геие- ратором синхроимпульсов процессора 22, код адреса al, снимаемый с выходов регистра 24. подключается мультиплексором 40 к адресным входам АЛП узлов 13. С приходом синхроимпульса С2 на подготовленный элемент 45 сигнал Р1 записывает информацию с выходов узлов 13 в регистры 14. С приходом следующего синхроимпульса С1 извлекается второе микрослово, содержащее РУАВ 1, СР1 О, СР2 1, КМО 000 - код микрооперации ИНЕ, ЭП1 1, ЭП2 1. Код а2, снимаемый с выходов регистра 25, подключается к входам АЛП узлов 13. Импульс С2, пройдя через подготовленный элемент 46, записывает информацию с выходов узлов 13 в регистры 15. С приходом С 3 сигнал с выхода элемента 16 через подготовленный элемент 17 записывается в узел 13 по адресу а2. Далее осуществляется переход к микропрограмме извлечения следующей команды из памяти 30 в регистры 24, 25. Команда ПВ1 а1, а2. Микропрограмма этой команды включает микрослово (РУАВ О, СР1 1) и микрослово (РУАВ 1, КМО

5 001-кодмикрооперацииП90°,ЗП1 1,ЗП2 1). В результате выполнения первого микрослова содержимое узлов 13с адресом а1 записывается в регистры 14. По С1 в регистр 23 вызывается второе микрослово. С прихо0 дом СЗ производится запись содержимого регистра 14 через подготовленный ключ 18 в узел 1.3 соответствующего процессора матрицы 1 (передача осуществляется по проводным связям, относящимся к второй

5 группе межоперационных связей). Команды СДВ а1, а2 и СИМ а1, а2. Микропрограммы этих команд отличаются от микропрограм- , мы ПВ1 а1, а2 тем, что во втором микрослове в случае СДВ а1, а2 код КМО равняется

0 010 (код микрооперации СДВ), а в случае СИМ а1, а2 - 011 (код микрооперации СИМ). Функцию управляющего ключа при выполнении СДВ а1, а2 выполняет элемент 19, а при выполнении СИМ а1, а2 -элемент20. После

5 выполнения СДВ а1, а2 первая (относительно ОХ) строка С х 1 заполняется единицами, т.к. высокий уровень логической 1 с выходов делителей (фиг. 5 б) поступает на входы 9 (РВВ 000)

0 Команда ПВ2 а 1, а2 осуществляет поворот квадранта С/2 х С/2, входящего в состав фрагмента F (фиг. 5 б, фиг, 7 д,е) изображения А1, на угол а некратный 90°. В начале выполнения команды двоичный код номера

5 угла а, хранящийся в памяти 30 по адресу в1, записывается в регистр 26 процессора 22. Сигнал, снимаемый с выхода дешифратора 34 и соответствующий коду номера а , поступает на шифратор, построенный из

0 элементов 36, и далее на информационные входы элементов 35. Выход каждого j-r.o элемента 35 соединен с управляющими входами элементов 56 j-ro узла 3, предназначенного для моделирования по5 ворота j-ой зону Zj (фиг. 7, е) поворачиваемого квадранта С/2 х С/2. j-й узел 3 используется (в общем случае) для моделирования поворота aoHbi Zj на несколько углов из диапазона 0° а 45°. Далее с

0 приходом С1 выполняется микрослово, содержащее: РУАВ О, СР1 1. КМО 100 - код микрооперации ПРМ, ЗП1 1. ЗП2 О, РВВ 001 - код режима ПВ. Сигнал с выхода ПВ дешифратора 39 открывает подготов5 ленные ключи 35, которые, в свою очередь, подготавливают элементы 56 выбранных узлов З..По С2 изображение А1 из узлов 13 переписывается в регистры 14 и на входах 8 появляется изображение повернутого квад- ... ... ранта. С приходом СЗ информация с входов

8 записывается в узлы 13 процессоров б по адресу а1. В узлах 13 процессоров информация не изменяется. Команда СЖ а1, а2. В начале выполнения команды двоичный код номера коэффициента К извлекается из па- мяти 30 и записывается в регистр 26. Сигнал, снимаемый с выхода дешифратора 34 и соответствующий коду номера К, поступает на шифратор, построенный из элементов 38 и далее на информационные входы элемен- тов 37. Выход каждого элемента 37 соединен с управляющими входами элементов 56 }-гоузла4, предназначенного для моделирования сжатия j-й зоны сжимаемой строки, j-й узел 4 используется (в общем случае) для моделирования сжатия j-й зоны на несколько коэффициентов сжатия. С приходом С1 выполняется микрослово, содержащее: РУ- АВ 0, СР1 1, КМО 010, ЗП1- 1,, РВВ 010 - код режима СН. Сигнал с выхо- да СЖ дешифратора 39 открывает подготовленные ключи 37, которые, в свою очередь, подготавливают элементы 56 выбранных узлов 4. По С 2 изображение А1 из узлов 13 переписывается в регистры 14 и на входах 9 появляется изображение сжатой строки. С приходом СЗ информация с входов 9 записывается в узлы 13 первой (относительно ОХ) строки Сх 1 матрицы 1, в узлы 13 остальных строк записывается исходное содержи- мое А1 со сдвигом на шаг в направлении ОХ. Команда ПЛ а1, в1. Микрослово этой команды содержит РУАВ О, СР1 1, ПЛ 1. По С2 содержимое А1 записывается в регистры 14, с приходом СЗ импульс с выхода элемен- та 47 поступает на вход опроса аналогового сумматора 50 и на вход синхронизации вольтметра 51. С выхода сумматора 50 импульс, амплитуда которого пропорциональна числу регистров 14, находящихся в единичном состоянии, поступает на информационный вход вольтметра 51. По окончании цикла аналого-цифрового преобразования код значения площади единичного содержимого А1 через контроллер 52 записывается в память 30 по адресу в1. Команда ЗПИ а1, в1. В начале выполнения команды в регистр 29 записывается содержимое ячейки в1. Далее выполняется микрослово, содержащее: РУАВ О, СР1 1,ЗПИ 1. По С2 содержимое А1 переписывается в регистры 14 и на информационных входах памяти 5 (выходы 10 матрицы 1) появляется изображение фрагмента F этого изображения. С приходом СЗ сигнал записи, снимав- мый с выхода элемента 42, записывает содержимое фрагмента F в память 5 по адресу, хранящемуся в регистре 29. Команда ЧПИ а1, в|. В начале выполнения команды в регистр 29 записывается содержимое

ячейки в1. Далее выполняется микрослово, содержащее: РУАВ О, КМО 100. РВВ 011 - код режима ЧПИ, ЗП1 1. С приходом С1 сигнал с выхода ЧПИ дешифратора 39 подключит выходы памяти 5, на которых находится извлеченный фрагмент F, к входам 8 матрицы 1. По С 3 сигнал с выхода элемента 43 запишет информацию с выходов 8 в узлы 13 процессоров 6 по адресу а1. Команда ЗСМ а1, в1. В начале выполнения команды слово, хранящееся в памяти 30 по адресу в1, переписывается в регистр 28. Далее выполняется микрослово, содержащее РУАВ О, РВВ 100 - код режима ЗСМ: СР1 1, КМО 010, ЗП1 1, . По С1 выходы регистра 28 сигналом, снимаемым с выхода ЗСМ дешифратора 39, соединяются с входами 9 матрицы. 1. По С2 изображение А1 записывается в регистры 14. По СЗ информация с входа 9 записывается в первую (относительно ОХ) строку С х 1 матрицы 1 по адресу а1, в узлы 13 остальных строк записывается сдвинутое исходное содержимое А1.

Команды ЧСМ а1, в1. Микрослово этой команды содержит: РУАВ О, РВВ 101 - код режима ЧС, СР1 1, КМО 010, ЗП1 1, ЗП2 1. По С2 изображение А1 записывается в регистры 14. По СЗ информация с выхо- ,дов регистров 14, принадлежащих последней (относительно ОХ) строке С х 1 матрицы 1, сигналом, снимаемым с выхода элемента 41, записывается в регистр 27. Содержимое остальных регистров 14 со сдвигом на шаг записывается в матрицу 1 по адресу а1. Далее содержимое регистра 27 записывается в память 30 в ячейку с адресом в1. Рассмотрим работу устройства, изображенного на фиг. 2, 3. Это устройство предназначено для параллельной обработки изображений, имеющих шестиугольный формат и состоящих либо из треугольных (фиг. 6 а), либо из шестиугольных пикселов (фиг. 6 б). Ориентация устройства на обработку изображений данного вида позволяет примерно на треть сократить число проводных связей и элементов 56, используемых в узлах 3, по сравнению с устройством, рассмотренным выше, что дает возможность иметь больший диапазон углов высокоскоростного поворота при одинаковом объеме оборудования, используемого в устройствах. В зависимости от способа управления узлами 13 все процессоры матрицы 1 делятся на три группы. Первую группу образуют процессоры 6, входы 8 и выходы 10 которых непосредственно связаны с узлами 3, 5. Запись информации в узлы 13 процессоров 6 осуществляется микрооперацией ЗП1. Процессорам 6 матрицы 1 на изображении соответствует ромбовидный фрагмент F (фиг.

6). Вторую группу образуют процессоры, через которые в матрице 1 осуществляется передача информации от входов 9 к выходам 11 (путем пошагового сдвига в направлении ОХ). Запись информации в узлы 13 этих процессоров производится микрооперацией ЗП2. Процессорам этой группы на изображении соответствует фрагмент Т. Для случая Т F (фиг. 6 б) выполняется ЗП1 ЗП2, К третьей группе процессоров отно- сятся процессоры матрицы 1, не входящие в первые две из названных групп. Запись информации в узлы 13 этих процессоров производится микрооперацией ЗПЗ. Группе процессоров на зображении соответст- вует фрагмент Р P (UF). Одновременная запись во все узлы 13 матрицы 1 осуществляется одновременной подачей сигналов WRi, WRa. WRa, для чего соответствующее микрослово должно содержать ЗП1 1, ЗЛ2 1,ЗПЗ 1.

Проиллюстрируем выполнение команд устройства на примере устройства, ориентированного на обработку изображений с треугольными пикселами (фиг. 6 а), если ТП F 0, форма и размерит совпадают с формой и размером ромба F. Процессоры 7, принадлежащие второй группе процессоров матрицы 1, обозначим 7t процессоры 7, принадлежащие третьей группе, обозначим 2. Число команд, входящих в систему команд рассматриваемого устройства их мнемоническое обозначение совпадают с числом и мнемоническим обозначением команд устройства, рассмотренного ранее (фиг. 1, 2). Однако из-за различия в применяемых способах дискретизации R , а также различия в форматах р 2 обрабатываемых изображений некоторые из этих команд (за исключением арифметико-логических ко- манд, команд условного и безусловного перехода, ИНЕ а1, а2, СДВ а1, а2, СИМ at, a2, ЧПИ al, в1, ЗЛИ al, в1, ПЛ а1, в1) имеют несколько иной смысл. Рассмотрим в отдельности каждую из этих команд. Команда ПВ1 а1, э2 - сформировать изображение А2 из изображения А1 путем поворота изображения А1 на угол 60° вокруг центра изображения, результат поворота записать в матрицу 1 по адресу э2. Микропрограмма этой команды включает микрослово (РУАВ 0, СР1 1) и микрослово (РУАВ 1, КМО 001 - код микрооперации П60°, ЗП1 - 1, ЗП2 1, ЗПЗ 1). Выполнение команды аналогично выполнению команды ПВ1 al. а2 устройства (фиг. 1, 2). Команда ПВ2 al. в1 - сформировать изображение А1 из изображения А1 путем поворота треугольного фрагмента этого изображения (фиг. 8) на

угол а (0 а 30°), номер которого хранится в памяти 30 по адресу в1. Выполнение команды аналогично выполнению команды ПВ2 а1, в1 устройства (фиг. 1,2). Команда СЖ а1, в1 - сформировать изображение А1 из изображения А1 путем сдвига содержимого фрагмента Т на шаг в направлении ОХ, записать сжатое в К раз содержимое последней (по направлению ОХ) строки фрагмента Т исходного изображения А1 в первую (относительно ОХ) строку фрагмента Т результирующего изображения код номера значения К расположен в памяти 30 по адресу в1. Сжатие строки, выполняемое командой, является косоугольным и осуществляется к оси ОХ (фиг. 9,6). Микропрограмма команды содержит микрослово (РУАВ О, СР1 1, КМО 010 - код микрооперации СДВ, ЗП1 0, ЗП2 1, ЗПЗ 0, РВВ 010- код режима СЖ). В остальном реализация этой команды совпадает с реализацией команды СЖа1, в1 устройства (фиг. 1, 2). Команда ЗСМ а1, в1 - записать слово, хранящееся в памяти 30 в ячейке с адресом в1, в матрицу 1 по адресу al, сдвинуть содержимое фрагмента Т исходного изображения А1 на шаг по направлению ОХ. Микропрограмма команды содержит микрослово (РУАВ О, РВВ 100 -- код режима ЗСМ, СР1 1, КМО 010, ЗП2 1, Зт О, ЗПЗ 0). В остальном реализация команды совпадает с реализацией команды ЗСМ а1 в1 устройства (фиг. 1, 2).оманда ЧСМ а1, в1 - сдвинуть фрагмент Т изображения А1 на шаг в направлении Ох, записать содержимое последней (относительно ОХ) строки фрагмента Т в память 30 по адресу в1. Микрослово команды содержит: РУАВ О, РВВ 101 -код режимаЧС, СР1 1, КМО 010,ЗП1 О, ЗП2 1, ЗПЗ 0). В остальном реализация команды совпадает с реализацией команды ЧСМ а1, в1 устройства (фиг. 1, 2). Обработка изображений с помощью устройства (фиг. 2, 3) осуществляется в 60°-й косоугольной системе координат (фиг. 9а). Изменение масштаба полноформатного изображения производится при помощи команд СЖа1, в1,ПВ1 а1. а2. СИМа1.а2. На фиг. 9(а) показан принцип моделирования преобразования сжатия R к точке О путем последовательного выполнения 60°-го косо.- угольного сжатия R2 к оси ОХ и 60°-го косоугольного сжатия R2 к оси ОY. На фиг.9 (в-з) показаны последовательные этапы реализации сжатия полноформатного изображения (фиг. 9 в) к центру изображения. Поворот полноформатных изображений на углы некратные 60° осуществляются в устройстве при помощи команд: ПВ2 а1. в1, ПВ1 а1, а2, ИНЕа1.а2. СИМа1,а2./

Наличие в составе заявленного устройства сверхбольшого числа электронных компонентов и проводных связей требует использование в этих устройствах специальной элементной базы и специальной не- сущесоединительной конструкции. Процессоры 6, 7, связанные в матрице 1 проводными связями, относящимися к второй и третьей группам межпроцессорных связей, и образующие относительно этих связей замкнутую систему, объединяются в модуль 53, изготавливаемый по интегральной технологии. Тем самым уменьшается число межмодульных связей, повышается надежность устройства, Пикселы, соответ- ствующие процессорам 6, 7, входящим в модуль 53 на фиг. 5(6), б выделены сплошной и двойной штриховкой. Возможности использования в заявленном устройстве для решения задач анализа и синтеза изображе- ний продемонстрируем на примере решения с помощью устройства (фиг. 1, 2) задачи выделения из произвольного 4-уровневого изображения СхС (фиг. 10,6) связанного плоского объекта, геометрическая форма которого совпадает с геометрической формой заданного объекта-эталона (фиг. 10а) и составленного из пикселов 1 х 1 3-го уровня зачерненности. Анализируемое изображение представлено в матрице 1 двумя бинар- ными изображениями А1 и А2, соответствующими двум разрядам двоичного кода интенсивности. Эталон представлен бинарным изображением АО. После цифровой фильтрации (выполняемой при помощи команд СДВ, ПВ1, ИНЕ) формируется бинарное изображение (фиг. 10 в), темные пикселы которого соответствуют пикселам 3-го уровня зачерненности отфильтрованного исходного изображения (фиг. 10,6). Далее осуществляется выделение из изображения (фиг. 10,в) первого темного топологически- связного объекта Q. Выделение начинается с захвата (с помощью команд СДВ, ПВ1, ИНЕ, ПРО) верхнего правого темного пиксе- :ла (фиг. 10,г) этого изображения. Путем анализа соседних пикселов из захваченной точки строится изображение всего объекта Q (фиг. Ю.д.е.ж). После этого при помощи команды ПЛ определяется площадь объекта Q, ас помощью команд СДВ, ПВ1, ПРО определяются его габаритные размеры и его положение на изображении (фиг. 10,з). Далее вычисляется значение К S3/So (где 5э - площадь эталона; SQ - площадь объекта Q) и производится сжатие эталона в К раз (фиг. 10 и). Затем определяются габаритные размеры сжатого эталона и сравниваются с габаритными размерами объекта Q. Если габаритные размеры эталона и объекта не

совпадают, осуществляется поворот сжатого эталона на угол а и вновь производится сравнение габаритных размеров объекта U и повернутого эталона. Если габаритные размеры опять не совпадают, осуществляется поворот эталона на угол а +1 и т.д. При совпадении габаритных размеров производится привязка объекта Q и эталона L, после чего выполняется теоретико-множественная операция М Q/L. Если площадь 5м объекта М не превышает критического значения SK, объект Q и эталон считаются фигурами, обладающими одинаковой геометрической формой, и задача решена. Если SM SK производится поворот сжатого эталона на следующий угол а + 1 и процедура повторяется. Если SM SK, а диапазон углов исчерпан , то формы объекта и эталона не совпадают. В этом случае объект Q удаляется из изображения (фиг. 10,в) и процедура анализа повторяется. Так как устройство (фиг. 1, -2) отличается сверхскоростным выполнением теоретико-множественных операций, сжатий, поворотов, сдеигов, анализа на пересекаемость, вычисления площади, время выполнения данного алгоритма с помощью указанного устройства будет крайне малым. Заявленные устройства позволяют обрабатывать изображения сверхвысокого разрешения, в которых изображения F являются лишь фрагментами (фиг. 11). Обработка таких изображений осуществляется в устройствах последовательно: фрагмент за фрагментом.

По сравнению с прототипом в заявленных устройствах значительно сокращено время выполнения (над изображениями) геометрических преобразований, анализа на пересекаемость, вычислены площади. Формула изобретения 1. Устройство обработки изображений, содержащее матрицу процессоров, блок управления, матрицу узлов памяти, матрицу узлов сжатия-растяжения и матрицу узлов поворота, причем первая группа информационных выходов матрицы процессоров соединена с первой группой информационных выходов устройства и с группами информационных входов матриц узлов памяти и узлов поворота, группы информационных выходов которых соединены с первой группой информационных входов матрицы процессоров, группа управляющих входов которой и группы управляющих входов матриц узлов памяти, узлов сжатия-растяжения и узлов поворота соединены с соответствующими группами управляющих выходов блока управления, отличающееся тем, что, с целью увеличения скорости и точности

выполнения поворотов и сжатий изображений, вторая группа информационных выходов матрицы процессоров соединена с информационными входами матрицы узлов сжатия-растяжения, блока управления и является второй группой информационных выходов устройства, группа информационных входов которого соединена с второй группой информационных входов матрицы процессоров и группой информационных

выходов матрицы узлов сжа ия растяже- ния.

2. Устройство по п. 1, о т л и ч а ю щ е е- с я тем, что матрица процессоров имеет квадратную решетку.

3. Устройство по п. .1, о т л и ч а ю щ е е- с я тем, что матрица процессоров имеет треугольную решетку.

4. Устройство по п. 1, о т л и ч а ю щ е е- с я тем, что матрица процессоров имеет гексагональную решетку.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для параллельной обработки трехмерных сцен | 1990 |

|

SU1817109A1 |

| Устройство для параллельной обработки трехмерных сцен | 1986 |

|

SU1456965A1 |

| Устройство для параллельной обработки трехмерных сцен | 1988 |

|

SU1612307A2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ АВТОНОМНЫМ РОБОТОМ | 2008 |

|

RU2424105C2 |

| Устройство для параллельной обработки трехмерных сцен | 1988 |

|

SU1689966A1 |

| УСТРОЙСТВО ОБРАБОТКИ ДВУХМЕРНЫХ И ТРЕХМЕРНЫХ ИЗОБРАЖЕНИЙ | 2005 |

|

RU2289161C1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| УСТРОЙСТВО ОБРАБОТКИ ДВУХМЕРНЫХ И ТРЕХМЕРНЫХ ИЗОБРАЖЕНИЙ | 2008 |

|

RU2376637C1 |

| Микропроцессорное вычислительное устройство | 1982 |

|

SU1269145A1 |

| Устройство для сопряжения двух микро эвм с общей памятью | 1985 |

|

SU1280643A1 |

Изобретение относится к вычислительной технике, предназначено для решения задач обработки изображений, задач размещения, распознавания образов, машинной графики. Цель изобретения - увеличение скорости и точности выполнения поворотов и сжатий изображений. Для этого устройство содержит матрицу процессоров, матрицу узлов памяти, матрицу узлов поворота, блок управления и блок узлов сжатия-растяжения. 3 з.п. ф-лы, 11 ил.

.- j fe./

SL

JL

9W

Л

о

Л---t

VV v i

& p

«)

(

(в

80Ш81

ft

(

fc

801Z.181

aJ

У .

ж)

)

. 10

9

i)

У

s).

А)

с. Я.

| Устройство для параллельной обработки трехмерных сцен | 1986 |

|

SU1456965A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

| Устройство для параллельной обработки трехмерных сцен | 1988 |

|

SU1612307A2 |

Авторы

Даты

1993-05-23—Публикация

1989-09-13—Подача