Изобретение относится к области кибернетики и вычислительной техники и может быть использовано при обработке и распознавании изображений объектов.

Сущность преобразования Хо состоит в следующем. Пусть R - область определения сигналов изображения и в ней действует прямоугольная система координат хОу. Тогда координаты точки изображения могут быть заданы парой (х, у), а амплитуда сигнала изображения в этой точке - как S (х, у).

Контур изображения объекта всегда представим совокупностью отрезков прямых линий. Произвольную прямую линию L в области R можно описать в виде уравнения

р х cos 0+ у sin в , (1) где р - длина нормали, проведенной из начала координат (точки О) к рассматриваемой линии;

0 - угол между направлением Ох и - нормалью; х, ye L

Если, например, лрямая составлена из конечного числа точек-ячеек (XL yi), (xa, y2). ..., (хп, УП), то любая пара из этого семейства должна удовлетворять уравнению

p xi-cos 0+yi-sln 0; I 1, 2,..., n, (2) Введем в рассмотрение область Р определения параметров; произвольная точка этой области задается парой (р, 0), а параметр в этой точке - как h (р, 0). Тогда прямую L можно записать в виде S(x, у, р, ©), где S( ) - амплитуда сигнала изображения в точке (х, у), а связь между парами координат (х, у) и (р, 0) выражается уравнением (1). Преобразование Хо прямой L выполняется по правилу:

00

ел о

2

h(p, 0) // S(x, у, р, в) dx dy, x, у с L, (3)

а при конечном числе точек, образующих прямую линию L, как

h(h,0) 2 S (xi. yi), xi, yi e L , (4) i 1

Согласно (3), (4). преобразование Хо состоит в интегрировании (или суммировании) амплитуд сигналов изображения вдоль каждого из возможных линейных направлений и отображении этой суммы параметром h(p, О ) в соответствующей точке области Р.

Известна техническая реализация преобразования Хо изображения с помощью специализированной параллельной вычислительной структуры 1. Однако данная структура включает в себя очень большое количество отдельных процессоров, соединенных между собой многочисленными связями. Поэтому специализированная параллельная вычислительная структура неудобна в реализации даже на сверхбольших интегральных микросхемах.

Известен другой, более простой и высокопроизводительный процессор 2 для выполнения преобразования Хо изображений. Этот процессор выбран в качестве устройства - прототипа. Процессор включает в себя телевизионную камеру, аналого-цифровые и цифроаналоговые преобразователи, блоки оперативной и постоянной памяти, управляющую вычислительную систему, блок адресов ячеек сигналов изображения, буферные накопители, блок памяти параметров, секцию обработки параметров, логико-вычислительные блоки, секцию памяти кадра, секцию вычисления адреса параметра.

Исходное изображение преобразуется с помощью телевизионной камеры в видеосигнал, который после его аналого-цифрового преобразования поступает в секцию памяти кадра.

На очередном шаге из блока адресов ячеек сигналов изображения на вход секции вычисления адреса параметра поступает пара (xi, yi). Другой вход этой секции соединен с памятью, гд записаны sin On и cos ©n . Первоначально на вход секции вычисления адреса параметра подаются значения sin Gb и cos 6b и на ее выходе вычисляется значение ро, удовлетворяющее уравнению (2), которое запоминается в буферной памяти. Далее выбирается следующее значение ©1 и из памяти на вход секции вычисления адреса параметра поступают значения

sin ©i и cos ©i , по которым здесь вычисляется соответствующее значение pi. Оно также запоминается в буферной памяти. Эти вычисления проводятся для всех

возможных значений ®п, в результате чего в буферной памяти запоминаются 512 значений рп. Далее содержимое ячейки (xi, yi) сигнала изображения извлекается из памяти кадра и записывается в те ячейки блока

памяти параметров, адреса которых ( ©h, рп) сформированы в соответствии с описанной процедурой. Управление записью ведется блоком обработки параметров.

После этого из блока адресов ячеек сигналов изображения извлекается новая пара (xi, yi) и вся процедура повторяется до тех пор, пока не будут таким образом обработаны все адреса сигналов ячеек секции памяти кадра. По окончании этой обработки в блоке

памяти параметров формируется преобразование Хо исходногоо изображения.

Недостатки прототипа: 1) наличие составляющей ошибки выполнения преобразования Хо, связанной с необходимостью

предварительного квантования амплитуд сигналов и значений параметров; 2) сложность устройства, обусловленная использованием в его схеме универсальных вычислительных систем, нескольких.видов

оперативной и постоянной памяти, аналого-цифрового и цифроаналогового преобразователей.

Цель предлагаемого изобретения - повышение точности и упрощение устройства

за счет использования аналоговой формы представления обрабатываемых сигналов изображения при цифровом управлении процессами обработки с помощью специализированных вычислительных и управляющих микросхем.

Аналоговое представление сигналов изображения позволило исключить потребность в квантовании этих сигналов и тем самым устранить погрешности, обусловленные этой операцией. Использование принципа цифрового управления процессами обработки сигналов изображения с помощью специализированных вычислительных управляющих микросхем позволило упростить схему устройства и исключить используемые в прототипе блок постоянной памяти, вычислительные системы, аналого- цифровые и цифроаналоговые преобразователи.

Поставленная цель достигается благодаря тому, что в устройстве использованы секция памяти кадра, блок памяти параметров, секция обработки параметров, первый блок адресов ячеек сигналов изображения

из схемы устройства - прототипа и дополнительно введены оптическая головка, выход которой оптически соединен с информационным выходом секции памяти кадра, накопитель сигналов, информационный вход которого подключен к выходу секции памяти кадра, выход накопителя сигналов подключен к информационному входу блока памяти параметров, блок мультиплексоров, генератор тактовых импульсов, формирователи адреса строки и столбца параметров, второй блок адресов ячеек сигналов изображения, элемент задержки и блок инициализации, при этом первый выход секции обработки параметров соединен с управляющим входом накопителя сигналов, входом записи блока памяти параметров и входом управления сдвигом формирователя адреса столбца параметров, управляющий выход которого подключен к первому управляющему входу секции обработки параметров, второй и третий управляющие входы которой соеди йены соответственно с первым и вторым управляющими выходами первого блока адресов ячеек сигналов изображения, второй выход секции обработки параметров соединен с входами управления сдвигом блока памяти параметров, формирователя адреса строки параметров и обнуляющим входом формирователя адреса столбца параметров, информационный выход формирователя адреса столбца параметров подключен к первому параметрическому входу второго блока адресов ячеек сигналов изображения и параметрическому входу первого блока адресов ячеек сигналов изображения, первый и второй информационные выходы которого соединены соответственно с первым и вторым информационными входами блока мультиплексоров, выходы которого соединены с адресными входами секции памяти кадра, первый управляющий вход которой соединен с первыми управляющими входами первого и второго блоков адресов ячеек сигналов изображения, управляющим входом блока мультиплексоров и первым управляющим выходом формирователя адреса строки параметров, информационный и третий управляющий выходы которо- гоо подключены соответственно ко второму параметрическому и второму управляющему входам второго блока адресов ячеек сигналов изображения, первый и второй информационные выходы которого соединены соответственно с третьим и четвертым информационными входами блока мультиплексоров, разрешающий вход которого соединен с первым управляющим выходом второго блока адресов ячеек сигналов изображения и со вторым управляющим вхо- дом секции памяти кадра, третий управляющий вход которой соединен со вторым управляющим выходом второго блока адре- 5 сов ячеек сигналов изображения, третий управляющий выход которого соединен с четвертым управляющим входом секции обработки параметров, выход генератора тактовых импульсов соединен с первым 0 тактовым входом секции памяти кадра и входом элемента задержки, выход которого соединен со вторым тактовым входом секции памяти кадра и тактовыми входами формирователя адреса строки параметров, 5 секции обработки параметров, формирователя адреса столбца параметров, второго блока адресов ячеек сигналов изображения, блока мультиплексоров и первого блока адресов ячеек сигналов изображения, второй 0 управляющий вход которого соединен с четвертым управляющим выходом формирователя адреса строки параметров, второй управляющий выход которого соединен со входом считывания секции обработки пара- 5 метров и входом сброса секции памяти кадра, выход блока инициализации подключен ко входу генератора тактовых импульсов, к инициализирующим входам формирователей адреса строки и столбца параметров, 0 первого и второго блока адресов ячеек сигналов изображения.

Сопоставительный анализ показывает, что заявляемое устройство отличается тем, что в его схему (по сравнению с прототипом) 5 введены оптическая головка, накопитель сигналов, блок мультиплексоров, генератор тактовых импульсов, формирователи адресов строки и столбца параметров, дополнительный блок адресов ячеек сигналов 0 изображения, элемент задержки и блок инициализации.

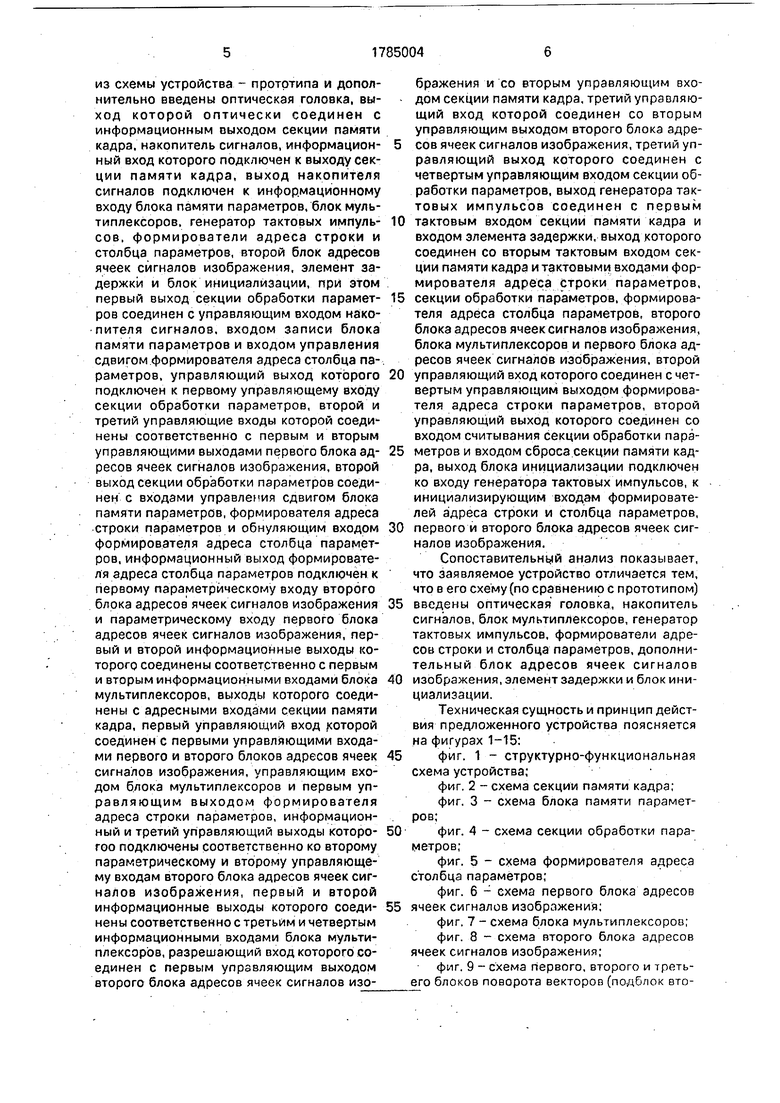

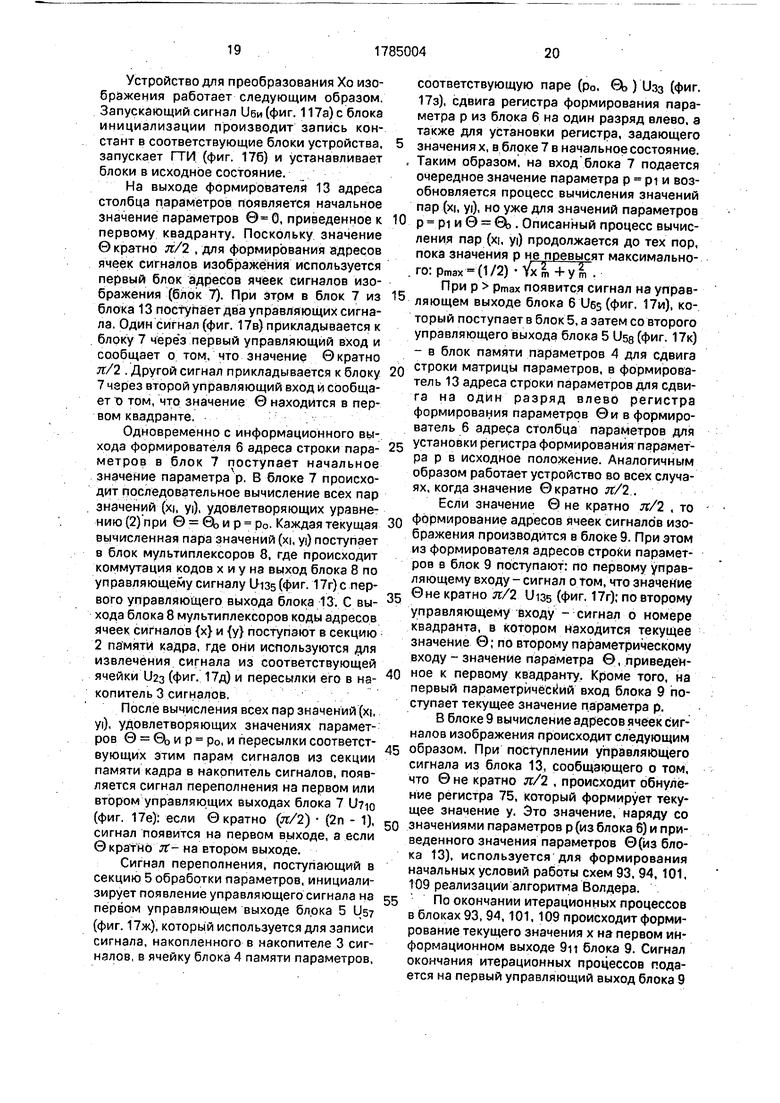

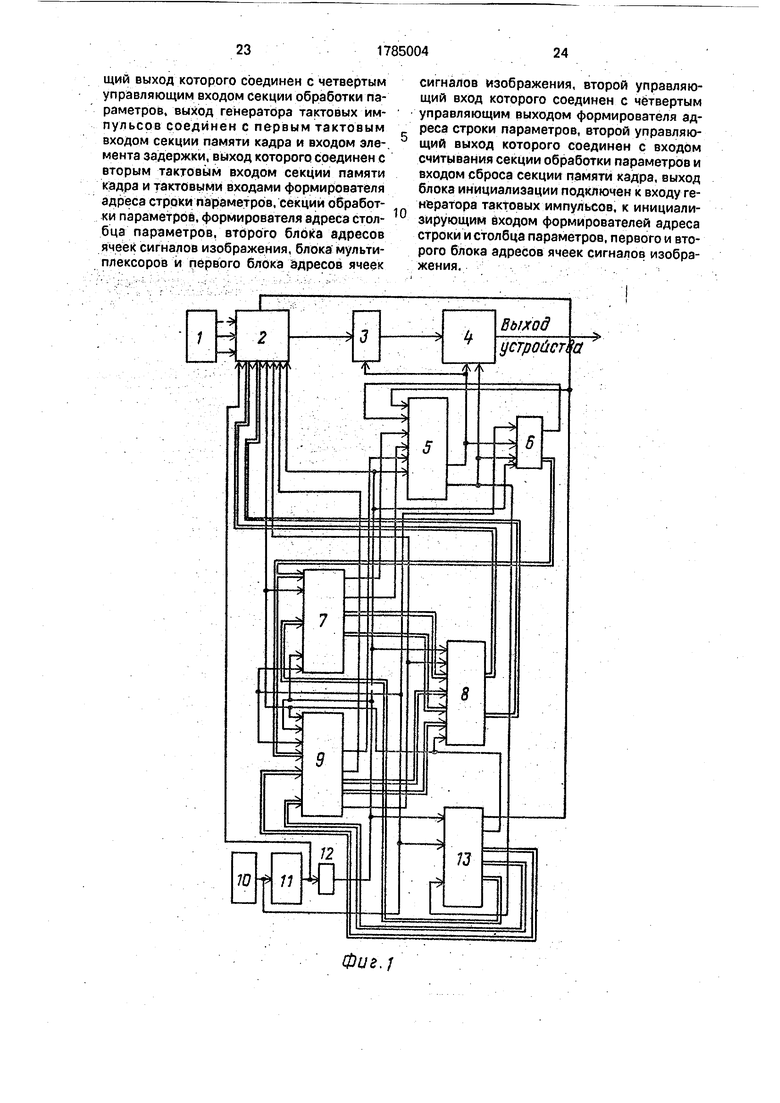

Техническая сущность и принцип действия предложенного устройства поясняется на фигурах 1-15:

5 фиг. 1 - структурно-функциональная схема устройства;

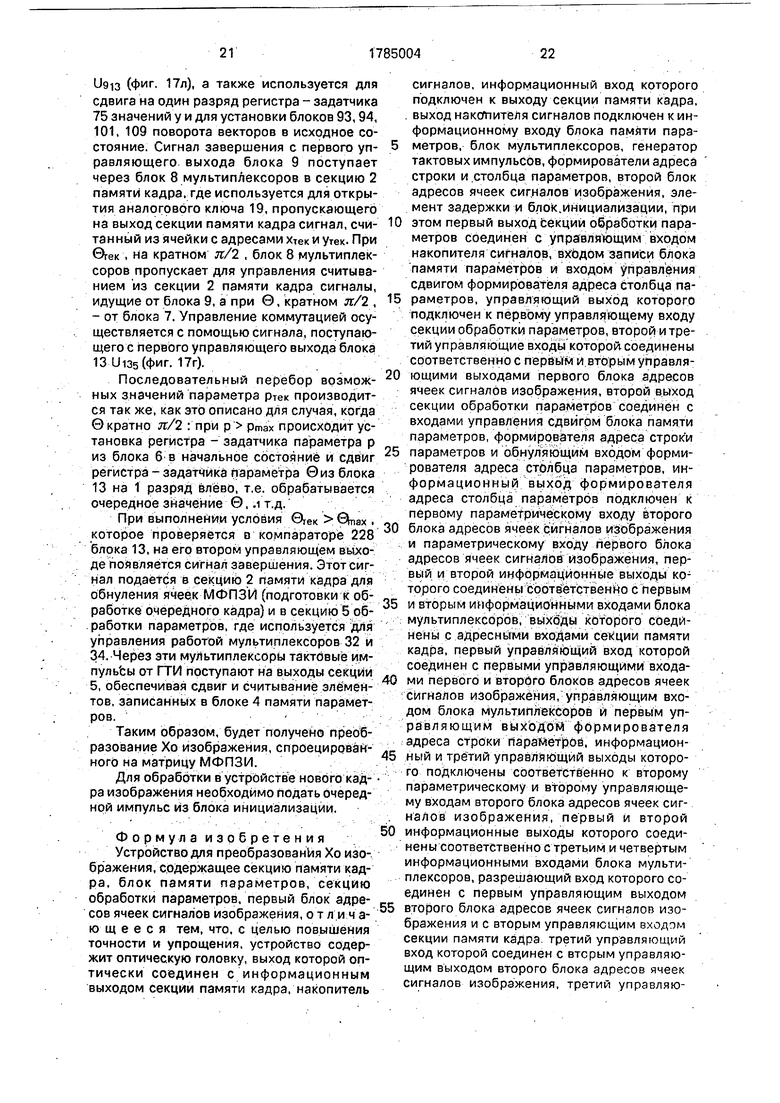

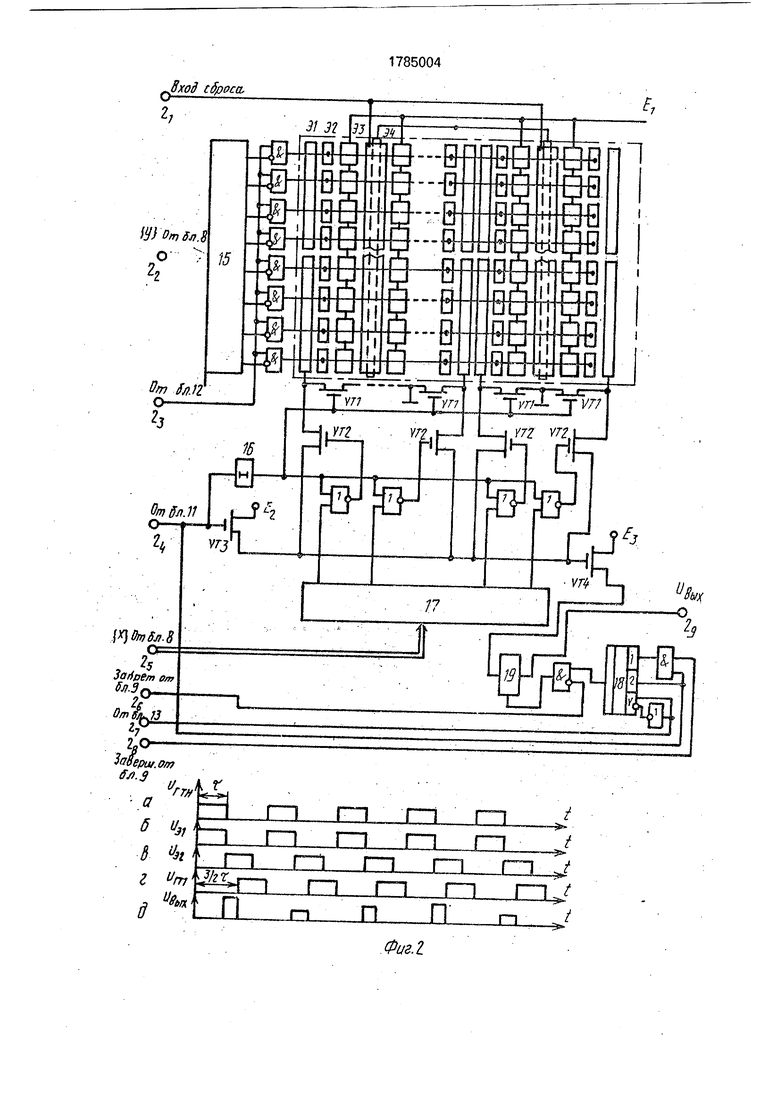

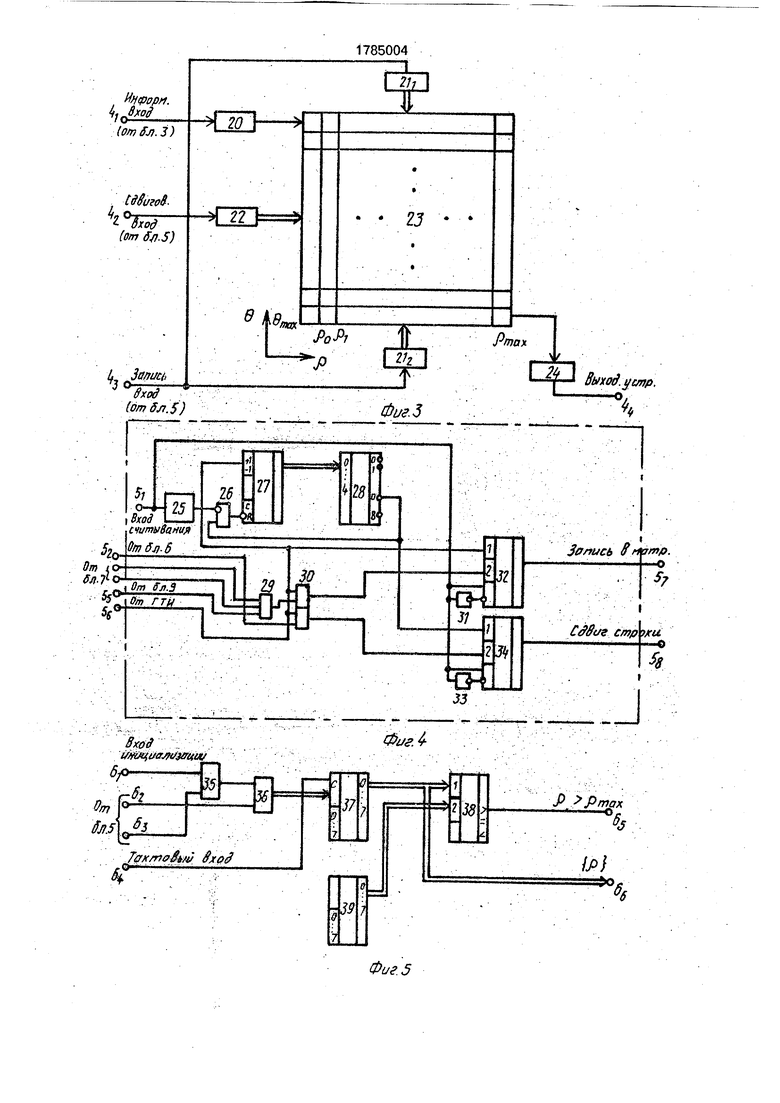

фиг. 2 - схема секции памяти кадра; фиг. 3 - схема блока памяти параметров;

0 фиг. 4 - схема секции обработки параметров;

фиг. 5 - схема формирователя адреса столбца параметров;

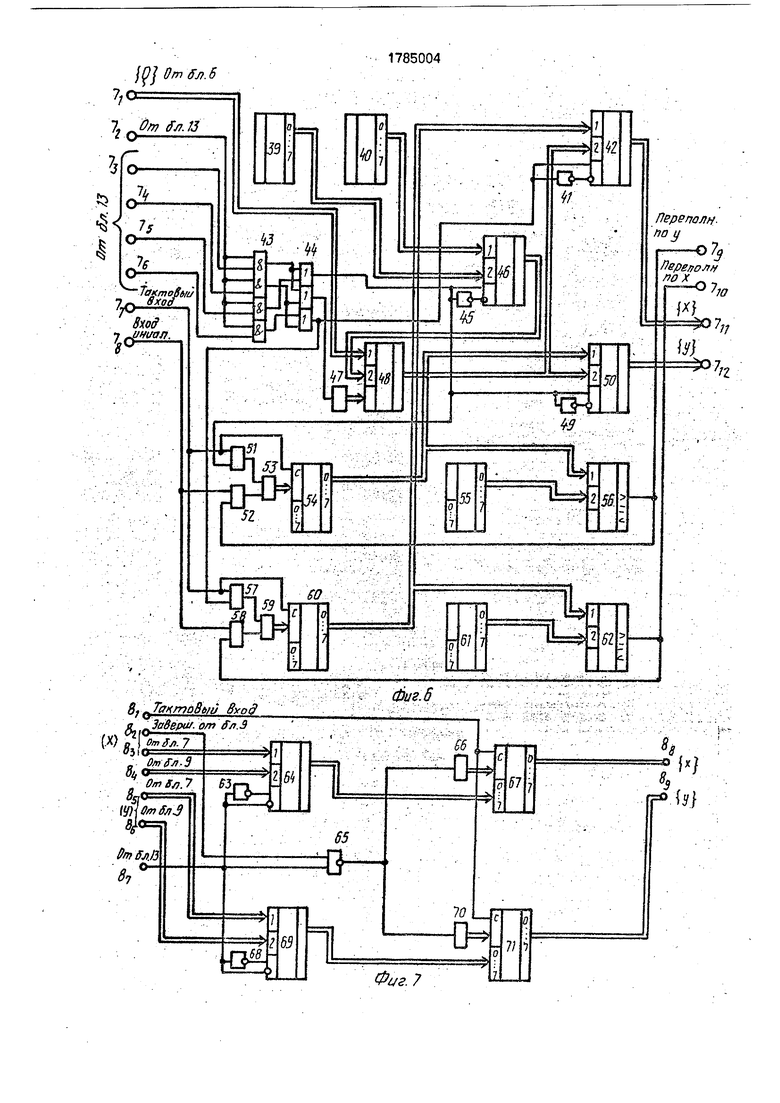

фиг. 6 - схема первого блока адресов 5 ячеек сигналов изображения;

фиг, 7 - схема блока мультиплексоров; фиг. 8 - схема второго блока адресов ячеек сигналов изображения;

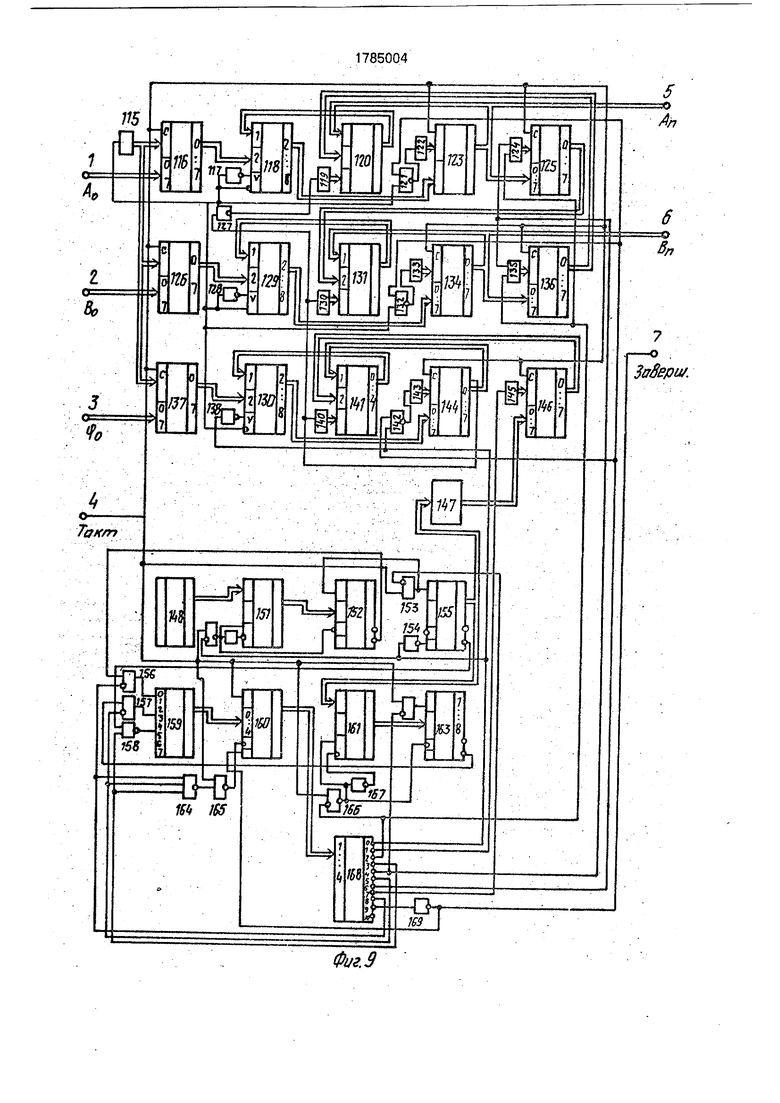

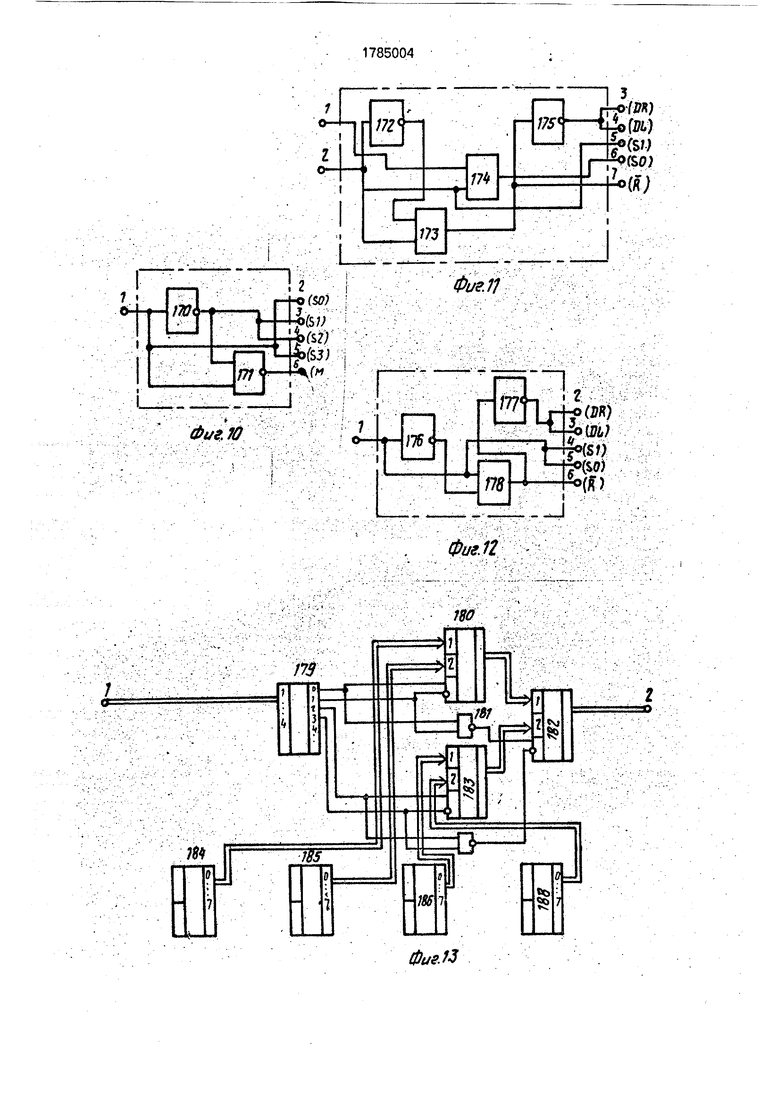

фиг. 9 - схема первого, второго и третьего блоков поворота векторов (подблок второго блока адресов ячеек сигналов изображения);

фиг. 10 - схема формирователя кода для управления арифметикологическим устройством (АЛУ);

фиг. 11 - схема первого формирователя кода для управления регистром;

фиг. 12 - схема второго формирователя кода для управления регистром;

фиг. 13 - схема постоянного запоминающего устройства (ПЗУ) блока поворота векторов;

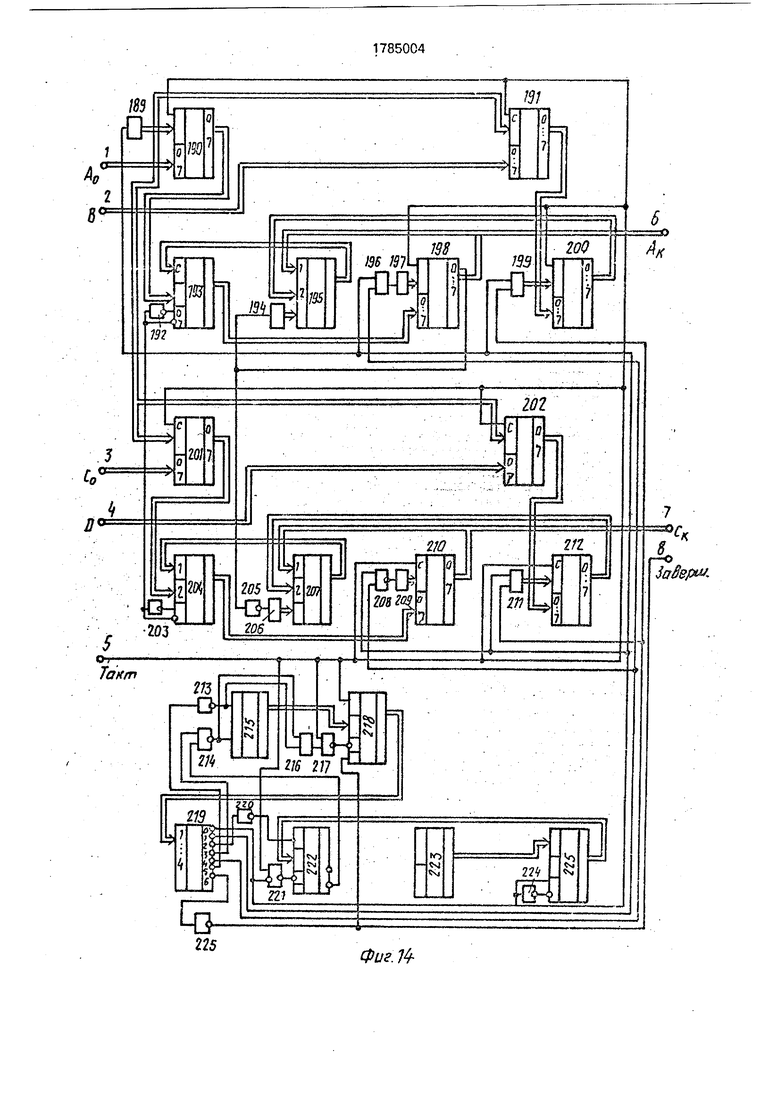

фиг. 14 - схема четвертого блока поворота векторов (подблок второго блока адресов ячеек сигналов изображения);

фиг. 15 - схема формирователя адреса строки параметров;

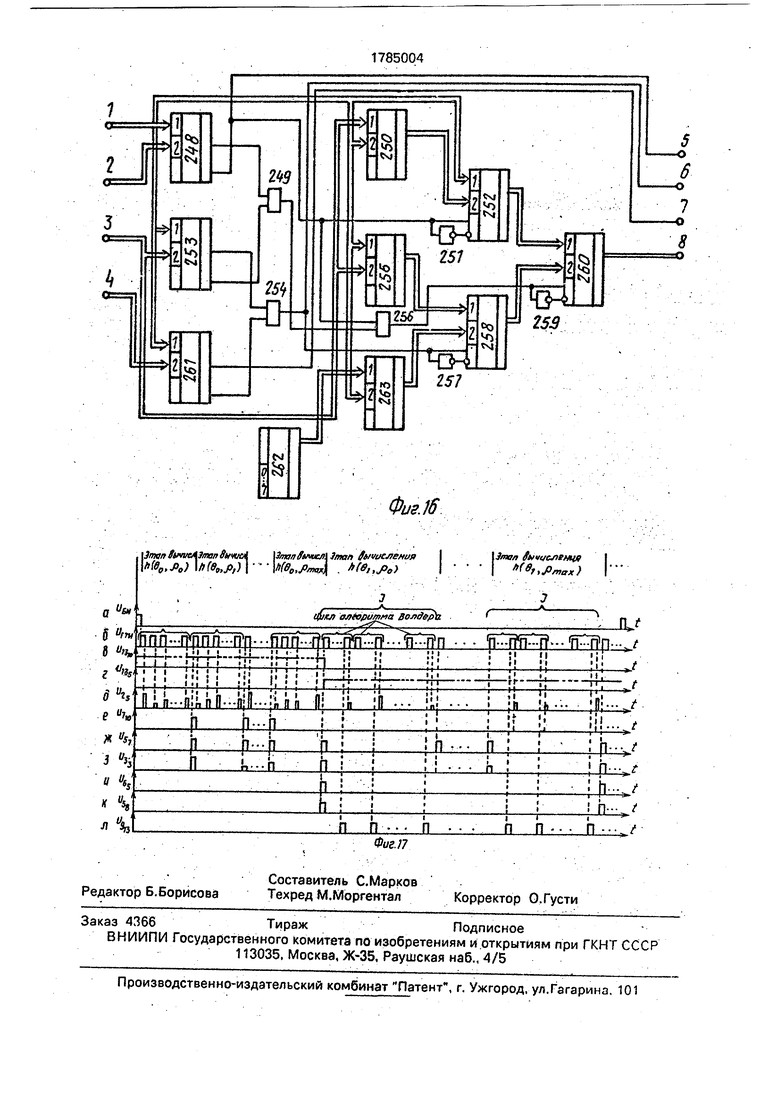

фиг. 16 - схема блока приведения параметра 0 (подблок формирователя адреса строки параметров);

фиг. 17 - эпюры напряжений на выходах блоков устройства.

Предложенное устройство, включает в себя следующие блоки: 1 - оптическая головка; 2 - секция памяти кадра; 3 - накопитель сигналов; 4 - блок памяти параметров; 5 - секция обработки параметров; 6 - формирователь адреса столбца параметров; 7 - первый блок адресов ячеек сигналов изображения; 8 - блок мультиплексоров; 9 - второй блок адресов ячеек сигналов изображения; 10 - блок инициализации; 11 - генератор тактовых импульсов; 12 - элемент задержки; 13 - формирователь адреса строки параметров.

На фиг. 1 и далее непрерывной одиночной линией обозначены одмоканальные электрические связи, непрерывной сдвоенной линией - многоканальные электрические связи; пунктирной линией со стрелкой обозначена оптическая связь между блоками 1 и 2.

Оптическая головка предназначена для формирования действительногоо оптического изображения объекта в плоскости матричного фотоприбора с зарядовой ин- жекцией (МФПЗИ) 14, входящего в состав секции 2 памяти кадра (фиг, 2),

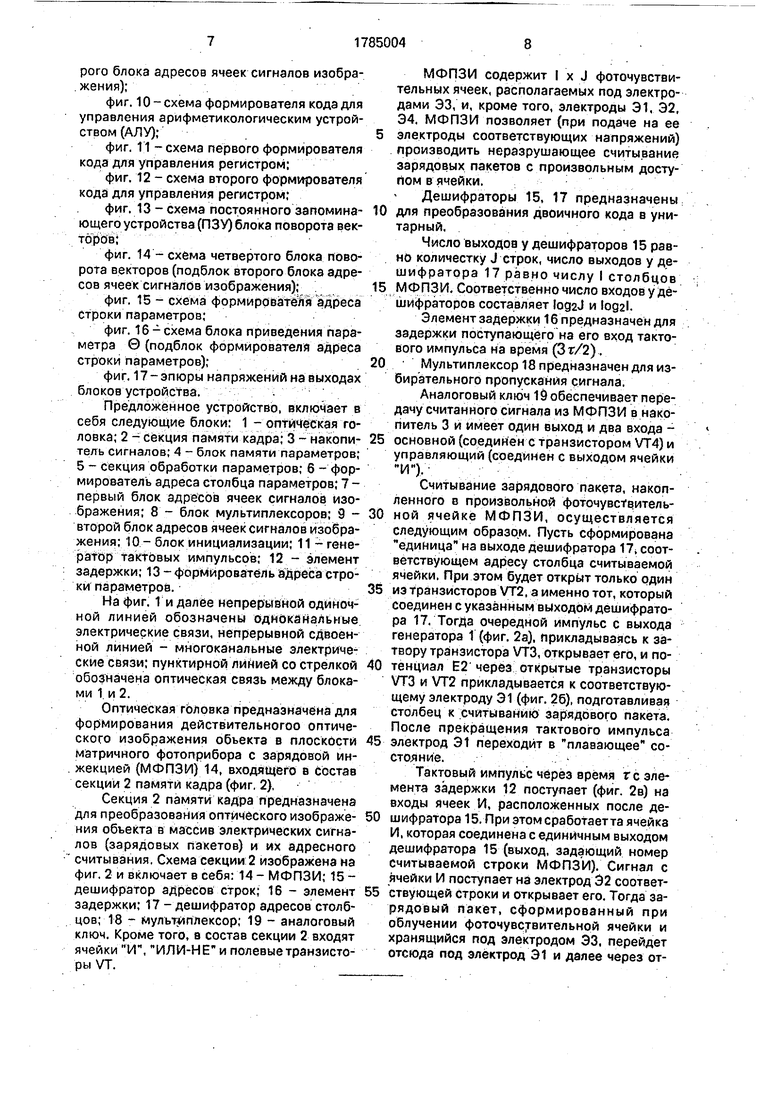

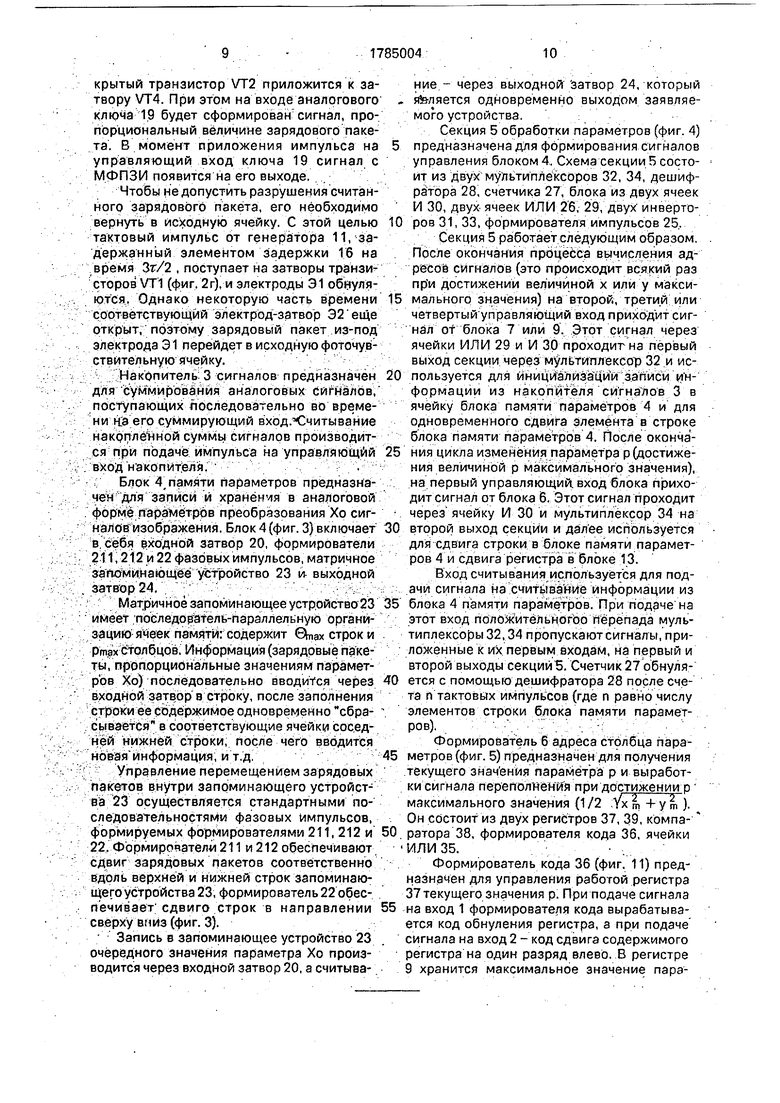

Секция 2 памяти кадра предназначена для преобразования оптического изображения объекта в массив электрических сигналов (зарядовых пакетов) и их адресного считывания, Схема секции 2 изображена на фиг. 2 и включает в себя: 14 - МФПЗИ; 15 - дешифратор адресов строк; 16 - элемент задержки; 17 - дешифратор адресов столбцов; 18 - мультиплексор; 19 - аналоговый ключ. Кроме того, в состав секции 2 входят ячейки И, ИЛИ-НЕ и полевые транзисторы VT.

МФПЗИ содержит I x J фоточувствительных ячеек, располагаемых под электродами ЭЗ, и, кроме того, электроды Э1, Э2, 34. МФПЗИ позволяет (при подаче на ее

электроды соответствующих напряжений) производить неразрушающее считывание зарядовых пакетов с произвольным доступом в ячейки.

Дешифраторы 15, 17 предназначены

для преобразования двоичного кода в унитарный.

Число выходов у дешифраторов 15 равно количестку J строк, число выходов у дешифратора 17 равно числу I столбцов

МФПЗИ. Соответствен но число входов у дешифраторов составляет logaJ и logal.

Элемент задержки 16 предназначен для задержки поступающего на его вход тактового импульса на время (Зт/2).

Мультиплексор 18 предназначен для избирательного пропускания сигнала.

Аналоговый ключ 19 обеспечивает передачу считанного сигнала из МФПЗИ в накопитель 3 и имеет один выход и два входа основной (соединен с транзистором VT4) и управляющий (соединен с выходом ячейки И).

Считывание зарядового пакета, накопленного в произвольной фоточувствительной ячейке МФПЗИ, осуществляется следующим образом. Пусть сформирована единица на выходе дешифратора 17, соответствующем адресу столбца считываемой ячейки. При этом будет открыт только один

из транзисторов VT2, а именно тот, который соединен с указанным выходом дешифратора 17. Тогда очередной импульс с выхода генератора 1 (фиг. 2а), прикладываясь к затвору транзистора VT3, открывает его, и потенциал Е2 через открытые транзисторы VT3 и VT2 прикладывается к соответствующему электроду 31 (фиг. 26), подготавливая столбец к считыванию зарядового пакета. После прекращения тактового импульса

электрод Э1 переходит в плавающее состояние.

Тактовый импульс через время г с элемента задержки 12 поступает (фиг. 2в) на входы ячеек И, расположенных после дешифратора 15. При этом сработаетта ячейка И, которая соединена с единичным выходом дешифратора 15 (выход, задающий номер считываемой строки МФПЗИ). Сигнал с ячейки И поступает на электрод Э2 соответствующей строки и открывает его. Тогда зарядовый пакет, сформированный при облучении фоточувствительной ячейки и хранящийся под электродом ЭЗ, перейдет отсюда под электрод Э1 и далее через открытый транзистор VT2 приложится к затвору VT4. При этом на входе аналогового ключа 19 будет сформирован сигнал, пропорциональный величине зарядового пакета. В момент приложения импульса на управляющий вход ключа 19 сигнал с МФПЗИ появится на его выходе.

Чтобы не допустить разрушения считанного зарядового пакета, его необходимо вернуть в исходную ячейку. С этой целью тактовый импульс от генератора 11, задержанный элементом задержки 16 на время Зг/2 , поступает на затворы транзисторов VT1 (фиг. 2г), и электроды Э1 обнуляются. Однако некоторую часть времени соответствующий электрод-затвор Э2 еще открыт, поэтому зарядовый пакет из-под электрода Э1 перейдет в исходную фоточувствительную ячейку.

Накопитель 3 сигналов предназначен для суммирования аналоговых сигналов, поступающих последовательно во времени на его суммирующий входХ читывание накопленной суммы сигналов производится при подаче импульса на управляющий вход накопителя.

Блок 4, памяти параметров предназначен для записи и хранения в аналоговой форме параметров преобразования Хо сигналов изображения. Блок 4 (фиг. 3} включает в себя входной затвор 20, формирователи 211,212 и 22 фазовых импульсов, матричное запоминающее устройство 23 и- выходной затвор 24.

Матричное запоминающее устройство 23 имеет последователь-параллельную организацию ячеек памяти: содержит Эт9 строк и Ртах столбцов. Информация (зарядовые пакеты, пропорциональные значениям параметров Хо) последовательно вводится через входной затвор в строку, после заполнения строки ее содержимое одновременно сбрасывается в соответствующие ячейки соседней нижней строки, после чего вводится новая информация, и т д

Управление перемещением зарядовых пакетов внутри запоминающего устройства 23 осуществляется стандартными последовательностями фазовых импульсов, формируемых формирователями 211, 212 и 22. Формиргшателм 211 и 212 обеспечивают сдвиг зарядовых пакетов соответственно вдоль верхней и нижней строк запоминающего устройства 23, фо рмиро вател ь 22 обес- печивает сдвиго строк в направлении сверху вниз (фиг. 3).

Запись в запоминающее устройство 23 очередного значения параметра Хо производится через входной затвор 20, а считывание - через выходной затвор 24, который , является одновременно выходом заявляемого устройства

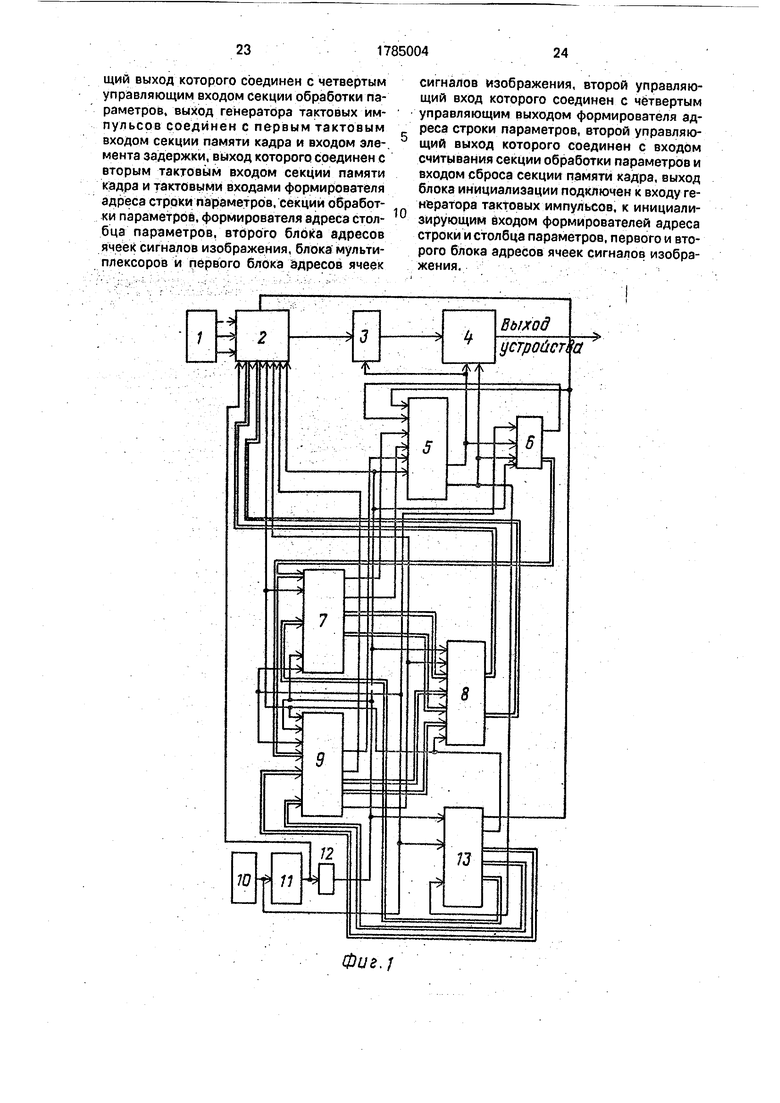

Секция 5 обработки параметров (фиг 4) 5 предназначена для формирования сигналов управления блоком 4. Схема секции 5 состоит из двух мультиплексоров 32, 34, дешифратора 28, счетчика 27, блока из двух ячеек И 30, двух ячеек ИЛИ 26, 29, двух инверто10 ров 31, 33, формирователя импульсов 25.

Секция 5 работает следующим образом После окончания процесса вычисления адресов сигналов (это происходит всякий раз при достижении величиной х или у макси5 мального значения) на второй, третий или четвертый управляющий вход приходит сигнал от блока 7 или 9. Этот сигнал через ячейки ИЛИ 29 и И 30 проходит на первый выход секции через мультиплексор 32 и ис0 пользуется для инициализации записи информации из накопителя сигналов 3 в ячейку блока памяти параметров 4 и для одновременного сдвига элемента в строке блока памяти параметров 4. После оконча5 ния цикла изменения параметра р (достижения величиной р максимального значения), на первый управляющий, вход блока приходит сигнал от блока 6. Этот сигнал проходит через ячейку И 30 и мультиплексор 34 на

0 второй выход секции и далее используется для сдвига строки в блоке памяти параметров 4 и сдвига регистра в блоке 13.

Вход считывания используется для подачи сигнала на считывание информации из

5 блока 4 памяти параметров. При подаче на этот вход положительногоо перепада мультиплексоры 32,34 пропускают сигналы, приложенные к их первым входам, на первый и второй выходы секции В. Счетчик 27 обнуля0 ется с помощью дешифратора 28 после счета п тактовых импульсов (где п равно числу элементов строки блока памяти параметров)

Формирователь 6 адреса столбца пара5 метров (фиг. 5) предназначен для получения текущего значения параметра р и выработки сигнала переполнения при достижении р максимального значения (1/2 Yxm+ym ). Он состоит из двух регистров 37, 39, компа-

0 ратора 38, формирователя кода 36, ячейки ИЛИ 35.

Формирователь кода 36 (фиг. 11) предназначен для управления работой регистра 37 текущего значения р. При подаче сигнала

5 на вход 1 формирователя кода вырабатывается код обнуления регистра, а при подаче сигнала на вход 2 - код сдвига содержимого регистра на один разряд влево. В регистре 9 хранится максимальное значение параметра р: pmax 1 /2 х т + у т . Компаратор 38 служит для контроля достижения максимального значения параметром р.

Формирователь 6 адреса столбца параметров работает следующим образом: инициализирующий сигнал обнуляет регистр 37 и устанавливает начальное состояние схемы. Всякий раз при поступлении сигнала от блока 5 на вход 62 управления сдвигом происходит сдвиг содержимого регистра 37 на один разряд влево (вырабатывается очередное значение р), а при поступлении сигнала на обнуляющий вход 63 происходит обнуление регистра 37 (цикл изменения р возобновляется).

Первый блок 7 адресов ячеек сигналов изображения (фиг. 6) предназначен для вычисления текущих значений кодов адресов ячеек секции памяти кадра в случае, когда значение параметра ©кратно я/2 и, кроме того, блок 7 обеспечивает выдачу управляющих сигналов в блок 5.

Блок 7 (фиг. 6) состоит из шести регистров 39, 40.54,55.60,61, трех мультиплексоров 42,46.50, трех формирователей кода 47, 53, 59, двух компараторов 56, 62, одногоо арифметико-логического устройства (АЛУ) 48, пяти ячеек ИЛИ (блок из трех ячеек 44, 52,58), шести ячеек И (блик из четырех ячеек 43, 51, 57), трех инверторов , 45, 49.

Формирователь 47 кода (фиг. 10) предназначен для управления работой АЛУ 48.

Формирователи 53 и 59 кода (фиг. 11) предназначены для управления работой регистров соответственно 54 и 60.

Регистры 39. 40, 55. 61 предназначены для хранения и выдачи констант соответственно хт/2, ут/2, ут, хт. В регистрах 60 и 54 формируются текущие значения соответственно х, у.

Компараторы 62 и 56 служат для контроля достижения величинами х и у своих максимальных значений. Мультиплексоры 42, 46, 50, в зависимости от величины 0, подключают к выходу блока сигналы от различных схем вычисления сигналов.

Первый блок 7 адресов ячеек сигналов изображения работает следующим образом. Инициализирующий сигнал через ячейки ИЛИ 52, 58 поступает соответственно на формирователи 53, 59 кода, в кдторых вырабатываются коды обнуления регистров 54 и 60. При этом схема блока 7 приходит в начальное состояние.

Сигнал от блока 13, поступающий на первый управляющий вход 7z, разрешает работу блока 7 (это происходит, если значение ©кратно я/2 ). На второй управляющий вход (группа входов 7з ... 7е) приходит сигнал от блока 13, который определяет зна

чение ©. Открывается одна из ячеек И блока 43. Далее в блоке 44 элементов ИЛИ вырабатываются сигналы, управляющие АЛУ 48, мультиплексорами 42, 46, 50, реги- страми 54, 60. На информационных выходах 7ц и 7i2 блока, в зависимости от величины е.появляются сигналы:

0- 0 : X - Хт/2 + р; ©° я/2:у ут/2 + р,- п: х - Хт/2 - р, © Злг/2:у-ут/2-р.

Для каждого случая одна из координат

постоянна в течение всего цикла работы блока, а другая изменяется от 0 до максимального значения. По окончании цикла на одном из управляющих выходов 7д или 7ю появляется сигнал переполнения, который

используется для управления накопителем сигналов 3. Значение р с информационного выхода блока 6 поступает на АЛУ 48 через параметрический вход 7.

Блок 8 мультиплексоров (фиг. 7) предназначен для коммутации значений адресов сигналов х и у, поступающих на информационные входы этого блока с первого и второго блоков адресов ячеек сигналов изображения в зависимости от текущих значений параметра ©. Схема блока 8 состоит из двух регистров 67, 71 (в которых записываются соответственно текущие значения х и у), собственно двух мультиплексоров 64, 69, двух формирователей 66-, 70 кодов, двух инверторов 63, 68 и ячейки И-НЕ 65. Формирователи кодов 66, 70 (фиг. 12) предназначены для управлений записью информации в регистры 67, 71.

Блок 8 работает следующим образом.

На информационные входы 8з ... 8е поступают значения х и у, вычисленные в блоках 7 и 9, и далее эти значения проходят на мультиплексоры 64, 69. Управляющий вход 8 соединен с первым управляющим

выходом блока 13. Если текущее значение ©кратно я/2 , то с первого управляющего выхода блока 13 снимается логический О, который подается на вход ячейки И-НЕ 65 и на управляющие входы мультиплексоров

64, 69. По сигналу логического О мультиплексоры 64, 69 пропустят текущие значения х и у, вычисленные в блоке 7. Выходной сигнал ячейки ИЛИ поступает на формирователи 66,70, где формируются коды, разре шающие запись значений х и у с выхода мультиплексоров 64, 69 в регистры 67, 71.

При ©, не кратном я/2 , на управляющий вход 8f поступает логическая 1, что приводит к тому, что мультиплексоры 64, 69

коммутируют значения х и у, поступающие от блока 9. Эти значения запишутся в регистры 67, 71 при поступлении на разрешающий вход 82 сигнала завершения вычислений с первого управляющего выхо- да блока 9.

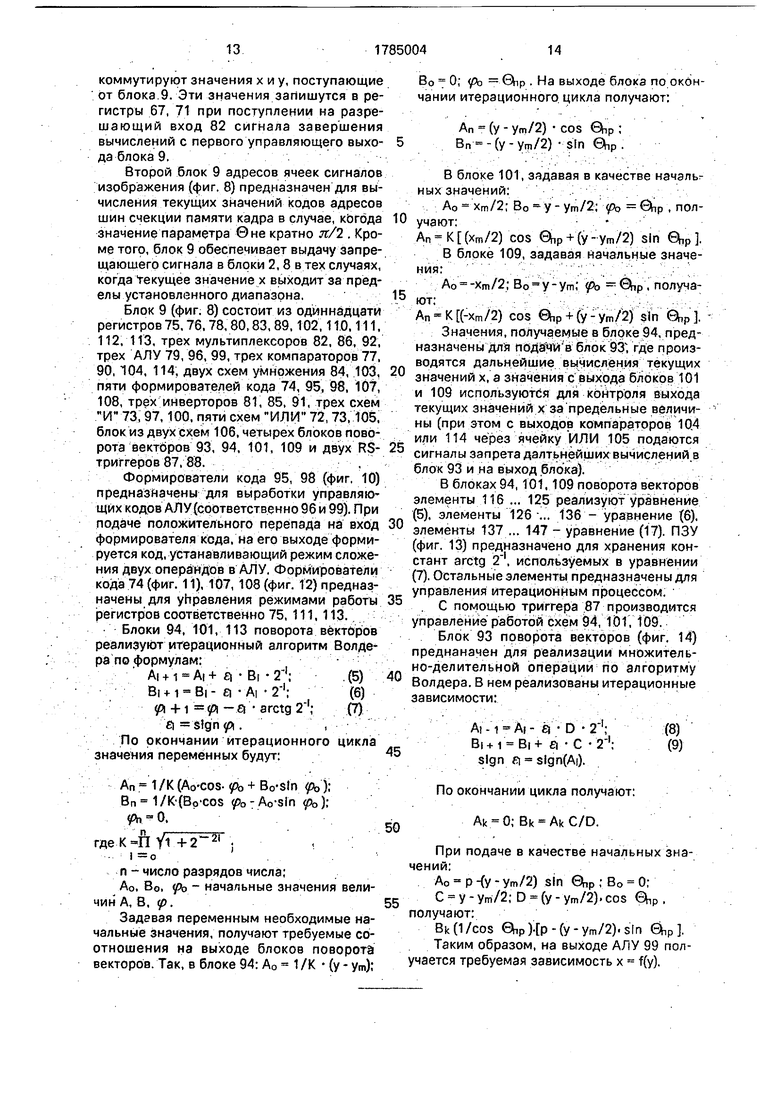

Второй блок 9 адресов ячеек сигналов изображения (фиг. 8) предназначен для вычисления текущих значений кодов адресов шин счекции памяти кадра в случае, когода значение параметра ©не кратно я/2 . Кроме того, блок 9 обеспечивает выдачу зэпре- щаюшего сигнала в блоки 2,8 в тех случаях, когда текущее значение х выходит за пределы установленного диапазона.

Блок 9 (фиг. 8) состоит из одиннадцати регистров 75,76, 78,80,83, 89,102,110.111, 112, 113, трех мультиплексоров 82, 86, 92, трех АЛУ 79, 96, 99, трех компараторов 77, 90,104, 114, двух схем умножения 84, 103, пяти формирователей кода 74, 95, 98, 107, 108, трех инверторов 81, 85, 91, трех схем И 73, 97,100, пяти схем ИЛИ 72, 73, 105. блок из двух схем 106, четырех блоков поворота векторов 93, 94, 101, 109 и двух RS- триггеров 87, 88.

Формирователи кода 95, 98 (фиг, 10) предназначены для выработки управляю- щих кодов АЛУ (соответственно 96 и 99). При подаче положительного перепада на вход формирователя кода, на его выходе формируется код, устанавливающий режим сложения двух операндов в АЛУ. Формирователи кода 74 (фиг. 11), 107, 108 (фиг. 12) предназначены для управления режимами работы регистров соответственно 75, 111,113.

Блоки 94, 101, 113 поворота векторов реализуют итерационный алгоритм Волде- ра по формулам:

Аи-1 - AI + Ј| Bi

(5) (6) (7)

В| + 1 В| - Ј| AI fl +1 ф( - ei arctg

fii f.

По окончании итерационного цикла значения переменных будут:

An 1 /К (АО-COS- ро + Bo-sln фо ); Вп 1/K-(Boicos po-Ao-sln po}; ь 0,

где К П Yl .

- о

п - число разрядов числа;

АО, Во, ро начальные значения величин А, В, (р.

Задавая переменным необходимые начальные значения, получают требуемые соотношения на выходе блоков поворота векторов Так, в блоке 94: А0 1/К (у - ут);

5

0 5

0 5

0 5

0

Во 0, ро - Ohp . На выходе блока по окончании итерационного цикла получают:

An (у - ут/2) cos ©пр ;

Вп - (у - Ут/2) Sin Ohp .

В блоке 101, задавая в качестве начальных значений.

АО Хт/2; Во у - ут/2; ро 6hp , получают:An K(xm/2) cos 6hp + (y-ym/2) sin 0пр.

В блоке 109, задавая начальные значения:

Ао -Хт/2; В0 у-ут; ро - ©пр . получают:An K(-Xm/2) cos ©пр + (у-Ут/2) sin Ghp.

Значения, получаемые в блоке 94, предназначены для подачи в блок 93Ч, где производятся дальнейшие вычисления текущих значений х, а значения с выхода блоков 101 и 109 используются для контроля выхода текущих значений х за предельные величины (при этом с выходов компараторов 104 или 114 через ячейку ИЛИ 105 подаются сигналы запрета далтьнейших вычислений в блок 93 и на выход блока).

В блоках 94,101,109 поворота векторов элементы 116 ... 125 реализуют уравнение (5), элементы 126 ... 136 - уравнение (б), элементы 137 ... 147 - уравнение (17). ПЗУ (фиг. 13) предназначено для хранения констант arctg , используемых в уравнении (7). Остальные элементы предназначены для управления итерационным процессом.

С помощью триггера 87 производится управление работой схем 94, 101, 109.

Блок 93 поворота векторов (фиг. 14) преднаначен для реализации множитель- но-делительной операции по алгоритму Волдера. В нем реализованы итерационные зависимости:

At -1 - AI - $ D Вц-1 Bi + я С sign FI slgn(Ai).

По окончании цикла получают: Ak 0; Bk Ak C/D.

(8) (9)

При подаче в качестве начальных значений:

АО р ЧУ - Ут/2) sin бпр ; В0 0; С у - ут/2; D (у - ут/2). cos ©пр , получают:

Bk(1/cos 0np)(y-ym/2).sln ©пр

Таким образом, на выходе АЛУ 99 получается требуемая зависимость х f(y).

Поскольку при вычислениях в блоке 93 происходит сокращение на величину (у - ут/2), необходимо проверить ее на равенство нулю, что и производится в компараторе 90 (фиг. 8). Если (у - ут/2) - 0. в соответствующие схемы выдаются альтернативные величины.

Контроль за тем, чтобы операнды блока 93 не выходили за допустимые значения, производится с помощью блоков 101,109 и компараторов 104,114.

Регистры, использованные в блоке 9, имеют назначение: 75 -хранение и обработка текущего значения у; 76 - хранение константы упа; 80 - хранение константы 1; 78 - хранение константы ут/2, 83 - хранение константы 1/К; 89 - хранение константы 0; 102 - хранейие константы хт/2; 112 - хранение константы К; 113 - хранение и обработка выходной величины блока 101; 110- хранение константы -хт/2; 111 - хранение и обработка выходного значения переменной блока 109.

Компаратор 77 служит для контроля выполнения условия у ут. При нарушении этого условия, на выход 9э выдается соответствующий сигнал и в регистре 75 устанавливается начальное значение переменной у. А/1У 79 постоянно работает в режиме вычитания.

Блок 9 работает следующим образом. Сигнал с инициализирующего входа 93, проходя через ячейки ИЛИ 72, поступает на вход 1 формирователя кода 74, где вырабатывается код обнуления регистра 75. Таким образом, схема приводится в исходное положение. Сигнал с выхода элемента 72 поступает также в ячейку ИЛИ 73, откуда далее на вход S триггера 87, который устанавливает рабочий режим блоков 94, 101, 109 поворота векторов.

При (у -Ут/2) & 0 (это условие проверяется компаратором 90) происходит формирование начальных значений:

АО - (1 /К)-(У Ут/2): Во - 0: ро Ohp ,

которые подаются соответственно на входы 1, 2, 3 блока поворота векторов 94;

А О

хт/2; Во - у - ут/2; fb-®np,

которые подаются соответственно на входы 1,2,3 блока поворота векторов 101;

IIН|

АО - -хт/2; В0 - у - ут/2: рь Qip.

которые подаются соответственно на входы 1, 2, 3 блока поборота векторов 109.

0

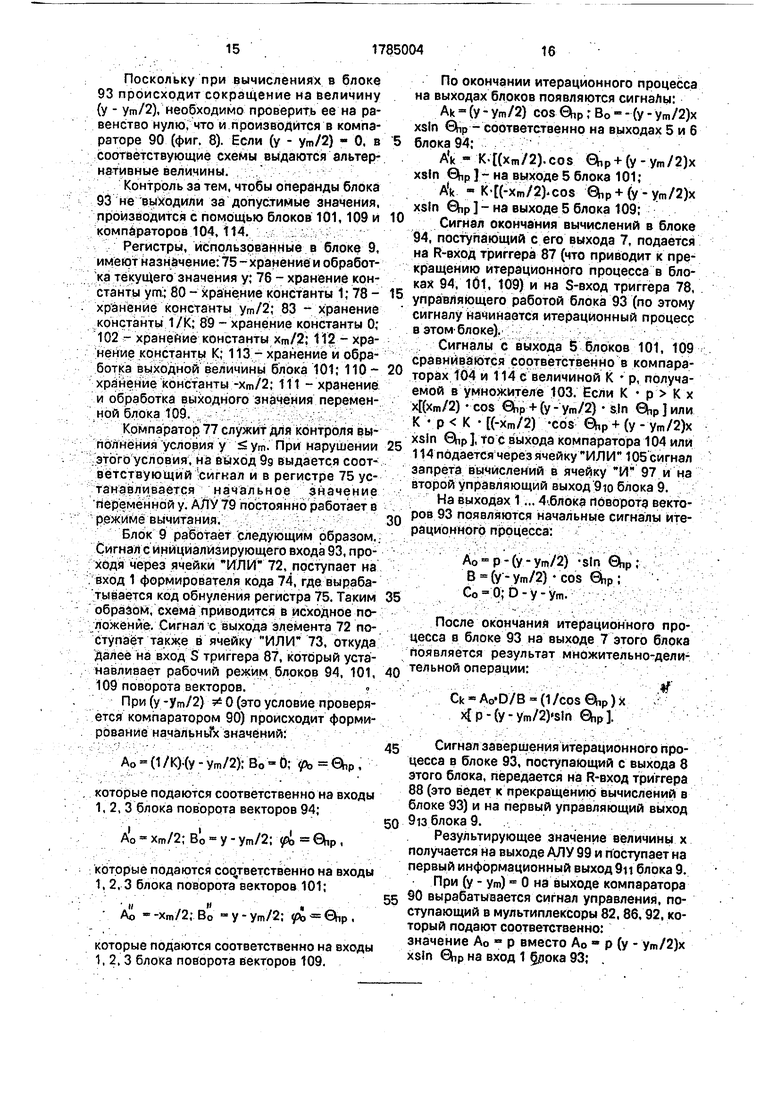

По окончании итерационного процесса на выходах блоков появляются сигналы:

Ak - (У - Ут/2) COS ®пр Г Во - - (у - Ут/2)х

xsln ip - соответственно на выходах 5 и 6 блока 94;

A k - K-(xm/2).cos Ghp + (y-ym/2)x xsln Qip - на выходе 5 блока 101;

Afk - K-(-Xm/2)COS &np + (у - ym/2)x xsln Qnp - на выходе 5 блока 109;

Сигнал окончания вычислений в блоке 94, поступающий с его выхода 7, подается на R-вход триггера 87 (что приводит к прекращению итерационного процесса в блоках 94, 101, 109) и на S-вход триггера 78, 5 управляющего работой блока 93 (по этому сигналу начинается итерационный процесс в этом блоке).

Сигналы с выхода 5 блоков 101, 109 сравниваются соответственно в компараторах 104 и 114 с величиной К р, получаемой в умножителе 103. Если К р К х хГ(хт/2) cos Qnp + (у - ут/2) sin Ghp J или К р К (-Хт/2) -COS 6hp + (у - ут/2)х xsln On J, TO с выхода компаратора 104 или 114 подается через ячейку ИЛИ 105 сигнал запрета вычислений в ячейку И 97 и на второй управляющий выход 9ю блока 9.

На выходах 1... 4 блока поворота векторов 93 появляются начальные сигналы итерационного процесса:

0

5

0

АО р - (у - Ут/2) Sin В - (у - Ут/2) COS 6h

Со - 0; D - у - ут.

ip ,

После окончания итерационного процесса в блоке 93 на выходе 7 этого блока появляется результат множительно-дели- тельной операции:

Ck-A0 D/B (1/cosGhp)x 4 Р - (У ym/2) sln Qhp.

If

Сигнал завершения итерационного процесса в блоке 93, поступающий с выхода 8 этого блока, передается на R-вход триггера 88 (это ведет к прекращению вычислений в блоке 93) и на первый управляющий выход

91зблока9.

Результирующее значение величины х

получается на выходе АЛУ 99 и поступает на

первый информационный выход 9ц блока 9.

При (у - ут) 0 на выходе компаратора

90 вырабатывается сигнал управления, поступающий в мультиплексоры 82. 86,92, который подают соответственно: значение АО - р вместо А0 - р (у - ут/2)х xsin 6hp на вход 1 §лока 93;

значение D 1 вместо D у - ym на вход 4 блока 93;

значение А0 1 /Квместо Ао(1 /К) (у-ут/2) на вход 2 блока 94.

При этом на первом информационном выходе блока 9 формируется сигнал:

х (хт/2) + (p/cos 6hp).

Сигналы, поступающие со второго управляющего входа (группа входов 9е, 9, 9а) блока 9 в блок 106 ячеек ИЛИ, используются для управления знаками АЛУ 96, 99 в зависимости от номера квадранта, в котором находится значение 0.

Работа схемы возобновляется всякий раз при поступлении сигналов обнуления или сдвига на регистр 75.

Блок 10 инициализации (БИ) формирует одиночный импульс для запуска генератора 11 и приведения в исходное состояние блоков устройства.

Генератор 11 тактовых импульсов (ГТИ) обеспечивает формирование тактовых импульсов, синхронизирующих работу устройства.

Элемент 12 задержки предназначен для задержки поступающего на его вход тактового импульса на время т.

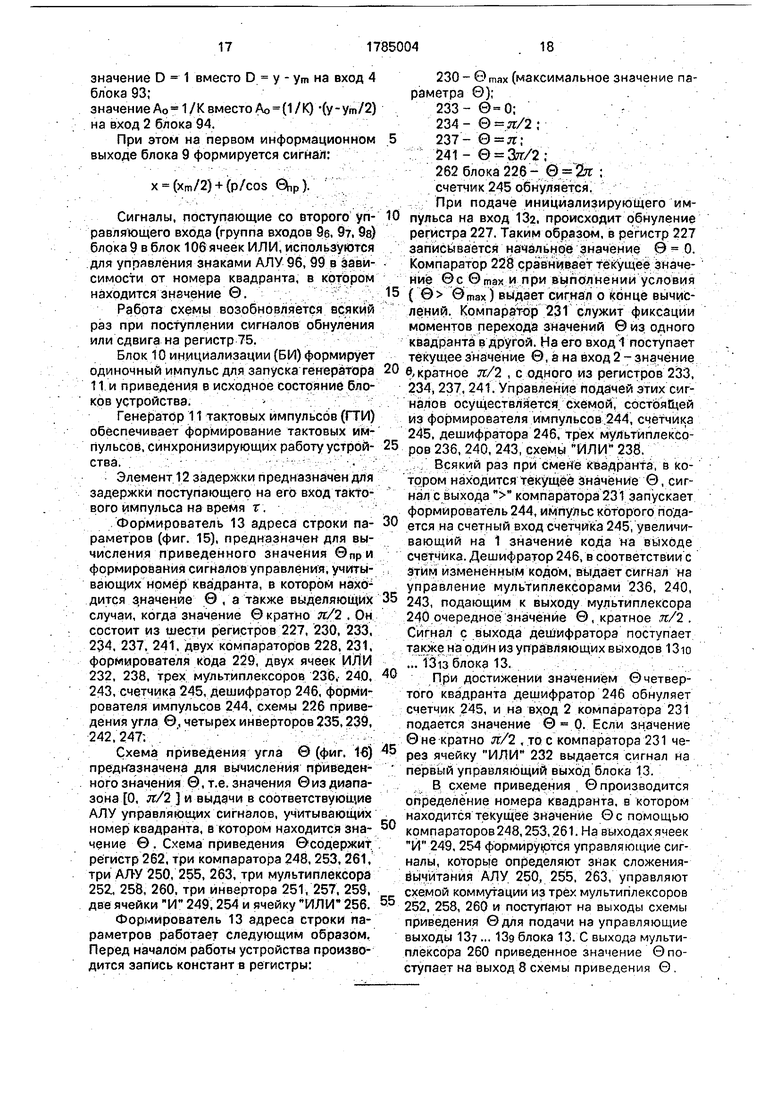

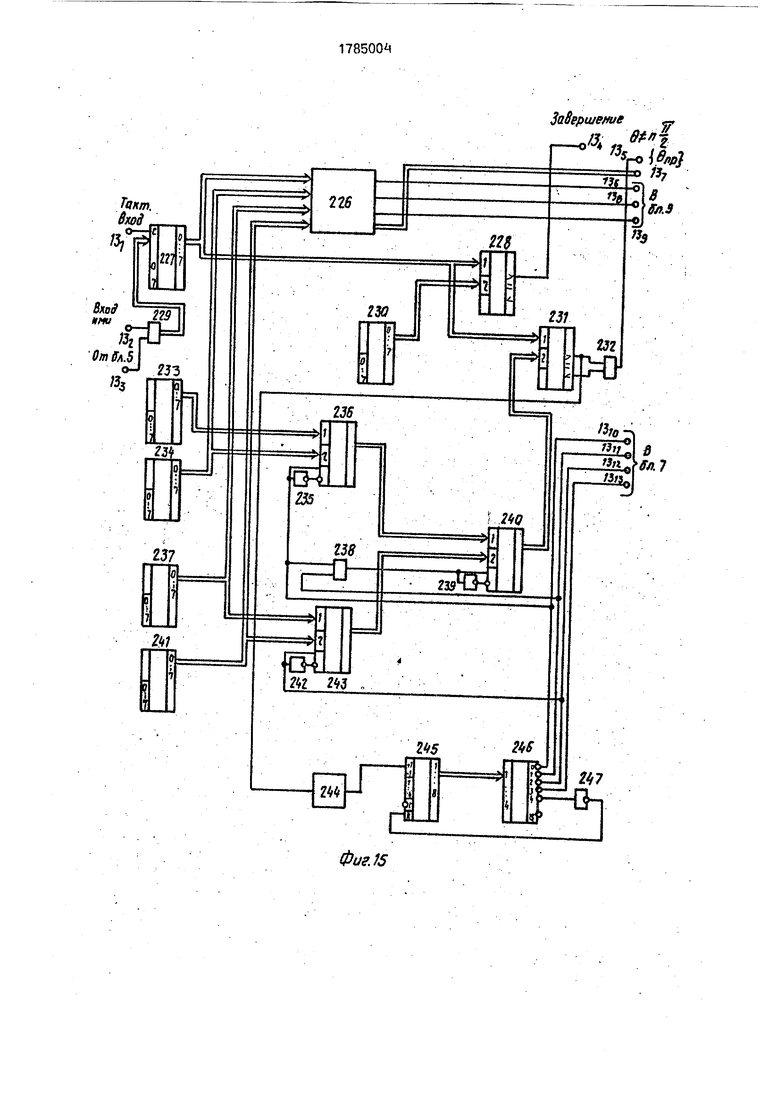

Формирователь 13 адреса строки параметров (фиг. 15), предназначен для вычисления приведенного значения ©при формирования сигналов управления, учитывающих номер квадранта, в котором находится значение 0 , а также выделяющих случаи, когда значение 0 кратно л/2 . Он состоит из шести регистров 227, 230, 233, 234. 237, 241, двух компараторов 228, 231, формирователя кода 229, двух ячеек ИЛИ 232, 238. трех мультиплексоров 236, 240, 243, счетчика 245, дешифратор 246, формирователя импульсов 244, схемы 226 приведения угла 0, четырех инверторов 235,239, 242,247;

Схема приведения угла 0 (фиг. 16} предназначена для вычисления приведенного значения 0,т.е.значения ©издиапазона 0, л/2 и выдачи в соответствующие АЛУ управляющих сигналов, учитывающих номер квадранта, в котором находится значение © . Схема приведения ©содержит регистр 262, три компаратора 248, 253, 261, три АЛУ 250, 255, 263, три мультиплексора 252, 258, 260, три инвертора 251, 257, 259, две ячейки И 249. 254 и ячейку ИЛИ 256.

Формирователь 13 адреса строки параметров работает следующим образом. Перед началом работы устройства производится запись констант в регистры:

5

0

5

5

0

5

0

5

0

0

5

230 - © max (максимальное значение параметра ©);

233-0 0;

234-@ л/2; 237- 241- 0 Зя/2;

262 блока 226- 0 ;

счетчик 245 обнуляется.

При подаче инициализирующего импульса на вход 132, происходит обнуление регистра 227. Таким образом, в регистр 227 записывается начальное значение . Компаратор 228 сравнивает текущее значение ©с ©max и при выполнении условия ( 0 ©max) выдает сигнал о конце вычислений. Компаратор 231 служит фиксации моментов перехода значений 0 из одного квадранта в другой. На его вход 1 поступает текущее значение 0, а на вход 2 - значение в, кратное л/2 , с одного из регистров 233, 234,237,241. Управление подачей этих сигналов осуществляется схемой, состоящей из формирователя импульсов 244, счетчика 245, дешифратора 246, трех мультиплексоров 236, 240, 243, схемы ИЛИ 238.

Всякий раз при смене квадранта, в котором находится текущее значение 0, сигнал с выхода компаратора 231 запускает формирователь 244, импульс которого подается на счетный вход счетчика 245, увеличивающий на 1 значение кода на выходе счетчика. Дешифратор 246, в соответствии с этим измененным кодом, выдает сигнал на управление мультиплексорами 236, 240, 243, подающим к выходу мультиплексора 240 очередное значение 0, кратное л/2 . Сигнал с выхода дешифратора поступает также на один из управляющих выходов 13ю ... 13i3 блока 13.

При достижении значением ©четвертого квадранта дешифратор 246 обнуляет счетчик 245, и на вход 2 компаратора 231 подается значение . Если значение ©не кратно л/2 , то с компаратора 231 через ячейку ИЛИ 232 выдается сигнал на первый управляющий выход блока 13.

В схеме приведения ©производится определение номера квадранта, в котором находится текущее значение ©с помощью компараторов 248,253,261. На выходах ячеек И 249, 254 формируются управляющие сигналы, которые определяют знак сложения- вычитания АЛУ 250, 255. 263, управляют схемой коммутации из трех мультиплексоров 252, 258, 260 и поступают на выходы схемы приведения ©для подачи на управляющие выходы 13 ... 13э блока 13. С выхода мультиплексора 260 приведенное значение ©поступает на выход 8 схемы приведения ©

Устройство для преобразования Хо изображения работает следующим образом. Запускающий сигнал Ыби (фиг. 117а) с блока инициализации производит запись констант в соответствующие блоки устройства, запускает ГТИ (фиг. 176) и устанавливает блоки в исходное состояние.

На выходе формирователя 13 адреса столбца параметров появляется начальное значение параметров , приведенное к первому квадранту. Поскольку значение 0 кратно я/2 , для формирования адресов ячеек сигналов изображения используется первый блок адресов ячеек сигналов изображения (блок 7). При этом в блок 7 из блока 13 поступает два управляющих сигнала. Один сигнал (фиг. 17в) прикладывается к блоку 7 чере з первый управляющий вход и сообщает о том, что значение ©кратно я/2 . Другой сигнал прикладывается к блоку 7 чзрез второй управляющий вход и сообщает т том, что значение 0 находится в первом квадранте.

Одновременно с информационного выхода формирователя 6 адреса строки параметров в блок 7 поступает начальное значение параметра р. В блоке 7 происходит последовательное вычисление всех пар значений (xi, yi), удовлетворяющих уравнению (2) при © 0о и р р0. Каждая текущая вычисленная пара значений (xi, yi) поступает в блок мультиплексоров 8, где происходит коммутация кодов х и у на выход блока 8 по управляющему сигналу 1Нз5(Фиг- 17г)с первого управляющего выхода блока 13. С выхода блока 8 мультиплексоров коды адресов ячеек сигналов {х} и {у} поступают в секцию 2 памяти кадра, где они используются для извлечения сигнала из соответствующей ячейки U23 (Фиг. 17д) и пересылки его в накопитель 3 сигналов.

После вычисления всех пар значений (xi, yi), удовлетворяющих значениях параметров 0 ©о и р ро, и пересылки соответствующих этим парам сигналов из секции памяти кадра в накопитель сигналов, появляется сигнал переполнения на первом или втором управляющих выходах блока 7 (фиг. 17е): если ©кратно (я/2) (2п - 1), сигнал появится на первом выходе, а если 0 кратно Я- на втором выходе.

Сигнал переполнения, поступающий в секцию 5 обработки параметров, инициализирует появление управляющего сигнала на первом управляющем выходе блока 5 Us (фиг. 17ж), который используется для записи сигнала, накопленного в накопителе 3 сигналов, в ячейку блока 4 памяти параметров,

соответствующую паре (РО. 0о ) Узз (фиг. 17з), сдвига регистра формирования параметра р из блока б на один разряд влево, а также для установки регистра, задающего

значения х, в блоке 7 в начальное состояние. Таким образом, на вход блока 7 подается очередное значение параметра р pi и возобновляется процесс вычисления значений пар (xi, yi), но уже для значений параметров

р Р1 и 0 0о. Описанный процесс вычисления пар (xi, yi) продолжается до тех пор, пока значения р не превысят максимального: ртах (1 /2) Ух т + у jj, .

При р ртах появится сигнал на управляющем выходе блока 6 Убз (фиг. 17и), который поступает в блок 5, а затем со второго управляющего выхода блока 5 Uss (фиг. 17к) - в блок памяти параметров 4 для сдвига

строки матрицы параметров, в формирователь 13 адреса строки параметров для сдвига на один разряд влево регистра формирования параметров ©ивформирователь б адреса столбца параметров для

Установки регистра формирования параметра р в исходное положение. Аналогичным образом работает устройство во всех случаях, когда значение 0 кратно я/2 .

Если значение 0 не кратно я/2 , то

формирование адресов ячеек сигналов изображения производится в блоке 9. При этом из формирователя адресов строки параметров в блок 9 поступают: по первому управляющему входу - сигнал о том, что значение

©не кратно я/2 Ui35 (фиг. 17г); по второму управляющему входу - сигнал о номере квадранта, в котором находится текущее значение 0; по второму параметрическому входу - значение параметра 0, приведенное к первому квадранту. Кроме того, на первый параметрический вход блока 9 поступает текущее значение параметра р.

В блоке 9 вычисление адресов ячеек сигналов изображения происходит следующим

образом. При поступлении управляющего сигнала из блока 13, сообщающего о том, что 0 не кратно я/2 , происходит обнуление регистра 75, который формирует текущее значение у. Это значение, наряду со

значениями параметров р (из блока 6) и приведенного значения параметров 0(из блока 13), используется для формирования начальных условий работы схем 93, 94, 101, 109 реализации алгоритма Волдера.

По окончании итерационных процессов в блоках 93,94,101.109 происходит формирование текущего значения х на первом информационном выходе 9ц блока 9. Сигнал окончания итерационных процессов подается на первый управляющий выход блока 9

Usi3 (фиг. 17л), а также используется для сдвига на один разряд регистра - задатчика 75 значений у и для установки блоков 93,94, 101. 109 поворота векторов в исходное состояние. Сигнал завершения с первого управляющего выхода блока 9 поступает через блок 8 мультиплексоров в секцию 2 памяти кадра, где используется для открытия аналогового ключа 19, пропускающего на выход секции памяти кадра сигнал, считанный из ячейки с адресами хтек и утек. При ©тек , на кратном л/2 , блок 8 мультиплексоров пропускает для управления считыванием из секции 2 памяти кадра сигналы, идущие от блока 9, а при в, кратном л/2 , - от блока 7. Управление коммутацией осуществляется с помощью сигнала, поступающего с первого управляющего выхода блока 13и1з5(фиг. 17г).

Последовательный перебор возможных значений параметра ртек производится так же, как это описано для случая, когда 0 кратно л/2 : при р ртах происходит установка регистра - задатчика параметра р из блока 6 в начальное состояние и сдвиг регистра - зэдатчика параметра виз блока 13 на 1 разряд влево, т.е. обрабатывается очередное значение 0, и т.д.

При ВЫПОЛНеНИИ УСЛОВИЯ ©тек ©max .

которое проверяется в компараторе 228 блока 13, на его втором управляющем выходе появляется сигнал завершения. Этот сигнал подается в секцию 2 памяти кадра для обнуления ячеек МФПЗИ (подготовки к обработке очередного кадра) и в секцию 5 обработки параметров, где используется для управления работой мультиплексоров 32 и 34, Через эти мультиплексоры тактовые импульсы от ГТИ поступают на выходы секции 5, обеспечивая сдвиг и считывание элементов, записанных в блоке 4 памяти параметров.

Таким образом, будет получено преобразование Хо изображения, спроецированного на матрицу МФПЗИ.

Для обработки в устройстве нового кадра изображения необходимо подать очередной импульс из блока инициализации.

Формула изобретения Устройство для преобразования Хо изображения, содержащее секцию памяти кадра, блок памяти параметров, секцию обработки параметров, первый блок адресов ячеек сигналов изображения, отличающееся тем, что, с целью повышения точности и упрощения, устройство содержит оптическую головку, выход которой оптически соединен с информационным выходом секции памяти кадра, накопитель

сигналов, информационный вход которого подключен к выходу секции памяти кадра, выход накопителя сигналов подключен к информационному входу блока памяти пара- 5 метров, блок мультиплексоров, генератор тактовых импульсов, формирователи адреса строки и столбца параметров, второй блок адресов ячеек сигналов изображения, элемент задержки и блок.инициализации, при 0 этом первый выход секции обработки параметров соединен с управляющим входом накопителя сигналов, входом записи блока памяти параметров и входом управления сдвигом формирователя адреса столбца па5 раметров, управляющий выход которого подключен к первому управляющему входу секции обработки параметров, второй и третий управляющие входы которой соединены соответственно с первым и вторым управля0 ющими выходами первого блока адресов ячеек сигналов изображения, второй выход секции обработки параметров соединен с входами управления сдвигом блока памяти параметров, формирователя адреса строки

5 параметров и обнуляющим входом формирователя адреса столбца параметров, информационный выход формирователя адреса столбца параметров подключен к первому параметрическому входу второго

0 блока адресов ячеек сигналов изображения и параметрическому входу первого блока адресов ячеек сигналов изображения, первый и второй информационные выходы которого соединены соответственно с первым

5 и вторым информационными входами блока мультиплексоров, выходы которого соединены с адресными входами секции памяти кадра, первый управляющий вход которой соединен с перЁыми управляющими входа0 ми первого и второго блоков адресов ячеек сигналов изображения, управляющим входом блока мультиплексоров и первым управляющим выходом формирователя адреса строки параметров, информацион5 ный и третий управляющий выходы которого подключены соответственно к второму параметрическому и второму управляющему входам второго блока адресов ячеек сигналов изображения, первый и второй

0 информационные выходы которого соединены соответственно с третьим и четвертым информационными входами блока мультиплексоров, разрешающий вход которого соединен с первым управляющим выходом

5 второго блока адресов ячеек сигналов изображения и с вторым управляющим входом секции памяти кадра третий управляющий вход которой соединен с вторым управляющим выходом второго блока адресов ячеек сигналов изображения, третий управляющий выход которого соединен с четвертым управляющим входом секции обработки параметров, выход генератора тактовых импульсов соединен с первым тактовым входом секции памяти кадра и входом эле-, мента задержки, выход которого соединен с вторым тактовым входом секции памяти кадра и тактовыми входами формирователя адреса строки параметров, секции обработки параметров, формирователя адреса столбца параметров, второго блока адресов ячеек сигналов изображения, блока мультиплексоров и первого блока адресов ячеек

0

сигналов изображения, второй управляющий вход которого соединен с четвертым управляющим выходом формирователя адреса строки параметров, второй управляющий выход которого соединен с входом считывания секции обработки параметров и входом сброса секции памяти кадра, выход блока инициализации подключен к входу генератора тактовых импульсов, к инициализирующим входом формирователей адреса строки и столбца параметров, первого и второго блока адресов ячеек сигналов изображения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации | 1989 |

|

SU1741123A1 |

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

| КРЕМНИЕВЫЙ МУЛЬТИПЛЕКСОР | 2015 |

|

RU2602373C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| Буферное запоминающее устройство | 1990 |

|

SU1833918A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ИЗОБРАЖЕНИЯ ОБЪЕКТА | 1992 |

|

RU2054196C1 |

| Пульт учащегося для устройства обучения языкам | 1985 |

|

SU1354235A1 |

| Устройство для отображения информации | 1988 |

|

SU1501135A1 |

| Устройство для формирования гистограммы изображения | 1990 |

|

SU1826081A1 |

| Спектроанализатор | 1979 |

|

SU866494A1 |

Изобретение относится к области кибернетики и вычислительной техники и может быть использовано при обработке и распознавании изображений объектов. Цель изобретения состоит в повышении точности преобразования Хо изображения и упро шении устройства. Цель достигается за счет использования аналоговой формы представления обрабатываемых сигналов изображения при цифровом управлении процессами обработки с помощью специализированных вычислительных и управляющих микросхем. Схема устройства включает в себя оптическую головку и сопряженную с ней оптически секцию памяти кадра, блок памяти параметров, секцию обработки параметров, блоки адресов ячеек сигналов изображения, накопитель сигналов, блок мультиплексоров, генератор тактовых импульсов, формирователи адреса строки и столбца параметров, элемент задержки и блок инициализации. 17 ил.

Фиг./

Jxod сброса.

U

О

2j

faffa.1t Ог

6л.8

Ъа

4b

От i о Л.

Вход iswtitfffjrt/yrttai/

33

J

Фие.4Фиг 5

jfj От fa б

1785004

U-ut

WQ

W)098a

Фм.3

июзеа

225

Фиг. №

fl 3

-Т О

$

ее

3men tvweAiman Л

,„) 1(в„ j Мвъ&нА

w

Эаюя0ичисл Зтап ftivacjieftua h(8t,

Зтап favt/сленцв 9t,J3max)

| Реальность и прогнозы искусственного интеллекта | |||

| М., Мир, 1987, с | |||

| Прибор для массовой выработки лекал | 1921 |

|

SU118A1 |

| Harahare К, Marugama Т, Uchljama Т | |||

| High - Speed Hagh transform processor and № application To automatic Inspection and measurement | |||

| Proc | |||

| IEEE Tht | |||

| Conf | |||

| Rob and Autan | |||

| San Francisco, Calif | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| Устройство для автоматического пуска в ход регистрирующих механизмов в самопишущих приборах | 1925 |

|

SU1954A1 |

Авторы

Даты

1992-12-30—Публикация

1990-06-07—Подача