Изобретение относится к цифровой вычислительной технике, к средствам визуального отображения графической информации и может быть иснользовано для цостроения быстродейству1оц.1их систем памяти для растровых графических систем отображения информации в реальном времени.

Цель изобретения - повышение быстродействия запоминающего устройства с многоформатным доступом к дапным путем обеспечения возможности обращения в течение одного цикла обращения к элементам памяти к произвольному, заранее не предопределенному фрагменту данных, при условии, что элементы фрагмента данных располагаются в различных элементах памяти.

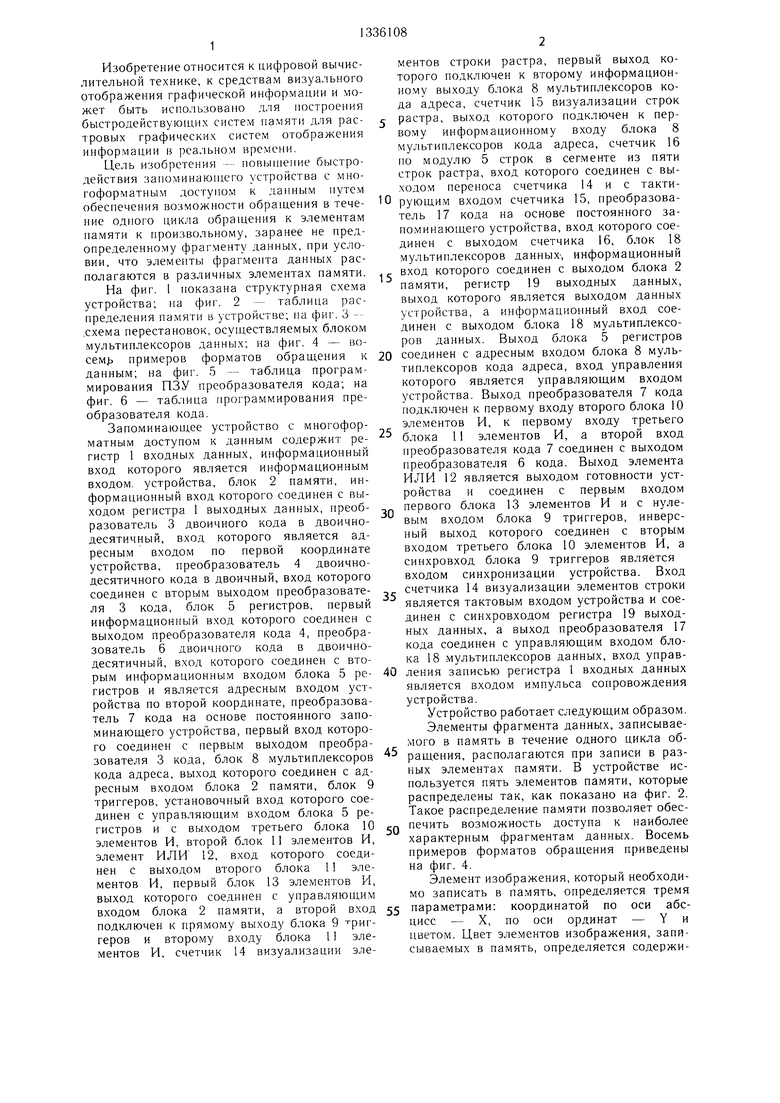

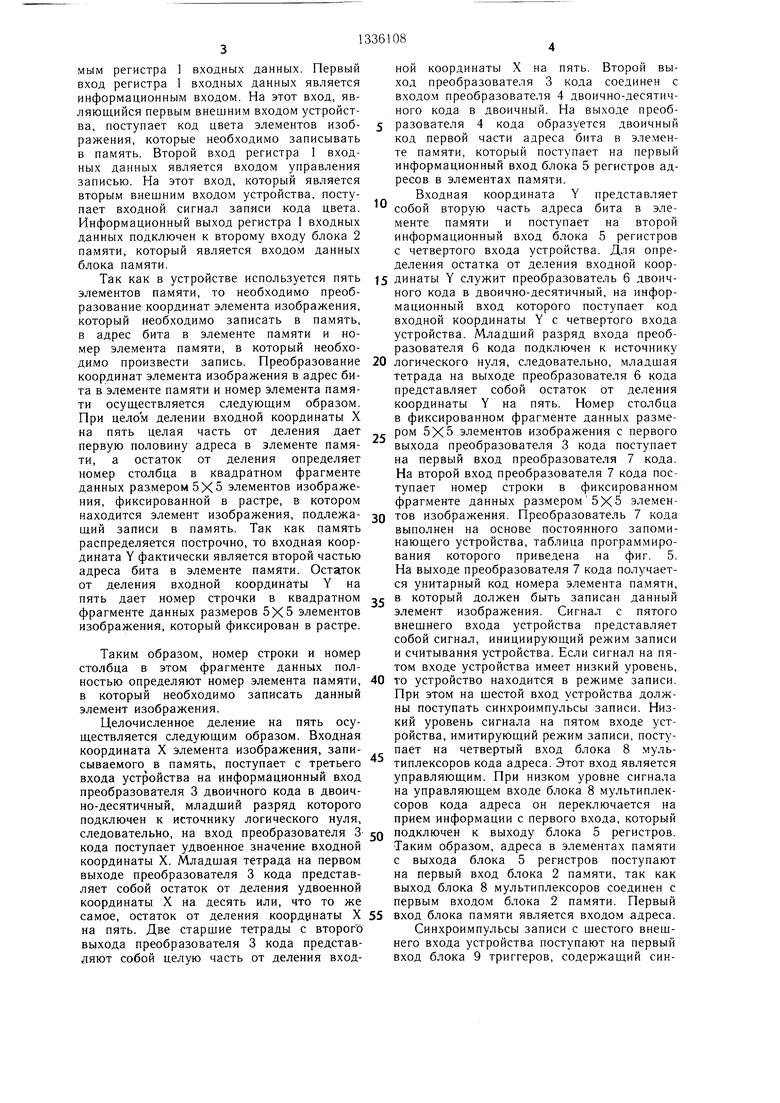

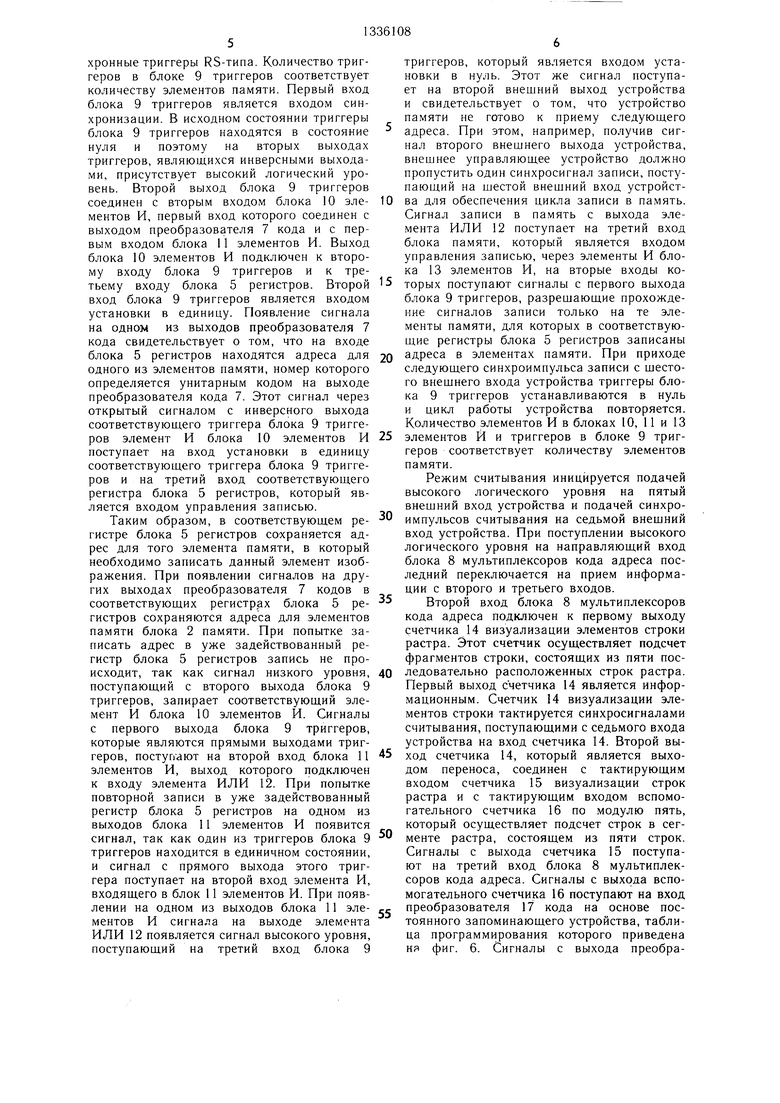

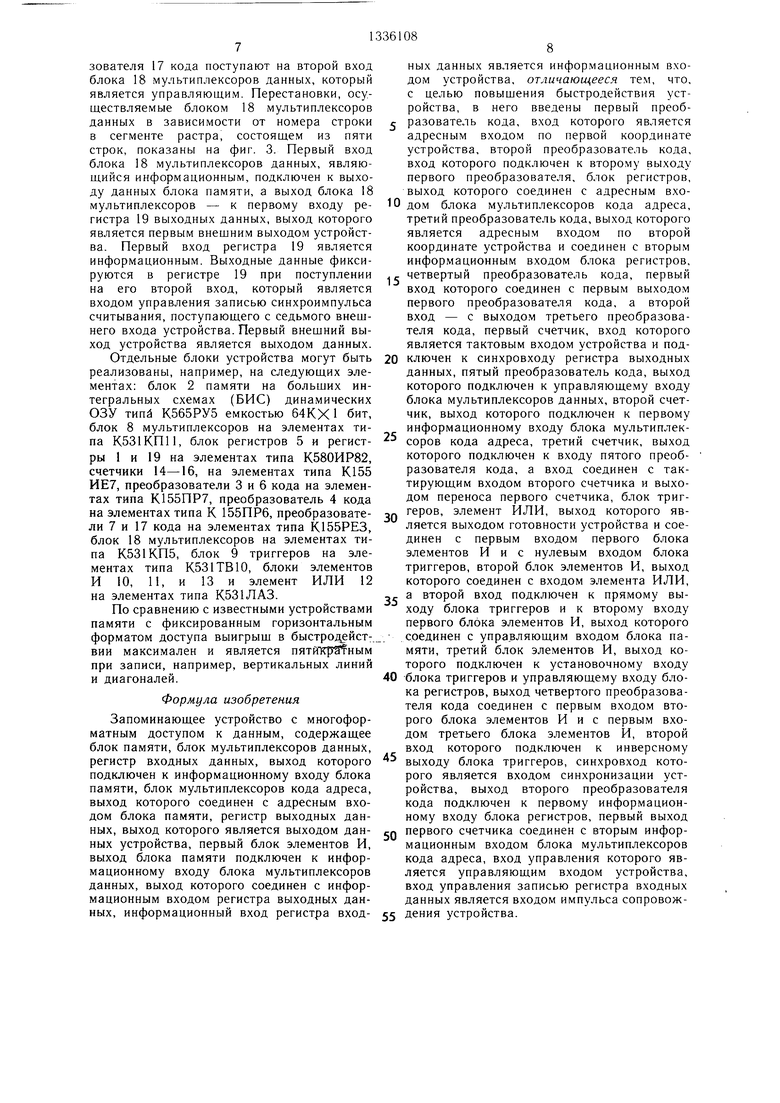

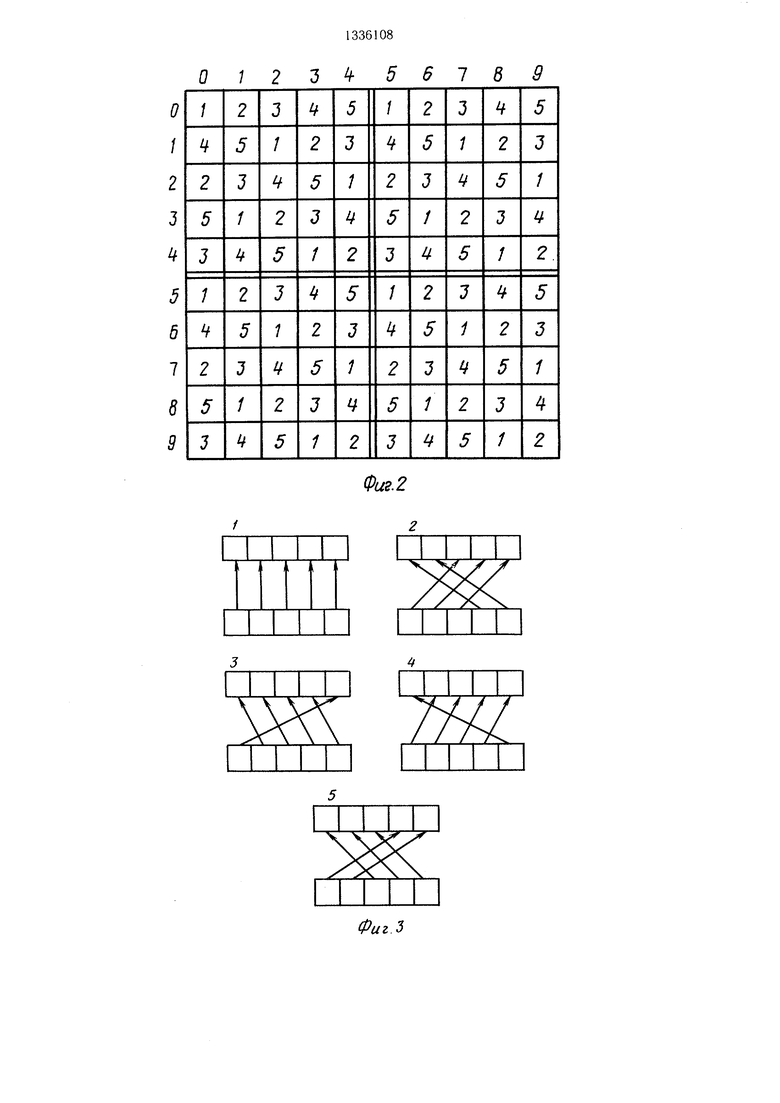

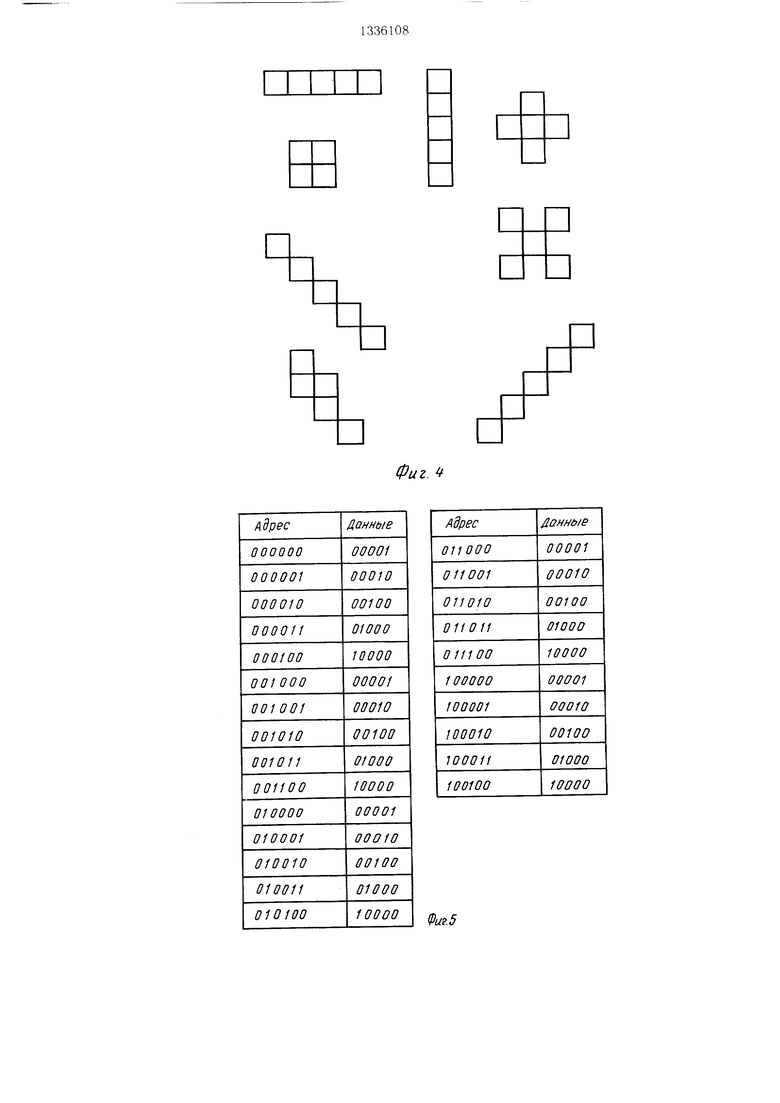

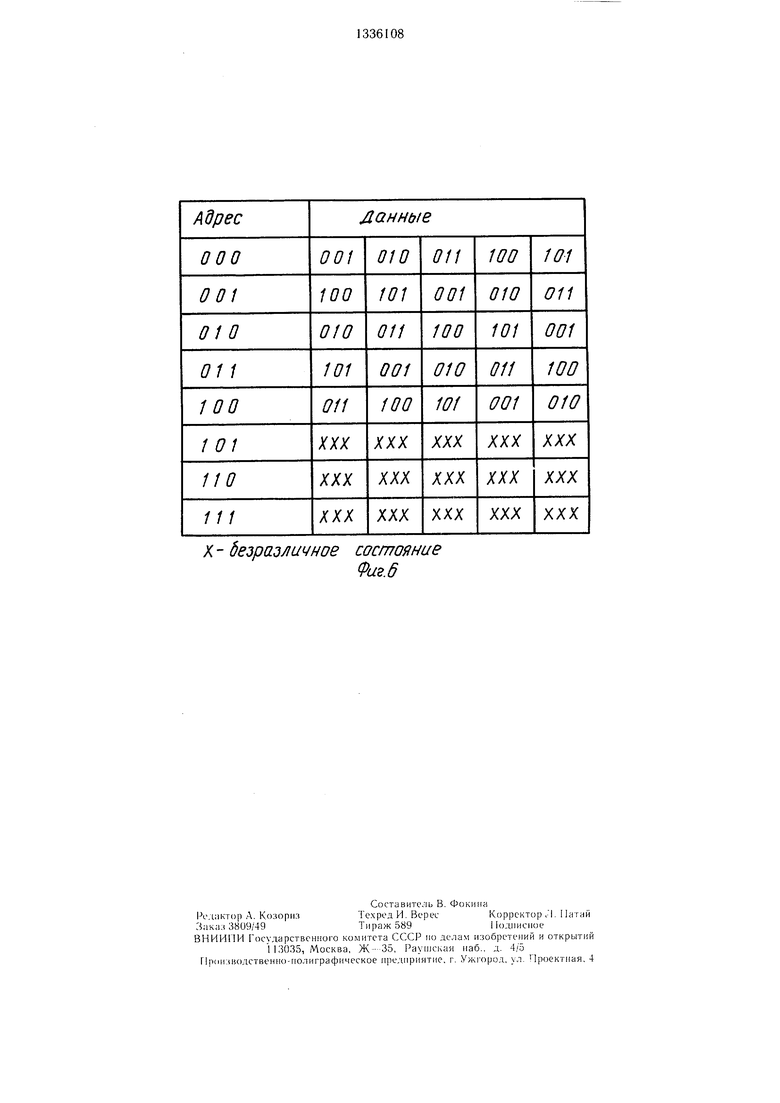

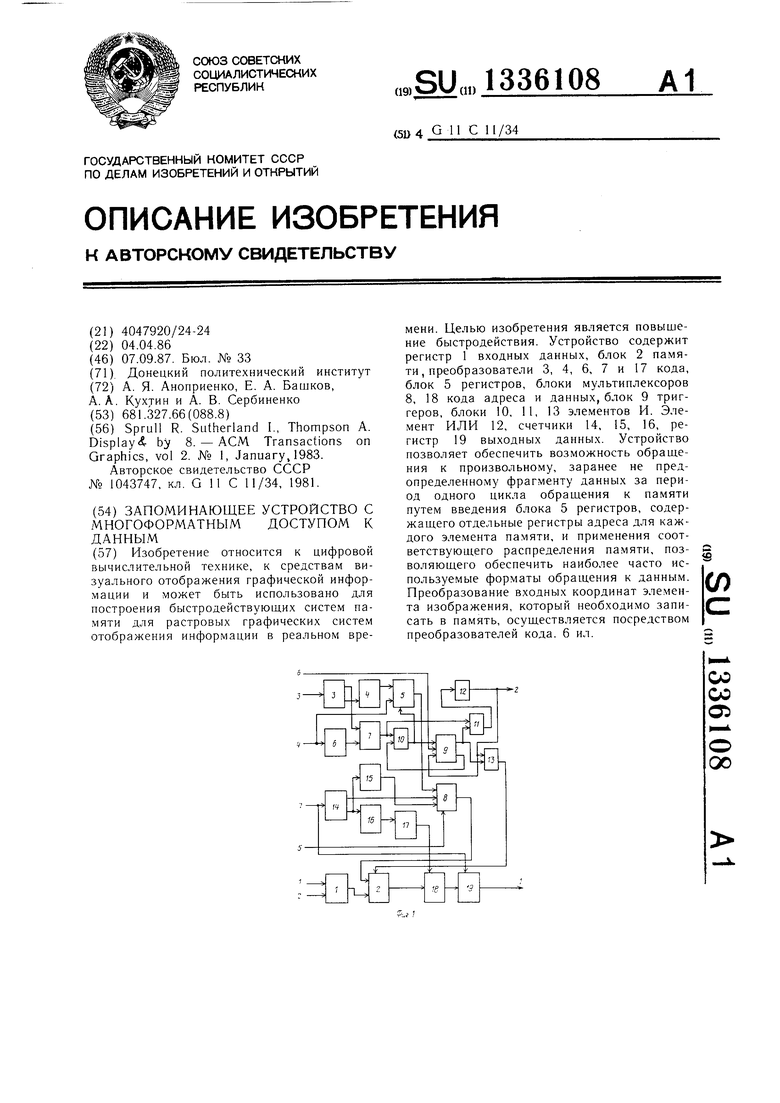

На фиг. 1 показана структурная схема устройства; на фиг. 2 - таблица распределения памяти в устройстве; па фиг. 3 - .схема перестановок, осуществляемых блоком мультиплексоров данных; на фиг. 4 - во- ceMja примеров форматов обращения к данным; на фиг. 5 - таблица программирования ПЗУ преобразователя кода; на фиг. 6 - таблица программирования преобразователя кода.

Запоминающее устройство с многоформатным доступом к данным содержит регистр 1 входных данных, информационный вход которого является информационным входом, устройства, блок 2 памяти, информационный вход которого соединен с выходом регистра 1 выходных данных, преобразователь 3 двоичного кода в двоично- десятичный, вход которого является адресным входом по первой координате устройства, преобразователь 4 двоично- десятичного кода в двоичный, вход которого соединен с вторым выходом преобразователя 3 кода, блок 5 регистров, первый информационный вход которого соединен с выходом преобразователя кода 4, преобразователь 6 двоичного кода в двоично- десятичный, вход которого соединен с вторым информационным входом блока 5 регистров и является адресным входом устройства по второй координате, преобразователь 7 кода на основе постоянного запоминающего устройства, первый вход которого соединен с первым выходом преобразователя 3 кода, блок 8 мультиплексоров кода адреса, выход которого соединен с адресным входом блока 2 памяти, блок 9 триггеров, установочный вход которого соединен с управляющи.м входом блока 5 регистров и с выходом третьего блока 10 элементов И, второй блок 1 элементов И, элемент ИЛИ 12, вход которого соединен с выходом второго блока 11 элементов И, первый блок 13 элементов И, выход которого соединен с управляюнхим входом блока 2 памяти, а второй вход подключен к прямому выходу блока 9 триггеров и второму входу блока 11 элементов И, счетчик 14 визуализации эле5

5

ментов строки растра, первый выход которого подключен к второму информационному выходу блока 8 мультиплексоров кода адреса, счетчик 15 визуализации строк

растра, выход которого подключен к первому информационному входу блока 8 мультиплексоров кода адреса, счетчик 16 по модулю 5 строк в сегменте из пяти строк растра, вход которого соединен с выходом переноса счетчика 14 и с такти0 РУЮЩ.ИМ входом счетчика 15, преобразователь 17 кода на основе постоянного запоминающего устройства, вход которого соединен с выходом счетчика 16, блок 18 мультиплексоров данных-, информационный вход которого соединен с выходом блока 2 памяти, регистр 19 выходных данных, выход которого является выходом данных устройства, а информационный вход соединен с выходом блока 18 мультиплексоров данных. Выход блока 5 регистров

0 соединен с адресным входом блока 8 мультиплексоров кода адреса, вход управления которого является управляющим входом устройства. Выход преобразователя 7 кода подключен к первому входу второго блока 10 элементов И, к первому входу третьего блока 11 элементов И, а второй вход преобразователя кода 7 соединен с выходом преобразователя 6 кода. Выход элемента ИЛИ 12 является выходом готовности устройства и соединен с первым входом первого блока 13 элементов И и с нулевым входом блока 9 триггеров, инверсный выход которого соединен с вторым входом третьего блока 10 элементов И, а синхровход блока 9 триггеров является входом синхронизации устройства. Вход счетчика 14 визуализации элементов строки является тактовым входом устройства и соединен с синхровходом регистра 19 выходных данных, а выход преобразователя 17 кода соединен с управляющим входом блока 18 мультиплексоров данных, вход управ0 ления записью регистра 1 входных данных является входом импульса сопровождения устройства.

Устройство работает следующим образом. Элементы фрагмента данных, записываемого в память в течение одного цикла обращения, располагаются при записи в разных элементах памяти. В устройстве используется пять элементов памяти, которые распределены так, как показано на фиг. 2. Такое распределение памяти позволяет обеспечить возможность доступа к наиболее характерным фрагментам данных. Восемь примеров форматов обращения приведены на фиг. 4.

Элемент изображения, который необходимо записать в память, определяется тремя

5 параметрами: координатой по оси абсцисс - X, по оси ординат - Y и цветом. Цвет элементов изображения, записываемых в память, определяется содержи0

5

5

0

мым регистра 1 входных данных. Первый вход регистра 1 входных данных является информационным входом. На этот вход, являющийся первым внешним входом устройства, поступает код цвета элементов изоб- ражения, которые необходимо записывать в память. Второй вход регистра 1 входных данных является входом управления записью. На этот вход, который является вторым внешним входом устройства, поступает входной сигнал записи кода цвета. Информационный выход регистра 1 входных данных подключен к второму входу блока 2 памяти, который является входом данных блока памяти.

Так как в устройстве используется пять элементов памяти, то необходимо преобразование координат элемента изображения, который необходимо записать в память, в адрес бита в элементе памяти и номер элемента памяти, в который необходимо произвести запись. Преобразование координат элемента изображения в адрес бита в элементе памяти и номер элемента памяти осуществляется следующим образом. При целом делении входной координаты X на пять целая часть от деления дает первую половину адреса в элементе памяти, а остаток от деления определяет номер столбца в квадратном фрагменте данных размером 5X5 элементов изображения, фиксированной в растре, в котором находится элемент изображения, подлежа- щий записи в память. Так как память распределяется построчно, то входная координата Y фактически является второй частью адреса бита в элементе памяти. Остаток от деления входной координаты Y на пять дает номер строчки в квадратном фрагменте данных размеров 5X5 элементов изображения, который фиксирован в растре.

Таким образом, номер строки и номер столбца в этом фрагменте данных полностью определяют номер элемента памяти, в который необходимо записать данный элемент изображения.

Целочисленное деление на пять осуществляется следующим образом. Входная координата X элемента изображения, записываемого в память, поступает с третьего входа устройства на информационный вход преобразователя 3 двоичного кода в двоично-десятичный, младщий разряд которого подключен к источнику логического нуля, следовательно, на вход преобразователя 3 кода поступает удвоенное значение входной координаты X. Младшая тетрада на первом выходе преобразователя 3 кода представляет собой остаток от деления удвоенной координаты X на десять или, что то же самое, остаток от деления координаты X на пять. Две старщие тетрады с второПэ выхода преобразователя 3 кода представляют собой целую часть от деления вход

5

15 0 о 5

0

о 5

5

ной координаты X на пять. Второй выход преобразователя 3 кода соединен с входом преобразователя 4 двоично-десятичного кода в двоичный. На выходе преобразователя 4 кода образуется двоичный код первой части адреса бита в элементе памяти, который поступает на первый информационный вход блока 5 регистров адресов в элементах памяти.

Входная координата Y представляет собой вторую часть адреса бита в элементе памяти и поступает на второй информационный вход блока 5 регистров с четвертого входа устройства. Для определения остатка от деления входной координаты Y служит преобразователь 6 двоичного кода в двоично-десятичный, на информационный вход которого поступает код входной координаты Y с четвертого входа устройства. Младший разряд входа преобразователя 6 кода подключен к источнику логического нуля, следовательно, младшая тетрада на выходе преобразователя 6 кода представляет собой остаток от деления координаты Y на пять. Номер столбца в фиксированном фрагменте данных размером 5X5 элементов изображения с первого выхода преобразователя 3 кода поступает на первый вход преобразователя 7 кода. На второй вход преобразователя 7 кода поступает номер строки в фиксированном фрагменте данных размером 5X5 элементов изображения. Преобразователь 7 кода выполнен на основе постоянного запоминающего устройства, таблица программирования которого приведена на фиг. 5. На выходе преобразователя 7 кода получается унитарный код номера элемента памяти, в который должен быть записан данный элемент изображения. Сигнал с пятого внешнего входа устройства представляет собой сигнал, инициирующий режим записи и считывания устройства. Если сигнал на пятом входе устройства имеет низкий уровень, то устройство находится в режиме записи. При этом на шестой вход устройства должны поступать синхроимпульсы записи. Низкий уровень сигнала на пятом входе устройства, имитирующий режим записи, поступает на четвертый вход блока 8 мультиплексоров кода адреса. Этот вход является управляющим. При низком уровне сигнала на управляющем входе блока 8 мультиплексоров кода адреса он переключается на прием информации с первого входа, который подключен к выходу блока 5 регистров. Таким образом, адреса в элементах памяти с выхода блока 5 регистров поступают на первый вход блока 2 памяти, так как выход блока 8 мультиплексоров соединен с первым входом блока 2 памяти. Первый вход блока памяти является входом адреса.

Синхроимпульсы записи с шестого внешнего входа устройства поступают на первый вход блока 9 триггеров, содержащий синхронные триггеры RS-типа. Количество триггеров в блоке 9 триггеров соответствует количеству элементов памяти. Первый вход блока 9 триггеров является входом синхронизации. В исходном состоянии триггеры блока 9 триггеров находятся в состояние нуля и поэтому на вторых выходах триггеров, являющихся инверсными выходами, присутствует высокий логический уровень. Второй выход блока 9 триггеров соединен с вторым входом блока 10 элементов И, первый вход которого соединен с выходом преобразователя 7 кода и с первым входом блока 11 элементов И. Выход блока 10 элементов И подключен к второму входу блока 9 триггеров и к тре10

триггеров, который является входом установки в нуль. Этот же сигнал поступает на второй внешний выход устройства и свидетельствует о том, что устройство памяти не готово к приему следующего адреса. При этом, например, получив сигнал второго внещнего выхода устройства, внешнее управляющее устройство должно пропустить один синхросигнал записи, поступающий на шестой внешний вход устройства для обеспечения цикла записи в память. Сигнал записи в память с выхода элемента ИЛИ 12 поступает на третий вход блока памяти, который является входом управления записью, через элементы И блока 13 элементов И, на вторые входы котьему входу блока 5 регистров. Второй 5 торых поступают сигналы с первого выхода вход блока 9 триггеров является входомблока 9 триггеров, разрешающие прохождение сигналов записи только на

установки в единицу. Появление сигнала на одном из выходов преобразователя 7 кода свидетельствует о том, что на входе блока 5 регистров находятся адреса для одного из элементов памяти, номер которого определяется унитарным кодом на выходе преобразователя кода 7. Этот сигнал через открытый сигналом с инверсного выхода соответствующего триггера блока 9 триггесигналов записи только на те элементы памяти, для которых в соответствующие регистры блока 5 регистров записаны 20 адреса в элементах памяти. При приходе следующего синхроимпульса записи с шестого внешнего входа устройства триггеры блока 9 триггеров устанавливаются в нуль и цикл работы устройства повторяется. Количество элементов И в блоках 10, 11 и 13

ров элемент И блока 10 элементов И 25 элементов И и триггеров в блоке 9 триг- поступает на вход установки в единицу соответствующего триггера блока 9 триггеров и на третий вход соответствующего регистра блока 5 регистров, который является входом управления записью.

Таким образом, в соответствующем ре- гистре блока 5 регистров сохраняется адрес для того элемента памяти, в который необходимо записать данный элемент изображения. При появлении сигналов на других выходах преобразователя 7 кодов в соответствующих регистрах блока 5 регистров сохраняются адреса для элементов памяти блока 2 памяти. При попытке записать адрес в уже задействованный регистр блока 5 регистров запись не про35

геров соответствует количеству элементов памяти.

Режим считывания иницируется подачей высокого логического уровня на пятый внешний вход устройства и подачей синхро- импу«1ьсов считывания на седьмой внешний вход устройства. При поступлении высокого логического уровня на направляющий вход блока 8 мультиплексоров кода адреса последний переключается на прием информации с второго и третьего входов.

Второй вход блока 8 мультиплексоров кода адреса подключен к первому выходу счетчика 14 визуализации элементов строки растра. Этот счетчик осуществляет подсчет фрагментов строки, состоящих из пяти посисходит, так как сигнал низкого уровня, 40 ледовательно расположенных строк растра.

поступающий с второго выхода блока 9 триггеров, запирает соответствующий элемент И блока 10 элементов И. Сигналы с первого выхода блока 9 триггеров, которые являются прямыми выходами тригПервый выход счетчика 14 является информационным. Счетчик 14 визуализации элементов строки тактируется синхросигналами считывания, поступающими с седьмого входа устройства на вход счетчика 14. Второй вы50

геров, поступ ают на второй вход блока 11 ход счетчика 14, который является выходом переноса, соединен с тактирующим входом счетчика 15 визуализации строк растра и с тактирующим входом вспомогательного счетчика 16 по модулю пять, который осуществляет подсчет строк в сегменте растра, состоящем из пяти строк. Сигналы с выхода счетчика 15 поступают на третий вход блока 8 мультиплексоров кода адреса. Сигналы с выхода вспомогательного счетчика 16 поступают на вход преобразователя 17 кода на основе постоянного запоминающего устройства, таблица программирования которого приведена ня фиг. 6. Сигналы с выхода преобраэлементов И, выход которого подключен к входу элемента ИЛИ 12. При попытке повторной записи в уже задействованный регистр блока 5 регистров на одном из выходов блока 11 элементов И появится сигнал, так как один из триггеров блока 9 триггеров находится в единичном состоянии, и сигнал с прямого выхода этого триггера поступает на второй вход элемента И, входящего в блок 11 элементов И. При появлении на одном из выходов блока 11 элементов И сигнала на выходе элемента ИЛИ 12 появляется сигнал высокого уровня, поступающий на третий вход блока 9

55

0

триггеров, который является входом установки в нуль. Этот же сигнал поступает на второй внешний выход устройства и свидетельствует о том, что устройство памяти не готово к приему следующего адреса. При этом, например, получив сигнал второго внещнего выхода устройства, внешнее управляющее устройство должно пропустить один синхросигнал записи, поступающий на шестой внешний вход устройства для обеспечения цикла записи в память. Сигнал записи в память с выхода элемента ИЛИ 12 поступает на третий вход блока памяти, который является входом управления записью, через элементы И блока 13 элементов И, на вторые входы ко5 торых поступают сигналы с первого выхода блока 9 триггеров, разрешающие прохождение сигналов записи только на

сигналов записи только на те элементы памяти, для которых в соответствующие регистры блока 5 регистров записаны адреса в элементах памяти. При приходе следующего синхроимпульса записи с шестого внешнего входа устройства триггеры блока 9 триггеров устанавливаются в нуль и цикл работы устройства повторяется. Количество элементов И в блоках 10, 11 и 13

элементов И и триггеров в блоке 9 триг-

геров соответствует количеству элементов памяти.

Режим считывания иницируется подачей высокого логического уровня на пятый внешний вход устройства и подачей синхро- импу«1ьсов считывания на седьмой внешний вход устройства. При поступлении высокого логического уровня на направляющий вход блока 8 мультиплексоров кода адреса последний переключается на прием информации с второго и третьего входов.

Второй вход блока 8 мультиплексоров кода адреса подключен к первому выходу счетчика 14 визуализации элементов строки растра. Этот счетчик осуществляет подсчет фрагментов строки, состоящих из пяти последовательно расположенных строк растра.

Первый выход счетчика 14 является информационным. Счетчик 14 визуализации элементов строки тактируется синхросигналами считывания, поступающими с седьмого входа устройства на вход счетчика 14. Второй выход счетчика 14, который является выходом переноса, соединен с тактирующим входом счетчика 15 визуализации строк растра и с тактирующим входом вспомогательного счетчика 16 по модулю пять, который осуществляет подсчет строк в сегменте растра, состоящем из пяти строк. Сигналы с выхода счетчика 15 поступают на третий вход блока 8 мультиплексоров кода адреса. Сигналы с выхода вспомогательного счетчика 16 поступают на вход преобразователя 17 кода на основе постоянного запоминающего устройства, таблица программирования которого приведена ня фиг. 6. Сигналы с выхода преобразователя 17 кода поступают на второй вход блока 18 мультиплексоров данных, который является управляющим. Перестановки, осуществляемые блоком 18 мультиплексоров данных в зависимости от номера строки в сегменте растра, состоящем из пяти строк, показаны на фиг. 3. Первый вход блока 18 мультиплексоров данных, являющийся информационным, подключен к выходу данных блока памяти, а выход блока 18 мультиплексоров - к первому входу регистра 19 выходных данных, выход которого является первым внещним выходом устройства. Первый вход регистра 19 является информационным. Выходные данные фиксируются в регистре 19 при поступлении на его второй вход, который является входом управления записью синхроимпульса считывания, поступающего с седьмого внещ- него входа устройства. Первый внещний выход устройства является выходом данных.

Отдельные блоки устройства могут быть реализованы, например, на следующих элементах: блок 2 памяти на больщих интегральных схемах (БИС) динамических ОЗУ типй К565РУ5 емкостью 64КХ1 бит, блок 8 мультиплексоров на элементах типа К531КП11, блок регистров 5 и регистры 1 и 19 на элементах типа К580ИР82, счетчики 14-16, на элементах типа К155 ИЕ7, преобразователи 3 и б кода на элементах типа К155ПР7, преобразователь 4 кода на элементах типа К 155ПР6, преобразовате- 30 ли 7 и 17 кода на элементах типа К155РЕЗ, блок 18 мультиплексоров на элементах типа К531КП5, блок 9 триггеров на элементах типа К531ТВ10, блоки элементов И 10, 11, и 13 и элемент ИЛИ 12 на элементах типа К531ЛАЗ.

По сравнению с известными устройствами памяти с фиксированным горизонтальным

ных данных является информационным входом устройства, отличающееся тем, что с целью повыщения быстродействия устройства, в него введены первый преоб разователь кода, вход которого является адресным входом по первой координате устройства, второй преобразователь кода вход которого подключен к второму выходу первого преобразователя, блок регистров выход которого соединен с адресным вхо10 дом блока мультиплексоров кода адреса, третий преобразователь кода, выход которого является адресным входом по второй координате устройства и соединен с вторым информационным входом блока регистров,

,, четвертый преобразователь кода, первый вход которого соединен с первым выходом первого преобразователя кода, а второй вход - с выходом третьего преобразователя кода, первый счетчик, вход которого является тактовым входом устройства и подключен к синхровходу регистра выходных данных, пятый преобразователь кода, выход которого подключен к управляющему входу блока мультиплексоров данных, второй счетчик, выход которого подключен к первому информационному входу блока мультиплексоров кода адреса, третий счетчик, выход которого подключен к входу пятого преобразователя кода, а вход соединен с тактирующим входом второго счетчика и выходом переноса первого счетчика, блок триггеров, элемент ИЛИ, выход которого является выходом готовности устройства и соединен с первым входом первого блока элементов И и с нулевым входом блока триггеров, второй блок элементов И, выход которого соединен с входом элемента ИЛИ, а второй вход подключен к прямому выходу блока триггеров и к второму входу первого блока элементов И, выход которого

20

25

35

форматом доступа выигрыщ в быстродейст:./ соединен с управляющим входом блока па- вин максимален и является пятйтф ным мяти, третий блок элементов И, выход ко- при записи, например, вертикальных линий и диагоналей.

торого подключен к установочному входу 40 блока триггеров и управляющему входу блока регистров, выход четвертого преобразователя кода соединен с первым входом второго блока элементов И и с первым входом третьего блока элементов И, второй вход которого подключен к инверсному выходу блока триггеров, синхровход которого является входом синхронизации устройства, выход второго преобразователя кода подключен к первому информационному входу блока регистров, первый выход первого счетчика соединен с вторым информационным входом блока мультиплексоров кода адреса, вход управления которого является управляющим входом устройства, вход управления записью регистра входных данных является входом импульса сопровожФормула изобретения

Запоминающее устройство с многоформатным доступом к данным, содержащее блок памяти, блок мультиплексоров данных, регистр входных данных, выход которого подключен к информационному входу блока памяти, блок мультиплексоров кода адреса, выход которого соединен с адресным входом блока памяти, регистр выходных данных, выход которого является выходом данных устройства, первый блок элементов И, выход блока памяти подключен к информационному входу блока мультиплексоров данных, выход которого соединен с информационным входом регистра выходных дан

ных, информационный вход регистра вход-

0

ных данных является информационным входом устройства, отличающееся тем, что, с целью повыщения быстродействия устройства, в него введены первый преоб разователь кода, вход которого является адресным входом по первой координате устройства, второй преобразователь кода, вход которого подключен к второму выходу первого преобразователя, блок регистров, выход которого соединен с адресным вхо0 дом блока мультиплексоров кода адреса, третий преобразователь кода, выход которого является адресным входом по второй координате устройства и соединен с вторым информационным входом блока регистров,

, четвертый преобразователь кода, первый вход которого соединен с первым выходом первого преобразователя кода, а второй вход - с выходом третьего преобразователя кода, первый счетчик, вход которого является тактовым входом устройства и подключен к синхровходу регистра выходных данных, пятый преобразователь кода, выход которого подключен к управляющему входу блока мультиплексоров данных, второй счетчик, выход которого подключен к первому информационному входу блока мультиплексоров кода адреса, третий счетчик, выход которого подключен к входу пятого преобразователя кода, а вход соединен с тактирующим входом второго счетчика и выходом переноса первого счетчика, блок триггеров, элемент ИЛИ, выход которого является выходом готовности устройства и соединен с первым входом первого блока элементов И и с нулевым входом блока триггеров, второй блок элементов И, выход которого соединен с входом элемента ИЛИ, а второй вход подключен к прямому выходу блока триггеров и к второму входу первого блока элементов И, выход которого

0

5

5

соединен с управляющим входом блока па- мяти, третий блок элементов И, выход ко-

Дения устройства.

торого подключен к установочному входу блока триггеров и управляющему входу блока регистров, выход четвертого преобразователя кода соединен с первым входом второго блока элементов И и с первым входом третьего блока элементов И, второй вход которого подключен к инверсному выходу блока триггеров, синхровход которого является входом синхронизации устройства, выход второго преобразователя кода подключен к первому информационному входу блока регистров, первый выход первого счетчика соединен с вторым информационным входом блока мультиплексоров кода адреса, вход управления которого является управляющим входом устройства, вход управления записью регистра входных данных является входом импульса сопровож

012 56189

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1983 |

|

SU1124379A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели переменного тока | 1989 |

|

SU1793458A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТЕЛЕВИЗИОННОГО ИЗОБРАЖЕНИЯ С ИЗМЕНЕНИЕМ МАСШТАБА УПРАВЛЯЕМОГО ФРАГМЕНТА | 1993 |

|

RU2065206C1 |

| Устройство для ввода информации | 1990 |

|

SU1795443A1 |

| Устройство для отображения графической информации | 1988 |

|

SU1566339A1 |

| Устройство для ввода информации | 1990 |

|

SU1702382A1 |

| Устройство для ввода информации | 1990 |

|

SU1698890A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1988 |

|

SU1583967A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Устройство для ввода информации | 1990 |

|

SU1783509A2 |

Изобретение относится к цифровой вычислительной технике, к средствам визуального отображения графической информации и может быть использовано для построения быстродействующих систем памяти для растровых графических систем отображения информации в реальном времени. Целью изобретения является повышение быстродействия. Устройство содержит регистр 1 входных данных, блок 2 памяти, преобразователи 3, 4, 6, 7 и 17 кода, блок 5 регистров, блоки мультиплексоров 8, 18 кода адреса и данных, блок 9 триггеров, блоки 10, 11, 13 элементов И. Элемент ИЛИ 12, счетчики 14, 15, 16, регистр 19 выходных данных. Устройство позволяет обеспечить возможность обращения к произвольному, заранее не предопределенному фрагменту данных за период одного цикла обращения к памяти путем введения блока 5 регистров, содержащего отдельные регистры адреса для каждого элемента памяти, и применения соответствующего распределения памяти, позволяющего обеспечить наиболее часто используемые форматы обращения к данным. Преобразование входных координат элемента изображения, который необходимо записать в память, осуществляется посредством преобразователей кода. 6 ил. « (Л

Фиг.

Фиг. «

У.-безразличное состояние

(Pus.6

| Sprull R | |||

| Sutherland I., Thompson A | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| - ACM Transactions on Graphics, vol 2 | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство с многоформатным доступом к данным | 1981 |

|

SU1043747A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-04—Подача