информационными входами устройства.

2. Устройство по п. 1, отличающееся тем, что блок управления режимом содержит триггеры с второго по шестой и элементы Й-ШШ, причем первый и второй входы перво- го элемента И-ИЛИ подключены к прямым выходам второго и третьего триггеров соответственно, а выход соединен с входом запуска пятого триггера, первьй и второй входы второго элемента И-ИПИ подключены соответственно к инверсным выходам второго и третьего триггеров, а выход соединен с входом запуска шестого триггера, третьи и четвертые входы элементов И-ИЛИ соответственно объединены и являются первым и вторым

входами блока, третьим, четвертым и пятым входами которого являются соответственно установочные входы второго, третьего триггеров и вход запуска четвертого триггера, установочный вход которого и входы синхронизации второго и третьего триггеров являются mecTbiM входом блока, седьмым ВХОДОМ которого является пятый вход первого элемента И-ИЛИ, шестой вход которого подключен к прямому выходу четвертого триггера, восьмым и девять1м входами блока являются соответственно установочные входы пятого и шестого триггеров и пятый и шестой входы второго элемента И-ИЛИ первым, вторым и третьим выходами блока являются соответственно прямые выходышестого,пятого и четвертого тригерров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

| Буферное запоминающее устройство для блоков отображения информации | 1986 |

|

SU1411830A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1280457A1 |

| Устройство для сопряжения цифровой вычислительной машины с устройством ввода изображений | 1983 |

|

SU1176339A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1571679A1 |

| Устройство для обработки элементов сканерных изображений | 1983 |

|

SU1134945A1 |

| Устройство формирования телевизионного изображения с перемещением управляемого фрагмента | 1988 |

|

SU1644171A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1105940A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1261012A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТЕЛЕВИЗИОННОГО ИЗОБРАЖЕНИЯ С ИЗМЕНЕНИЕМ МАСШТАБА УПРАВЛЯЕМОГО ФРАГМЕНТА | 1993 |

|

RU2065206C1 |

1. БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее основной блок памяти, информационные входы и выходы которого являются одними из информаи онных входов н выходами устройства, счетчик адресов записи, счетчик адресов считывания и первый триггер, первый вход которого соединен с входом счетчика адресов записи и является входом адреса записи устройства, а второй вход - с входом счетчика адресов считывания и является входом адреса считывания устройства, причем прямой выход первого триггера лодключен к одному из управляющих входов осйовного блока памяти, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения возможности автоматического изменения адреса по строкам и по столбцам основного блог ка памяти, в него введены дополнительные блоки памяти, сумматор адресов строк, сумматор адресов столбцов, мультиплексор координат столбцов, мультиплексор координат строк и блок управления режимом, причем входы мультиплексора ко(эрдинат столбцов соединены соответственно с одним из выходов счетчика адреса записи и с одним из выходов счетчика адресов считывания, другие выходы которых подключены к входам мультиплексора координат строк, управляющие входы мультиплексоров соединены с прямым выходом первого триггера, одни из адресных входов первого дополнительного блока памяти подключены к выходам мультиплексора координат столбцов и одним из входов сумматора адресов столбцов, другие входы которого соединены с выходами второго дополнительного блока памяти, одни из адресных входов которого подключены к выходам мультиплексора координат b строк и одним из входов сумматора адресов строк, другие входы которого соединены с выходами первого дополнительного блока памяти, выходы сумматора адресов строк и сумматора адресов столбцов подключены к адресным входам основного блока памяти, другой управляющий вход которого соединен 1C с первым выходом блока управления ре4ib жимом, второй и третий выходы кото00 СО рого подключены к управлякщим входам первого и второго дополнительных блоков памяти, первый и второй входы блока управления режимом соединены с первым и с вторым входами первого триггера, входы с третьего по седьмой блока управления режимом являются управляющими входами устройства, а восьмой и девятый входы подключены со ответственно к управляющим выходам основного и первого дополнительного блоков памяти, другие адресные и информационные входы дополнительных блоков памяти являются соответственно другими адресными и другими

Изобретение относится к вычислительной технике и может быть использовано в устройствах ввода изображений в цифровом виде в системь обработки информации. .

Известно буферное запоминакицее устройство (БЗУ), позволяющее осуществлять обмен информацией и совме,щать процесс ввода данных с процессом их обработки СООднако известное устройство характеризуется ограниченной областью его применения из-за невозможности использования для ввода изображений в цифровом виде, представляюпщх собой двумерную матрицу данных.

Наиболее близким техническим решением к изобретению является буферное запоминающее устройство, содержащее накопитель, счетчики адресов записи и чтения, мультиплексор, служащий для выбора того или иного счетчика адреса в зависимости от выполняемой операции,регистр числа, соединенныйс разрядными шинами накопителя и с общими шинами числа, дешифратор, подключенный к адресным шинамнакопителя, блок управления, одни из входов которого соединены с шинами управления, счетчик объема буферной зоны, первые и вторые входы которого соединены с первым и вторым входами блока управления, регистр объема буферной зоны, одни из входов которого подключены к общим шинам числа, а другой вход соединен с третьим входом блока управления, блок анализа состояния буферной зоны, первые и вторые входы которого подключены к выходам счетчика объема буферной зоны и регистра объема буферной зоны,

одни из выходов которог.о соединены с одноименными входами счетчика объема буферной зоны, а другие выходыс одноименными входами дещифратора 2. Недостаток данного устройства обусловлен также ограниченной областью его применения.

Цель изобретения - расширение области примене1шя устройства за счет обеспечения возможности автоматического изменения адреса по строкам и столбцам основного блока памяти.

Поставленная цель достигается тем, что в буферное запоминающее устройство, содержащее основной блок памяти,

информационные входы и выходы которого являются одними из информационных входов и выходами устройства, счетчик адресов записи, счетчик адресов считывания и первьй триггере

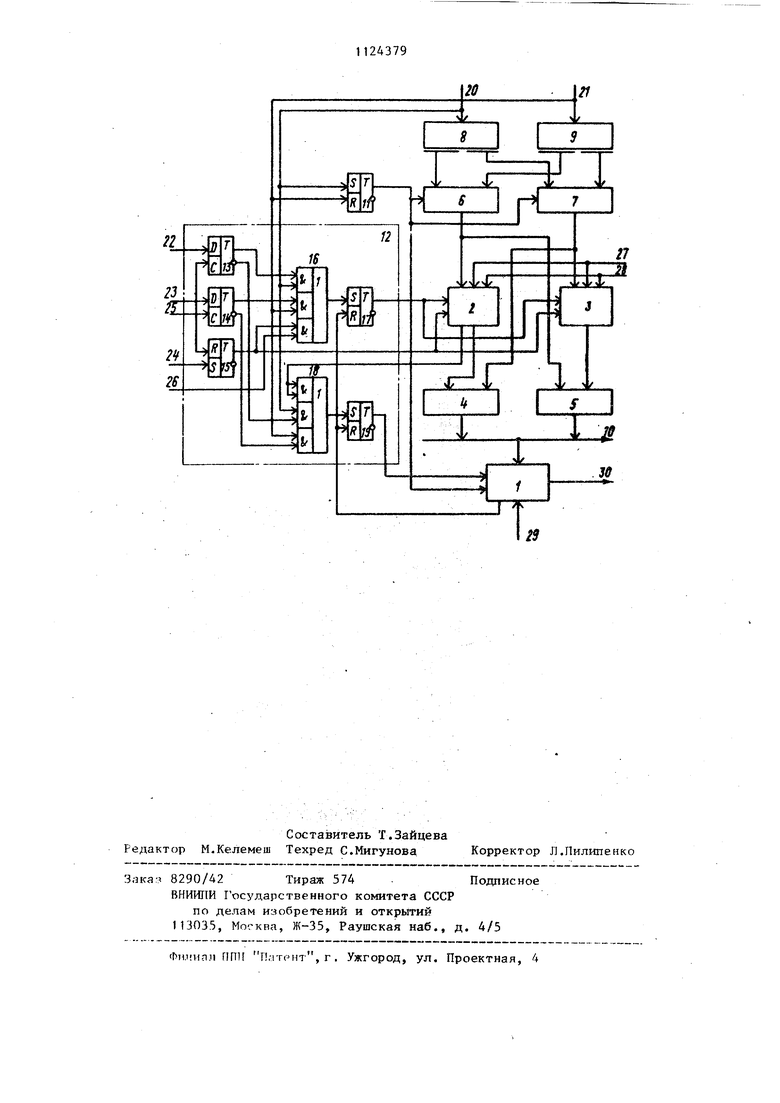

первьй вход которого соединен с входом счетчика адресов записи и является выходом адреса записи устройства. a второй вход - с входом счетчика адресов считывания и является входом ад реса считывания устройства, причем прямой выход первого триггера подключен к одному из управляющих входов основного блока памяти, введены дополнительные блоки памяти, сумматор адресов строк, сумматор адресов столб цов, мультиплексор координат столбЦов, мультиплексор координат строк , и блок управления режимом, причем вхо ды мультиплексора координат столбцов соединены соответственно с одними из входов счетчика адреса записи и с одними из выходов счетчика адресов считывания, другие выходы которых подключены к входам мультиплексора координат строк, управляющие входы мультиплексоров соединены с прямым выходом первого триггера, одни из адресных входов первого до полнительного блока памяти подключены к выходам мультиплексора коорди нат столбцов и одним из входов сумматора адресов столбцов, другие входы которого соединены с выходами второго дополнительного блокапамяти, одни из адресных входов которого подключе ны к выходам мультиплексора координат строк и одним из входов сумматора ад ресов строк. Другие входы которого соединены с выходами первого дополнительного блока памяти, выходы сумматора адресов строк и сумматора адресов столбцов подключены к адресным входам основного блока памяти, другой управляющий вход которого соединен с первым выходом блока ynpaBJleния режимом, второй и третий выходы которого подключены к управляклцим входам первого и второго дополнитель ных блоков памяти, первьш и второй входы блока управления режимом соеди нены с первым и с вторым входами пер вого триггера, входы с третьего по седьмой блока управления режимом являются управляюищьм входами устройст ва, а восьмой и девятый входы подклю чены соответственно к управлягадим вы ходам основного и первого дополнител ного блоков памяти, другие адресные и информационные входы дополнительных блоков памяти являются соответст венно другими адресными и другими ин формационными входами устройства. Кроме того, блок управления режимом содержит триггеры с второго по шестой Иэлементы И-ИЛИ, причем пер- вьш и второй входы первого элемента И-ИЛИ подключены к прямым выходам второго и третьего триггеров соответственно, а выход соединен с входом запуска пятого триггера, первый и вгорой входы второго элемента И-ИЛИ подключены соответственно к инверсным выходам второго и третьего триггеров, а вькод соединен с входом запуска шестого.триггера, третьи и четвертые входы элементов И-ШШ соответственно объединены и являются первым и BTOpbiM входами блока, третьим, четвертым и пятым входами которого являются соответственно установочные входы второго, третьего триггеров и вход запуска четвертого триггера, установочный вход которого и вход синхронизации второго и третьего триггеров являются шестым входом блока, седьмым входом которого является пятый вход первого элемента И-ШШ, шестой вход которого подюцочен к прямому выходу четвертого триггера, восьмым и девятым входами блока являются соответственно установочные входы пятого и шестого триггеров и пятый и шестой входы второго элемента И-ШШ, первым, вторым, и третьим выходами блока являются соответственно прямые выходы шестого, пятого и четвертого триггеров. На чертеже представлена функциональная схема предложенного устройства. Устройство содержит основной блок 1 памяти, дополнительные блпки 2 и 3 памяти, сумматор 4 адресов строк, сумматор 5 адресов столбцов, мультиплексоры 6 координат столбцов, мультиплексор 7 координат строк, счетчик 8 адресов записи, счетчика 9 адресов считывания, адресные входы tO основного блока t памяти, первый триггер 11, блок 12 управления режимом. Блок 12 управления режимом содержит триггеры 13-15 с второго по чет- . вертьй, первый элемент И-ИЛИ 16, пятый триггер 17, второй элемент И-ИЛИ 18 и шестой триггер 19. На чертеже обозначены вход 20 адреса записи, вход 21 адреса считывания, управляющие входы 22-26, другие адресные входы 27, информационные входы 28 и 29 и информационные выходы 30 устройства. Устройство работает следующим образом. До сеанса ра.боты сигналом на входе 24 устанавливается триггер 15, опрелеляющий операцию записи в блоках 2 и 3 и разрешающий прохождение запросов на загрузку с входа 26 через эле мент И-ИЛИ 16. По входам 27, 28 и 26 осуществляется запись информации в блоки 2 и 3. Эта информация представляет собой совокупность поправок к координатам строк и столбцов, вычисляемых предварительно в соответствии с заданным алгоритмом геометрической нормализации. В блок 2 записываются поправки к координатам строк, в блок 3 - к координатам столбцов. Запись информации в блоки 2 и 3 может осуществляться параллель но за счет пространственного разделе ния Еин 27. Устройство функционирует в трех режимах. Первый режим: запись с нормализацией, считывание без нормализации. Перед установкой режима на выход 22 подается сигнал уровня единицы на входы 23 и 24 - сигналы нуля. Установка режима осуществляется импульсным сигналом на входе 25, кото рый устанавливает триггер 13 и сбра сывает триггеры 14 и 15. Запрос на запись,поступивший по входу 20,увеличивает содержимое счет чика 8 на единицу, устанавливает триггер 11 и открывает третий вход элемента И-ИЛИ 16, на первом входе которого поступает уровень единицы с прямого выхода триггера 13. Сигнал с прямого выхода триггера 11 выбирает входы мультиплексоров 6 и 7, подключенные, к счетчику 8, и определяет операцию записи в блоке 1. Старшие разряды кода адреса в счетчике 8, являющиеся координатами стол ца вводимого элемента изображения, с выходом мультиплексора 6 поступают на адресные входы блока 2 и входы сумматора 5. Младшие разряды кода ад реса в счетчике 8, являющиеся коорди натами строки вводимого элемента изо ражения, с выходов мультиплексора поступают на адресные входы блока 3 и на входы сумматора 4. Сигнал с вых да элемента И-ИЛИ 16 устанавливает триггер 17, который формирует сигнал Разрешение выборки для блоков 2 и 3. После опера1щи считывания на выхо дах блоков 2 и 3 оказываются коды поправок к координатам элемента мат рицы вводимого изображения. В блоке 2 счипипается поправка к координатг с;троки, которая определяется координатой столбца вводимого элемента матрицы изображения, а в блоке 3 считывается поправка к координате столбца, определяемая координатой строки вводимого элемента матрицы изображения. Сумматоры 4 и 5 осуществляют суммирование считанных поправок с TeKyu iMH координатами адресов соответственно строки и столбца элемента ненормализованного изображения. Таким образом, на шинах 10 появляется новый адре.с элемента изображения, сформированный в соответствии с требуемым алгоритмом нормализации. По завершении операции считывания в блоках 2 и 3 блок 2 формирует сигнал Конец цикла, поступающий на пятый и шестой входы элемента И-ИЛИ 18. Сигнал с выхода элемента И-ИЛИ 18 устанавливает триггер 19, формирующий сигнал Разрешение выборки для блока 1, После завершения операции записи по адресу на входах 10 блок 1 формирует сигнал Конец циклa который сбрасывает триггеры 19 и 17, возвращая блок 12 в исходное состояние. При поступлении по входу 21 заявки на считывание информации из БЗУ увеличивается на единицу содержимое счетчика 9 и сбрасывается триггер 11, сигнал с прямого выхода которого выбирает вторые входы мультиплексоров 6 и, 7 и определяет операцию считывания в блоке 1. Элемент И-ИЛИ 16 сигнала не вырабатывает, так как его второй вход закрыт сигналом с прямого выхода триггера 14. Триггер 17, следовательно, не устанавливается, а операция считывания в блоках 2 и 3 не производится. На информационньЕх выходах блоков 2 и 3 - нули. Координаты столбца и строки элемента матрицы изображения с выхода мультиплексора 7 после суммирования.с нулями на сумматорах 5 и 4 без изменения подаются на входы 10. Заявка на считывание, поступившая по входу 21, открывает элемент И-4ШИ 18, на втором входе которого уровень единицы с обратного выхода триггера 14. Сигнал с выхода элемента И-ИЛИ 18 устанавливает триггер 19,формирующий сигнал Разрешение выборки для блока 1.В результате считьшание информации в блоке 1 осуществляется по адресу,хранящемуся в счетчике 9,т.е. без нормализации. Режим второй: считывание с нормализацией, запись без нормализации. 71 Перед установкой режима на вход 23 подается уровень единицы, на входы 22 и 24 - уровни нуля. Установка режима осуществляется импульсным сигналом на входе 25, который устанавливает триггер 14 и сбрасывает триггеры 13 и 15. Отличие этого режима от предьщущего состоит в том, что сигнал Разрешение выборки для блоков 2 и 3 формируется триггером 17 при поступлении запроса на считывание по входу 21, так как элемент И-ИЛИ 16 открыт сигналом с прямого выхода триггера 1 В этом случае сумматорами 4 и 5 осуществляется суммирование текущих координат строки и столбца элемента ма рицы вводимого изображения с поправками к координатам, которые считываются в блоках 2 и 3. Считывание информации в блоке 1 производится по новому адресу, сформированному по заданному алгоритму нормализации. При поступлении по входу 20 запроса на запись сигнал Разрешение выборки для блоков 2 и 3 не формируется, так как закрыт элемент И-ИЛИ 16 сигналом с прямого выхода триггера 13. Запись информации в блоке 1 осуществляется по адресу, хранящемуся в счетчике 8, т.е. без нормализации. 9 Третий режим: запись и чтение без нормализации. Установка режима производится подачей импульсного сигнала на вход 25, причем на входах 22, 23 и 24 предварительно должны быть установлены уровни нуля. В результате триггеры 13, 14 и 15 сбрасываются. При работе в этом режиме как при поступлении по входу 20 запроса на запись, так и при поступлении по вхопу 21 запооса на считывание сигнал Разоешение выборки пля блоков 2 и 3 не формируется, так как элемент И-ИЛИ 16 закрыт сигналами с триггеров 13 и 14. На выходах блоков 2 и 3 присутствуют нули. В этом случае сумматоры 4 и 5 без изменения передают при записи содержимое счетчика 8, а при считывании - содержимое счетчика 9 на входы 10. Таким образом, использование изобретения позволяет совместить ввод изображений в цифровом виде с их предварительной обработкой, заключающейся в устранении геометрических искажений, за счет чего расщиряется область применения БЗУ. Технико-экономическое преимущество предложенного устройства заключается в бапее широкой nq сравнению с прототипом области егоприменения.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № 407394, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Буферное запоминающее устройство | 1977 |

|

SU705517A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-11-15—Публикация

1983-07-08—Подача