1

Изобретение ОТРЮСИТСЯ к вычислительной технике и может быть использовано для преобразования табличных неизбыточных кодов.

Цель изобретения - упрощение устройства.

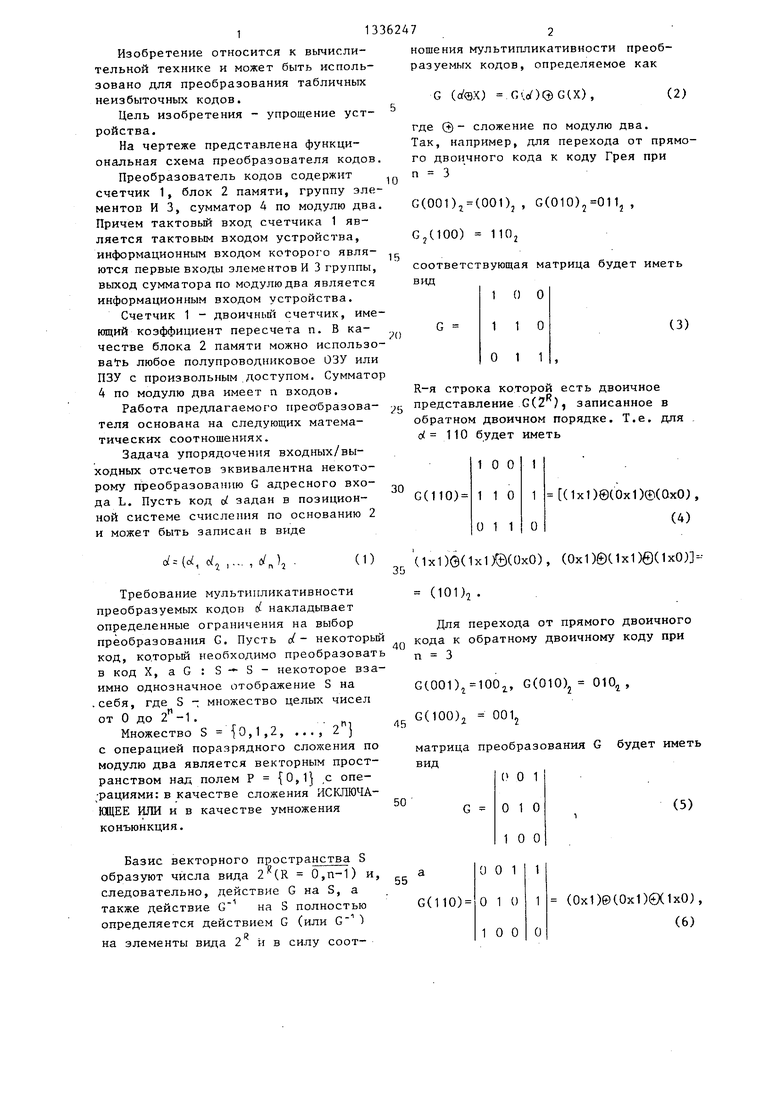

На чертеже представлена функциональная схема преобразователя кодов

Преобразователь кодов содержит счетчик 1, блок 2 памяти, группу элементов И 3, сумматор А по модулю два Причем тактовый вход счетчика 1 является тактовым входом устройства, информационным входом которого являются первые входы элементов И 3 группы, выход сумматора по модулю два является информационным входом устройства.

Счетчик 1 - двоичньш счетчик, имеющий коэффициент пересчета п. В качестве блока 2 памяти можно использо ва гь любое полупроводниковое ОЗУ или ПЗУ с произвольным доступом. Суммато 4 по модулю два имеет п входов.

Работа предлагаемого прео бразова- теля основана на следующих математических соотношениях.

Задача упорядочения входных/выходных отсчетов эквивалентна некоторому п реобраэованию G адресного входа L. Пусть код Ы задан в позиционной системе счисления по основанию 2 и может быть записан в виде

(, с, ,... ,J,

Требование мультипликативности преобразуемых кодой d накладывает определенные ограничения на выбор преобразования G. Пусть с - некоторы код, ко.торьш необходимо преобразоват в код X, а G : S S - некоторое взаимно однозначное отображение S на .себя, где S множество целых чисел от О до 2 -1.

Множество S ,1,2, ..., 2 с операцией поразрядного сложения по модулю два является векторным пространством над полем Р {0,1 ,с опе- рациями:в качестве сложения ИСКЛЮЧАЮЩЕЕ ИЛИ и в качестве умножения конъюнкция.

Базис векторного пространства S образуют числа вида 2 (R 0,п-1) и, следовательно, действие G на S, а также действие G на S полностью определяется действием G (или G )

п

на элементы вида 2 ив силу соот13362472

ношения мультипликативности преобразуемых кодов, определяемое как

G (а/®Х) G ,,)eG(X),

(2)

где О)- сложение по модулю два. Так, например, для перехода от прямого двоичного кода к коду Грея при п 3

G(001).j (001)j

0(010),

Gj(IOO) 110

15

соответствующая матрица будет иметь

вид

1 О О

()

G

1 1 О

(3)

О 1 1

R-я строка которой есть двоичное g представление С(2 ), записанное в обратном двоичном порядке. Т.е. для d 110 будет иметь

1 О О

G(110)

1 1 О

О 1 1

О

(1х1)®(0х1)©(ахо;,

(4)

3D

40

45

С1х1)0(1х1)©(ОхО), (Ох1)0С1х1)@(1хО)- (101)j .

Для перехода от прямого двоичного кода к обратному двоичному коду при п 3

G(001) 100i, G(010)j OlOj, G(IOO), 001

матрица преобразования G будет иметь вид

( О 1

G

01 О

1О О

(5)

55

О О 1

О 1 О

1 О О

(0x1)0(0x1)0(1x0), (6)

(Ох1)©С1х1)©(ОхО), .(1хШ(.Ох1)@(ОхО) (011) .

Можно построить аналогичным образом матрицы G размерности п х п для различных преобразований кодов, являющихся мультипликативными (2).

Преобразователь кодов работает следующим образом.

В исходном состоянии счетчик 1 обнулен. В блоке 2 памяти записана матрица преобразования G (например, (3) или (5). На информационный вход устройства поступают разряды кода , которые перемножаются с первой строкой матрицы G, которая поступает на вторые входы элементов И 3, и суммируются по модулю два сумматором 4, на выходе которого будет сформирован первый разряд кода X .. Далее по следующему тактовому импульсу счетчик 1 увеличит свое состояние на 1, на выход блока 2 памяти поступит следующая строка матрицы преобразования G и на выходе устройства будет сформирован следующий разряд кода Х- и т.д. По п-му такту на выходе сумматора 4 по модулю два будет сформирован последний разряд кода X . По следующему такту счетчик 1 обнуляется и на вход устройств

Редактор С. Патрушева Заказ 4055/56

Составитель М.Аршавский

Техред И.Попович Корректор G. Шекмар

Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

можно подавать следующий код d- и т.д.

Для формирования всех п-разрядов кода X необходимо присутствие на информационных входах устройства кода d в течение п тактов. . ...

Таким образом, предлагаемое устройство позволяет осуществлять пре- образование мультипликативных кодов, требуя для этого в п раз меньшего объема памяти по сравнению с известным.

Формула изобретения

Преобразователь кодов, содержащий блок памяти и сумматор по модулю два, отличающийся тем, что, с

целью упрощения устройства, он содержит группу элементов И и счетчик, тактовый вход которого является тактовым входом преобразователя, информационные входы которого соединены с

первыми входами соответствующих элементов И группы, вторые входы которых соединены с соответствующими выходами блока памяти, адресные входы которого соединены с соответствующими выходами счетчика, а выходы элементов И группы соединены с соответствующими входами сумматора по модулю два, выход которого является выходом преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор функций Уолша | 1986 |

|

SU1332304A1 |

| Устройство радиосвязи | 2019 |

|

RU2713921C1 |

| Кодек для передачи информации с помощью имитостойких последовательностей сигналов сложной формы | 1987 |

|

SU1451719A1 |

| Генератор функций Уолша | 1986 |

|

SU1341628A1 |

| Устройство для исправления отказов линейных преобразователей кодов | 1989 |

|

SU1702531A1 |

| СПОСОБ КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2326494C1 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Генератор систем базисных функций аристова | 1990 |

|

SU1753465A2 |

| Многоканальный систолический процессор для вычисления полиномиальных функций | 2020 |

|

RU2737236C1 |

| Декодер линейного систематического кода | 1987 |

|

SU1534756A1 |

Изобретение относится к области вычислительной техники и может быть использовано для преобразования табличных кодов. Целью изобретения яв- ляется упрощение устройства. Поставленная цель достигается тем, что в преобразователь кодов, содержащий блок памяти 2 и сумматор по модулю 4, введены счетчик 1 и группа элементов И 3, первые входы которых являются информационными входами преобразователя, вторые входы соединены с выходами блока памяти 2, адресные входы которого соединены с выходами счетчика 1, а выходы элементов И группы соединены с входами сумматора по модулю два 4. 1 ил. С « (Л со оо а to N

| Красноголовый Б.Н., Шпилевой Б.Н | |||

| Преобразователи кодов, Минск, изд-во БГУ, 1983, с | |||

| Железобетонный фасонный камень для кладки стен | 1920 |

|

SU45A1 |

| Двунаправленный преобразователь табличных кодов | 1983 |

|

SU1163480A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-09—Подача