Изобретение относится к вычислительной технике и может быть использовано в специализированных системах многоканальной цифровой обработки сигналов и в измерительно-вычислительных системах.

Известен систолический процессор для вычисления полиномиальных функций (Авторское свидетельство SU 1608689, МПК G06F 15/332 «Систолический процессор для вычисления полиномиальных функций»), содержащий информационный вход, входной регистр, коммутатор, систолическую матрицу из  (

( – размер преобразования) операционного блока, блок восстановления с информационным выходом, блок постоянной памяти коэффициентов, блок синхронизации с входом запуска, двумя тактовыми и одним информационным выходами.

– размер преобразования) операционного блока, блок восстановления с информационным выходом, блок постоянной памяти коэффициентов, блок синхронизации с входом запуска, двумя тактовыми и одним информационным выходами.

Недостатками известного систолического процессора для вычисления полиномиальных функций являются: низкая эффективность использования оборудования ( ) за счет простоя систолической матрицы на этапе загрузки исходных данных и, как следствие низкая скорость вычислений значений полиномиальных функций, низкая точность вычислений, обусловленная использованием схемы Горнера и возможность только одноканальной обработки поступающих данных.

) за счет простоя систолической матрицы на этапе загрузки исходных данных и, как следствие низкая скорость вычислений значений полиномиальных функций, низкая точность вычислений, обусловленная использованием схемы Горнера и возможность только одноканальной обработки поступающих данных.

Известен систолический процессор дискретного преобразования Фурье (Авторское свидетельство SU 1615741, МПК G06F 15/332 «Систолический процессор дискретного преобразования Фурье»), содержащий два  – канальных коммутатора (входной и выходной), операционный блок, блок постоянной памяти (взвешивающих множителей), группу из

– канальных коммутатора (входной и выходной), операционный блок, блок постоянной памяти (взвешивающих множителей), группу из  (

( – размер преобразования) операционного блока, блок постоянной памяти (весовых множителей), группу из

– размер преобразования) операционного блока, блок постоянной памяти (весовых множителей), группу из  блоков хранения, блок управления с тактовым входом и выходом, первым и вторым управляющими выходами, адресным выходом.

блоков хранения, блок управления с тактовым входом и выходом, первым и вторым управляющими выходами, адресным выходом.

Недостатками систолического процессора дискретного преобразования Фурье, взятого за прототип, являются низкая скорость (время выполнения операций умножения и сложения пропорционально разрядности обрабатываемых операндов) и точность вычисления значений полиномиальных функций при обработке целочисленных данных. Низкая точность вычислений связана с аддитивными и мультипликативными ошибками, возникающими при вычислениях.

Основной задачей предлагаемого изобретения является повышение скорости и точности многоканальных вычислений значений полиномиальных функций за счет применения системы остаточных классов (СОК).

Техническим результатом, достигнутым при осуществлении заявленного изобретения, является повышение скорости и точности многоканальной цифровой обработки сигналов за счет применения СОК.

Указанный технический результат достигается тем, что в предлагаемом изобретении реализуются вычисления с использованием параллельного непозиционного кода СОК. В данной системе вычисления осуществляются параллельно над малоразрядными остатками, определяемыми основаниями системы остаточных классов, что позволяет использовать ПЗУ для выполнения операций сложения и умножения, при этом, время выполнения этих операций будет определяться временем выборки из ПЗУ, что значительно меньше, чем в прототипе. Таким образом, распараллеливание на уровне арифметических операций и независимая обработка данных по основаниям СОК, реализуемая выборками из ПЗУ, повышает скорость цифровой обработки сигналов с использованием полиномиальных функций без аддитивных и мультипликативных ошибок.

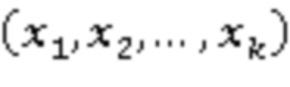

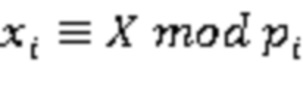

Для предотвращения аддитивных и мультипликативных ошибок и повышения скорости выполнения арифметических операций, в предлагаемом изобретении вычисления производятся с использованием кодов СОК. В СОК используются взаимно простые числа  , называемые основаниями и целое число

, называемые основаниями и целое число  представляется в виде набора остатков

представляется в виде набора остатков  , где

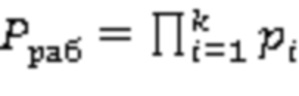

, где  . Произведение оснований

. Произведение оснований  определяет рабочий диапазон кода СОК:

определяет рабочий диапазон кода СОК:

. (1)

. (1)

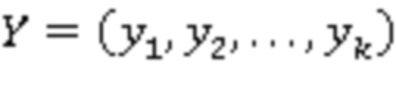

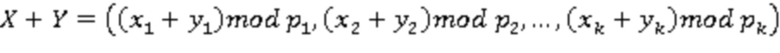

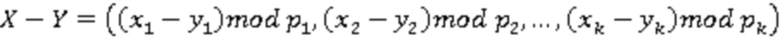

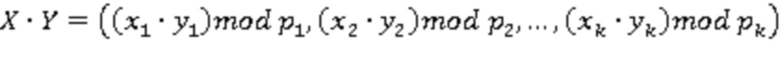

Для двух чисел  и

и  , представленных в коде СОК справедливы равенства:

, представленных в коде СОК справедливы равенства:

, (2)

, (2)

, (3)

, (3)

. (4)

. (4)

Анализ выражений (2) – (4) показывает, что за счет параллельных вычислений с малоразрядными остатками, использование кодов СОК предотвращает возникновение аддитивных и мультипликативных ошибок и повышает скорость выполнения арифметических операций.

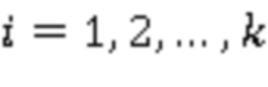

Восстановление результата, полученного в коде СОК до полного значения в позиционной системе счисления возможно на основе Китайской теоремы об остатках, утверждающей, что для любых значений чисел  , система уравнений:

, система уравнений:

, (5)

, (5)

где  – попарно взаимно-простые числа,

– попарно взаимно-простые числа,  , имеет единственное решение по

, имеет единственное решение по  (1). Это решение можно выразить в виде:

(1). Это решение можно выразить в виде:

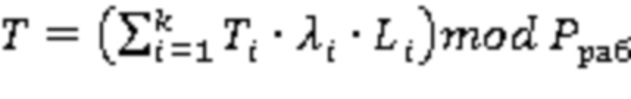

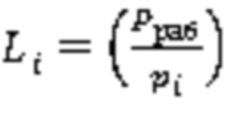

, (6)

, (6)

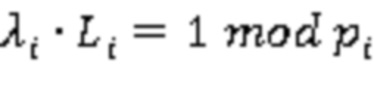

где  ,

,  и

и  находится из условия:

находится из условия:

. (7)

. (7)

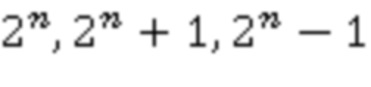

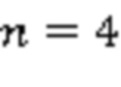

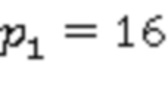

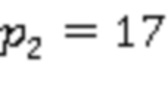

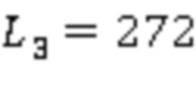

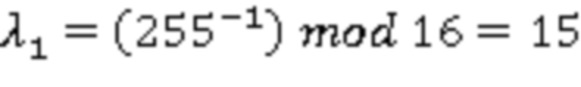

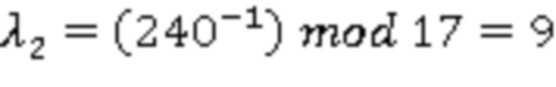

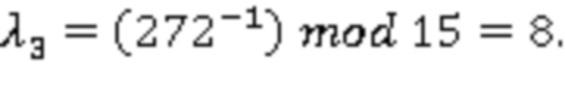

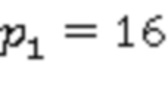

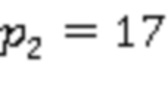

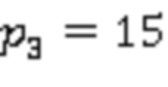

Для практических вычислений удобно использовать модули вида:  [см. Макклеллан Дж. Г., Рейдер Ч.М. Применение теории чисел в цифровой обработке сигналов: Пер. с англ./ Под ред. Ю.И. Манина. – М.: Радио и связь, 1983. – 264 с.]. Рассмотрим возможность перевода СОК-ПСС при

[см. Макклеллан Дж. Г., Рейдер Ч.М. Применение теории чисел в цифровой обработке сигналов: Пер. с англ./ Под ред. Ю.И. Манина. – М.: Радио и связь, 1983. – 264 с.]. Рассмотрим возможность перевода СОК-ПСС при  ,

,  ,

,  ,

,  и

и  , для чего вычислим

, для чего вычислим  ,

,  ,

,  . На основе (7) получаем:

. На основе (7) получаем:

;

;

;

;

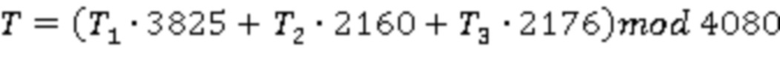

На основе (6) получим формулу преобразования СОК-ПСС для оснований  ,

,  ,

,  :

:

, (8)

, (8)

где  ,

,  ,

,  – вычеты числа

– вычеты числа  по модулям 16, 17 и 15 соответственно.

по модулям 16, 17 и 15 соответственно.

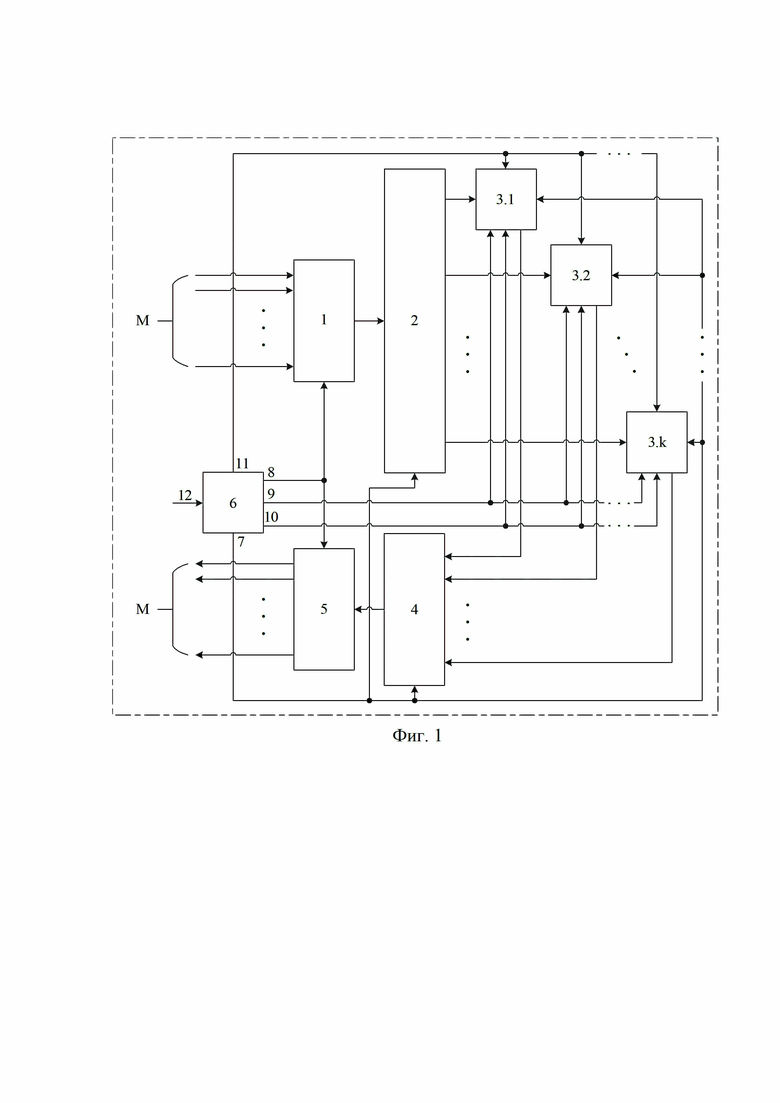

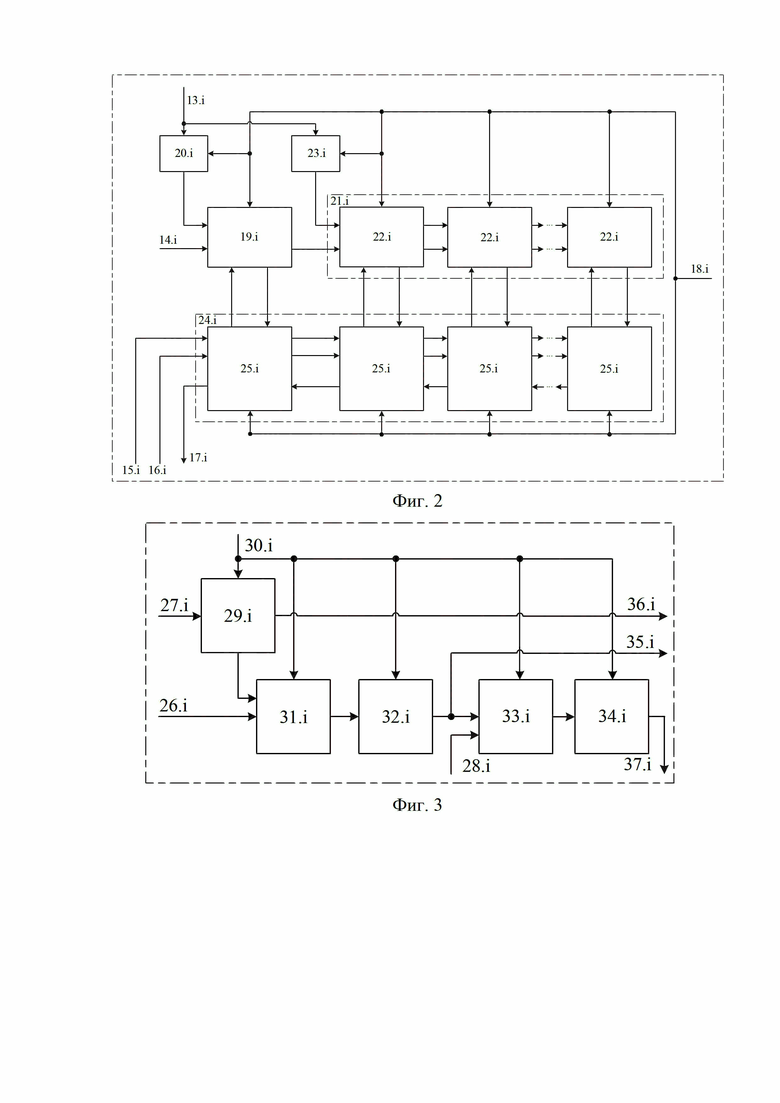

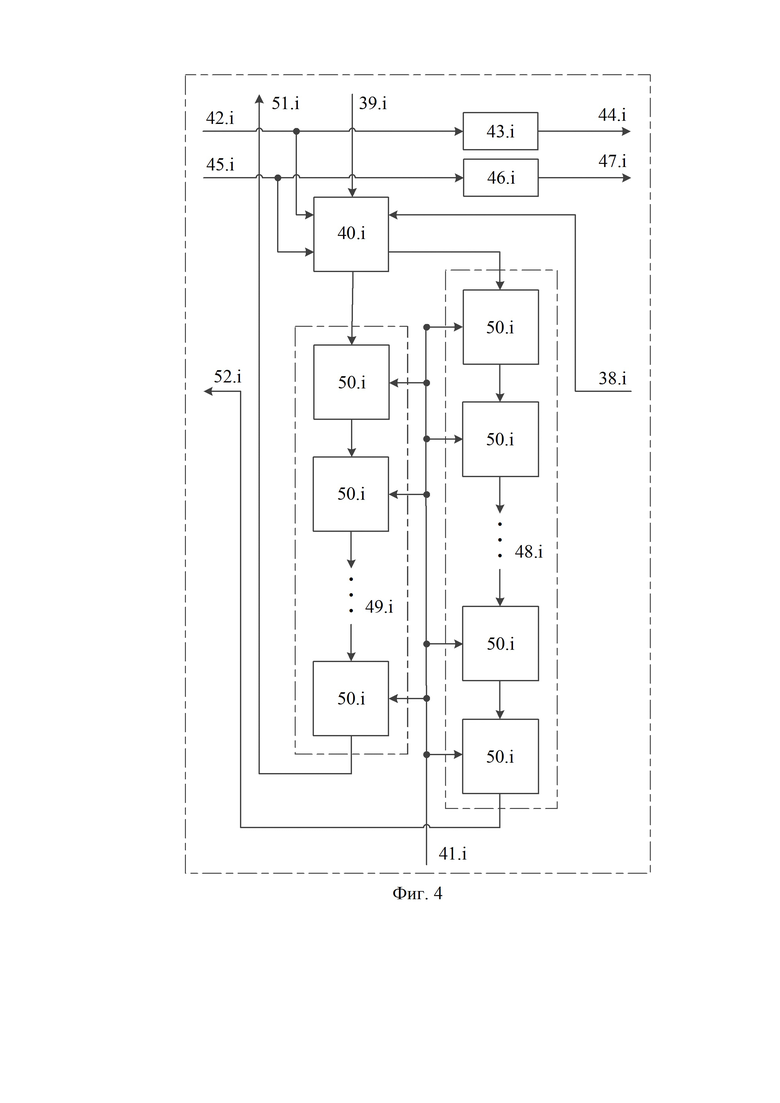

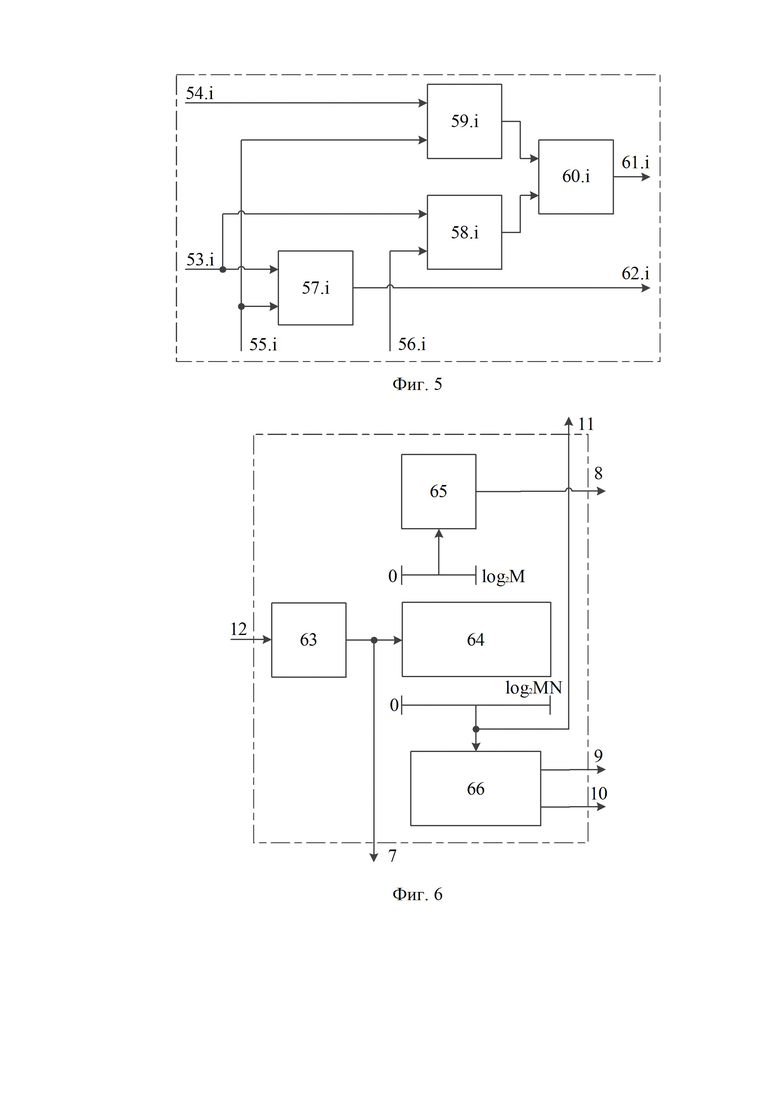

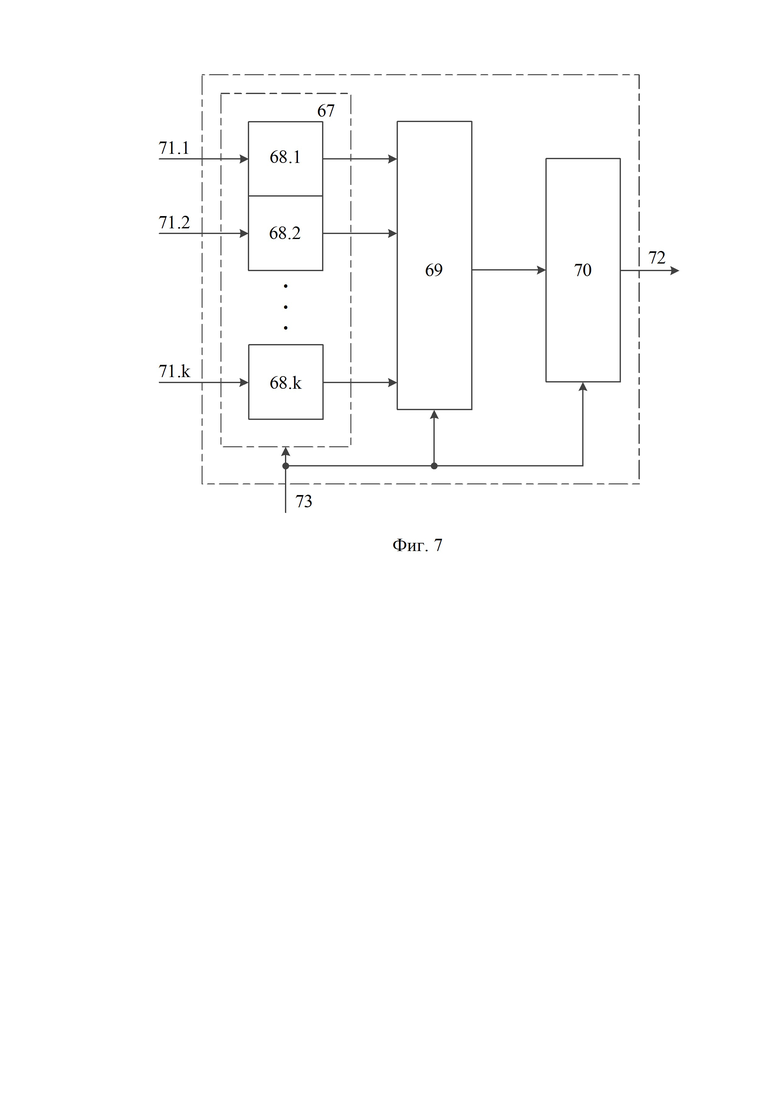

На фиг.1 представлена структурная схема многоканального систолического процессора для вычисления полиномиальных функций, на фиг.2 – структурная схема вычислительного тракта по модулю  , на фиг.3 – структурная схема операционного блока вычислительного тракта по модулю

, на фиг.3 – структурная схема операционного блока вычислительного тракта по модулю  , на фиг. 4 – структурная схема блока хранения вычислительного тракта, на фиг.5 – структурная схема коммутатора блока хранения, на фиг. 6 – структурная схема блока управления.

, на фиг. 4 – структурная схема блока хранения вычислительного тракта, на фиг.5 – структурная схема коммутатора блока хранения, на фиг. 6 – структурная схема блока управления.

В состав схемы многоканального систолического процессора для вычисления полиномиальных функций (фиг. 1) входят входной  – канальный коммутатор 1, преобразователь ПСС-СОК 2,

– канальный коммутатор 1, преобразователь ПСС-СОК 2,  вычислительных трактов 3.1 – 3.k по модулям

вычислительных трактов 3.1 – 3.k по модулям  , преобразователь СОК-ПСС 4, выходной

, преобразователь СОК-ПСС 4, выходной  – канальный коммутатор 5, блок 6 управления, тактовый выход 7 блока 6 управления, первый 8, второй 9 и третий 10 управляющие выходы блока 6 управления, адресный выход 11 блока 6 управления и тактовый вход 12.

– канальный коммутатор 5, блок 6 управления, тактовый выход 7 блока 6 управления, первый 8, второй 9 и третий 10 управляющие выходы блока 6 управления, адресный выход 11 блока 6 управления и тактовый вход 12.

Выход входного  – канального коммутатора 1 подключен к входу преобразователя ПСС-СОК 2, имеющего

– канального коммутатора 1 подключен к входу преобразователя ПСС-СОК 2, имеющего  выходов подключенных к информационным входам

выходов подключенных к информационным входам  вычислительных трактов 3.1 – 3.k по модулям

вычислительных трактов 3.1 – 3.k по модулям  , информационные выходы которых подключены к входам преобразователя СОК-ПСС 4, выход которого подключен к входу выходного

, информационные выходы которых подключены к входам преобразователя СОК-ПСС 4, выход которого подключен к входу выходного  – канального коммутатора 5, при этом, тактовый выход 7 блока 6 управления подключен к тактовым входам преобразователей ПСС-СОК 2, СОК-ПСС 4 и тактовым входам

– канального коммутатора 5, при этом, тактовый выход 7 блока 6 управления подключен к тактовым входам преобразователей ПСС-СОК 2, СОК-ПСС 4 и тактовым входам  вычислительных трактов 3.1 – 3.k по модулям

вычислительных трактов 3.1 – 3.k по модулям  , первый управляющий выход 8 подключен к управляющим входам входного и выходного

, первый управляющий выход 8 подключен к управляющим входам входного и выходного  – канальных коммутаторов 1 и 5, второй 9, третий 10 управляющие выходы и адресный выход 11 подключены к первым, вторым управляющим и адресным входам k вычислительных трактов 3.1 – 3.k по модулям

– канальных коммутаторов 1 и 5, второй 9, третий 10 управляющие выходы и адресный выход 11 подключены к первым, вторым управляющим и адресным входам k вычислительных трактов 3.1 – 3.k по модулям  соответственно.

соответственно.

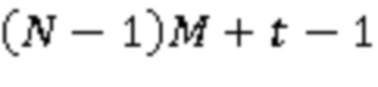

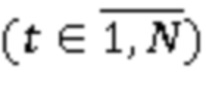

В состав схемы вычислительного тракта 3.i по модулю  , (фиг.2) входят адресный вход 13.i, информационный вход 14.i, первый 15.i и второй 16.i управляющие входы, информационный выход 17.i, тактовый вход 18.i, операционный блок 19.i, блок 20.i постоянной памяти (взвешивающих множителей), систолическая матрица 21.i из (

, (фиг.2) входят адресный вход 13.i, информационный вход 14.i, первый 15.i и второй 16.i управляющие входы, информационный выход 17.i, тактовый вход 18.i, операционный блок 19.i, блок 20.i постоянной памяти (взвешивающих множителей), систолическая матрица 21.i из ( ) – го операционного блока 22.i (

) – го операционного блока 22.i ( – размер преобразования), блок 23.i постоянной памяти (весовых множителей), группа 24.i из

– размер преобразования), блок 23.i постоянной памяти (весовых множителей), группа 24.i из  блоков 25.i хранения.

блоков 25.i хранения.

Адресный вход 13.i,  подключен к блокам 20.i и 23.i постоянной памяти (взвешивающих множителей и весовых множителей соответственно), выходы которых подключены к первым информационным входам операционного блока 19.i и первого операционного блока 22.i систолической матрицы 21.i. Информационный вход 14.i подключен к второму информационному входу операционного блока 19.i, второй выход которого подключен к второму информационному входу первого операционного блока 22.i систолической матрицы 21.i., третий выход подключен ко второму информационному входу первого блока 25.i хранения группы 24.i. Первый и второй выходы t – го (

подключен к блокам 20.i и 23.i постоянной памяти (взвешивающих множителей и весовых множителей соответственно), выходы которых подключены к первым информационным входам операционного блока 19.i и первого операционного блока 22.i систолической матрицы 21.i. Информационный вход 14.i подключен к второму информационному входу операционного блока 19.i, второй выход которого подключен к второму информационному входу первого операционного блока 22.i систолической матрицы 21.i., третий выход подключен ко второму информационному входу первого блока 25.i хранения группы 24.i. Первый и второй выходы t – го ( ) операционного блока 22.i систолической матрицы 21.i подключены к первому и второму информационным входам t

) операционного блока 22.i систолической матрицы 21.i подключены к первому и второму информационным входам t операционного блока 22.i систолической матрицы 21.i, , третьи выходы t – го (

операционного блока 22.i систолической матрицы 21.i, , третьи выходы t – го ( ) операционного блока 22.i систолической матрицы 21.i подключены ко вторым информационным входам t

) операционного блока 22.i систолической матрицы 21.i подключены ко вторым информационным входам t блока 25.i хранения группы 24.i. Третий выход первого блока 25.i хранения группы 24.i подключен к третьему информационному входу операционного блока 19.i, третий выход t – го (t

блока 25.i хранения группы 24.i. Третий выход первого блока 25.i хранения группы 24.i подключен к третьему информационному входу операционного блока 19.i, третий выход t – го (t ) блока 25.i хранения группы 24.i подключен к третьему информационному входу

) блока 25.i хранения группы 24.i подключен к третьему информационному входу  -го операционного блока 22.i систолической матрицы 21.i. Первый и второй выходы t – го (

-го операционного блока 22.i систолической матрицы 21.i. Первый и второй выходы t – го ( ) блока 25.i хранения группы 24.i подключены к первому и второму управляющим входам t

) блока 25.i хранения группы 24.i подключены к первому и второму управляющим входам t – го блока хранения 25.i группы 24.i. Четвертые выходы t – го (t

– го блока хранения 25.i группы 24.i. Четвертые выходы t – го (t ) блока 25.i хранения группы 24.i подключены к первым информационным входам t

) блока 25.i хранения группы 24.i подключены к первым информационным входам t – го блока хранения 25.i группы 24.i. Тактовый вход 18.i подключен к тактовым входам

– го блока хранения 25.i группы 24.i. Тактовый вход 18.i подключен к тактовым входам  блоков 25.i хранения группы 24.i, тактовым входам

блоков 25.i хранения группы 24.i, тактовым входам  операционного блока 22.i систолической матрицы 21.i, тактовому входу операционного блока 19.i, тактовым входам блоков 20.i и 23.i постоянной памяти. Первый 15.i и второй 16.i управляющие входы подключены к первому и второму управляющим входам первого блока 25.i хранения группы 24.i, четвертый выход которого подключен к информационному выходу 17.i вычислительного тракта 3.i по модулю

операционного блока 22.i систолической матрицы 21.i, тактовому входу операционного блока 19.i, тактовым входам блоков 20.i и 23.i постоянной памяти. Первый 15.i и второй 16.i управляющие входы подключены к первому и второму управляющим входам первого блока 25.i хранения группы 24.i, четвертый выход которого подключен к информационному выходу 17.i вычислительного тракта 3.i по модулю  .

.

В состав схемы операционного блока 19.i, 22.i вычислительного тракта по модулю  , (фиг.3) входят первый 27.i, второй 26.i и третий 28.i информационные входы, регистр 29.i, тактовый вход 30.i, умножитель 31.i, сумматор 33.i, два узла постоянной памяти 32.i, 34.i, первый 36.i, второй 35.i и третий 37.i выходы. В операционном блоке 19.i первый выход 36.i остается не подключенным к другим элементам схемы, в

, (фиг.3) входят первый 27.i, второй 26.i и третий 28.i информационные входы, регистр 29.i, тактовый вход 30.i, умножитель 31.i, сумматор 33.i, два узла постоянной памяти 32.i, 34.i, первый 36.i, второй 35.i и третий 37.i выходы. В операционном блоке 19.i первый выход 36.i остается не подключенным к другим элементам схемы, в  -м операционном блоке 22.i первый 36.i и второй 35.i выходы не связаны с другими элементами схемы.

-м операционном блоке 22.i первый 36.i и второй 35.i выходы не связаны с другими элементами схемы.

Второй информационный вход 26.i соединен с первым входом умножителя 31.i, вторым входом которого является первый выход регистра 29.i, второй выход которого является первым выходом 36.i операционного блока. Первый информационный вход 27.i соединен с входом регистра 29.i. Выход умножителя 31.i соединен с входом узла постоянной памяти 32.i, выход которого соединен с первым входом сумматора 33.i и вторым выходом 35.i операционного блока, третий информационный вход 28.i подключен к второму входу сумматора 33.i, выход которого соединен с входом узла постоянной памяти 34.i, выход которого соединен с третьим выходом 37.i операционного блока, тактовый вход 30.i подключен к регистру 29.i, умножителю 31.i, сумматору 33.i и узлам постоянной памяти 32.i, 34.i.

В состав схемы блока хранения вычислительного тракта 25.i,  , (фиг.4) входят первый 38.i и второй 39.i информационные входы, коммутатор 40.i, тактовый вход 41.i, первый 42.i и второй 45.i управляющие входы, элементы 43.i, 46.i задержки, первый 44.i и второй 47.i выходы, узлы 48.i и 49.i из

, (фиг.4) входят первый 38.i и второй 39.i информационные входы, коммутатор 40.i, тактовый вход 41.i, первый 42.i и второй 45.i управляющие входы, элементы 43.i, 46.i задержки, первый 44.i и второй 47.i выходы, узлы 48.i и 49.i из  и

и  регистров 50.i соответственно, третий 51.i и четвертый 52.i выходы.

регистров 50.i соответственно, третий 51.i и четвертый 52.i выходы.

Первый 38.i и второй 39.i информационные входы блока хранения 25.i подключены к коммутатору 40.i, выходы которого подключены к входам узлов 48.i и 49.i. Выход каждого t – го (t ) регистра 50.i узла 48.i подключен к входу t

) регистра 50.i узла 48.i подключен к входу t регистра 50.i узла 48.i из (M-1) регистра, выход каждого t – го (t

регистра 50.i узла 48.i из (M-1) регистра, выход каждого t – го (t регистра 50.i узла 49.i подключен к входу t

регистра 50.i узла 49.i подключен к входу t регистра 50.i узла 49.i из M регистров. Выход

регистра 50.i узла 49.i из M регистров. Выход  – го регистра 50.i узла 48.i является четвертым выходом 52.i блока хранения 25.i, выход

– го регистра 50.i узла 48.i является четвертым выходом 52.i блока хранения 25.i, выход  – го регистра 50.i узла 49.i является третьим выходом 51.i блока хранения 25.i. Первый управляющий вход 42.i подключен к первому управляющему входу коммутатора 40.i и элементу 43.i задержки, выход которого является первым 44.i выходом блока хранения 25.i, второй управляющий вход 45.i подключен к второму управляющему входу коммутатора 40.i и элементу 46.i задержки, выход которого является вторым 47.i выходом блока хранения 25.i. Тактовый вход 41.i блока хранения 25.i подключен к тактовым входам всех регистров 50.i узлов 48.i и 49.i.

– го регистра 50.i узла 49.i является третьим выходом 51.i блока хранения 25.i. Первый управляющий вход 42.i подключен к первому управляющему входу коммутатора 40.i и элементу 43.i задержки, выход которого является первым 44.i выходом блока хранения 25.i, второй управляющий вход 45.i подключен к второму управляющему входу коммутатора 40.i и элементу 46.i задержки, выход которого является вторым 47.i выходом блока хранения 25.i. Тактовый вход 41.i блока хранения 25.i подключен к тактовым входам всех регистров 50.i узлов 48.i и 49.i.

В состав схемы коммутатора 40.i блока хранения 25.i,  , (фиг.5) входят первый 53.i и второй 54.i вход данных, первый 55.i и второй 56.i управляющие входы, элементы «И» (используемые для разрешения/запрещения) 57.i – 59.i, элемент «ИЛИ» 60.i, первый 61.i и второй 62.i выходы.

, (фиг.5) входят первый 53.i и второй 54.i вход данных, первый 55.i и второй 56.i управляющие входы, элементы «И» (используемые для разрешения/запрещения) 57.i – 59.i, элемент «ИЛИ» 60.i, первый 61.i и второй 62.i выходы.

Первый вход данных 53.i коммутатора 40.i блока хранения 25.i подключен к информационным входам элементов «И» 57.i и 58.i, выходы которых являются вторым выходом 62.i коммутатора 40.i блока хранения 25.i и входом элемента «ИЛИ» 60.i соответственно. Второй вход данных 54.i коммутатора 40.i блока хранения 25.i подключен к информационному входу элемента «И» 59.i, выход которого подключен к входу элемента «ИЛИ» 60.i, выход которого является первым выходом 61.i коммутатора 40.i блока хранения 25.i. Первый управляющий вход 55.i коммутатора блока хранения подключен к управляющим входам элементов «И» 57.i и 59.i, второй управляющий вход 56.i коммутатора блока хранения подключен к управляющему входу элемента «И» 58.i.

В состав схемы блока 6 управления (фиг.6) входят генератор 63 тактовых импульсов,  – разрядный двоичный счетчик 64, первый 65 и второй 66 дешифраторы состояний счетчика.

– разрядный двоичный счетчик 64, первый 65 и второй 66 дешифраторы состояний счетчика.

Тактовый вход систолического процессора для вычисления полиномиальных функций 12 является тактовым входом генератора 63 тактовых импульсов, выход которого является тактовым выходом 7 блока 6 управления и подключен к  – разрядному двоичному счетчику 64,

– разрядному двоичному счетчику 64,  – выход которого подключен к первому дешифратору 65 состояний счетчика,

– выход которого подключен к первому дешифратору 65 состояний счетчика,  – выход которого подключен ко второму дешифратору 66 состояний счетчика и адресному выходу 11 блока 6 управления. Выход первого дешифратора 65 состояний счетчика является первым управляющим выходом 8 блока 6 управления, первый и второй выходы второго дешифратора 66 являются вторым 9 и третьим 10 управляющими выходами блока 6 управления.

– выход которого подключен ко второму дешифратору 66 состояний счетчика и адресному выходу 11 блока 6 управления. Выход первого дешифратора 65 состояний счетчика является первым управляющим выходом 8 блока 6 управления, первый и второй выходы второго дешифратора 66 являются вторым 9 и третьим 10 управляющими выходами блока 6 управления.

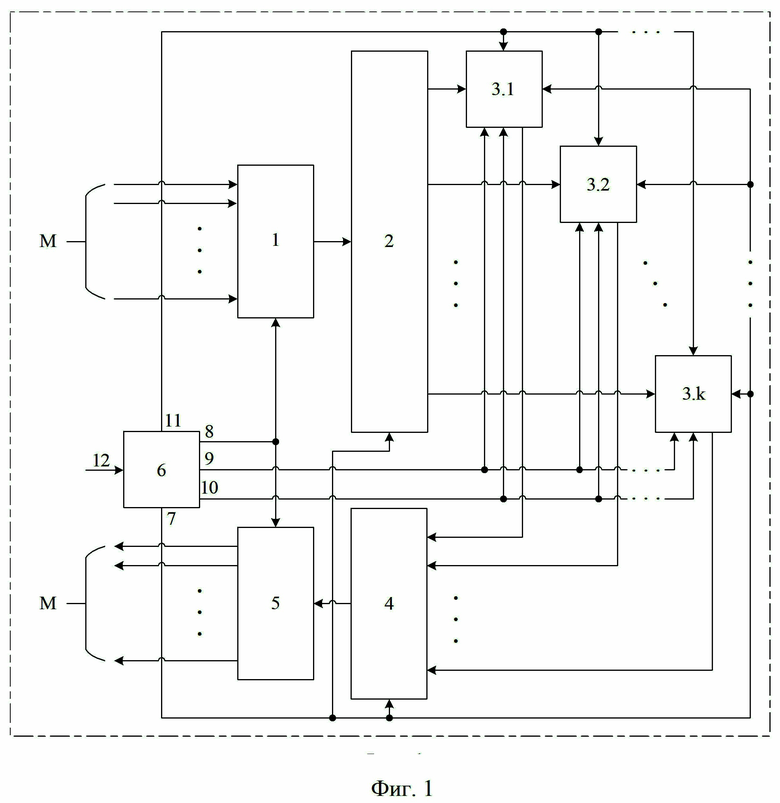

В состав схемы преобразователя СОК-ПСС 4 (фиг. 7) входят узел 67 постоянной памяти из k секций 68.1 – 68.k, k – входовый сумматор 69, узел 70 постоянной памяти, информационные входы 71.1 – 71.k, выход 72 и тактовый вход 73.

Информационные входы 71.1 – 71.k преобразователя СОК-ПСС 4 подключены к секциям 68.1 – 68.k узла 67 постоянной памяти, выходы которых подключены к входам  – входового сумматора 69, выход которого подключен к входу узла 70 постоянной памяти, выход которого является выходом 72 преобразователя СОК-ПСС 4, тактовый вход 73 которого соединен с входами разрешения считывания узла 67 постоянной памяти, k – входового сумматора 69 и узла постоянной памяти 70.

– входового сумматора 69, выход которого подключен к входу узла 70 постоянной памяти, выход которого является выходом 72 преобразователя СОК-ПСС 4, тактовый вход 73 которого соединен с входами разрешения считывания узла 67 постоянной памяти, k – входового сумматора 69 и узла постоянной памяти 70.

Таким образом, для достижения технического результата, в заявленное изобретение, содержащее входной и выходной M – канальные коммутаторы 1 и 5, блок управления 6 и один вычислительный тракт 3.i, где i=1, тактовый вход которого является тактовым выходом 7 блока управления 6, тактовый вход 12 которого является тактовым входом устройства, первый управляющий выход 8 блока управления 6 подключен к управляющим входам входного и выходного M – канальных коммутаторов, второй управляющий выход 9 и адресный выход 11 блока управления подсоединены соответственно к первому управляющему и адресному входам первого вычислительного тракта 3.i,который содержит операционный блок 19.i, два блока постоянной памяти (взвешивающих множителей) 20.i и (весовых множителей) 23.i соответственно, группу 24.i из  блоков хранения 25.i (

блоков хранения 25.i ( – размер преобразования) и систолическую матрицу 21.i из

– размер преобразования) и систолическую матрицу 21.i из  операционного блока 22.i, причем первый и второй выходы t-го (

операционного блока 22.i, причем первый и второй выходы t-го ( ) операционного блока 22.i систолической матрицы 21.i из

) операционного блока 22.i систолической матрицы 21.i из  операционного блока подключены соответственно к первому и второму информационным входам (t

операционного блока подключены соответственно к первому и второму информационным входам (t )-го операционного блока, тактовые входы всех операционных блоков 19.i и 22.i, блоков хранения 25.i группы 24.i из N блоков хранения и блоков постоянной памяти (взвешивающих множителей) 20.i и (весовых множителей) 23.i подключены к тактовому входу 18.i, соединённому с тактовым выходом 7 блока управления 6, адресный вход 13.i соединен с блоками постоянной памяти (взвешивающих множителей) 20.i и (весовых множителей) 23.i, выход блока постоянной памяти (взвешивающих множителей) 20.i подключен к первому информационному входу операционного блока 19.i, второй выход которого подключен ко второму информационному входу первого операционного блока 22.i систолической матрицы 21.i, первый информационный вход которого соединен с выходом блока постоянной памяти (весовых множителей) 23.i, третьи выходы всех операционных блоков 19.i и 22.i подключены ко вторым информационным входам соответствующих блоков хранения 25.i, третьи выходы которых подключены к третьим информационным входам соответствующих операционных блоков 19.i и 22.i, первый управляющий вход 15.i является первым управляющим входом первого блока хранения 25.i группы 24.i из N блоков хранения, первый выход t-го (

)-го операционного блока, тактовые входы всех операционных блоков 19.i и 22.i, блоков хранения 25.i группы 24.i из N блоков хранения и блоков постоянной памяти (взвешивающих множителей) 20.i и (весовых множителей) 23.i подключены к тактовому входу 18.i, соединённому с тактовым выходом 7 блока управления 6, адресный вход 13.i соединен с блоками постоянной памяти (взвешивающих множителей) 20.i и (весовых множителей) 23.i, выход блока постоянной памяти (взвешивающих множителей) 20.i подключен к первому информационному входу операционного блока 19.i, второй выход которого подключен ко второму информационному входу первого операционного блока 22.i систолической матрицы 21.i, первый информационный вход которого соединен с выходом блока постоянной памяти (весовых множителей) 23.i, третьи выходы всех операционных блоков 19.i и 22.i подключены ко вторым информационным входам соответствующих блоков хранения 25.i, третьи выходы которых подключены к третьим информационным входам соответствующих операционных блоков 19.i и 22.i, первый управляющий вход 15.i является первым управляющим входом первого блока хранения 25.i группы 24.i из N блоков хранения, первый выход t-го ( ) блока хранения 25.i подключен к первому управляющему входу (t+1)-го блока хранения 25.i, четвертый выход (t+1)-го блока хранения 25.i подключен к первому информационному входу выход t-го блока хранения 25.i, при этом операционные блоки содержат сумматор 33.i, умножитель 31.i и регистр 29.i, первый выход которого подключен к второму входу умножителя 31.i, второй выход регистра 29.i является первым выходом 36.i операционного блока, тактовый вход 30.i которого соединен с тактовым входом регистра 29.i и умножителя 31.i, первый информационный вход 27.i операционного блока подключен к входу регистра 29.i, второй информационный вход 26.i операционного блока является первым входом умножителя 31.i, третий информационный вход 28.i операционного блока является вторым входом сумматора 33.i, при этом каждый блок хранения 25.i группы 24.i из N блоков хранения содержит два узла 48.i и 49.i из (M-1) и M регистров 50.i соответственно, элемент задержки 43.i и коммутатор 40.i, выходы которого подключены к входам узлов из (M-1) 48.i и M 49.i регистров 50.i, тактовые входы которых соединены между собой и являются тактовым входом 41.i блока хранения 25.i, выход каждого t – го (t

) блока хранения 25.i подключен к первому управляющему входу (t+1)-го блока хранения 25.i, четвертый выход (t+1)-го блока хранения 25.i подключен к первому информационному входу выход t-го блока хранения 25.i, при этом операционные блоки содержат сумматор 33.i, умножитель 31.i и регистр 29.i, первый выход которого подключен к второму входу умножителя 31.i, второй выход регистра 29.i является первым выходом 36.i операционного блока, тактовый вход 30.i которого соединен с тактовым входом регистра 29.i и умножителя 31.i, первый информационный вход 27.i операционного блока подключен к входу регистра 29.i, второй информационный вход 26.i операционного блока является первым входом умножителя 31.i, третий информационный вход 28.i операционного блока является вторым входом сумматора 33.i, при этом каждый блок хранения 25.i группы 24.i из N блоков хранения содержит два узла 48.i и 49.i из (M-1) и M регистров 50.i соответственно, элемент задержки 43.i и коммутатор 40.i, выходы которого подключены к входам узлов из (M-1) 48.i и M 49.i регистров 50.i, тактовые входы которых соединены между собой и являются тактовым входом 41.i блока хранения 25.i, выход каждого t – го (t ) регистра 50.i узла 48.i из (M-1) регистра подключен к входу t

) регистра 50.i узла 48.i из (M-1) регистра подключен к входу t регистра 50.i узла 48.i из (M-1) регистра, выход каждого t – го (t

регистра 50.i узла 48.i из (M-1) регистра, выход каждого t – го (t регистра 50.i узла 49.i подключен к входу t

регистра 50.i узла 49.i подключен к входу t регистра 50.i узла 49.i из M регистров, первый управляющий вход 42.i подключен к первому управляющему входу коммутатора 40.i и входу элемента задержки 43.i, выход которого является первым выходом блока хранения 25.i, первый 38.i и второй 39.i информационные входы которого подключены к коммутатору 40.i, выход

регистра 50.i узла 49.i из M регистров, первый управляющий вход 42.i подключен к первому управляющему входу коммутатора 40.i и входу элемента задержки 43.i, выход которого является первым выходом блока хранения 25.i, первый 38.i и второй 39.i информационные входы которого подключены к коммутатору 40.i, выход  – го регистра 50.i узла 48.i из (M-1) регистра является четвертым выходом 52.i блока хранения 25.i, выход

– го регистра 50.i узла 48.i из (M-1) регистра является четвертым выходом 52.i блока хранения 25.i, выход  – го регистра 50.i узла 49.i из M регистров является третьим выходом 51.i блока хранения 25.i, , причем первый выход операционного блока 19.i, первый и второй выходы (N-1)-го операционного блока 22.i систолической матрицы 21.i, первый выход и первый информационный вход N-го блока хранения 25.i не соединены с другими элементами, введены преобразователь из позиционной системы счисления в систему остаточных классов (ПСС-СОК) 2, преобразователь из системы остаточных классов в позиционную систему счисления (СОК-ПСС) 4,

– го регистра 50.i узла 49.i из M регистров является третьим выходом 51.i блока хранения 25.i, , причем первый выход операционного блока 19.i, первый и второй выходы (N-1)-го операционного блока 22.i систолической матрицы 21.i, первый выход и первый информационный вход N-го блока хранения 25.i не соединены с другими элементами, введены преобразователь из позиционной системы счисления в систему остаточных классов (ПСС-СОК) 2, преобразователь из системы остаточных классов в позиционную систему счисления (СОК-ПСС) 4,  вычислительный тракт 3.i по модулю

вычислительный тракт 3.i по модулю  , причем выход входного M – канального коммутатора соединен с входом преобразователя ПСС-СОК 2, k выходов которого подключены к информационным входам вычислительных трактов 3.i по модулю

, причем выход входного M – канального коммутатора соединен с входом преобразователя ПСС-СОК 2, k выходов которого подключены к информационным входам вычислительных трактов 3.i по модулю  , информационные выходы которых подключены ко входам преобразователя СОК-ПСС 4, выход которого подключен к входу выходного

, информационные выходы которых подключены ко входам преобразователя СОК-ПСС 4, выход которого подключен к входу выходного  – канального коммутатора 4, тактовый выход 7 блока управления 6 подключен к тактовым входам преобразователя ПСС-СОК 2, преобразователя СОК-ПСС 4, вычислительных трактов 3.i по модулю

– канального коммутатора 4, тактовый выход 7 блока управления 6 подключен к тактовым входам преобразователя ПСС-СОК 2, преобразователя СОК-ПСС 4, вычислительных трактов 3.i по модулю  , адресный выход 11 и второй управляющий выход 9 блока 6 управления подключены соответственно к адресным и первым управляющим входам вычислительных трактов 3.i по модулю

, адресный выход 11 и второй управляющий выход 9 блока 6 управления подключены соответственно к адресным и первым управляющим входам вычислительных трактов 3.i по модулю  , третий управляющий выход 10 блока управления 6 подключен ко вторым управляющим входам вычислительных трактов 3.i по модулю

, третий управляющий выход 10 блока управления 6 подключен ко вторым управляющим входам вычислительных трактов 3.i по модулю  , в вычислительных трактах 3.i по модулю

, в вычислительных трактах 3.i по модулю  информационный вход 14.i подключен ко второму информационному входу операционного блока 19.i, второй управляющий вход 16.i и информационный выход 17.i вычислительного тракта 3.i по модулю

информационный вход 14.i подключен ко второму информационному входу операционного блока 19.i, второй управляющий вход 16.i и информационный выход 17.i вычислительного тракта 3.i по модулю  подключены соответственно ко второму управляющему входу и четвертому выходу первого блока хранения 25.i группы из N блоков хранения 24.i, второй выход t-го блока хранения 25.i (

подключены соответственно ко второму управляющему входу и четвертому выходу первого блока хранения 25.i группы из N блоков хранения 24.i, второй выход t-го блока хранения 25.i ( ) подключен к второму управляющему входу (t+1)-го блока хранения 25.i, второй выход N-го блока хранения 25.i не соединен с другими элементами, во все операционные блоки 19.i и 22.i вычислительных трактов по модулю

) подключен к второму управляющему входу (t+1)-го блока хранения 25.i, второй выход N-го блока хранения 25.i не соединен с другими элементами, во все операционные блоки 19.i и 22.i вычислительных трактов по модулю  введены по два узла постоянный памяти 32.i и 34.i, причем выход умножителя 31.i операционного блока подключен к входу узла постоянной памяти 32.i, хранящего вычеты всех возможных произведений по модулям

введены по два узла постоянный памяти 32.i и 34.i, причем выход умножителя 31.i операционного блока подключен к входу узла постоянной памяти 32.i, хранящего вычеты всех возможных произведений по модулям  ,

,  , выход которого подключен ко второму выходу 35.i операционного блока и первому входу сумматора 33.i, выход которого подключен к входу узла постоянной памяти 34.i, хранящего вычеты всех возможных сумм по модулям

, выход которого подключен ко второму выходу 35.i операционного блока и первому входу сумматора 33.i, выход которого подключен к входу узла постоянной памяти 34.i, хранящего вычеты всех возможных сумм по модулям  ,

,  , выход которого является третьим выходом 37.i операционного блока, тактовый вход 30.i которого дополнительно подключен к тактовым входам двух узлов постоянной памяти 32.i и 34.i и сумматора 33.i, во все блоки хранения вычислительных трактов по модулю

, выход которого является третьим выходом 37.i операционного блока, тактовый вход 30.i которого дополнительно подключен к тактовым входам двух узлов постоянной памяти 32.i и 34.i и сумматора 33.i, во все блоки хранения вычислительных трактов по модулю  введен элемент задержки 46.i, выход которого является вторым выходом 47.i блока хранения 25.i, а вход соединен со вторым управляющим входом коммутатора 40.i блока хранения 25.i и подключен ко второму управляющему входу 45.i блока хранения 25.i.

введен элемент задержки 46.i, выход которого является вторым выходом 47.i блока хранения 25.i, а вход соединен со вторым управляющим входом коммутатора 40.i блока хранения 25.i и подключен ко второму управляющему входу 45.i блока хранения 25.i.

Многоканальный систолический процессор для вычисления полиномиальных функций работает следующим образом.

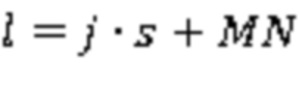

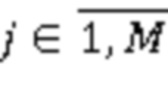

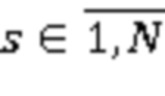

Пусть  входных параллельных потоков данных формируются так, что в течение очередных

входных параллельных потоков данных формируются так, что в течение очередных  тактов времени на вход процессора поступает по одному отсчету данных в каждый такт, при этом последовательно поступают

тактов времени на вход процессора поступает по одному отсчету данных в каждый такт, при этом последовательно поступают  отсчетов данных

отсчетов данных  от каждого из

от каждого из  каналов – источников данных

каналов – источников данных  , где j – номер канала данных, s – номер отсчета данных канала,

, где j – номер канала данных, s – номер отсчета данных канала,  – длина входной последовательности (число отсчетов) обрабатываемых данных по каждому каналу.

– длина входной последовательности (число отсчетов) обрабатываемых данных по каждому каналу.

Отсчеты данных  поступают на входы входного

поступают на входы входного  – канального коммутатора 1, управляющий вход которого соединен с первым управляющим выходом 8 блока 6 управления, являющегося выходом первого дешифратора 65 состояний счетчика 64. В результате на

– канального коммутатора 1, управляющий вход которого соединен с первым управляющим выходом 8 блока 6 управления, являющегося выходом первого дешифратора 65 состояний счетчика 64. В результате на  – м такте работы

– м такте работы  s – й отсчет данных от j – го канала передается с входа входного M – канального коммутатора 1 на его выход и далее на вход преобразователя ПСС-СОК 2.

s – й отсчет данных от j – го канала передается с входа входного M – канального коммутатора 1 на его выход и далее на вход преобразователя ПСС-СОК 2.

Преобразователь ПСС-СОК 2 осуществляет перевод отсчетов данных  в СОК по модулям

в СОК по модулям  . Переведенные отсчеты

. Переведенные отсчеты  поступают для обработки на информационные входы

поступают для обработки на информационные входы  вычислительных трактов 3.1 – 3.k по модулям

вычислительных трактов 3.1 – 3.k по модулям  .

.

Блоки 20.i,  постоянной памяти (взвешивающих множителей) емкостью

постоянной памяти (взвешивающих множителей) емкостью  слов имеют страничную организацию из

слов имеют страничную организацию из  страниц по

страниц по  слов. В каждой странице блока 20.i записаны взвешивающие множители для отсчетов данных

слов. В каждой странице блока 20.i записаны взвешивающие множители для отсчетов данных  , где

, где  , а

, а  – порядковый номер страницы. Для обращения к блокам 20.i по адресному выходу 11 блока 6 управления на адресный вход 13.i вычислительного тракта 3.i по модулю

– порядковый номер страницы. Для обращения к блокам 20.i по адресному выходу 11 блока 6 управления на адресный вход 13.i вычислительного тракта 3.i по модулю  передается

передается  – разрядный адрес.

– разрядный адрес.

Блоки 23.i,  постоянной памяти (весовых множителей) имеет емкость

постоянной памяти (весовых множителей) имеет емкость  слов, для обращения к ним требуется

слов, для обращения к ним требуется  – двоичный адрес, что достигается подключением старших

– двоичный адрес, что достигается подключением старших  – разрядов адресного выхода 11 блока 6 управления к адресным входам вычислительных трактов 3.i.

– разрядов адресного выхода 11 блока 6 управления к адресным входам вычислительных трактов 3.i.

Перед началом работы процессора  – разрядный двоичный счетчик 64 блока управления 6 обнулен и тем самым на управляющих входах 55.i и 56.i,

– разрядный двоичный счетчик 64 блока управления 6 обнулен и тем самым на управляющих входах 55.i и 56.i,  коммутаторов 40.i всех блоков хранения 25.i поступают управляющие сигналы, обнуляющие все регистры 50.i узлов 48.i и 49.i из (M-1) и M регистров соответственно, памяти FIFO.

коммутаторов 40.i всех блоков хранения 25.i поступают управляющие сигналы, обнуляющие все регистры 50.i узлов 48.i и 49.i из (M-1) и M регистров соответственно, памяти FIFO.

На первые информационные входы 27.i операционных блоков 19.i вычислительных трактов 3.i по модулям  поступают с выходов блоков 20.i постоянной памяти (взвешивающих множителей) отсчеты весовой функции «окна» с тем же темпом и синхронно с отсчетами обрабатываемых данных

поступают с выходов блоков 20.i постоянной памяти (взвешивающих множителей) отсчеты весовой функции «окна» с тем же темпом и синхронно с отсчетами обрабатываемых данных  .

.

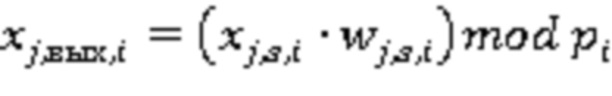

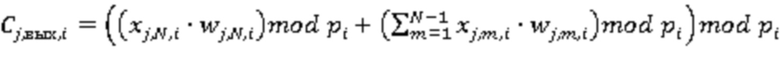

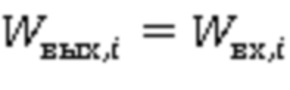

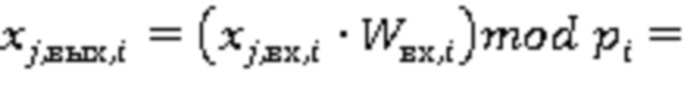

Операционные блоки 19.i вычислительных трактов 3.i по модулям  реализуют в СОК операции вида:

реализуют в СОК операции вида:

, (9)

, (9)

, (10)

, (10)

где  – соответствующий взвешивающий множитель,

– соответствующий взвешивающий множитель,  .Текущие суммы вида

.Текущие суммы вида  в выражении (10) накапливаются в первых блоках 25.i хранения групп 24.i операционных блоков 3.i. Значения

в выражении (10) накапливаются в первых блоках 25.i хранения групп 24.i операционных блоков 3.i. Значения  ,

,  передаются на вторые информационные входы первых операционных блоков 22.i систолических матриц 21.i, на вторые информационные входы которых поступают весовые множители

передаются на вторые информационные входы первых операционных блоков 22.i систолических матриц 21.i, на вторые информационные входы которых поступают весовые множители  ,

,  от блоков 23.i постоянной памяти (весовых множителей) с тем же темпом и синхронно с отсчетами

от блоков 23.i постоянной памяти (весовых множителей) с тем же темпом и синхронно с отсчетами  .

.

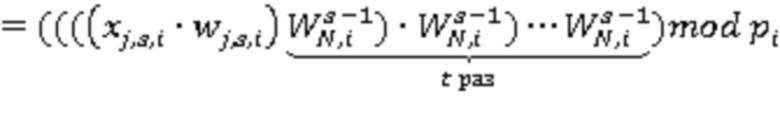

В операционных блоках 22.i с номерами t  систолических матриц 21.i и связанными с ними блоками 25.i хранения с номерами t

систолических матриц 21.i и связанными с ними блоками 25.i хранения с номерами t реализуются функции:

реализуются функции:

, (11)

, (11)

, (12)

, (12)

. (13)

. (13)

Текущее значение суммы в выражении (13) накапливается в блоках 25.i хранения с номерами t . Тем самым, операционные блоки 19.i, операционные блоки 22.i систолических матриц 21.i и связанных с ними блоков 25.i групп 24.i реализуют в совокупности вычисления одномерных полиномиальных функций с предварительным взвешиванием отсчетов исходных данных по выражению:

. Тем самым, операционные блоки 19.i, операционные блоки 22.i систолических матриц 21.i и связанных с ними блоков 25.i групп 24.i реализуют в совокупности вычисления одномерных полиномиальных функций с предварительным взвешиванием отсчетов исходных данных по выражению:

. (14)

. (14)

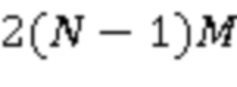

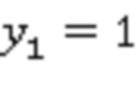

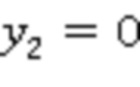

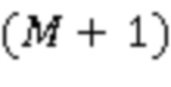

Данное выражение вычисляется в процессоре за  тактов. При этом, в течение первых

тактов. При этом, в течение первых  тактов в узлах 49.i регистров 50.i блоков 25.i хранения с номерами t

тактов в узлах 49.i регистров 50.i блоков 25.i хранения с номерами t  осуществляется накопление текущей суммы в соответствии с выражениями (10) и (13). В течение всего данного промежутка времени со второго 9 и третьего 10 управляющих выходов блока 6 управления на первые 55.i и вторые 56.i управляющие входы коммутаторов 40.i блоков 25.i хранения с номерами t присутствуют сигналы

осуществляется накопление текущей суммы в соответствии с выражениями (10) и (13). В течение всего данного промежутка времени со второго 9 и третьего 10 управляющих выходов блока 6 управления на первые 55.i и вторые 56.i управляющие входы коммутаторов 40.i блоков 25.i хранения с номерами t присутствуют сигналы  ,

,  , сформированные вторым дешифратором 66 состояний счетчика 64 блока 6 управления.

, сформированные вторым дешифратором 66 состояний счетчика 64 блока 6 управления.

Операции умножения и сложения в СОК реализуются в умножителях 31.i и сумматорах 33.i операционных блоков 19.i, 22.i. Нахождение вычетов по модулям  ,

,  производится в соответствии с принципами табличной арифметики посредством обращения к узлам постоянной памяти 32.i, 34.i. В узлах постоянной памяти 32.i и 34.i хранятся вычеты всех возможных произведений и сумм по модулям

производится в соответствии с принципами табличной арифметики посредством обращения к узлам постоянной памяти 32.i, 34.i. В узлах постоянной памяти 32.i и 34.i хранятся вычеты всех возможных произведений и сумм по модулям  ,

,  соответственно.

соответственно.

Данные со вторых 39.i информационных входов t – блоков 25.i хранения  поступают в коммутаторы 40.i и далее, на входы первых регистров 50.i узлов 49.i. Данные, являющиеся частичными суммами в выражениях (10) и (13), последовательно переписываются из регистра в регистр узлов 49.i. С выходов последних регистров 50.i узлов 49.i данные поступают на третьи 51.i выходы блоков 25.i хранения, далее на третьи информационные входы 28.i соответствующих операционных блоков 22.i систолических матриц 21.i (при

поступают в коммутаторы 40.i и далее, на входы первых регистров 50.i узлов 49.i. Данные, являющиеся частичными суммами в выражениях (10) и (13), последовательно переписываются из регистра в регистр узлов 49.i. С выходов последних регистров 50.i узлов 49.i данные поступают на третьи 51.i выходы блоков 25.i хранения, далее на третьи информационные входы 28.i соответствующих операционных блоков 22.i систолических матриц 21.i (при  ) или на третьи информационные входы 28.i операционных блоков 19.i (при

) или на третьи информационные входы 28.i операционных блоков 19.i (при  ).

).

В течение следующих  тактов работы процессора, в операционных блоках 19.i и 22.i с номерами

тактов работы процессора, в операционных блоках 19.i и 22.i с номерами

систолических матриц 21.i формируются окончательные результаты в соответствии с выражениями (10) и (13). Каждый результат

систолических матриц 21.i формируются окончательные результаты в соответствии с выражениями (10) и (13). Каждый результат  поступает в первые регистры 50.i узлов 48.i соответствующих блоков 25.i хранения, поскольку на

поступает в первые регистры 50.i узлов 48.i соответствующих блоков 25.i хранения, поскольку на  – м такте работы, вторым дешифратором 66 состояний счетчика 64 блока управления 6 формируются управляющие сигналы

– м такте работы, вторым дешифратором 66 состояний счетчика 64 блока управления 6 формируются управляющие сигналы  ,

,  , которые сохраняются до такта

, которые сохраняются до такта  с начала обработки данных

с начала обработки данных  в процессоре. При этом, данные, поступающие на вторые информационные входы 39.i блоков хранения 25.i через коммутаторы 40.i поступают на входы первого регистра 50.i узлов 48.i.

в процессоре. При этом, данные, поступающие на вторые информационные входы 39.i блоков хранения 25.i через коммутаторы 40.i поступают на входы первого регистра 50.i узлов 48.i.

Поскольку каждый операционный блок 22.i систолических матриц 21.i включается в работу тактом позже, то через  тактов с начала переключения узлов 48.i и 49.i, заполняются все регистры 50.i узлов 48.i первых блоков хранения 25.i, через

тактов с начала переключения узлов 48.i и 49.i, заполняются все регистры 50.i узлов 48.i первых блоков хранения 25.i, через  тактов – вторых блоков хранения 25.i и далее до блока 25.i с номером

тактов – вторых блоков хранения 25.i и далее до блока 25.i с номером  . Входы узлов 49.i блоков хранения 25.i при этом отключены от коммутаторов 40.i и содержимое регистров 50.i узлов 49.i за этот период обнуляется.

. Входы узлов 49.i блоков хранения 25.i при этом отключены от коммутаторов 40.i и содержимое регистров 50.i узлов 49.i за этот период обнуляется.

Начиная с такта  (на

(на  – такте после переключения выходов коммутаторов между узлами 48.i и 49.i), производится вывод результатов

– такте после переключения выходов коммутаторов между узлами 48.i и 49.i), производится вывод результатов  ,

,  с четвертых выходов 52.i первых блоков хранения 25.i группы 24.i, который занимает

с четвертых выходов 52.i первых блоков хранения 25.i группы 24.i, который занимает  тактов. Выводимые отсчеты

тактов. Выводимые отсчеты  , полученные в СОК, поступают на информационные выходы 17.i вычислительных трактов 3.i по модулю

, полученные в СОК, поступают на информационные выходы 17.i вычислительных трактов 3.i по модулю  и далее на информационные входы 71.1 – 71.k преобразователя СОК-ПСС 4. В последнем реализуется операция, соответствующая выражению (6). В основу работы преобразователя СОК-ПСС положен принцип табличной арифметики. В k – секционном узле 67 постоянной памяти хранятся всевозможные произведения вычетов на нормирующие множители, взятые по модулю

и далее на информационные входы 71.1 – 71.k преобразователя СОК-ПСС 4. В последнем реализуется операция, соответствующая выражению (6). В основу работы преобразователя СОК-ПСС положен принцип табличной арифметики. В k – секционном узле 67 постоянной памяти хранятся всевозможные произведения вычетов на нормирующие множители, взятые по модулю  (1) в соответствии с выражением (6). С выходов секций 68.1 – 68.k указанные произведения поступают на входы k – входового сумматора 69 и с его выхода сформированная сумма поступает на вход узла 70 постоянной памяти, в котором хранятся вычеты полученной суммы по модулю

(1) в соответствии с выражением (6). С выходов секций 68.1 – 68.k указанные произведения поступают на входы k – входового сумматора 69 и с его выхода сформированная сумма поступает на вход узла 70 постоянной памяти, в котором хранятся вычеты полученной суммы по модулю  (1). Таким образом, на выходе 72 преобразователя СОК-ПСС 4 получен результат, сформированный в позиционной системе счисления. Полученный результат поступает на вход выходного

(1). Таким образом, на выходе 72 преобразователя СОК-ПСС 4 получен результат, сформированный в позиционной системе счисления. Полученный результат поступает на вход выходного  – канального коммутатора 5 и далее в выводные каналы данных. При этом, выходной

– канального коммутатора 5 и далее в выводные каналы данных. При этом, выходной  – канальный коммутатор 5 управляется управляющими сигналами от первого дешифратора 65 счетчика 64 блока 6 управления, представляющими собой унитарный

– канальный коммутатор 5 управляется управляющими сигналами от первого дешифратора 65 счетчика 64 блока 6 управления, представляющими собой унитарный  – разрядный код. В результате на каждом

– разрядный код. В результате на каждом  – м такте (

– м такте ( , где

, где  ,

,  ) отсчет результата

) отсчет результата  передается в j – й выходной канал.

передается в j – й выходной канал.

На такте  с начала вывода данных, коммутаторы 40.i первых блоков 25.i хранения групп 24.i подключают к первым информационным входам 38.i данного блока 25.i четвертые выходы 52.i второго блока хранения 25.i группы 24.i. Это осуществляется поступлением на управляющие входы 55.i и 56.i коммутаторов 40.i управляющих сигналов

с начала вывода данных, коммутаторы 40.i первых блоков 25.i хранения групп 24.i подключают к первым информационным входам 38.i данного блока 25.i четвертые выходы 52.i второго блока хранения 25.i группы 24.i. Это осуществляется поступлением на управляющие входы 55.i и 56.i коммутаторов 40.i управляющих сигналов  ,

,  , сформированных вторым дешифратором 66 состояний счетчика 64. При этом наборе управляющих сигналов

, сформированных вторым дешифратором 66 состояний счетчика 64. При этом наборе управляющих сигналов  и

и  данные поступают на вторые входы данных 54.i коммутаторов 40.i и с первых выходов 61.i в первые регистры 50.i узлов 48.i. Одновременно с этим, данные со вторых информационных входов 39.i блоков 25.i хранения поступают на первые входы данных 53.i коммутаторов 40.i блоков хранения 25.i и со вторых выходов 62.i в первые регистры 50.i узлов 49.i.

данные поступают на вторые входы данных 54.i коммутаторов 40.i и с первых выходов 61.i в первые регистры 50.i узлов 48.i. Одновременно с этим, данные со вторых информационных входов 39.i блоков 25.i хранения поступают на первые входы данных 53.i коммутаторов 40.i блоков хранения 25.i и со вторых выходов 62.i в первые регистры 50.i узлов 49.i.

Далее аналогичные переключения осуществляются в t – м  блоке 25.i хранения группы 24.i,

блоке 25.i хранения группы 24.i,  . При этом, третьи выходы 37.i соответствующих операционных блоков 22.i подключаются коммутаторами 40.i в первые регистры 50.i узлов 49.i, а первые регистры 50.i узлов 48.i в данных блоках оказываются подключенным к четвертым выходам 52.i следующих

. При этом, третьи выходы 37.i соответствующих операционных блоков 22.i подключаются коммутаторами 40.i в первые регистры 50.i узлов 49.i, а первые регистры 50.i узлов 48.i в данных блоках оказываются подключенным к четвертым выходам 52.i следующих  блоков 25.i

блоков 25.i  .

.

Таким образом, в течение следующих  тактов, считая с начала вывода результатов, осуществляется вывод всех сформированных результатов

тактов, считая с начала вывода результатов, осуществляется вывод всех сформированных результатов  . Узлы 48.i всех блоков хранения 25.i при этом оказываются последовательно подключенными один за другим, образуя единую память типа FIFO емкостью

. Узлы 48.i всех блоков хранения 25.i при этом оказываются последовательно подключенными один за другим, образуя единую память типа FIFO емкостью  регистров. Одновременно в узлах 49.i накапливаются текущие суммы в соответствии с выражениями (10) и (13) для вновь поступающих последовательностей данных

регистров. Одновременно в узлах 49.i накапливаются текущие суммы в соответствии с выражениями (10) и (13) для вновь поступающих последовательностей данных

по всем входным каналам, тем самым в предлагаемом многоканальном процессоре отсутствуют паузы на ввод/вывод данных и вычисления осуществляются в системе остаточных классов.

по всем входным каналам, тем самым в предлагаемом многоканальном процессоре отсутствуют паузы на ввод/вывод данных и вычисления осуществляются в системе остаточных классов.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТОЛИЧЕСКИЙ ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1992 |

|

RU2029437C1 |

| СИСТОЛИЧЕСКИЙ ПРОЦЕССОР ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ С КОРРЕКЦИЕЙ ОШИБКИ | 1992 |

|

RU2018950C1 |

| Систолический процессор дискретного преобразования Фурье | 1989 |

|

SU1615741A1 |

| СИСТОЛИЧЕСКИЙ ПРОЦЕССОР ДЛЯ ВЫЧИСЛЕНИЯ ПОЛИНОМИАЛЬНЫХ ФУНКЦИЙ | 1991 |

|

RU2015549C1 |

| Систолический процессор для вычисления полиномиальных функций | 1988 |

|

SU1608689A1 |

| Систолический процессор цифровой обработки сигналов | 1987 |

|

SU1471200A1 |

| Способ построения системы опознавания "свой-чужой" на основе протокола с нулевым разглашением, реализованный в модулярном коде | 2018 |

|

RU2713511C1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1988 |

|

SU1571594A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных системах многоканальной цифровой обработки сигналов и в измерительно-вычислительных системах. В предлагаемом изобретении реализуются вычисления с использованием параллельного непозиционного кода СОК. В данной системе вычисления осуществляются параллельно над малоразрядными остатками, определяемыми основаниями системы остаточных классов, что позволяет использовать ПЗУ для выполнения операций сложения и умножения, при этом время выполнения этих операций будет определяться временем выборки из ПЗУ. Таким образом, распараллеливание на уровне арифметических операций и независимая обработка данных по основаниям СОК, реализуемая выборками из ПЗУ, повышает скорость цифровой обработки сигналов с использованием полиномиальных функций без аддитивных и мультипликативных ошибок. Изобретение направлено на повышение скорости и точности многоканальной цифровой обработки сигналов за счет применения системы остаточных классов (СОК). 7 ил.

Многоканальный систолический процессор для вычисления полиномиальных функций, содержащий входной и выходной M – канальные коммутаторы, блок управления и один вычислительный тракт 3.i, где i=1, тактовый вход которого является тактовым выходом блока управления, тактовый вход которого является тактовым входом устройства, первый управляющий выход блока управления подключен к управляющим входам входного и выходного M – канальных коммутаторов, второй управляющий выход и адресный выход блока управления подсоединены соответственно к первому управляющему и адресному входам первого вычислительного тракта, который содержит операционный блок, два блока постоянной памяти (взвешивающих множителей) и (весовых множителей) соответственно, группу из  блоков хранения (

блоков хранения ( – размер преобразования) и систолическую матрицу из

– размер преобразования) и систолическую матрицу из  операционного блока, причем первый и второй выходы t-го (

операционного блока, причем первый и второй выходы t-го ( ) операционного блока систолической матрицы из

) операционного блока систолической матрицы из  операционного блока подключены соответственно к первому и второму информационным входам (t

операционного блока подключены соответственно к первому и второму информационным входам (t )-го операционного блока, тактовые входы всех операционных блоков, блоков хранения группы из N блоков хранения и блоков постоянной памяти (взвешивающих множителей) и (весовых множителей) подключены к тактовому входу, соединённому с тактовым выходом блока управления, адресный вход соединен с блоками постоянной памяти (взвешивающих множителей) и (весовых множителей), выход блока постоянной памяти (взвешивающих множителей) подключен к первому информационному входу операционного блока, второй выход которого подключен ко второму информационному входу первого операционного блока систолической матрицы, первый информационный вход которого соединен с выходом блока постоянной памяти (весовых множителей), третьи выходы всех операционных блоков подключены ко вторым информационным входам соответствующих блоков хранения, третьи выходы которых подключены к третьим информационным входам соответствующих операционных блоков, первый управляющий вход является первым управляющим входом первого блока хранения группы из N блоков хранения, первый выход t-го (

)-го операционного блока, тактовые входы всех операционных блоков, блоков хранения группы из N блоков хранения и блоков постоянной памяти (взвешивающих множителей) и (весовых множителей) подключены к тактовому входу, соединённому с тактовым выходом блока управления, адресный вход соединен с блоками постоянной памяти (взвешивающих множителей) и (весовых множителей), выход блока постоянной памяти (взвешивающих множителей) подключен к первому информационному входу операционного блока, второй выход которого подключен ко второму информационному входу первого операционного блока систолической матрицы, первый информационный вход которого соединен с выходом блока постоянной памяти (весовых множителей), третьи выходы всех операционных блоков подключены ко вторым информационным входам соответствующих блоков хранения, третьи выходы которых подключены к третьим информационным входам соответствующих операционных блоков, первый управляющий вход является первым управляющим входом первого блока хранения группы из N блоков хранения, первый выход t-го ( ) блока хранения подключен к первому управляющему входу (t+1)-го блока хранения, четвертый выход (t+1)-го блока хранения подключен к первому информационному входу t-го блока хранения, при этом операционные блоки содержат сумматор, умножитель и регистр, первый выход которого подключен к второму входу умножителя, второй выход регистра является первым выходом операционного блока, тактовый вход которого соединен с тактовым входом регистра и умножителя, первый информационный вход операционного блока подключен к входу регистра, второй информационный вход операционного блока является первым входом умножителя, третий информационный вход операционного блока является вторым входом сумматора, при этом каждый блок хранения группы из N блоков хранения содержит два узла из (M-1) и M регистров соответственно, элемент задержки и коммутатор, выходы которого подключены к входам узлов из (M-1) и M регистров, тактовые входы которых соединены между собой и являются тактовым входом блока хранения, выход каждого t – го (t

) блока хранения подключен к первому управляющему входу (t+1)-го блока хранения, четвертый выход (t+1)-го блока хранения подключен к первому информационному входу t-го блока хранения, при этом операционные блоки содержат сумматор, умножитель и регистр, первый выход которого подключен к второму входу умножителя, второй выход регистра является первым выходом операционного блока, тактовый вход которого соединен с тактовым входом регистра и умножителя, первый информационный вход операционного блока подключен к входу регистра, второй информационный вход операционного блока является первым входом умножителя, третий информационный вход операционного блока является вторым входом сумматора, при этом каждый блок хранения группы из N блоков хранения содержит два узла из (M-1) и M регистров соответственно, элемент задержки и коммутатор, выходы которого подключены к входам узлов из (M-1) и M регистров, тактовые входы которых соединены между собой и являются тактовым входом блока хранения, выход каждого t – го (t ) регистра узла из (M-1) регистра подключен к входу t

) регистра узла из (M-1) регистра подключен к входу t регистра узла из (M-1) регистра, выход каждого t–го (t

регистра узла из (M-1) регистра, выход каждого t–го (t регистра узла из M регистров подключен к входу t

регистра узла из M регистров подключен к входу t регистра узла из M регистров, первый управляющий вход подключен к первому управляющему входу коммутатора и входу элемента задержки, выход которого является первым выходом блока хранения, первый и второй информационные входы которого подключены к коммутатору, выход

регистра узла из M регистров, первый управляющий вход подключен к первому управляющему входу коммутатора и входу элемента задержки, выход которого является первым выходом блока хранения, первый и второй информационные входы которого подключены к коммутатору, выход  –го регистра узла из (M-1) регистра является четвертым выходом блока хранения, выход

–го регистра узла из (M-1) регистра является четвертым выходом блока хранения, выход  –го регистра узла из M регистров является третьим выходом блока хранения, причем первый выход операционного блока, первый и второй выходы (N-1)-го операционного блока систолической матрицы, первый выход и первый информационный вход N-го блока хранения 25.i не соединены с другими элементами, отличающийся тем, что с целью повышения скорости и точности многоканальных вычислений значений полиномиальных функций в него введены преобразователь из позиционной системы счисления в систему остаточных классов (ПСС-СОК), преобразователь из системы остаточных классов в позиционную систему счисления (СОК-ПСС),

–го регистра узла из M регистров является третьим выходом блока хранения, причем первый выход операционного блока, первый и второй выходы (N-1)-го операционного блока систолической матрицы, первый выход и первый информационный вход N-го блока хранения 25.i не соединены с другими элементами, отличающийся тем, что с целью повышения скорости и точности многоканальных вычислений значений полиномиальных функций в него введены преобразователь из позиционной системы счисления в систему остаточных классов (ПСС-СОК), преобразователь из системы остаточных классов в позиционную систему счисления (СОК-ПСС),  вычислительный тракт по модулю

вычислительный тракт по модулю  , причем выход входного M – канального коммутатора соединен с входом преобразователя ПСС-СОК, k выходов которого подключены к информационным входам вычислительных трактов по модулю

, причем выход входного M – канального коммутатора соединен с входом преобразователя ПСС-СОК, k выходов которого подключены к информационным входам вычислительных трактов по модулю  , информационные выходы которых подключены к входам преобразователя СОК-ПСС, выход которого подключен к входу выходного

, информационные выходы которых подключены к входам преобразователя СОК-ПСС, выход которого подключен к входу выходного  –канального коммутатора, тактовый выход блока управления подключен к тактовым входам преобразователя ПСС-СОК, преобразователя СОК-ПСС, вычислительных трактов по модулю

–канального коммутатора, тактовый выход блока управления подключен к тактовым входам преобразователя ПСС-СОК, преобразователя СОК-ПСС, вычислительных трактов по модулю  , адресный выход и второй управляющий выход блока управления подключены соответственно к адресным и первым управляющим входам вычислительных трактов по модулю

, адресный выход и второй управляющий выход блока управления подключены соответственно к адресным и первым управляющим входам вычислительных трактов по модулю  , третий управляющий выход блока управления подключен ко вторым управляющим входам вычислительных трактов по модулю

, третий управляющий выход блока управления подключен ко вторым управляющим входам вычислительных трактов по модулю  , в вычислительных трактах по модулю

, в вычислительных трактах по модулю  информационный вход подключен ко второму информационному входу операционного блока, второй управляющий вход и информационный выход вычислительного тракта по модулю

информационный вход подключен ко второму информационному входу операционного блока, второй управляющий вход и информационный выход вычислительного тракта по модулю  подключены соответственно ко второму управляющему входу и четвертому выходу первого блока хранения группы из N блоков хранения, второй выход t-го блока хранения (

подключены соответственно ко второму управляющему входу и четвертому выходу первого блока хранения группы из N блоков хранения, второй выход t-го блока хранения ( ) подключен ко второму управляющему входу (t+1)-го блока хранения, второй выход N-го блока хранения не соединен с другими элементами, во все операционные блоки вычислительных трактов по модулю

) подключен ко второму управляющему входу (t+1)-го блока хранения, второй выход N-го блока хранения не соединен с другими элементами, во все операционные блоки вычислительных трактов по модулю  введены по два узла постоянный памяти, причем выход умножителя операционного блока подключен к входу узла постоянной памяти, хранящего вычеты всех возможных произведений по модулям

введены по два узла постоянный памяти, причем выход умножителя операционного блока подключен к входу узла постоянной памяти, хранящего вычеты всех возможных произведений по модулям  ,

,  , выход которого подключен ко второму выходу операционного блока и первому входу сумматора, выход которого подключен к входу узла постоянной памяти, хранящего вычеты всех возможных сумм по модулям

, выход которого подключен ко второму выходу операционного блока и первому входу сумматора, выход которого подключен к входу узла постоянной памяти, хранящего вычеты всех возможных сумм по модулям  ,

,  , выход которого является третьим выходом операционного блока, тактовый вход которого дополнительно подключен к тактовым входам двух узлов постоянной памяти и сумматора, во все блоки хранения вычислительных трактов по модулю

, выход которого является третьим выходом операционного блока, тактовый вход которого дополнительно подключен к тактовым входам двух узлов постоянной памяти и сумматора, во все блоки хранения вычислительных трактов по модулю  введен элемент задержки, выход которого является вторым выходом блока хранения, а вход соединен со вторым управляющим входом коммутатора блока хранения и подключен ко второму управляющему входу блока хранения.

введен элемент задержки, выход которого является вторым выходом блока хранения, а вход соединен со вторым управляющим входом коммутатора блока хранения и подключен ко второму управляющему входу блока хранения.

| US 5249146 A, 28.09.1993 | |||

| US 5371696 A, 06.12.1994 | |||

| US 2008288569 A1, 20.11.2008 | |||

| Систолический процессор для вычисления полиномиальных функций | 1988 |

|

SU1608689A1 |

Авторы

Даты

2020-11-26—Публикация

2020-02-19—Подача