Изобретение относится к вычислительной технике и может быть использовано в системах хранения, преобразования и обработки дискретной информации.

Цель изобретения - упрощение устройства.

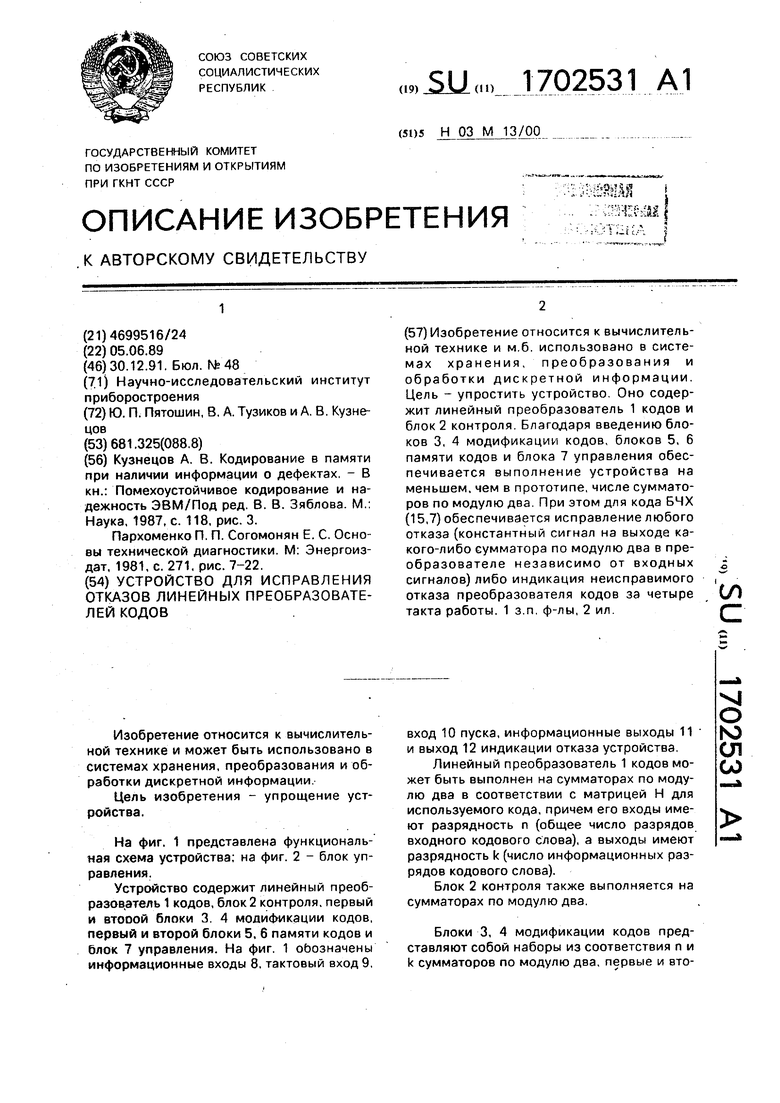

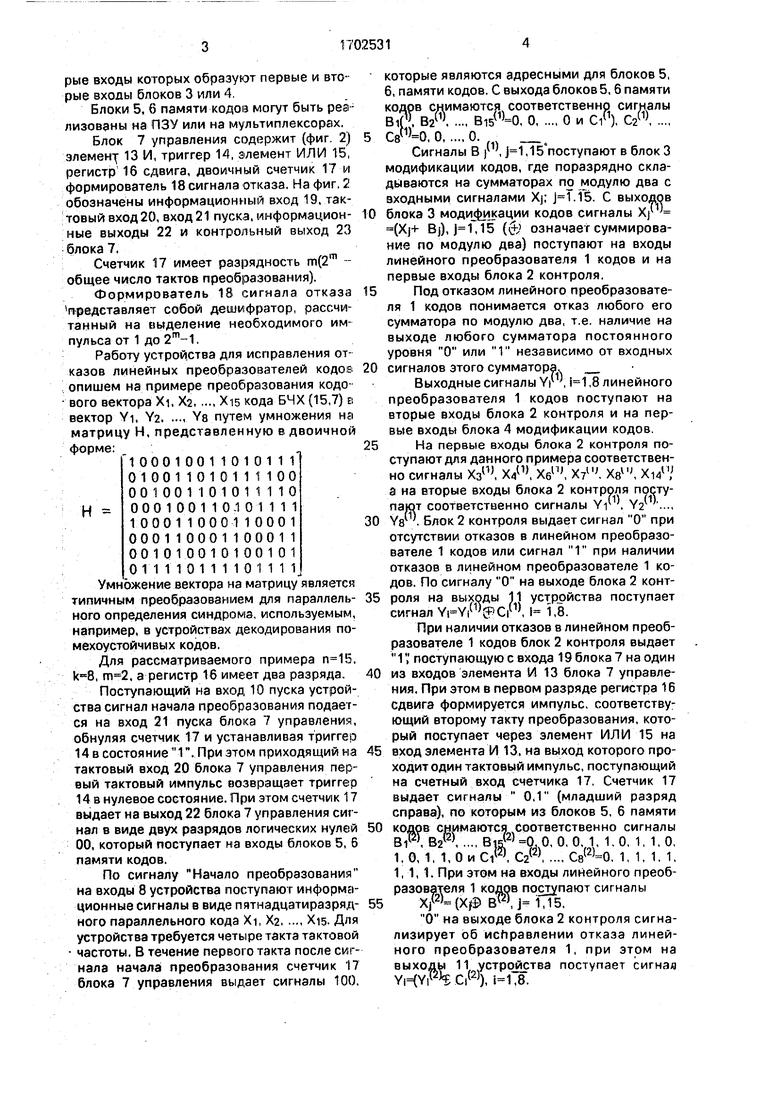

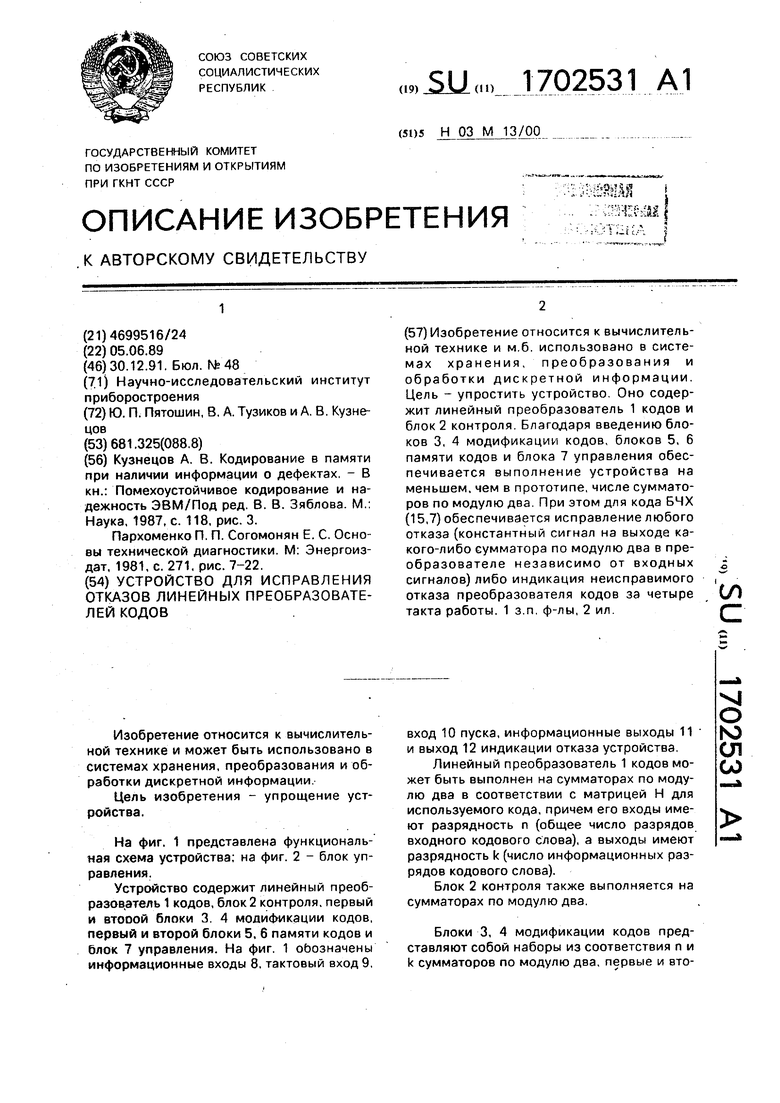

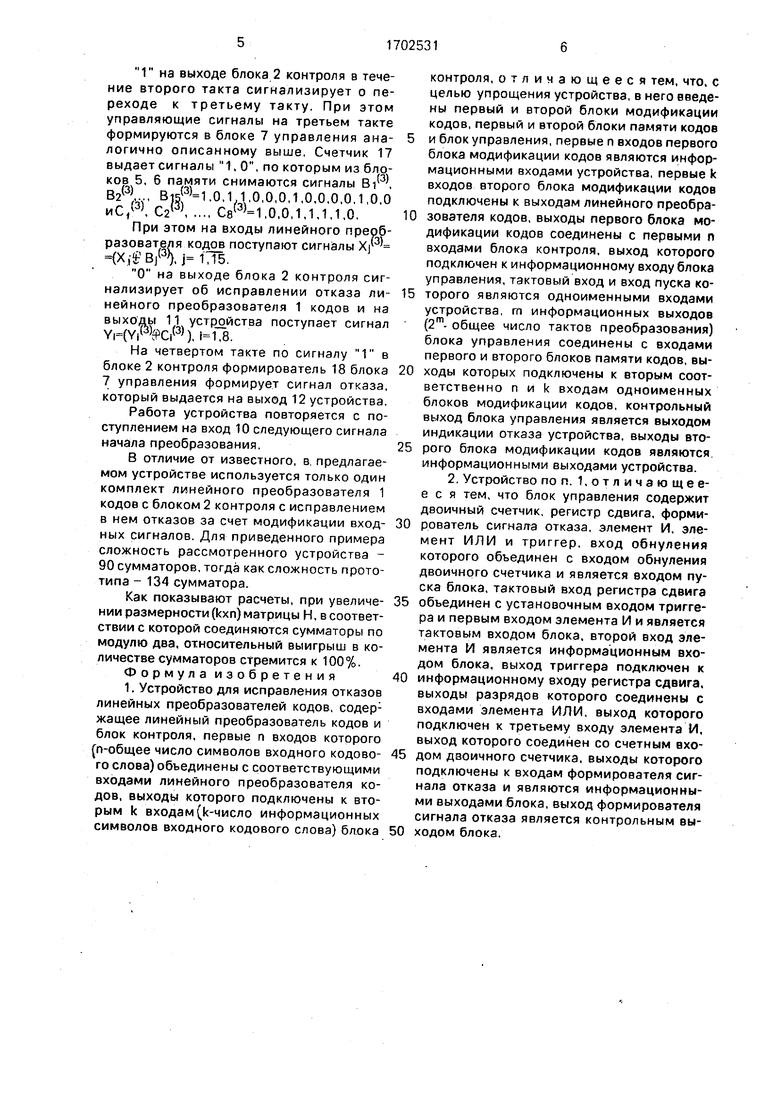

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - блок управления.

Устройство содержит линейный преобразователь 1 кодов, блок 2 контроля, первый и втооой блоки 3. 4 модификации кодов, первый и второй блоки 5, 6 памяти кодов и блок 7 управления. На фиг. 1 обозначены информационные входы 8, тактовый вход 9,

вход 10 пуска, информационные выходы 11 и выход 12 индикации отказа устройства.

Линейный преобразователь 1 кодов может быть выполнен на сумматорах по модулю два в соответствии с матрицей Н для используемого кода, причем его входы имеют разрядность п (общее число разрядов входного кодового слова), а выходы имеют разрядность к (число информационных разрядов кодового слова).

Блок 2 контроля также выполняется на сумматорах по модулю два.

Блоки 3, 4 модификации кодов представляют собой наборы из соответствия п и k сумматоров по модулю два. первые и втоvj

О

Ю

сл

00

рые входы которых образуют первые и вторые входы блоков 3 или 4.

Блоки 5, 6 памяти кодов могут быть реализованы на ПЗУ или на мультиплексорах. Блок 7 управления содержит (фиг. 2) элемент 13 И, триггер 14, элемент ИЛИ 15, регистр 16 сдвига, двоичный счетчик 17 и формирователь 18 сигнала отказа. На фиг. 2 обозначены информационный вход 19, тактовый вход 20, вход 21 пуска, информационные выходы 22 и контрольный выход 23 блока 7.

Счетчик 17 имеет разрядность m(2m - общее число тактов преобразования).

Формирователь 18 сигнала отказа представляет собой дешифратор, рассчитанный на выделение необходимого импульса от 1 до 2т-1.

Работу устройства для исправления отказов линейных преобразователей кодов опишем на примере преобразования кодового вектора Xi, X2Xis кода БЧХ (15,7) в

вектор Yi, Y2 YB путем умножения на

матрицу Н, представленную в двоичной форме:

1 0001 0011010111 010011010111100 001001101011110 Н 000100110.101111 1 0001 1 0001 10001 000 1 1 000 1 1 0001 1 001010010100101 011110111101111, Умножение вектора на матрицу является типичным преобразованием для параллельного определения синдрома, используемым, например, в устройствах декодирования помехоустойчивых кодов.

Для рассматриваемого примера , k-8, , а регистр 16 имеет два разряда.

Поступающий на вход 10 пуска устройства сигнал начала преобразования подается на вход 21 пуска блока 7 управления, обнуляя счетчик 17 и устанавливая триггер 14 в состояние. При этом приходящий на тактовый вход 20 блока 7 управления первый тактовый импульс возвращает триггер 14 в нулевое состояние. При этом счетчик 17 выдает на выход 22 блока 7 управления сигнал в виде двух разрядов логических нулей 00, который поступает на входы блоков 5, 6 памяти кодов.

По сигналу Начало преобразования на входы 8 устройства поступают информационные сигналы в виде пятнадцатиразрядного параллельного кода XL X2Xis. Для

устройства требуется четыре такта тактовой частоты. В течение первого такта после сигнала начала преобразования счетчик 17 блока 7 управления выдает сигналы 100,

которые являются адресными для блоков 5, 6, памяти кодов. С выхода блоков 5,6 памяти кодов снимаются соответственно сигналы В Д В2(1) Bi5°4), 0О и С/1), С2(1)

С8(1)0, 00.t

Сигналы В р, 1,15 поступают в блок 3 модификации кодов, где поразрядно складываются на сумматорах по модулю два с входными сигналами Xj; .15. С выходов

0 блока 3 модификации кодов сигналы X/ (Xj+ Bj), ,15 (& означает суммирование по модулю два) поступают на входы линейного преобразователя 1 кодов и на первые входы блока 2 контроля.

5Под отказом линейного преобразователя 1 кодов понимается отказ любого его сумматора по модулю два, т.е. наличие на выходе любого сумматора постоянного уровня О или 1 независимо от входных

0 сигналов этого сумматора

Выходные сигналы Yr , ,8 линейного преобразователя 1 кодов поступают на вторые входы блока 2 контроля и на первые входы блока 4 модификации кодов.

5На первые входы блока 2 контроля поступают для данного примера соответственно сигналы Хзп, Х(1), Х6и , Х7и;, Xev, XulV а на вторые входы блока 2 контроля поступают соответственно сигналы Yr1 . Y2 ...,

0 Ye . Блок 2 контроля выдает сигнал О при отсутствии отказов в линейном преобразователе 1 кодов или сигнал 1 при наличии отказов в линейном преобразователе 1 кодов. По сигналу О на выходе блока 2 конт5 роля на выходы 11 устройства поступает сигнал (1)yCi(1), i 1.8.

При наличии отказов в линейном преобразователе 1 кодов блок 2 контроля выдает 17 поступающую с входа 19 блока 7 на один

0 из входов элемента И 13 блока 7 управления. При этом в первом разряде регистра 16 сдвига формируется импульс, соответствующий второму такту преобразования, который поступает через элемент ИЛИ 15 на

5 вход элемента И 13, на выход которого проходит один тактовый импульс, поступающий на счетный вход счетчика 17. Счетчик 17 выдает сигналы 0,1 (младший разряд справа), по которым из блоков 5, 6 памяти

0 кодов снимаются соответственно сигналы

Bi(2), B2p)Bigp 0, 0, 0, 0, 1, 1, 0, 1, 1. О,

1. О, 1, 1, 0 и Ci(2), С2(2)Св(2)0, 1, 1, 1, 1.

1, 1, 1. При этом на входы линейного преобразователя 1 кодов поступают сигналы

5 Xjp)-(X(© Вта,-1,15.

О на выходе блока 2 контроля сигнализирует об исправлении отказа линейного преобразователя 1, при этом на выходы 11 устрс йства поступает сигнал YKYr% Ci{2r), ,8.

1 на выходе блока 2 контроля в течение второго такта сигнализирует о переходе к третьему такту. При этом управляющие сигналы на третьем такте формируются в блоке 7 управления аналогично описанному выше. Счетчик 17 выдает сигналы 1, 0, по которым из блоков 5, 6 памяти снимаются сигналы Вг ,

„И

Дз)

В21 ,.., .0.1.1.0.0,0,1.0.0.0.0.1,0.0 иС/3), С2() Св(3)1.0.0.1.1,1.1.0.

При этом на входы линейного преобразователя кодов поступают сигналы X/ (X,ЈBj(3)), j 1,15.

О на выходе блока 2 контроля сигнализирует об исправлении отказа линейного преобразователя 1 кодов и на выходы 11 устройства поступает сигнал Yi(Yi%Ci(3)). ,8.

На четвертом такте по сигналу 1 в блоке 2 контроля формирователь 18 блока 7 управления формирует сигнал отказа, который выдается на выход 12 устройства.

Работа устройства повторяется с поступлением на вход 10 следующего сигнала начала преобразования.

В отличие от известного, в предлагаемом устройстве используется только один комплект линейного преобразователя 1 кодов с блоком 2 контроля с исправлением в нем отказов за счет модификации входных сигналов. Для приведенного примера сложность рассмотренного устройства - 90 сумматоров, тогда как сложность прототипа - 134 сумматора.

Как показывают расчеты, при увеличении размерности (kxn) матрицы Н, в соответствии с которой соединяются сумматоры по модулю два, относительный выигрыш в количестве сумматоров стремится к 100%.

Формула изобретения

1. Устройство для исправления отказов линейных преобразователей кодов. содер: жащее линейный преобразователь кодов и блок контроля, первые п входов которого (п-общее число символов входного кодового слова) объединены с соответствующими входами линейного преобразователя кодов, выходы которого подключены к вторым k входам(k-число информационных символов входного кодового слова) блока

контроля, отличающееся тем, что, с целью упрощения устройства, в него введены первый и второй блоки модификации кодов, первый и второй блоки памяти кодов 5 и блок управления, первые п входов первого блока модификации кодов являются информационными входами устройства, первые k входов второго блока модификации кодов подключены к выходам линейного преобра0 зователя кодов, выходы первого блока модификации кодов соединены с первыми п входами блока контроля, выход которого подключен к информационному входу блока управления, тактовый вход и вход пуска ко5 торого являются одноименными входами устройства, m информационных выходов (2т- общее число тактов преобразования) блока управления соединены с входами первого и второго блоков памяти кодов, вы0 ходы которых подключены к вторым соответственно п и k входам одноименных блоков модификации кодов, контрольный выход блока управления является выходом индикации отказа устройства, выходы вто5 рого блока модификации кодов являются информационными выходами устройства.

2. Устройство поп. 1,отличающее- е с я тем, что блок управления содержит двоичный счетчик, регистр сдвига, форми0 рователь сигнала отказа, элемент И, элемент ИЛИ и триггер, вход обнуления которого обьединен с входом обнуления двоичного счетчика и является входом пуска блока, тактовый вход регистра сдвига

5 обьединен с установочным входом триггера и первым входом элемента И и является тактовым входом блока, второй вход элемента И является информационным входом блока, выход триггера подключен к

0 информационному входу регистра сдвига, выходы разрядов которого соединены с входами элемента ИЛИ. выход которого подключен к третьему входу элемента И. выход которого соединен со счетным вхо5 дом двоичного счетчика, выходы которого подключены к входам формирователя сигнала отказа и являются информационными выходами блока, выход формирователя сигнала отказа является контрольным вы0 ходом блока.

20

19

Г

f3

22./ 22.2 22.m

A A

17

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для магнитной записи цифровой информации | 1982 |

|

SU1037337A1 |

| Система для исправления ошибок при передаче N-разрядных кодовых слов | 1985 |

|

SU1336254A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1027726A1 |

| Устройство для декодирования линейных кодов | 1985 |

|

SU1287297A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для передачи данных с самотестированием | 1988 |

|

SU1702376A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Устройство для контроля раствора валков прокатного стана | 1983 |

|

SU1088832A1 |

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

Изобретение относится к вычислительной технике и м.б. использовано в системах хранения, преобразования и обработки дискретной информации. Цель - упростить устройство Оно содержит линейный преобразователь 1 кодов и блок 2 контроля. Благодаря введению блоков 3, 4 модификации кодов, блоков 5, 6 памяти кодов и блока 7 управления обеспечивается выполнение устройства на меньшем, чем в прототипе, числе сумматоров по модулю два. При этом для кода БЧХ

AA t

| Кузнецов А | |||

| В | |||

| Кодирование в памяти при наличии информации о дефектах | |||

| - В кн.: Помехоустойчивое кодирование и надежность ЭВМ/Под ред | |||

| В | |||

| В | |||

| Зяблова | |||

| М.: Наука, 1987, с | |||

| Прибор для массовой выработки лекал | 1921 |

|

SU118A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Пархоменко П | |||

| П | |||

| Согомонян Е | |||

| С Основы технической диагностики | |||

| М: Энергоиз- дат, 1981, с | |||

| Искроудержатель для паровозов | 1920 |

|

SU271A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1991-12-30—Публикация

1989-06-05—Подача