Изобретение относится к технике связи и может быть использовано для обнаружения ошибок при приеме последовательного дуобинарного кода.

Целью изобретения является повышение надежности.

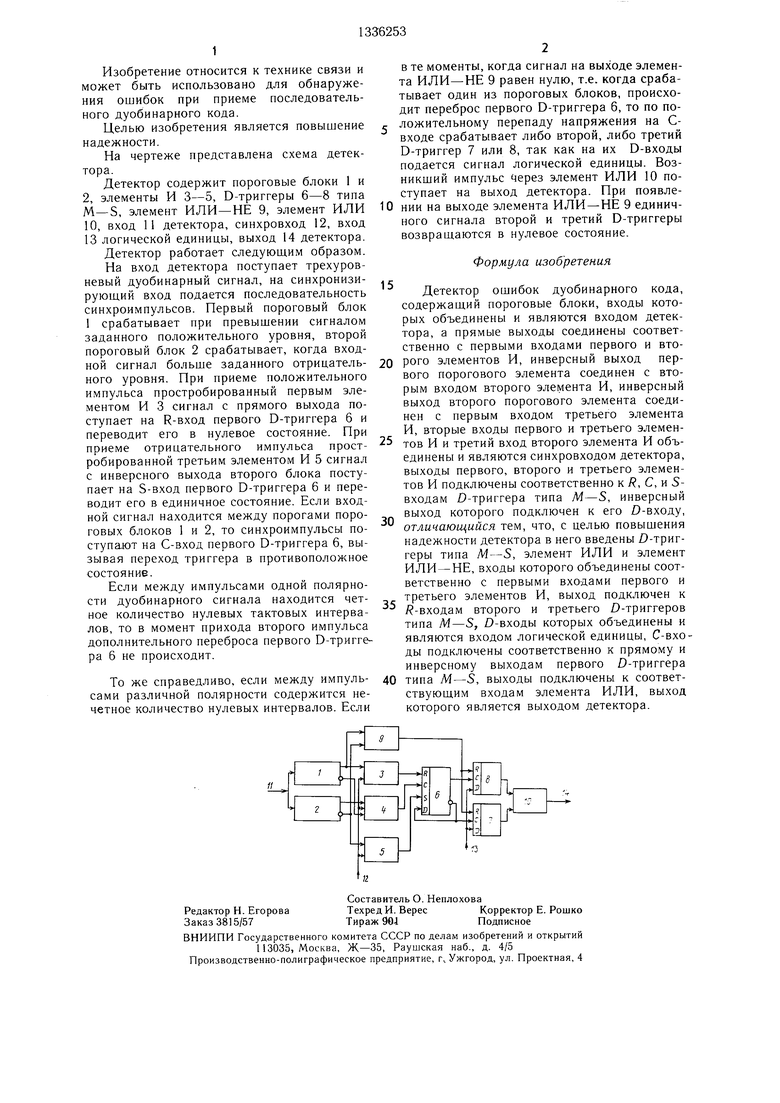

На чертеже представлена схема детектора.

Детектор содержит пороговые блоки 1 и 2, элементы И 3-5, D-триггеры 6-8 типа М-S, элемент ИЛИ-НЕ 9, элемент ИЛИ 10, вход 11 детектора, синхровход 12, вход 13 логической единицы, выход 14 детектора.

Детектор работает следуюш.им образом.

На вход детектора поступает трехуровневый дуобинарный сигнал, на синхронизи- руюш,ий вход подается последовательность синхроимпульсов. Первый пороговый блок 1 срабатывает при превышении сигналом заданного положительного уровня, второй пороговый блок 2 срабатывает, когда входной сигнал больше заданного отрицательного уровня. При приеме положительного импульса простробированный первым элементом И 3 сигнал с прямого выхода поступает на R-вход первого D-триггера 6 и переводит его в нулевое состояние. При приеме отрицательного импульса прост- робированной третьим элементом И 5 сигнал с инверсного выхода второго блока поступает на S-вход первого D-триггера 6 и переводит его в единичное состояние. Если входной сигнал находится между порогами пороговых блоков 1 и 2, то синхроимпульсы поступают на С-вход первого D-триггера 6, вызывая переход триггера в противоположное состояние.

Если между импульсами одной полярности дуобинарного сигнала находится четное количество нулевых тактовых интервалов, то в момент прихода второго импульса дополнительного переброса первого D-триггера 6 не происходит.

То же справедливо, если между импульсами различной полярности содержится нечетное количество нулевых интервалов. Если

в те моменты, когда сигнал на выходе элемента ИЛИ-НЕ 9 равен нулю, т.е. когда срабатывает один из пороговых блоков, происходит переброс первого D-триггера 6, то по положительному перепаду напряжения на С- входе срабатывает либо второй, либо третий D-триггер 7 или 8, так как на их D-входы подается сигнал логической единицы. Возникший импульс через элемент ИЛИ 10 поступает на выход детектора. При появлеНИИ на выходе элемента ИЛИ-НЕ 9 единичного сигнала второй и третий D-триггеры возвращаются в нулевое состояние.

5

0

5

0

5

0

Формула изобретения

Детектор ошибок дуобинарного кода, содержаший пороговые блоки, входы которых объединены и являются входом детектора, а прямые выходы соединены соответственно с первыми входами первого и второго элементов И, инверсный выход первого порогового элемента соединен с вторым входом второго элемента И, инверсный выход второго порогового элемента соединен с первым входом третьего элемента И, вторые входы первого и третьего элементов И и третий вход второго элемента И объединены и являются синхровходом детектора, выходы первого, второго и третьего элементов И подключены соответственно к /, С, и S- входам D-триггера типа М-S, инверсный выход которого подключен к его D-входу, отличающийся тем, что, с целью повышения надежности детектора в него введены D-триггеры типа М-S, элемент ИЛИ и элемент ИЛИ-НЕ, входы которого объединены соответственно с первыми входами первого и третьего элементов И, выход подключен к / -входам второго и третьего D-триггеров типа М-S, D-входы которых объединены и являются входом логической единицы, С-вхо- ды подключены соответственно к прямому и инверсному выходам первого D-триггера типа М-5, выходы подключены к соответствующим входам элемента ИЛИ, выход которого является выходом детектора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| УСТРОЙСТВО ОБРАБОТКИ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 1987 |

|

SU1841021A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1709318A1 |

| УСТРОЙСТВО ДЛЯ ВЫЯВЛЕНИЯ АСИНХРОННОГО РЕЖИМА ЭЛЕКТРОПЕРЕДАЧИ | 1993 |

|

RU2064726C1 |

| Частотный компаратор | 1982 |

|

SU1045376A1 |

| ОБНАРУЖИТЕЛЬ ПЕРЕОТРАЖЕННЫХ СИГНАЛОВ | 1999 |

|

RU2191400C2 |

| Устройство приема тональных сигналов | 1991 |

|

SU1793560A1 |

| Способ гашения дуги однофазного замыкания на землю в сети переменного тока | 1986 |

|

SU1376169A1 |

| Частотно-фазовый детектор | 1980 |

|

SU1040591A1 |

| Генератор-анализатор псевдослучайной последовательности | 1990 |

|

SU1784978A1 |

Изобретение относится к технике связи и может быть использовано для обнаружения ошибок при приеме последовательного дуобинарного кода. Целью изобретения является повышение надежности. Для этого в устройство, содержащее два пороговых блока, три элемента И и D-триггер типа М-S, введены два D-триггера типа М-S, элемент ИЛИ-НЕ и элемент ИЛИ. 1 ил. со со О5 го СП оо

| Патент США № 3337864, кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1987-09-07—Публикация

1985-07-09—Подача