Изобретение относится к вычислительной и радиоизмерительной технике и может быть использовано в устройствах измерения верности передачи информации в цифровых каналах связи (ЦКС).

Генератор-анализатор псевдослучайной последовательности (ГАПСП) решает следующие задачи: формирование и выдача псевдослучайной последобательности (ПСП) для использования ее в качестве тестовой и подачи на испытуемый ЦКС при проверке качества работы ЦКС или другого объекта контроля: прием ПСП, прошедшей ЦКС; формирование внутренней ПСП в анализаторе ошибок; синхронизация внутренней ПСП с входной внешней ПСП; выделение ошибок из входной ПСП путем сравнения входной внешней и внутренней ПСП в анализаторе ошибок; подсчет количества ошибок счетчиком ошибок.

В качестве тестовой ПСП наиболее часто используется ПСП максимальной длины (ПСПМД).

Известен анализатор кодовых последовательностей импульсов, содержащий выделитель ошибок, счетчик ошибок, блок управления, элемент ИЛИ, RS-триггер, два D-триггера. Недостатком этого анализатора является необходимость в отдельном генераторе ПСП.

Наиболее близким аналогом является генератор-анализатор ПСП. содержащий блок управления, первый выход которого , соединен со входом генератора тактовых импульсов, выход которого подключен к тактовому входу пер&ого регистра сдвига и является тактовым выходом генератора- анализатора, второй выход блока управления соединен с установочным входом первого регистра сдвига, первые выходы

ю VI

вймА

торого подключены к первым информационным входам первого коммутатора,выходы которого соединены со входами первого сумматора по модулю два, выход которого подключен к информационному входу первого регистра сдвига, вторые выходы рого соединены с информационными входами первого дешифратора, первый вы- ход которого явлйеТсяЪйх одом синхронизации гейератора-анализатора,первый . триггер, D-exdS которого является информа- циойтчш входом генератора-анализатора, прямой выход первого триггера подключен к первым входам компаратора и второго сумматора по модулю два, С-вход первого триггера объединён с тактовым входом второго регистра сдвига и счетным входом первого счетчика и является тактовым входом генератора-анализатора, первые выходы второго регистра сдвига соединены с первыми информационными входами второго коммутатора, выходы которого подключены ко входам третьего сумматора по модулю два, выход которого соединен с первым входом четвертого сумматора по модулю ДБЭ и вторым входом компаратора, выход которого подключен к D-входу второго триггера, прямой выход которого соединен со вторым входом второго сумматора по модулю два, выход которого подключен ко второму входу четвертого сумматора по модулю два, третьи выходы блока управления соединены с вторыми информационными входами первого и второго коммутаторов, четвертый выход блока управления и выход четвертого сумматора по модулю два соединены с R-входом третьего триггера, прямой выход которого подключен к R-входу четвертого и S-входу пятого триггеров и входу об- нуления первого счетчика, выход переполнения которого соединен с С-вхо- дом четвертого триггера, прямой и инверсный выходы пятого триггера подключены соответственно к первому входу первого элемента ИЛИ и S-входу третьего триггера. Недостатком прототипа является невысокая помехоустойчивости из-за невозможности синхронизации детектора ошибок

прототипа при приеме входной внешней

Y ПСПМД с коэффициентом ошибок Кош -к-,

где п - число разрядов (длина) регистра сдвига, т.е. когда в среднем на каждые 2п тактовых интервалов входной ПСП приходится хотя бы одна ошибка. При этом, чтобы произошла синхронизация детектора ошибок прототипа, необходимо наличие 2п безошибочных тактовых интервалов входной ПСП, принимаемой из ЦКС, (п тактовых интервалов затрачиваются на второй этап синхронизации, еще п тактовых интервалов - на третий). Поскольку при К0ш -о гГ наличие 2п

безошибочных тактовых интервалов входной ПСП очень редкое событие, то детектор ошибок прототипа может находиться в состоянии рассинхронизации неопределенно долгое время.

Цель изобретения - повышение помехо- 0 устойчивости ГАПСП за счет обеспечения генерации тестовой ПСП сложного вида, составленной из двух ПСП с периодами различной величины, первая - с минимально возможным периодом Lmin 2Пгп1п - 1 и вторая - с требуемым периодом ПСП, выдачи этой тестовой ПСП в ЦКС и за счет обеспечения возможности анализа этой сложной тестовой ПСП, прошед11

детектором

5

0

5

0

5

0

5

0

5

шей ЦКС, - Кош „

ошибок анализатора ГАПСП.

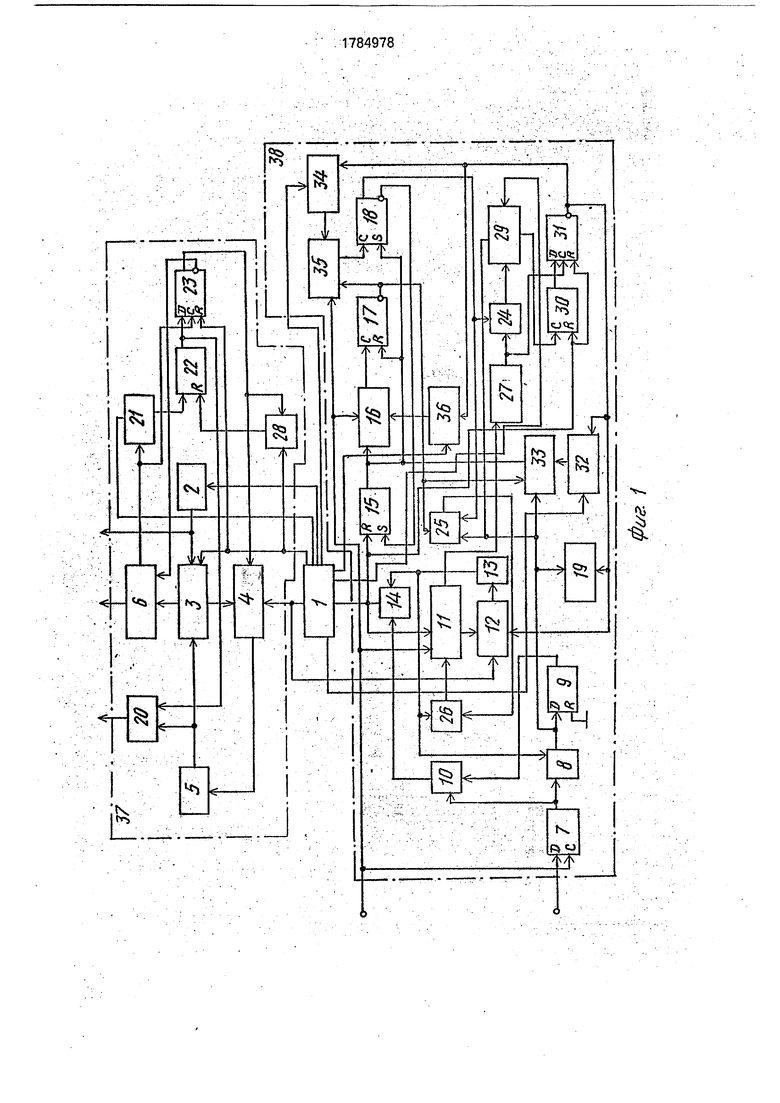

На фиг.1 изображена функциональная схема генератора-анализатора ПСП. На фиг.2 представлены временные диаграммы его работы,

Генератор-анализатор содержит блок управления 1, генератор тактовых импульсов 2, первый регистр сдвига 3, первый комму гатор 4, первый сумматор 5 по модулю два, первый дешифратор б, первый триггер 7, компаратор 8, второй триггер 9, второй сумматор 10 по модулю два, второй регистр сдвига 11, второй коммутатор 12, третий 13 и четвертый 14 сумматоры по модулю два, третий триггер 15, первый счетчик 16, четвертый 17 и пятый 18 триггеры, второй счетчик 19, пятый сумматор 20 по модулю два, третий счетчик 21, шестой 22 и седьмой 23 триггеры, первый элемент ИЛИ 24, элемент И 25, шестой сумматор 26 по модулю два, второй дешифратор 27, второй элемент ИЛИ 28, четвертый счетчик 29, восьмой 30 и девятый 31 триггеры, третий коммутатор 32, пятый счетчик 33, четвертый коммутатор 34, шестой счетчик 35, пятый коммутатор 36, генератор ПСП 37, анализатор ПСП 38.

Первый счетчик 16 тактов имеет модуль счета п+1, третий счетчик малых периодов имеет модуль счета К, четвертый и пятый счетчики 29,33 имеют модули счета I, 0 I - целое и (1+ а), 0 :Ј а - целое, соответственно, шестой счетчик тактов имеет модуль счета т, 0 т - целое. Блок управления 1, выполнен аналогично блоку управления прототипа.

Работа ГАПСП происходит следующим образом.

После включения ГАПСП с помощью блока управления 1 (клавиатуры встроенной

микроЭВМ, кнопок управления, регистров настройки)устанавливаются выбранные режимы работы - генерации ПСПМД требуемого периода, структуры и анализа ошибок. При этом-с блока управления 1 на коммутаторы 4 и 12, которые коммутируют точки подключения сумматоров 5 и 13 по модулю два к регистрам сдвига 3 и 11 соответственно, одновременно выдается одинаковый параллельный код включения обратных связей, в которые входят элементы ИСКЛЮЧАЮЩЕЕ ИЛИ сумматоров 5 и 13 по модулю два, для формирования регистрами сдвига 3,11 ПСПМД одинаковой требуемой структуры и периода и одинаковой ПСПМД одного и того же минимально возможного (малого) периода. При этом какая ПСПМД (малого или требуемого периода) будет генерироваться регистром сдвига 3, в данный момент времени зависит от состояния в этот момент триггера 23. а регистром сдвига 11 - от состояния триггера 31, которые устанавливаются в исходное нулевое состояние установочными импульсами генератора ПСП 37 и анализатора РСП 38 с выходов блока управления 1 соответственно одновременно при нажатии кнопки ПУСК блока управления 1 и начале процесса генерации ПСПМД малого периода.

На генератор тактовых импульсов 2 с блока управления выдается параллельный код управления установкой выбранного значения частоты тактовых импульсов. С выхода блока управления 1 на счетчик 21 выдается пар аллельный код выбранного числа малых периодов К ПСПМД. С выходов блока управления 1 на коммутатор 34, коммутатор 36, счетчик 29, коммутатор 32 выдаются параллельные коды сигналов управления установкой модулей счета т, (п+1), , (1+ а) счетчиков 35, 16, 29, 33 соответственно, которые могут быть установлены различными для ПСПМД малого и требуемого периодов и выбираются оператором, исходя из ожидаемой помеховой обстановки в ЦКС.

Установочные импульсы генератора и анализатора поступают также на регистры сдвига 3 и 11 соответственно, устанавливая их в начальное состояние 0 ..01 и разрешая их работу. Тактовые импульсы с выхода генератора 2 тактовых импульсов. ПСПМД с выхода сумматора 5 по модулю два через сумматор 20 по модулю два и импульсы СИНХРОНИЗАЦИИ с дешифратора 6 выдаются на выходы ГАПСП. При этом в течение длительности выдачи (К-1) малых периодов ПСПМД сумматор 20 по модулю два работает как элемент ИЛИ, пропуская ПСПМД на выход без инверсии, так как на

один из его входов поступает напряжение лог.О с прямого выхода шестого триггера 22, установленного в исходное состояние установочным импульсом. Число прошедших 5 периодов отсчитывает счетчик 21, считая импульсы, формируемые дешифратором 6 в моменты, когда регистр сдвига 3 устанавливается в начальное состояние.

По истечении (К-1) малых периодов

0 выдаваемой ПСПМД на выходе счетчика 21 появляется импульс, который устанавливает шестой триггер 22 в состояние лог.1, которая с его прямого выхода поступает на вход сумматора 20 по модулю два, вызывая

5 инверсию выдаваемой ПСПМД. После окончания инверсного малого периода ПСПМД очередной импульс с дешифратора 6 передним фронтом устанавливает триггер 23, на вход D которого в это время подается

0 лог.1, в состояние лог.1, которая вызываете помощью коммутатора 4 подключение сумматора 5 по модулю два к необходимым точкам (выходам разрядов) регистра сдвига 3 для генерации ПСПМД требуемого периб5 да с начального состояния 0...01, и, кроме того, через элемент ИЛИ 24 устанавливает триггер 22 в состояние лог.О, запрещая инверсию выходной ПСПМД.

ПСПМД в качестве тестовой подается

0 на испытуемый ЦКС, тактовые импульсы подаются на тактовый вход анализатора ошибок в режиме анализа ошибок по шлейфу.

Работу анализатора ГАПСП можно раз5 бить на три цикла: синхронизация внутренней ПСПМД малого периода детектора ошибок анализатора с входной внешней ПСПМД такого же периода с этапами - начальной установки, фазового сдвига внут0. ренней ПСПМД выделенными импульсами ошибок, проверка отсутствия ложной синхронизации; ожидание пакета ошибок в последнем малом периоде ПСПМД, вызванного инверсией выходной ПСПМД ге5 нератора; анализ входной ПСПМД требуемых (большого) периода и структуры.

Установочный импульс анализатора устанавливает триггеры 15, 17, 18, счетчики

0 16, 33, 35 в исходное состояние, при котором на выходе счетчиков 16, 35, прямом выходе триггера 17 устанавливается уровень лог.О, а на прямом выходе триггера 18 уровень лог,1, триггеры 30, 31 также уста5 навливаются в исходное нулевое состояние. При этом на выходе триггера 15 и счетчика 33 установится уровень лог.О, который разрешает счетчику 16 счет тактов. Модуль счета счетчика 35, равный числу m (0 m - целое), и модуль счета счетчика 33, равный

числу (1+ а), где 0 а - целое, устанавливаются сигналами управления с коммутаторов 34 и 32 соответственно, которые коммутиру- raf в этот момент на свои выходы сигналы управления, соответствующие числам, вы- бранным для малого периода ПСПМД. Аналогично модуль счета счетчика 16 устанавливается равным (rtmin + 1).

Компаратор 8 начинает сравнение входной внешней ПСПМД малого периода и формируемой на выходе сумматора 13 по модулю два внутренней ПСПМД такого же периода и структуры, но сдвинутой по фазе на некоторое число тактов. При этом импульсы ошибок с выхода компаратора 8 про- ходят на счетчик 33 ошибок и на элемент И 25. Элемент И 25 открыт уровнями лог.1 с инверсного выхода триггера 17 и прямого выхода триггера 18. Поэтому импульсы ошибок будут воздействовать на регистр сдвига 11 через сумматор 26 по модулю два до тех пор, пока счетчик 16 не досчитает число тактовых импульсов до (nmin + 1). Если при этом в регистр сдвига 11 будет записана безошибочная информация, т.е. регистр сдвига детектора ошибок войдет в синхронизм с регистром сдвига 3 на передающем конце, то на следующем этапе проверки на отсутствие ложной синхронизации, когда на инверсном выходе триггера 17 установится логический 0 и будет разрешен счет тактов счетчику 35 и счет ошибок счетчику 33, а элемент И 25 будет закрыт, счетчик 33 за число тактовых периодов mmin (для малого периода ПСПМД), при правильном выборе mmm и (1 + «min), не досчитает дб своего модуля счета (1 + оып) (при ожидаемом распределении ошибок во входной ПСП). На выходе счетчика 35 появится импульс, который установит лог.О на прямом выходе триг- гера 18, который закроет элемент И 25 и разрешит прохождение импульсов с дешифратора 27 на счетчик 29 для установки его в нулевое состояние, при этом в перерывах между этими импульсами счетчику 29 разре- шается счет ошибок с выхода компаратора 8. т.е. третий этап синхронизации закончится.

Если на втором этапе синхронизации в регистр сдвига 11 будет записана хотя бы одна ошибка, которая принята во входной ПСП, то на третьем этапе синхронизации счетчик 33 за число тактовых периодов nrimin успеет досчитать до своего модуля счета (1 + ctmin) и положительный импульс на выходе установит схему детектора ошибок анализатора в исходное состояние. Такой процесс повторяется до тех пор, пока регистр сдвига 11 анализатора не войдет в

синхронизм с регистром сдвига 3 генератора на передающем конце ЦКС. После этого анализатор ГАПСП переходит в цикл ожидания пакета ошибок.

На этом цикле работы при правильно выбранном модуле счета I (0 I - целое) счетчик 29 за время между импульсами с дешифратора 27 не успевает досчитать число ошибок с компаратора 8 до своего модуля счета, и триггеры 30, 31 находятся в своем исходном нулевом состоянии. Когда с компаратора 8 приходит пакет ошибок, вызванный инверсией одного последнего малого периода ПСПМД генератора, то счетчик 29 до следующего импульса с дешифратора 27 успевает досчитать ошибки до своего модуля счета I, и на его выходе появляется импульс, который устанавливает триггер 30 в состояние лог.1, которая поступает на D- вход триггера 31. Приходящий следом за этим импульс с дешифратора 27 на С-вход триггера 31 устанавливает его в состояние лог,1, а с его инверсного выхода разрешающий потенциал поступает на счетчик 19, разрешая ему счет ошибок, и на коммутаторы 12, 32, 34, 36, разрешая подключение необходимых разрядов регистра сдвига 11 к сумматору 13 по модулю два, что позволяет регистру сдвига 11 генерировать ПСПМД выбранной структуры и большого периода, и разрешая установку коммутаторами соответствующих выбранных модулей счета счетчиков 33, 35,16 для ПСПМД большого периода,

На этом цикл ожидания закончился и начался цикл анализа входной ПСПМД из ЦКС большого периода,

При нормальном функционировании детектора ошибок информация на обоих входах сумматора 14 по модулю два совпадает, так как ошибки во входной ПСП корректируются компаратором 8, триггером 9 и сумматором 10 по модулю два. поэтому на выхода сумматора 14 по модулю два формируется лог.О. Если в процессе нормального функционирования детектора ошибок произойдет сбой в регистре сдвига 11, на выходе сумматора 14 по модулю два появятся импульсы, которые воздействуя на вход установки логического нуля триггера 15 установят лог.О на его выходе, начнет работать счетчик 16, и детектор ошибок анализатора вновь перейдет к второму этапу работы при синхронизации - записи информации, затем к третьему этапу и т.д. до тех пор, пока автоматически не произойдет пересинхронизация детектора ошибок.

Такая структура ГАПСП позволяет проводить синхронизацию внутренней ПСП t:

М ИНИМаЛЬНО ВОЗМОЖНЫМ ПерИОДОМ Lmln,

формируемой детектором ошибок анализатора, в течение длительности нескольких малых периодов этой ПСП, число которых устанавливается заранее перед измерениями е зависимости от ожидаемой помеховой обстановки таким образом, чтобы за это число периодов с вероятностью близкой к 1 произошла синхронизация. Синхронизация обеспечивается за счет управления фазовым сдвигом внутренней ПСП выделенными импульсами ошибок за время входа в синхронизм при одной попытке, определяемое выражением

TCmin (nmln + 1 + ГПгЫп) Тт ,

где Тт - период следования тактовых импульсов;

nmin - число разрядов (длина) PC генератора и детектора ошибок, участвующих в формировании ПСП с минимально возможным (малым) периодом,

rrimin - модуль счета шестого счетчика тактов анализатора (число тактов этапа проверки отсутствия ложной синхронизации).

При этом для входной на анализатор ПСП с Lmin, прошедшей ЦКС, будет выполняться:

К,

1

ошч

Пт1п

После того, как произошла синхронизация внутренней ПСП детектора ошибок и ПСП генератора, прошедшей ЦКС, с ма- лым периодом и после окончания приема пакета ошибок, вызванного инверсией одного малого периода ПСП в генераторе ГАПСП на передающем конце, детектор ошибок анализатора ГАПСП автоматиче- ски переходит на анализ входной ПСП требуемого большого периода и структуры, формируемой генератором ГАПСП на передающем конце вслед за окончанием инверсного малого периода ПСП

Предлагаемый ГАПСП согласно (2) обладает более высокой помехоустойчивостью, так как во многих случаях можно выбрать

Пт1п « Птреб.

Большая помехоустойчивость позволя- ет использовать предлагаемый ГА.ПСП для функционального контроля объектов (ЦКС) в тех случаях, когда использование прототипа и аналогичных детекторов ошибок уже невозможно, и требуются другие методы ана- лиза тестовой ПСП, например, измерение времени задержки сигнала в объекте контроля. Тогда анализ тестовой ПСП можно проводить, запуская регистр сдвига в пере510

15

2025

30

35 40 45

50 55датчике (генераторе) ПСП, поступающей на объект контроля и такой же регистр в анализаторе ошибок с одних и тех же начальных условий, но с разницей во времени, равной времени задержки сигнала в объекте контроля. Очевидно, что такой способ определения задержки и, следовательно, другой принцип работы даже без аппаратуры анализа коэффициента ошибок требует больших аппаратных затрат, так как требует включения в измерительную аппаратуру, например, частотомера и тем более точного, чем более высокая тактовая частота используется для передачи ПСП.

Формула изобретения

Генератор-анализатор псевдослучайной последовательности, содержащий блок управления, первый выход которого соединен с входом генератора тактовых импульсов, выход которого подключен к тактовому входу первого регистра сдвига и является тактовым выходом генератора-анализатора, второй выход блока управления соединен с установочным входом первого регистра сдвига, первые выходы которого подключены к первым информационным входам первого коммутатора, выходы которого соединены с входами первого сумматора по модулю два, выход которого подключен к информационному входу первого регистра сдвига, вторые выходы которого соединены с информационными входами первого дешифратора, первый выход которого является выходом синхронизации генератора-анализатора, первый триггер, D-вход которого является информационным входом генератора-анализатора, прямой выход первого триггера подключен к первым входам компаратора и второго сумматора по модулю два, С-вход первого триггера объединен с тактовым входом второго регистра сдвига и счетным входом первого счетчика и является тактовым входом генератора-анализатора, первые выходы второго регистра сдвига соединены с первыми информационными входами второго коммутатора, выходы которого подключены к входам третьего сумматора по модулю два, выход которого соединен с первым входом четвертого сумматора по модулю два и вторым входом компаратора, выход которого подключен к D-входу второго триггера, прямой выход которого соединен с вторым входом второго сумматора по модулю два, выход которого подключен ко второму входу четвертого сумматора по модулю два, третьи выходы блока управления соединены со вторыми информационньгми входами первого и второго коммутаторов, четвертый выход блока управления и выход четвертого сумматора по модулю два соединены с R-входом третьего триггера, прямой выход которого подключен к R-входу четвертого и S-входу пятого триггеров и входу обнуления первого счетчика, выход переполнения которого соединен с С-входом четвертого триггера, прямой и инверсный выходы пятого триггера подключены соответственно к первому входу первого элемента ИЛИ и S-входу третьего триггера и второй счетчик, отличающийся тем, что, с целью повышения помехоустойчивости, в генератор-анализатор введены пятый и шестой сумматоры по модулю два, третий-шестой счетчики, второй дешифратор, шестой-девя- тый триггеры, третий-пятый коммутаторы, элемент И и второй элемент ИЛИ, первый вход которого объединен с R-входом седьмого триггера и подключен к второму выходу блока управления, пятые выходы которого соединены с установочными входами третьего счетчика, выход переполнения которого и выход второго элемента ИЛИ подключены соответственно к S- и R-входам шестого триггера, прямой выход которого соединен с D-входом седьмого триггера и первым входом пятого сумматора по модулю два, второй вход которого подключен к выходу первого сумматора по модулю два, второй выход первого дешифратора соединен с входом обнуления третьего счетчика и С-входом седьмого триггера, инверсный выход которого подключен к входу разрешения первого дешифратора, прямой выход седьмого триггера соединен с вторым входом второго элемента ИЛИ и входом разрешения первого коммутатора, шестой выход блока управления подключен к управляющему входу четвертого коммутатора, выход которого соединен с установочным входом шестого счетчика, счетный вход которого подключен к тактовому входу генератораанализатора, инверсный выход четвертого триггера соединен с первым входом элемента И и входами обнуления пятого и шестого счетчиков, выходы переполнения которых

подключены соответственно к S- и С-входам пятого триггера, второй вход элемента И подключен к прямому выходу пятого триггера, третий вход элемента И объединен с счетными входами второго, четвертого и пятого счетчиков и подключен к выходу компаратора, R-вход второго триггера соединен с общей шиной, седьмые-девятые выходы блока управления соединены соответственно с информационными входами пятого коммутатора, установочными входами четвертого счетчика и информационными входами третьего коммутатора, выходы третьего и пятого коммутаторов подключены к установочным входам соответственно

пятого и первого счетчиков, выход элемента И соединен с первым входом шестого сумматора по модулю два, второй вход и выход которого подключены соответственно к выходу третьего сумматора по модулю два

и информационному входу второго регистра сдвига,вторые выходы которого соединены с входами второго дешифратора, выход которого подключен к С-входу девятого триггера и второму входу первого элемента

ИЛИ, выход которого соединен с входом обнуления четвертого счетчика, выход переполнения которого подключен к С-входу восьмого триггера, R-вход которого объединен с R-входом девятого триггера и установочным входом второго регистра сдвига и подключен к четвертому выходу блока уп- ргвления, прямой выход восьмого триггера соединен с D-входом девятого триггера, инверсный выход которого подключен к

управляющим входам третьего-пятого коммутаторов, входу разрешения второго коммутатора и входу разрешения счета второго счетчика, выход пятого сумматора по модулю два является выходом генератора-анализатора.

I f

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2008 |

|

RU2390943C1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2004 |

|

RU2279184C2 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2004 |

|

RU2276835C1 |

| Устройство для детектирования ошибок | 1990 |

|

SU1709542A1 |

| Устройство для детектирования ошибок | 1988 |

|

SU1573545A1 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Устройство для передачи дискретных сообщений | 1983 |

|

SU1195471A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Устройство для контроля дискретного канала | 1984 |

|

SU1298930A1 |

Изобретение относится tf вычислительной и измерительной технике. Его использование в устройствах измерения верности передачи информации в Цифровых каналах связи (ЦКС) позволяет повысить помехоустойчивость. Это достигается за счет генерации тестовой псевдослучайной последовательности (ПСП) сложного вида, составленной из двух ПСП с периодами различной величины (минимально возможным и требуемым), а также за счет обеспечения возможности анализа этой сложной тестовой ПСП на наличие ошибок при прохождении ЦКС. 2 ил.

Редактор Н. Коляда

Техред М.Моргентал

Заказ 4365ТиражПодписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 6113035, Москва, Ж-35, Раушская наб., 4/5

Корректор О. Кравцова

| Анализатор кодовых последовательностей импульсов | 1984 |

|

SU1208609A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Генератор ПСП-анализатор кодовых последовательностей | |||

| Техническое описание и инструкция по эксплуатации | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-12-30—Публикация

1990-11-11—Подача