Изобретение относится к радиотехнике и может быть использовано для радиоприема и обработки сигналов с относительной фазовой манипуляцией (ОФМ).

Цель изобретения - повышение помехоустойчивости.

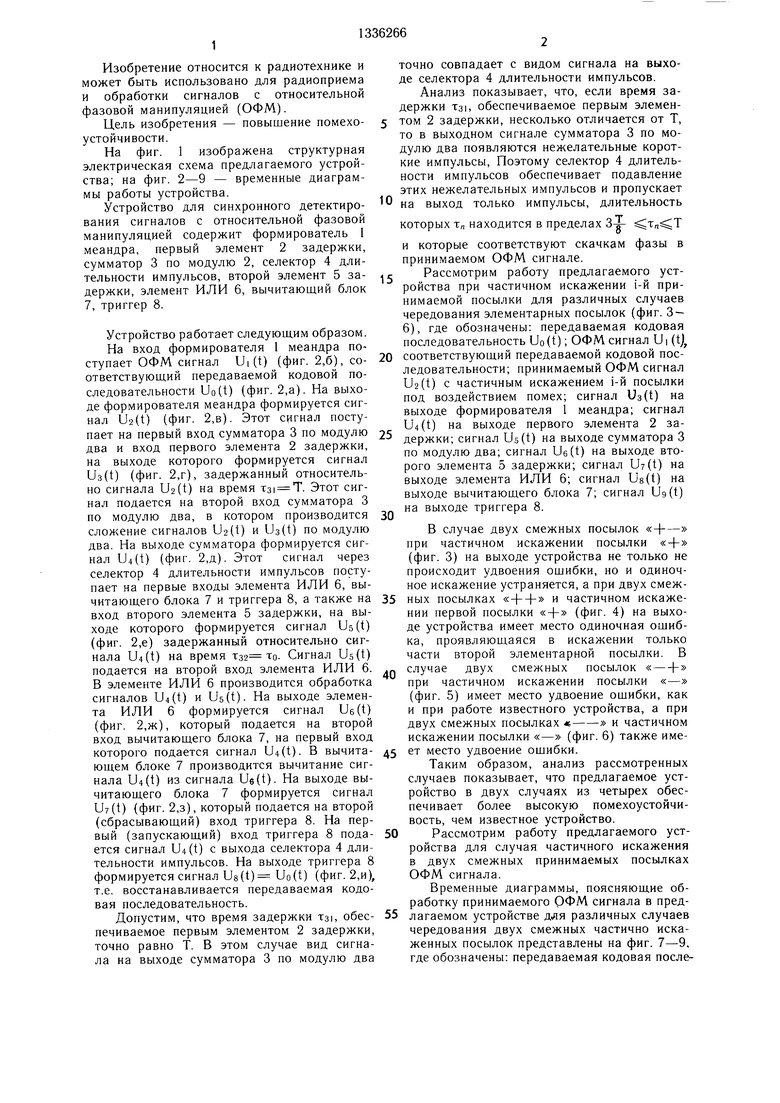

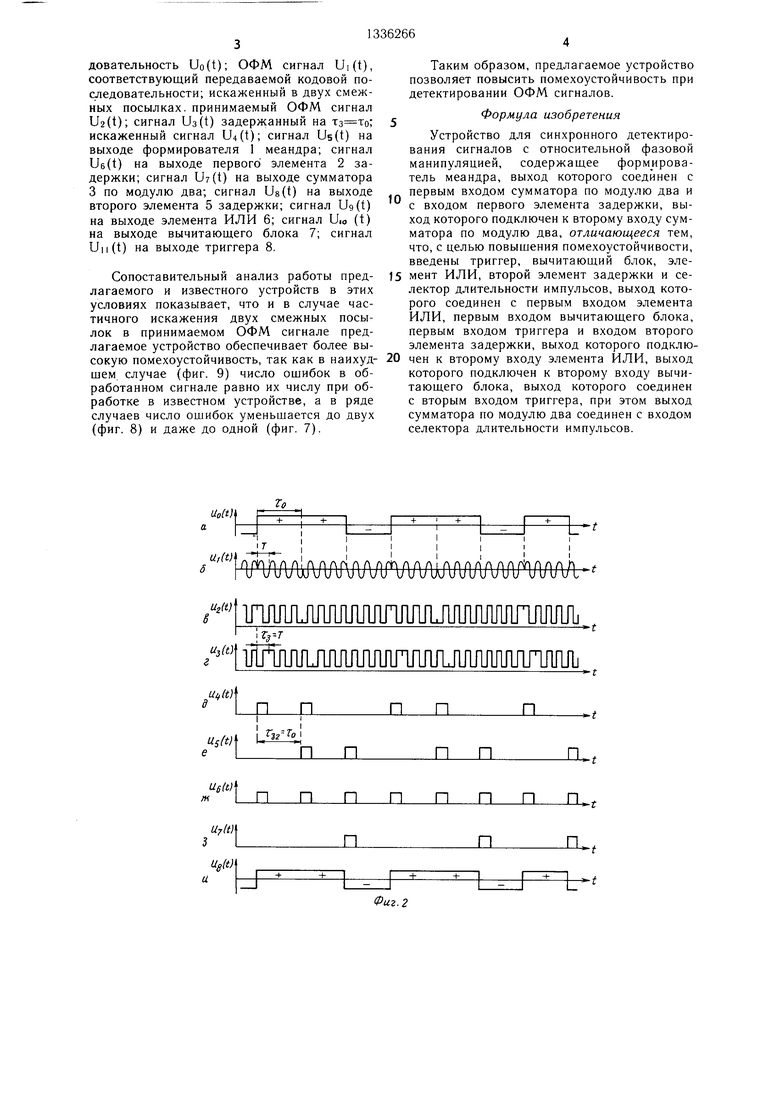

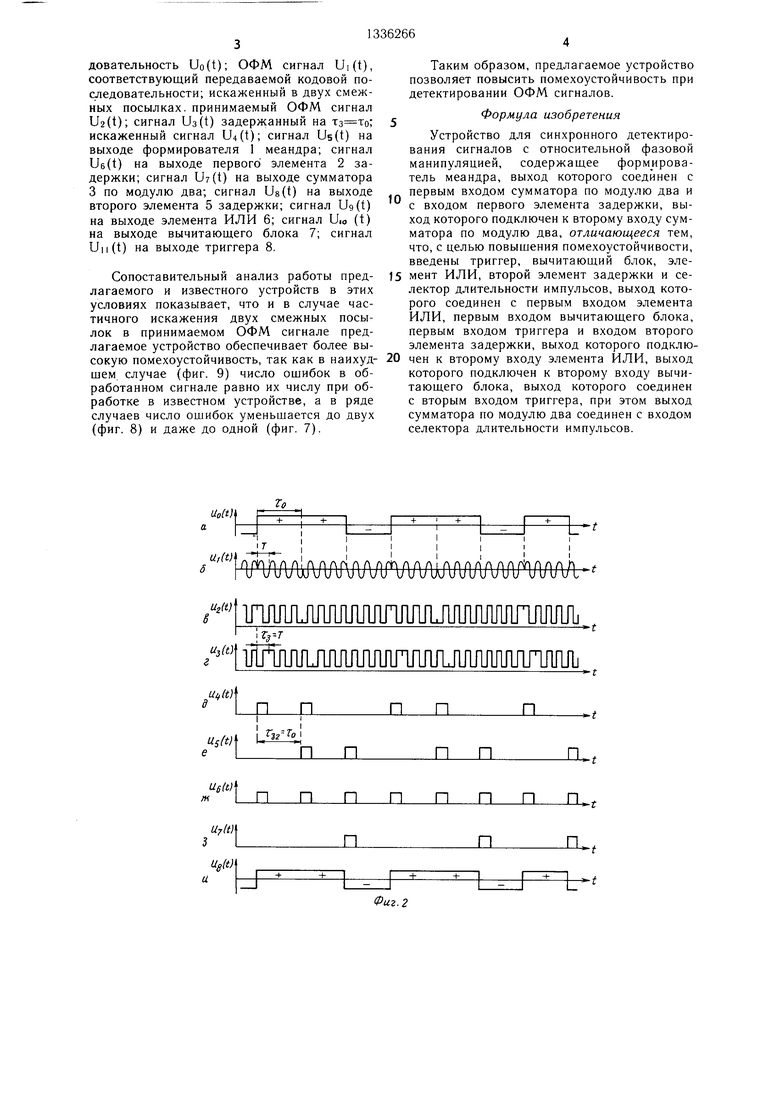

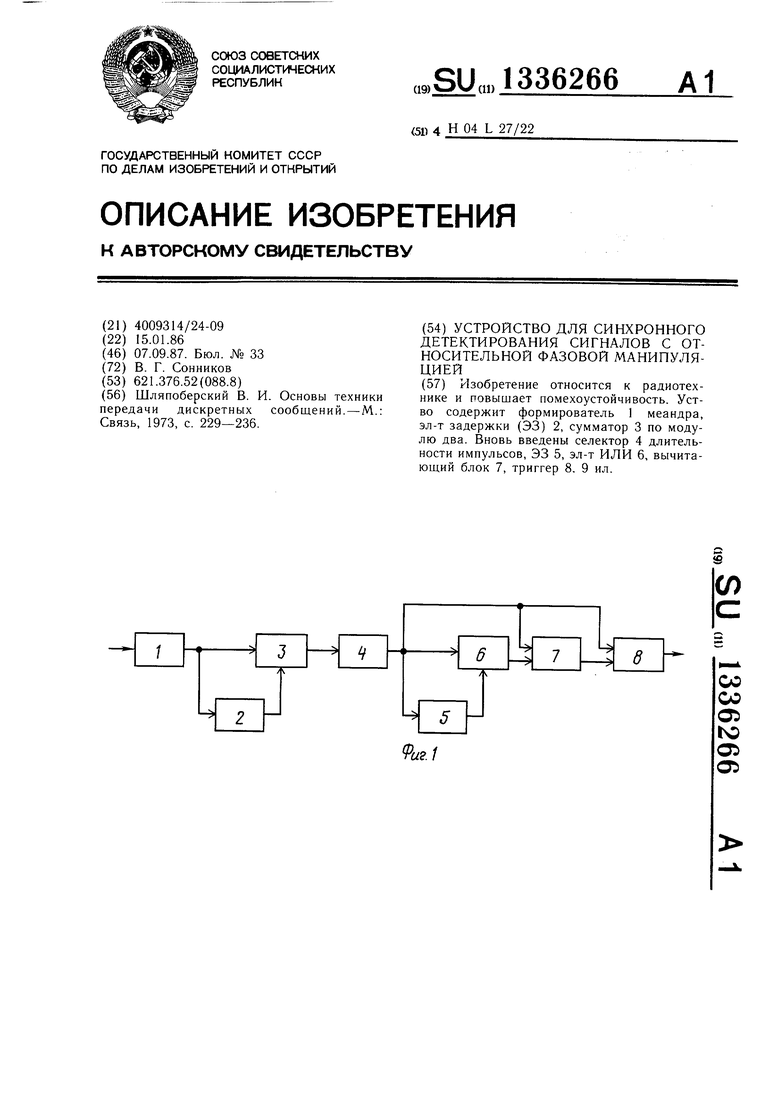

На фиг. 1 изображена структурная электрическая схема предлагаемого устройства; на фиг. 2-9 - временные диаграммы работы устройства.

Устройство для синхронного детектирования сигналов с относительной фазовой манипуляцией содержит формирователь 1 меандра, первый элемент 2 задержки, сумматор 3 по модулю 2, селектор 4 длительности импульсов, второй элемент 5 задержки, элемент ИЛИ 6, вычитающий блок 7, триггер 8.

Устройство работает следующим образом.

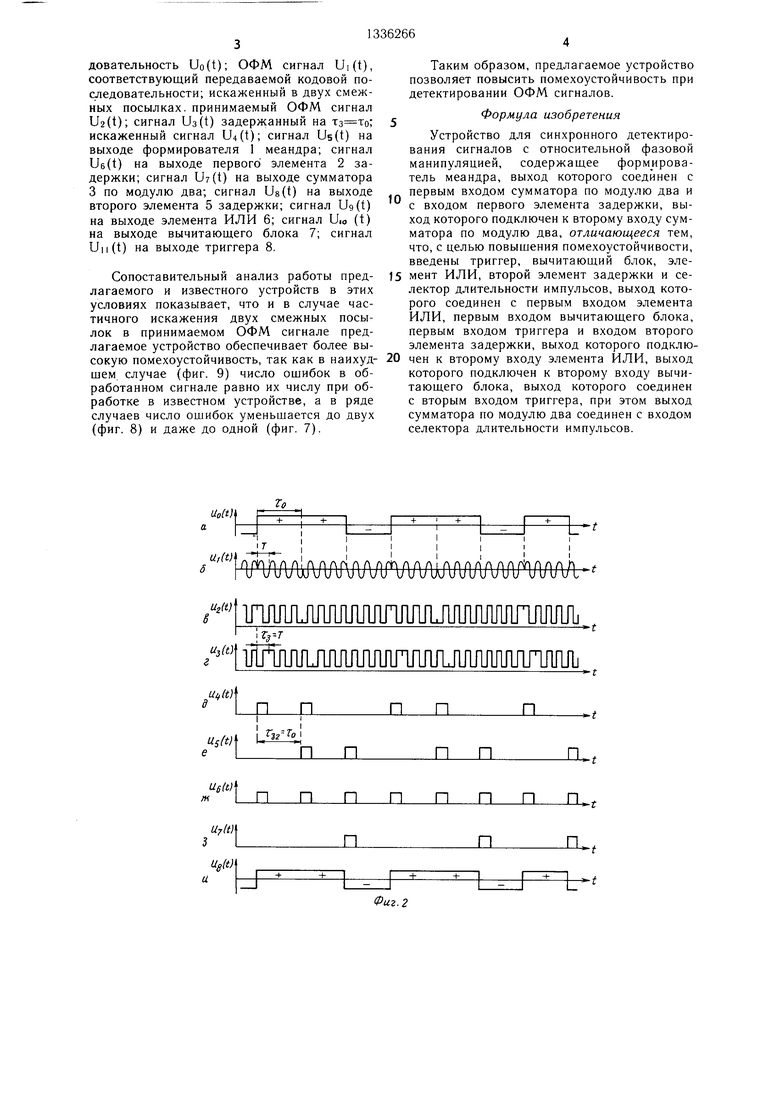

На вход формирователя 1 меандра поступает ОФМ сигнал Ui (t) (фиг. 2,6), соответствующий передаваемой кодовой последовательности Uo(t) (фиг. 2,а). На выходе формирователя меандра формируется сигнал U2(t) (фиг. 2,в). Этот сигнал поступает на первый вход сумматора 3 по модулю два и вход первого элемента 2 задержки, на выходе которого формируется сигнал из(1) (фиг. 2,г), задержанный относительно сигнала U2(t) на время тз1 Т. Этот сигнал подается на второй вход сумматора 3 по модулю два, в котором производится сложение сигналов U2(t) и U3(t) по модулю два. На выходе сумматора формируется сигнал U4(t) (фиг. 2,д). Этот сигнал через селектор 4 длительности импульсов поступает на первые входы элемента ИЛИ 6, вычитающего блока 7 и триггера 8, а также на вход второго элемента 5 задержки, на выходе которого формируется сигнал U5(t) (фиг. 2,е) задержанный относительно сигнала U4(t) на время тз2 TQ. Сигнал U5(t) подается на второй вход элемента ИЛИ 6. В элементе ИЛИ 6 производится обработка сигналов U4(t) и U5(t). На выходе элемента ИЛИ 6 формируется сигнал U6(t) (фиг. 2,ж), который подается на второй вход вычитающего блока 7, на первый вход которого подается сигнал U4(t). В вычитающем блоке 7 производится вычитание сигнала U4(t) из сигнала Ue(t). На выходе вычитающего блока 7 формируется сигнал U7(t) (фиг. 2,з), который подается на второй (сбрасывающий) вход триггера 8. На первый (запускающий) вход триггера 8 подается сигнал U4(t) с выхода селектора 4 длительности импульсов. На выходе триггера 8 формируется сигнал U8(t) Uo(t) (фиг. 2,и), т.е. восстанавливается передаваемая кодовая последовательность.

Допустим, что время задержки тз|, обеспечиваемое первым элементом 2 задержки, точно равно Т. В этом случае вид сигнала на выходе сумматора 3 по модулю два

0

точно совпадает с видом сигнала на выходе селектора 4 длительности импульсов.

Анализ показывает, что, если время задержки тзь обеспечиваемое первым элемен- том 2 задержки, несколько отличается от Т, то в выходном сигнале сумматора 3 по модулю два появляются нежелательные короткие импульсы. Поэтому селектор 4 длительности импульсов обеспечивает подавление этих нежелательных импульсов и пропускает на выход только импульсы, длительность

которых т„ находится в пределах ЗХ

и которые соответствуют скачкам фазы в принимаемом ОФМ сигнале.

г Рассмотрим работу предлагаемого устройства при частичном искажении i-й принимаемой посылки для различных случаев чередования элементарных посылок (фиг. 3 - 6), где обозначены: передаваемая кодовая последовательность Uo(t); ОФМ сигнал Ui (tj

0 соответствующий передаваемой кодовой последовательности; принимаемый ОФМ сигнал U2(t) с частичным искажением i-й посылки под воздействием помех; сигнал U3(t) на выходе формирователя 1 меандра; сигнал U4(t) на выходе первого элемента 2 за держки; сигнал U5(t) на выходе сумматора 3 по модулю два; сигнал U6(t) на выходе второго элемента 5 задержки; сигнал U7(t) на выходе элемента ИЛИ 6; сигнал U8(t) на выходе вычитающего блока 7; сигнал U9(t) на выходе триггера 8.

В случае двух смежных посылок «-|

при частичном искажении посылки (фиг. 3) на выходе устройства не только не происходит удвоения ощибки, но и одиночное искажение устраняется, а при двух смеж5 ных посылках и частичном искажении первой посылки «-|- (фиг. 4) на выходе устройства имеет место одиночная ощиб- ка, проявляющаяся в искажении только части второй элементарной посылки. В

р случае двух смежных посылок «1-

при частичном искажении посылки «- (фиг. 5) имеет место удвоение ощибки, как и при работе известного устройства, а при

двух смежных посылках « и частичном

искажении посылки «- (фиг. 6) также име5 ет место удвоение ощибки.

Таким образом, анализ рассмотренных случаев показывает, что предлагаемое устройство в двух случаях из четырех обеспечивает более высокую помехоустойчивость, чем известное устройство.

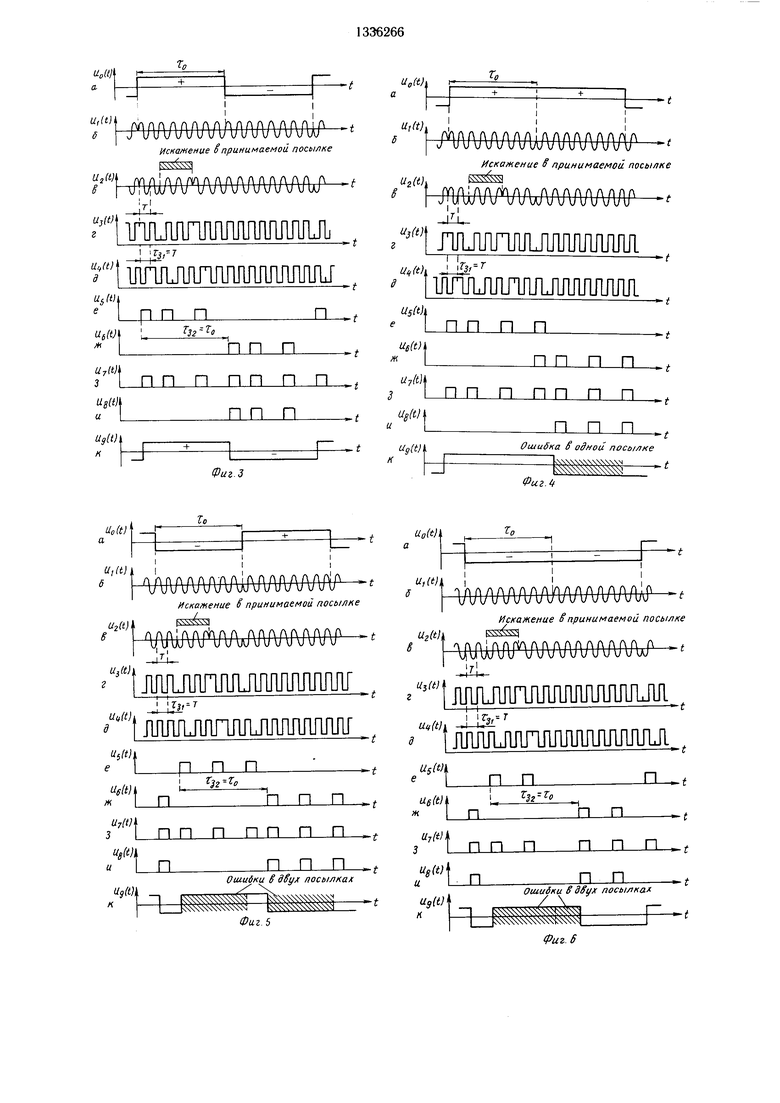

0 Рассмотрим работу предлагаемого устройства для случая частичного искажения в двух смежных принимаемых посылках ОФМ сигнала.

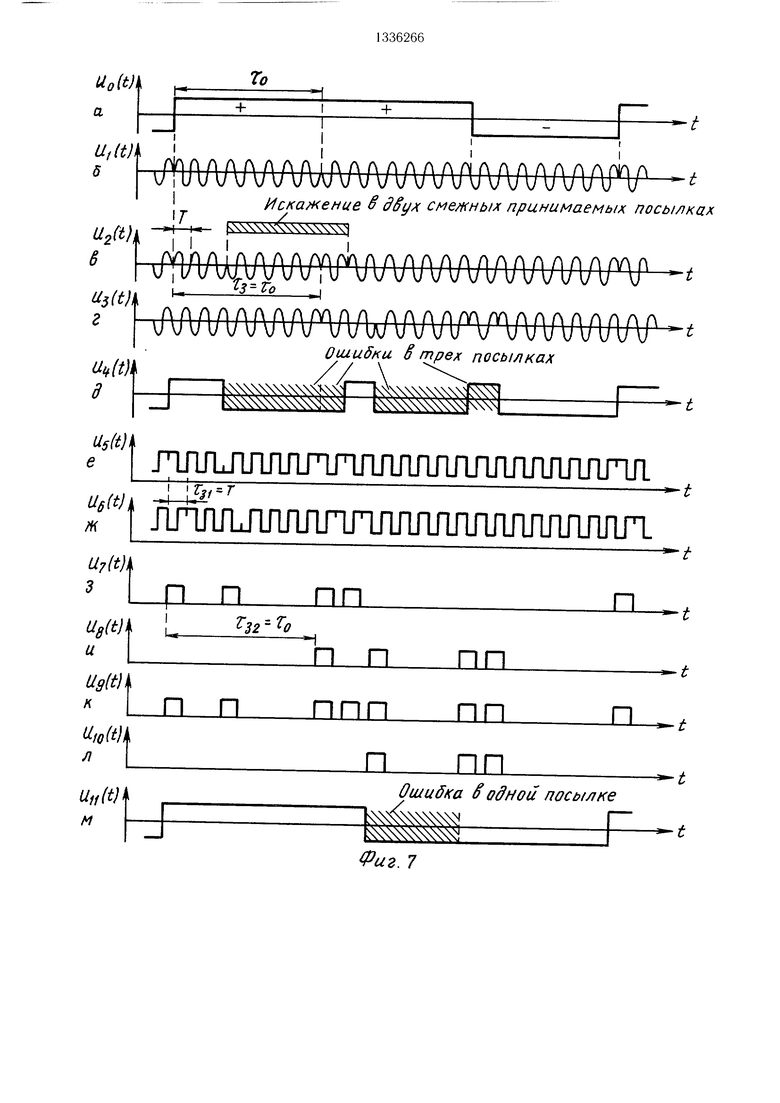

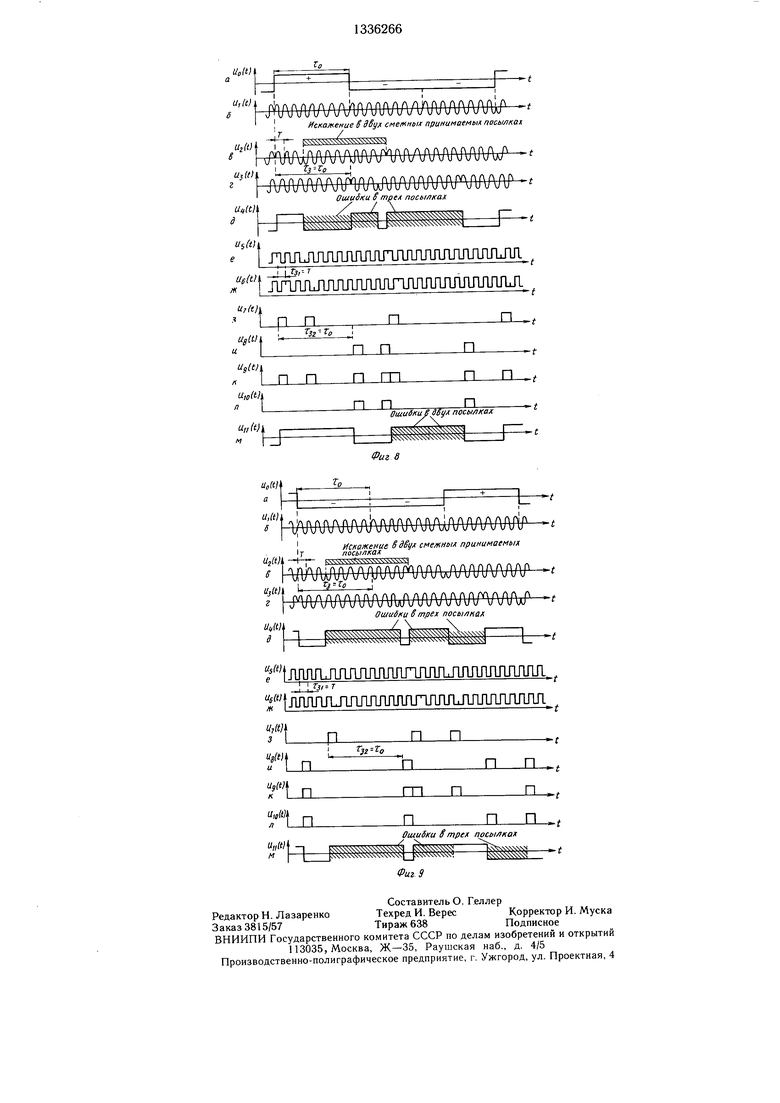

Временные диаграммы, поясняющие обработку принимаемого ОФМ сигнала в пред5 лагаемом устройстве для различных случаев чередования двух смежных частично искаженных посылок представлены на фиг. 7-9, где обозначены: передаваемая кодовая последовательность Uo(t); ОФМ сигнал Ui(t), соответствующий передаваемой кодовой последовательности; искаженный в двух смежных посылках, принимаемый ОФМ сигнал U2(t); сигнал U3(t) задержанный на искаженный сигнал U4(t); сигнал Uelt) на выходе формирователя 1 меандра; сигнал Ueit) на выходе первого элемента 2 задержки; сигнал U7(t) на выходе сумматора 3 по модулю два; сигнал UsCt) на выходе второго элемента 5 задержки; сигнал (i) на выходе элемента ИЛИ 6; сигнал Uio (t) на выходе вычитающего блока 7; сигнал U:i(t) на выходе триггера 8.

Сопоставительный анализ работы предлагаемого и известного устройств в этих условиях показывает, что и в случае частичного искажения двух смежных посылок в принимаемом ОФМ сигнале предлагаемое устройство обеспечивает более высокую помехоустойчивость, так как в наихудшем случае (фиг. 9) число ощибок в обработанном сигнале равно их числу при обработке в известном устройстве, а в ряде случаев число ошибок уменьшается до двух (фиг. 8) и даже до одной (фиг. 7).

Таким образом, предлагаемое устройство позволяет повысить помехоустойчивость при детектировании ОФМ сигналов.

Формула изобретения

Устройство для синхронного детектирования сигналов с относительной фазовой манипуляцией, содержащее формирователь меандра, выход которого соединен с первым входом сумматора по модулю два и с входом первого элемента задержки, выход которого подключен к второму входу сумматора по модулю два, отличающееся тем, что, с целью повышения помехоустойчивости, введены триггер, вычитающий блок, эле5 мент ИЛИ, второй элемент задержки и селектор длительности импульсов, выход которого соединен с первым входом элемента ИЛИ, первым входом вычитающего блока, первым входом триггера и входом второго элемента задержки, выход которого подклю0 чен к второму входу элемента ИЛИ, выход которого подключен к второму входу вычитающего блока, выход которого соединен с вторым входом триггера, при этом выход сумматора по модулю два соединен с входом селектора длительности импульсов.

Изобретение относится к радиотехнике и повышает помехоустойчивость. Уст- во содержит формирователь 1 меандра, эл-т задержки (ЭЗ) 2, сумматор 3 по модулю два. Вновь введены селектор 4 длительности импульсов, ЭЗ 5, эл-т ИЛИ 6, вычитающий блок 7, триггер 8. 9 ил. 9u2.1 СО со 05 1чЭ 05 О5

Uo(t).

U,(tj

U2(t)

11ЖЛЖШШЛ Ж11ШШП

I Г,-Г

им

Шишжяямшжишшл

f

P

Искажение Sпринимаемой посыпке

и Ml

I V|

ly

Ujlt)

тпмшжгуштмал

Иска/пение S принимаемой посылке

t

ь

i/rW

Искажение S принимаемой, посылке

«2

rl

Искажение S принимаемой посылке

Фиг. 7

U,M

zf

/ f j|lAM/ /W M/ AA/ / / m/W / IИскажение S SSyx сме/кних принимаемыл пасылкак

ilг(t) 1

UjUl

UN

E

Ошибки S fnpejt посылках fiSSS:

: SsSS: g:g; : : :g

yffyffiyfffjf;yi: :yf r f iy yyyffyy::yy.

лллJшлJlJШЛлллJlягlлшшnшum

Uftti

Тз,- r

JlfnMJШЛJШЛJШЛЛЛЛШШЯnЛЛJLГl

U,(th

Ugltl

Ugltn

л I п п u,o(th

u,,(t)

Г

Uslt а

U,(f) S

Искажение S deuf смеянтл принимаемых ,1 /ill .,посылках

U2 f/t t 144444444 444444444444441

Г)--TO

jM-,

IjnAAMA/W AIWWVV AAmОшибки S трех посылка .

,

«sW

|ЛМП 1Ш1ЛЛЛШ1ГиШГи1ПЛШШШ1Ш1

Fejt посылках

: SsSS: g:g; : : :g

f iy yyyffyy::yy.

л

П1

п п

XL

п гп

JHП

п п

f/(a/ i6yXL

Ошибки ё iCyx посылках

f 4-WNXsS OCC

Фиг в

| Шляпоберский В | |||

| И | |||

| Основы техники передачи дискретных Связь, 1973, с | |||

| Приспособление для подачи воды в паровой котел | 1920 |

|

SU229A1 |

| сообщений | |||

| - М.: | |||

Авторы

Даты

1987-09-07—Публикация

1986-01-15—Подача