00

о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронного детектирования фазоманипулированных сигналов | 1986 |

|

SU1363525A1 |

| Устройство для синхронного детектирования сигналов с относительной фазовой манипуляцией | 1986 |

|

SU1336266A1 |

| Устройство для приема дискретных составных частотных сигналов с внутриимпульсной фазовой манипуляцией | 1987 |

|

SU1425870A1 |

| Устройство для синхронного детектирования фазоманипулированных сигналов | 1984 |

|

SU1177945A1 |

| Приемник цифрового линейного сигнала | 1986 |

|

SU1462509A1 |

| Детектор частотно-манипулированных сигналов | 1986 |

|

SU1327315A1 |

| Синхронный детектор фазоманипулированных сигналов | 1987 |

|

SU1483666A1 |

| Временной селектор видеоимпульсов для дальномера | 1982 |

|

SU1070495A1 |

| Система передачи и приема дискретной информации | 1983 |

|

SU1119184A1 |

| Устройство для детектирования сигналов с фазовой и относительной фазовой манипуляцией | 1988 |

|

SU1559422A1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение помехоустойчивости путем частичного устранения парного группирования ошибок. Устр-во содержит формирователь 1 меандра, эл-ты задержки 2 и 5, сумматор 3 по модулю два, селектор 4 длительности импульсов, эл-т И 6, ключи 7 и 8 и триггер 9. Эл-т И 6 формирует сигнал, поступающий на управляющие входы ключей 7 и 8, сигналы с выходов которых поступают на запускающий и сбрасывающий входы триггера 9, восстанавливающего передаваемую кодовую последовательность. Цель достигается введением эл-та И 6 и ключей 7 и 8. 2 ил.

Фи. /

Изобретение относится к радиотехнике и может быть использовано в системах передачи информации.

Цель изобретения - повышение помехоустойчивости путем частичного устранения парного группирования ошибок

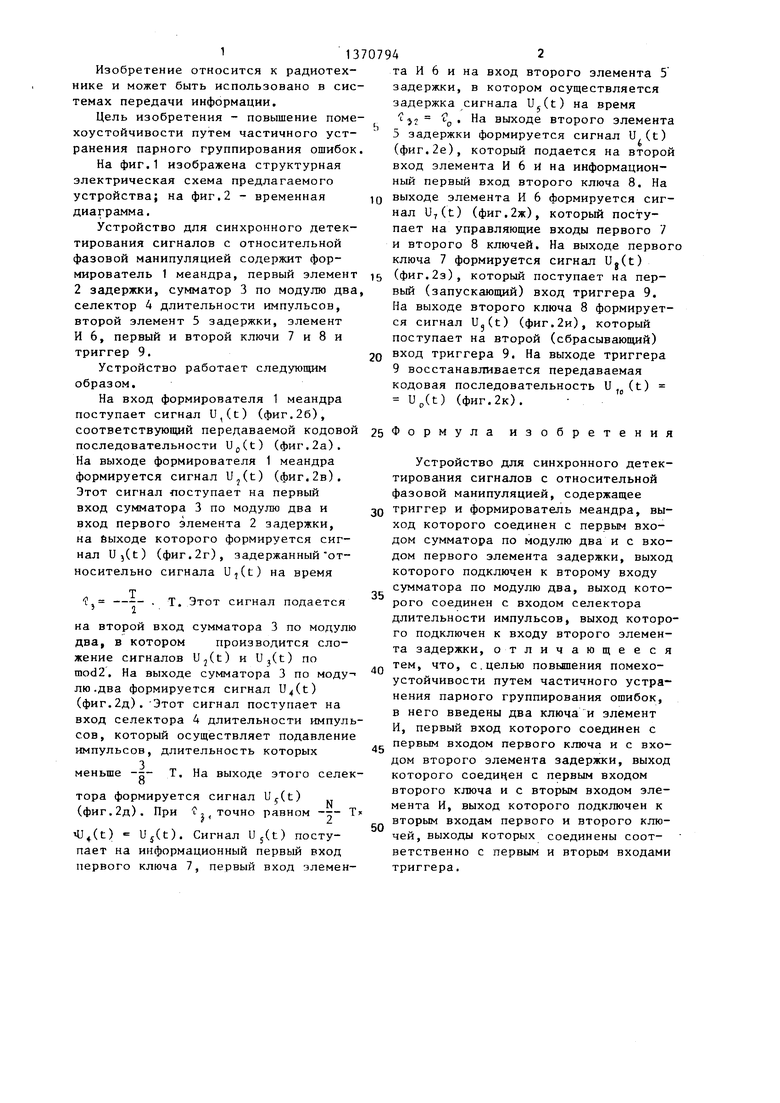

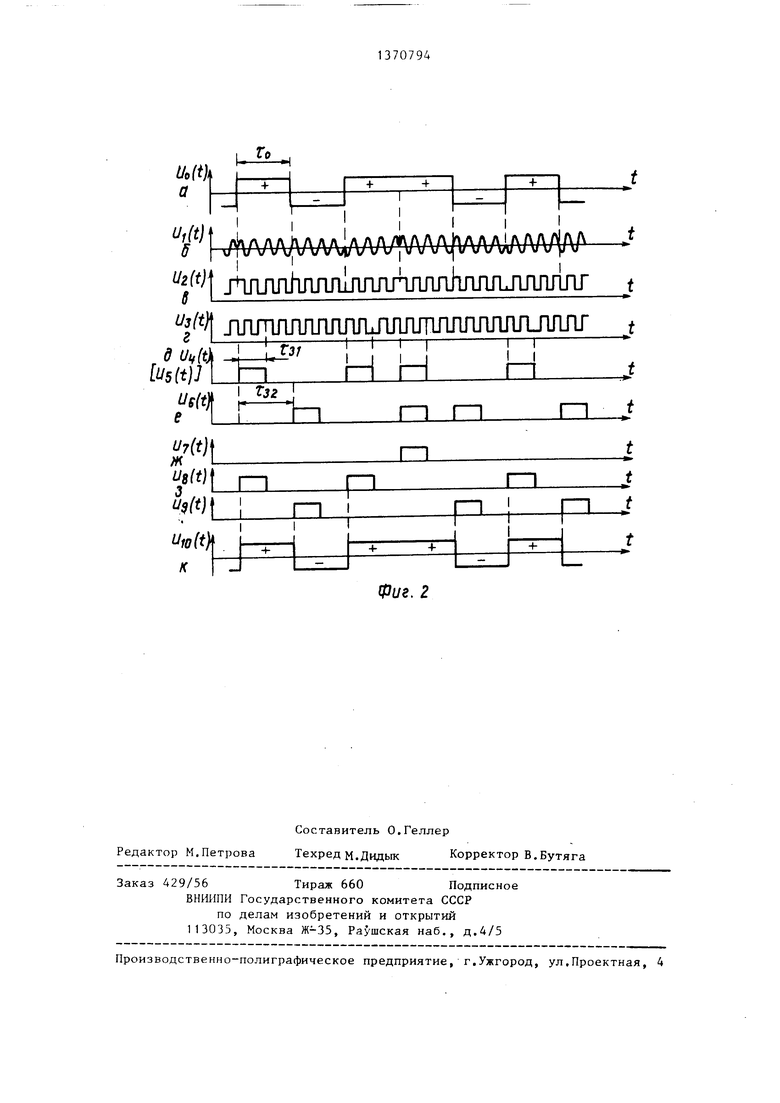

На фиг.1 изображена структурная электрическая схема предлагаемого устройства; на фиг.2 - временная диаграмма.

Устройство для синхронного детектирования сигналов с относительной фазовой манипуляцией содержит формирователь 1 меандра, первый элемент 2 задержки, сумматор 3 по модулю два селектор 4 длительности импульсов, второй элемент 5 задержки, элемент И 6, первый и второй ключи 7 и 8 и триггер 9.

Устройство работает следующим образом.

На вход формирователя 1 меандра поступает сигнал U,(t;) (фиг.26), соответствующий передаваемой кодовой последовательности ) (фиг.2а). На выходе формирователя 1 меандра формируется сигнал Uj(t) (фиг.2в). Этот сигнал поступает на первый вход сумматора 3 по модулю два и вход первого элемента 2 задержки, на выходе которого формируется сигнал Uj(t) (фиг.2г), задержанный относительно сигнала U,(t) на время

Т о -± 1 на второй вход сумматора 3 по модулю

Т. Этот сигнал подается

два, в котором

производится сложение сигналов ) и Uj(t) по mod2. На выходе сумматора 3 по моду-- лю .два формируется сигнал U4(t) (фиг.2д). Этот сигнал поступает на вход селектора 4 длительности импульсов, который осуществляет подавление импульсов, длительность которых

меньше

На выходе этого селек-|-т.

тора формируется сигнал U(t) (фиг.2д). При LJ точно равном

4J(t) Uj(t). Сигнал U;(t) поступает на информационный первый вход первого ключа 7, первый вход элемен

входы первого 7 На выходе первого

та И 6 и на вход второго элемента 5 задержки, в котором осуществляется задержка сигнала Uj(t) на время выходе второго элемента 5 задержки формируется сигнал U (t) (фиг.2е), который подается на второй вход элемента И 6 и на информационный первый вход второго ключа 8. На выходе элемента И 6 формируется сигнал ) (фиг.2ж), которьш поступает на управляющие и второго 8 ключей, ключа 7 формируется сигнал Uj(t)

(фиг.2з), который поступает на первый (запускающий) вход триггера 9. На выходе второго ключа 8 формируется сигнал Uj(t) (фиг.2и), который поступает на второй (сбрасывающий)

вход триггера 9. На выходе триггера 9 восстанавливается передаваемая кодовая последовательность U(t) U(t) (фиг.2к).

Формула изобретения

Устройство для синхронного детектирования сигналов с относительной фазовой манипуляцией, содержащее триггер и формирователь меандра, выход которого соединен с первым входом сумматора по модулю два и с входом первого элемента задержки, выход которого подключен к второму входу сумматора по модулю два, выход которого соединен с входом селектора длительности импульсов, выход которого подключен к входу второго элемента задержки, отличающееся тем, что, с.целью повышения помехоустойчивости путем частичного устранения парного группирования ошибок, в него введены два ключа и элемент И, первый вход которого соединен с первым входом первого ключа и с входом второго элемента задержки, выход которого соединен с первым входом второго ключа и с вторым входом элемента И, выход которого подключен к вторым входам первого и второго ключей, выходы которых соединены соответственно с первым и вторым входами триггера.

Фие. 2

| Устройство для синхронного детектирования сигналов с относительной фазовой манипуляцией | 1986 |

|

SU1336266A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-01-30—Публикация

1986-01-24—Подача