Изобретение относится к области автоматики и вычислительной техники и может быть использовано в различных устройствах автоматики повышенной надежности.

Целью изобретения является исключение сбоев в каналах делителя при рассинхронизации входных импульсов.

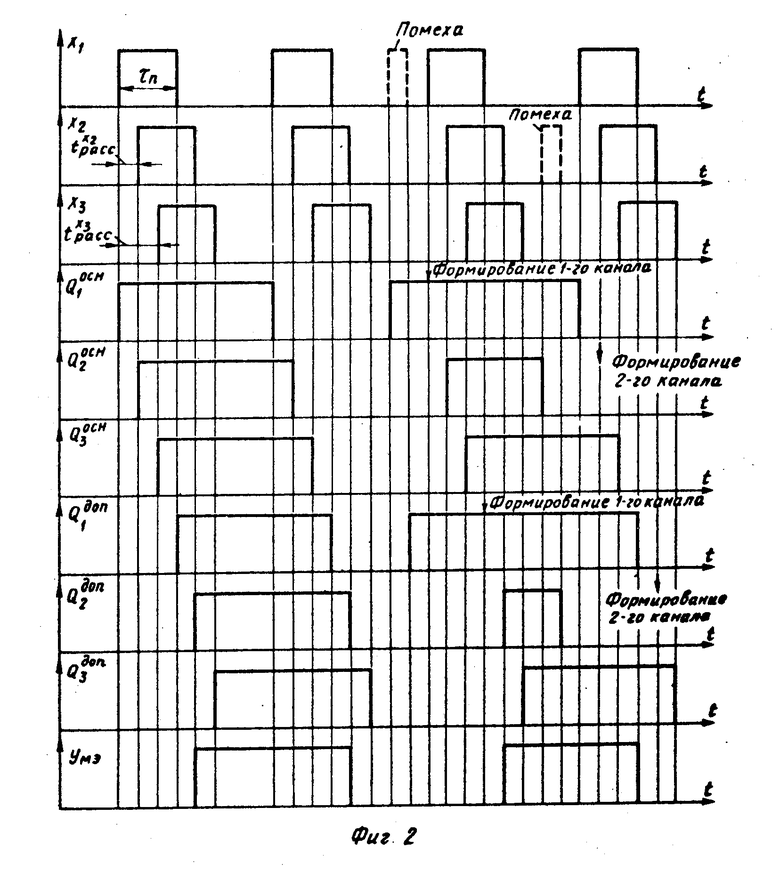

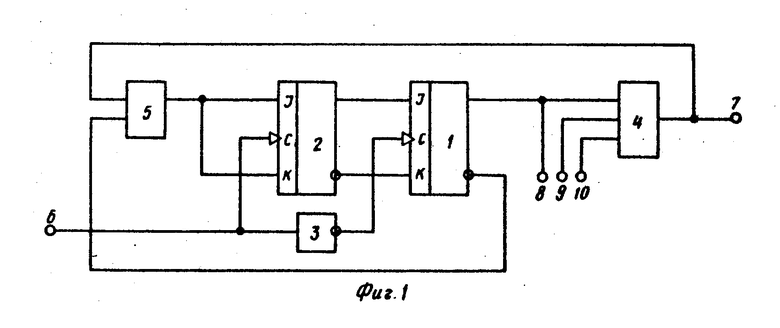

На фиг. 1 приведена функциональная схема одного канала делителя; на фиг. 2 временная диаграмма его работы.

Каждый канал делителя содержит первый IK-триггер 1, второй IK-триггер 2, элемент НЕ 3, мажоритарный элемент 4, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5, вход 6 канала, выход 7 канала, обменный входы 9 и 10 канала, выход 8 и входы 9 и 10 используются для связей между тремя каналами (на фиг. 1 изображен один из идентичных каналов).

Делитель работает следующим образом. Допустим, что в исходном состоянии прямые выходы IK-триггеров 1 и 2 всех трех каналов имеют состояние соответственно "0", "0" и "0", а поступающие входные импульсы имеют длительность τи и рассинхронизацию относительно первого канала t

Допустим, что на входе 6 первого канала появился импульс помехи, нарушающий фазировку IK-триггеров 1 и 2 первого канала относительно двух других. В этом случае сигналы с выхода мажоритарного элемента 4 и с инверсного выхода дополнительного IK-триггера 1 первого канала совпадают, и на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5 формируется сигнал запрета счета. В результате в момент прихода переднего фронта входного импульса первого канала основной IK-триггер 2 не меняет своего состояния. Не меняет своего состояния и дополнительный IK-триггер 1 в момент прихода заднего фронта входного импульса первого канала. Во втором и третьем каналах происходит переключение IK-триггеров 1 и 2 по соответствующим фронтам входных импульсов. Таким образом, во всех трех каналах на прямых выходах IK-триггеров 1 и 2 образуются сигналы одинакового уровня, т.е. происходит фазирование первого канала под правильную работу двух других (см. стрелки над сигналами прямых выходов Q

Допустим теперь, что на входе второго канала прошел импульс помехи, нарушающий фазировку IK-триггеров 1, и 2 второго канала относительно двух других. В этом случае также сигналы с выхода мажоритарного элементам 4 и с инверсного выхода дополнительного IK-триггера 1 второго канала совпадают по уровню, и на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5 формируется сигнал запрета счета. Поскольку входной импульс в первый канал по времени поступает раньше, чем во второй и в третий, основной IK-триггер 2 первого канала переключается по переднему фронту, а дополнительный IK-триггер 1 сохраняет свое состояние до прихода заднего фронта входного импульса. Но, поскольку передний фронт входного импульса во втором канале приходит раньше заднего фронта входного импульса первого канала, сохраняются условия фазирования, так как изменения уровня сигнала на выходе мажоритарного элемента 4 еще не произошло. В результате IK-триггеры 1 и 2 второго канала не изменяют своего состояния по соответствующим фронтам входного импульса, и на прямых выходах IK-триггеров 1 и 2 всех каналов образуются сигналы одинакового уровня, т.е. происходит фазирование второго канала под правильную работу двух других (см стрелки над сигналами прямых выходов Q

Аналогично происходит фазирование IK-триггеров 1 и 2 третьего канала, если на него поступил импульс помехи.

В общем случае условия фазирования будут сохранены, если будет выполняться соотношение tрасс<τио. Величина tрасс, как правило, определяется неодинаковым временем распространения сигнала в каждом из каналов от входа логического элемента (или их совокупности) до его выхода, поэтому выполнение этого соотношения не представляет никаких трудностей.

Таким образом, введение в каждый канал трехканального резервированного делителя частота на два дополнительного IK-триггера и элемента НЕ позволило повысить надежность работы и сохранить условия фазирования при рассогласовании входных импульсов между каналами.

| название | год | авторы | номер документа |

|---|---|---|---|

| Трехканальный резервированный делитель частоты на два | 1984 |

|

SU1215198A1 |

| Резервированный делитель частоты следования импульсов | 1986 |

|

SU1367152A2 |

| МАЖОРИТАРНО-РЕЗЕРВИРОВАННЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2015617C1 |

| Трехканальное резервированное устройство для синхронизации сигналов | 1983 |

|

SU1221769A1 |

| Устройство для управления многофазным инвертором | 1978 |

|

SU752749A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1988 |

|

SU1554153A1 |

| Резервированный делитель частоты следования импульсов | 1981 |

|

SU961155A1 |

| Резервированный делитель частоты | 1984 |

|

SU1243129A1 |

| Устройство для синхронизации резервированного делителя частоты | 1981 |

|

SU1001104A1 |

| Мажоритарное устройство | 1984 |

|

SU1399905A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в различных устройствах автоматики повышенной надежности. Целью изобретения является исключение сбоев в каналах делителя при рассинхронизации входных импульсов. Каждый канал делителя содержит первый 1 и второй 2 IK-триггеры, элемент НЕ 3, мажоритарный элемент 4, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5, вход 6 канала, выход 7 канала. В делителе обеспечивается фазирование сигналов во всех каналах при рассинхронизации входных импульсов, достигающей продолжительности самих импульсов, и при действии кратковременных помех на вход одного из каналов. 2 ил.

Трехканальный резервированный делитель частоты на два, содержащий в каждом канале первый IK-триггер, мажоритарный элемент и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, подключенный входами к выходу мажоритарного элемента и инверсному выходу первого IK-триггера, прямой выход которого соединен с одним из входов мажоритарного элемента данного канала и одноименными входами мажоритарных элементов соседних каналов, а выходы мажоритарных элементов являются выходами каналов, отличающийся тем, что, с целью исключения сбоев в каналах делителя при рассинхронизации входных импульсов, в каждый канал делителя введены второй IK-триггер и элемент НЕ, подключенный выходом к входу синхронизации первого IK-триггера, I- и K-входы которого соединены соответственно с прямым и инверсным выходами второго IK-триггера, вход канала связи с входом синхронизации второго IK-триггера и входом элемента НЕ, а выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к I- и K-входам второго IK-триггера.

| 1972 |

|

SU410559A1 | |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Трехканальный резервированный делитель частоты на два | 1984 |

|

SU1215198A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1996-12-27—Публикация

1986-03-20—Подача