(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ МНОГОФАЗНЫМ ИНВЕРТОРОМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления @ -фазным инвертором | 1984 |

|

SU1248019A1 |

| Устройство для управления многофазным инвертором | 1977 |

|

SU663065A1 |

| Резервированное пересчетное устройство | 1980 |

|

SU1042184A1 |

| Устройство для контроля многоканальных импульсных последовательностей | 1989 |

|

SU1732332A1 |

| ТРЕХКАНАЛЬНЫЙ РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ НА ДВА | 1986 |

|

SU1336788A1 |

| Преобразователь напряжения в частоту | 1986 |

|

SU1363471A1 |

| Резервированное пересчетноеуСТРОйСТВО | 1978 |

|

SU834923A1 |

| Резервированное многоканальное устройство для формирования тактовых импульсов | 1990 |

|

SU1714607A1 |

| Резервированное пересчетное устройство | 1982 |

|

SU1034196A1 |

| Мажоритарно-резервированный делитель частоты | 1975 |

|

SU664299A1 |

Изобретение относится к электротехнике, а именно к устройствам управления многофазными инверторами, используемы ми в системах электропитаюш и электро привода. Известно устройство дпя. управлешш трехфазным инвертором, содержащее задающий , три триггера, счетные входы которых соединены с выходом задающего генератора, а раздельные входы каждого триггера соединены соответстветшо с инверсным в прямь м выходами предьгдущего триггера TL. Недостатком данного устройства-является невысокое качество управлешш. Н(аиболее близким по технической сущности к изобретению является устрой ство для управления многофазным инвертором сод жашее (Задающий генератх три канала пересчетных схем на триггерах и дополнительные . фазировання Д. Недостатком такохч) устройства также является сравнительная сложность. так как схема фазирования каждого канала содержит две схемы ИЛИ и схему эквивалентности. : Цель изобретения - упрощение устройства и повышение надежности:. Поставленная цель достигается т&л, что устройство для управления многофазным инвертором снабжено двумя блоками выделения заднего фронта импульса, вход первого из вышеуказанных блоКОВ соешпген с выходом п вого мажоритарного элемента, выход первого блока выделения заднего фронта импульса соед1шен со входами установки в О первых триггеров и входами ус- , тановкй в 1 остальных триггеров каждого канала , выход второго блока выделения заднего фронта импульсов, соединен со входами установки в 1 первых триггеров и входами установки в СУ остальных триггеров каждого канала. При синфазной работе всех пересчетных схем сигналы на выходах триггеров и соответствующих мажоритарных элементов совпадают во времени. Если триггеры пересчетных схем имеют прямые связи с выходов каясдого гфедшествующего Tpiirrepa на входы последующего и перекрестные связи с выходовпоследнего триггера на входы первого, то после переключения первого триггера из состояния 1 в О и до момента переключения первого триггера из состояния в О и до момента переключения

второго триггера второй и последующие по кольцу триггеры находятся в состоянии I.

При переключении первого триггера из состояния О в I второй и последующие триггеры находятся в состоянии О, Сигналы на выходах соответствующих мажоритарных элементов изменяются аналогично.

Сигналы с выходов схемы фазирования {со схем выделения заднего фронта импульса), поступающие при переключении первого триггера из состояния 1 в О или из состояния О в 1, не изменяют состояния триггеров. При первоначальном включении устройства или при случайном сбое от воздействия помехи может наруиттся синфазная работа каналов, поэтому сигналы на выходах триггеров и соответствующих мажоритарных элементов не совпадают во времени. В этом случае сигналы с первого или второго выходов схемы фазирования, посту пающий на входы установки в О и 1 устанавливают триггеры каналов в состо ние 011 ......11 или 100....00. Таким

образом производится фазирование каналов, восстанавшшается их синфазность.

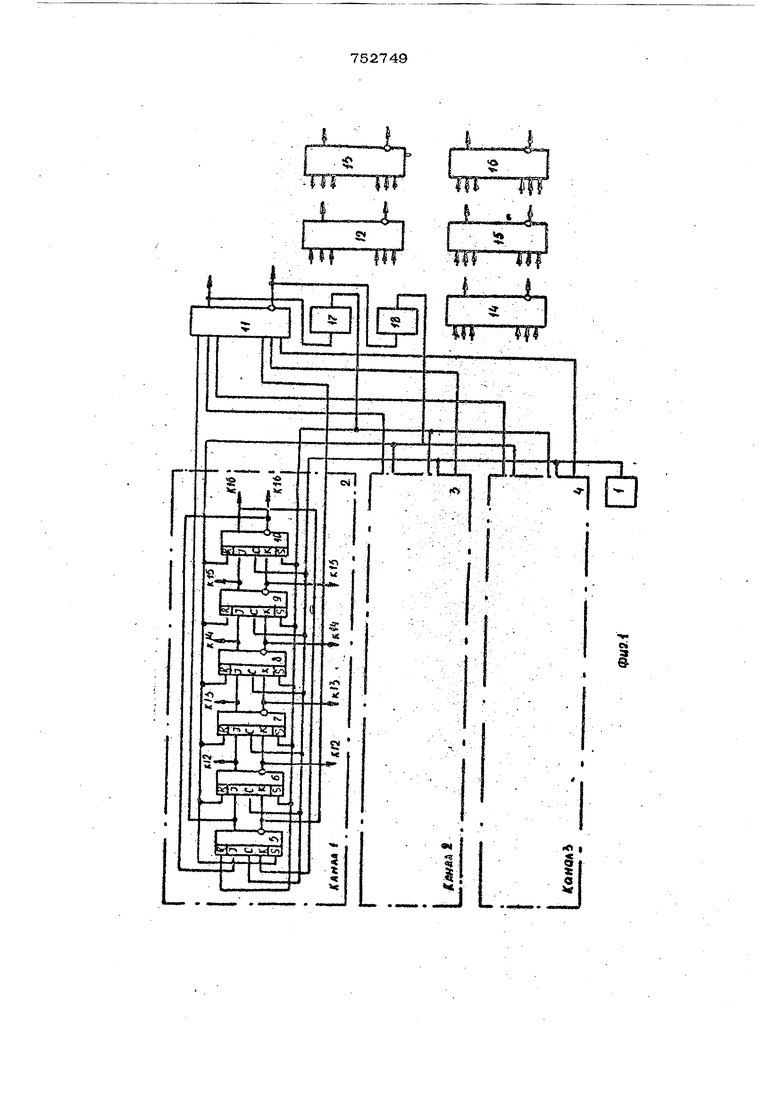

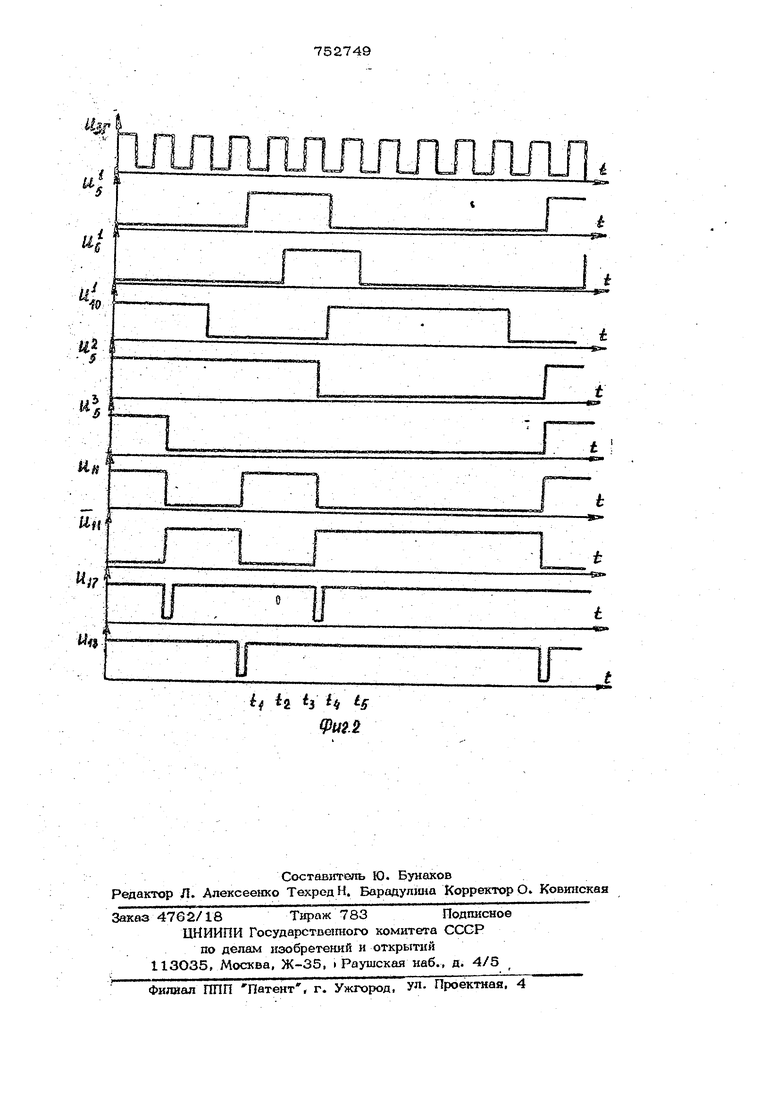

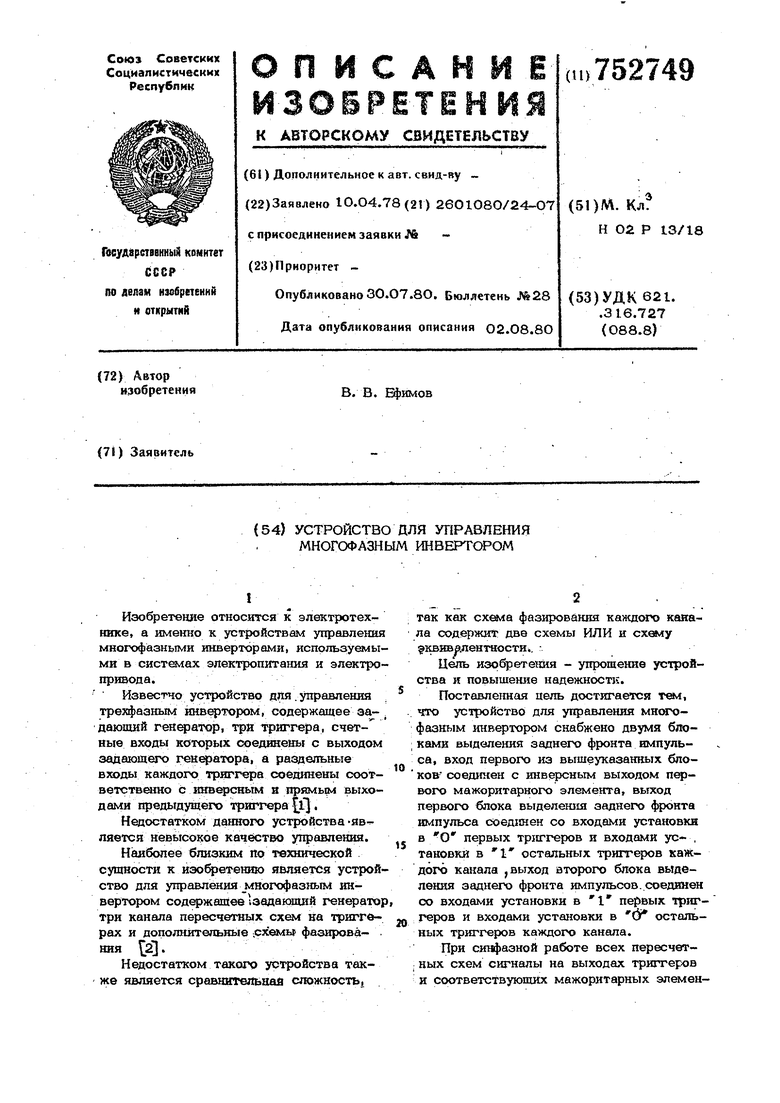

На фиг. 1 изображена схема устройства (на примере устройства управления двенадцатифазным инверторюм), на фиг.2 эпюры напряжений на элементах устройства управления при работе сх&лы фазирования каналов.

Устройство управления содержит задающий генератор 1, три одинаковых канала 2,3,4 пересчетных схем на триггерах 5-10, шесть выходных мажоритарных элементов 11-16 и узел фазировани содержащий два блока 17 и 18 вьщеления заднего фронта импульса. Каждая фаза выходного напряжения устройства формируется мажоритарными элементами 11-16, на входы которых поступают пря мые и инверсные :сигналы с одноименных триггеров трех каналов. : Предположшч, что до момента t выходы блоков 17 и 18 условно отключены

от входов установки в О и I всех . В этом случае фазы переключения одноименных триггеров могут отличаться одна от другой на произвольный угол, кратный ЗО эл.град.

Эпюры напряжений на прямых выходах триггеров 5, 6 и 1О первого канала

обозначены соответственно (}к U.И uA „- ( (lo

эпюры, напряжений на прямых выходах

триггеров 5 второго и третьего каналов обозначены соответственно Uy и Uy . Эпюры напряжений на прямом и инверсном выходе мажоритарного элемента 11 обозначены U и U на выходах блоков 17 и 18 и .

Пусть в момент времени 1 выходы схем 17 и .18 оказываются подключенными ко входам установки в Oj.-t (входы R ) и в 1 (входы S ) всех триггеров. В этот момент состояние триггеров 5-1О первого канала рав.но 1ООООО, второго канала - 111110 и третьего - ОО01И. На выходах мажоритарного элемента 11 и на входах блоков 17 и 18 сигналы равны Лог. и Лог.О соответственно. В момент времени действием импульса синхронизашш происходит переключение одного триггера в каждом канале. Состояние триггеров 5-10 в первом канале становится 11ОООО, во втором -1111Ц

в третьем - ОООО11. На выходе схемы 11, на входах и выходах блоков 17 и 1 сигнал не меняется. В момент времени t под действием очередного импульса синхронизации происходит очередное переключение по одному триггеру в каждом канале и состояние триггеров 5-1О в каналах становится равным 111ООО, 011111 и ООООО1 соответственно. Сигналы на выходах схемы 11 и на входах блоков 17 и 18 изменяются. На выходе блока 17 с момента времени i j до момента t , сигнал равен Лог.О. Этот сигнал с уровнем Лог.О воздействуя на входы установки в О и в 1 триггеров 5-1О каждого канала устанавливает триггеры 5 каждого канала в состояние Лог.О и триггеры 6-10 каждого канала в состояние Лог,. На этом процесс фазирования заканчивается, и при поступлении очередных импульсов синхронизации с момента времени t 5 все каналы работают синфазно.

Для такого устройства не требуется СК&4Ы первоначальной установки синфазности каналов, схемы устранения ложны режимов п)еключения триггеров фааорасщепителя в каждом канале. Таким об разом, схема фазирования в данном устройстве, являясь также и схемой, устраняющей ложные режимы переключения триггеров фазорасщепителей, позволяет значительно упростить устройство управл ния, в таком устройстве длительность .процесса фазирования всегда меньше полулериода выходного напряжения, так как фазирование может производиться либо блоком 17, либо 18. В случае не обходимости из устройства можно исклю чить либо блок 17 либо 18, при этом длительность процесса фазирования уве.личивается, но остается всегда меньше периода выходного напряжения. Использование в схеме фазирования нового элемента - блока выделения заднего фронта импульса-выгодно отличает данное устройство управления от известного так как уменьшается число элемен тов в схеме фазирования (с 9 до 2 или l). Разработанная схема может применяться во всех областях преобразователь ной техники, где требуется создание резервированных по трехканальной схеме приборов, а также в тех областях техники, где используются кольцевые счетчики, регистры сдвига, делители частоты, вьшолненные по трехканальной Формула изобретения Устройство для управления многофазным инвертором, содержащее задающий , три одинаковых канала пересчетных схем на ipHrrepax, с прямыми связями с выходов каждого предшествующего триггера на входы последующего и перекрестными связями с выходов последнего триггера на входы первого и мажоритарные элементы по числу фаз, отличаюш е е с тем, что, с целью упрощения устройства и повышения его надежности, оно снабжено двумя блоками выделения заднего фронта импульса, вход первого из вышеуказанных блоков соединен с прямым выходом первого мажоритарного элемента, вход второго из вышеуказанных блоков соединен с выходом первого мажоритарного элемента, выход первого блока выделения заднего фронта импульса соединен со входами установки в О первых триггеров д входами установки в остальных триггеров каждого канала, выход второго блока выделения заднего фронта импульса соединен с входами установки в первых триггеров и входами установки в О остальных триггеров каждого канала. Источники информации, принятые во внимание при экспертизе 1,Авторское свидетельство СССР № 546084, кл. Н 02 Р 13/18, 1978. 2.Авто юкое свидетельство СССР по заявке № 2439169/24-О7, кл. Н 02 Р 13/18, 1977.

«

Til rr

.

4

Tpr iiy

if ig 3 H 5 U.2

Авторы

Даты

1980-07-30—Публикация

1978-04-10—Подача