Изобретение относится к области вычислительной техники и может применяться, в частности при использовании микропроцессов для различных задач, например, для управления процессами обработки и переработки, работающих в реальном масштабе времени.

Известна система соединения нескольких вычислительных устройств. В DE-OS 24 46 970 - несколько работающих независимо друг от друга BbRHC- лительных устройств соединены с общим запоминающим устройством посредством интерфейса, причем последовательность- очередности вычислительных устройств при обращении к запоминающему устройству устанавливается блоком определения приоритета.

При этом виде соединения обмен дан-2о ронного, непосредственного и бесконфпыми осуществляется всегда через общее запоминающее устройство.

Известны соединения периферийного типа посредством специальных устройств управления сопряжением. По DE-OS 26 45 341 для каждой соединительной связи между двумя вычислительными устройствами расположено устройство сопряжения. Оно может быть выполнено как компактный самостоятельный блок или может быть включено в каждое соединяемое вычислительное устройство.

В устройствах с более чем двумя вычислительными устройствами системы нескольких вычислительных устройств могут быть вьшолнены по структуре кольца или звезды.

Педостаток таких систем вычислительных ycTpoficTB заключается в том, что для каждого соединения между двумя вычислительными устройствами необходимы раздельные устройства сопряжения .

Цель изобретения - создание схемы сопряжения для системы нескольких вычислительных устройств, чтобы при очень низких схемотехнических и конструктивных затратах была достигнута высокая производительность и одновременно обеспечивалась зкономичная, просто управляемая конструкция при высокой степени унифицирования.

В основу изобретения положена задача создания возможно простой по своей конструкции системы сопряжения для нескольких работающих одновременно и автономно над общей задачей активных вычислительных устройств.

из которых одно предусмотрено как главное, остальные - как подчиненные вычислетельные устройства с включенными в них программируемыми селекторными схемами ввода-вьшода, которая позволяла бы осуществлять асинхронные соединения отдельных вычислительных устройств посредством вызова прерьшания.

Поставленная цель достигается тем, что каждое вычислительное устройство через селекторную схему ввода-вывода подключено к общей собирающей линии

для информации данных и адресов, и что каждая селекторная схема ввода- вьшода через особую схему управления для передачи управляющих сигналов подключена к собирающей линии для асинхликтного обмена данными между главным вычислительным устройством и подчиненными вычислительными устройствами, и что предназначенная для главного вы25 числительного устройства селекторная схема ввода-вьшода имеет управляемый ею выход сигнала направления данных, который соединен с остальными селекторными схемами ввода-вывода для ус30 тановления направления передачи и приоритета главного вычислительного устройства.

Селекторная схема ввода-вывода управляющего вычислительного устройjg ства имеет устройство для определения приоритета при нескольких одновременно обращающихся подчиненных вычислительных устройствах.

40

45

50

55

Схема управления имеет конъюнктивное логическое звено для сигнала направления данных, посланного главным вычислительным устройством и принятого подчиненными вычислительными устройствами, и для сигнала готовности в вода-вьшода, выход которого подключен к второму конъюнктивному логическому звену с характеристикой выдержки времени. Второй вход конъюнктивного логического звена с характеристикой вьщержки времени соединен с вводом для сигнала готовности ввода-вывода, его выход через третий логический злемент подключен к выходу для сигнала направления данных для главного вычислительного устройства, его отрицание для подчиненных вычислительных устройств подключено к входам вызова ввода-вьшода остальных вычислительных устройств, и через четвертое логическое звено, которое своим другим входом соединено с вторым входом второго конъюнктивного логического звена и вводом для сигнала готовности ввода- вьгоода, второй вход конъюнктивного логического звена соединен с входом вызова ввода-вывода селекторной схе- мь ввода-вьшода, подчиненной подключенному вычислительному устройству.

Схема управления имеет вход активизации, через который происходят ее вызов вычислительным устройством через соответствующую селекторную схему ввода-вывода для обмена данными. Каждая селекторная схема ввода- вьшода имеет схему времени для определения времени ожидания, в течение которого посланное или принятое ею слово данных должно быть принято или послано участвующим в передаче данных вычислительным устройством, и программируемую, возбуждаемую вы- зьюаемым вычислительным устройством схему времени для сигнала ощибки в случае неприхода сигнала подтверждения в течение времени ожидания от вы зьшаемого вычислительного устройства

Подчиненные вычислительные устройства предназначены для управления различными шагами процесса или другими одинаковыми или отличающимися одна от другой задачами. Их функции управляются и координируются главным вычислительным устройством. Поиск передачи данных может осуществляться одним из подчиненных вычислительных устройств или главным вычислительньм устройством посредством адресной и управляющей линии, которые через селекторную схему ввода-вьшода подключены к собирающим линиям.

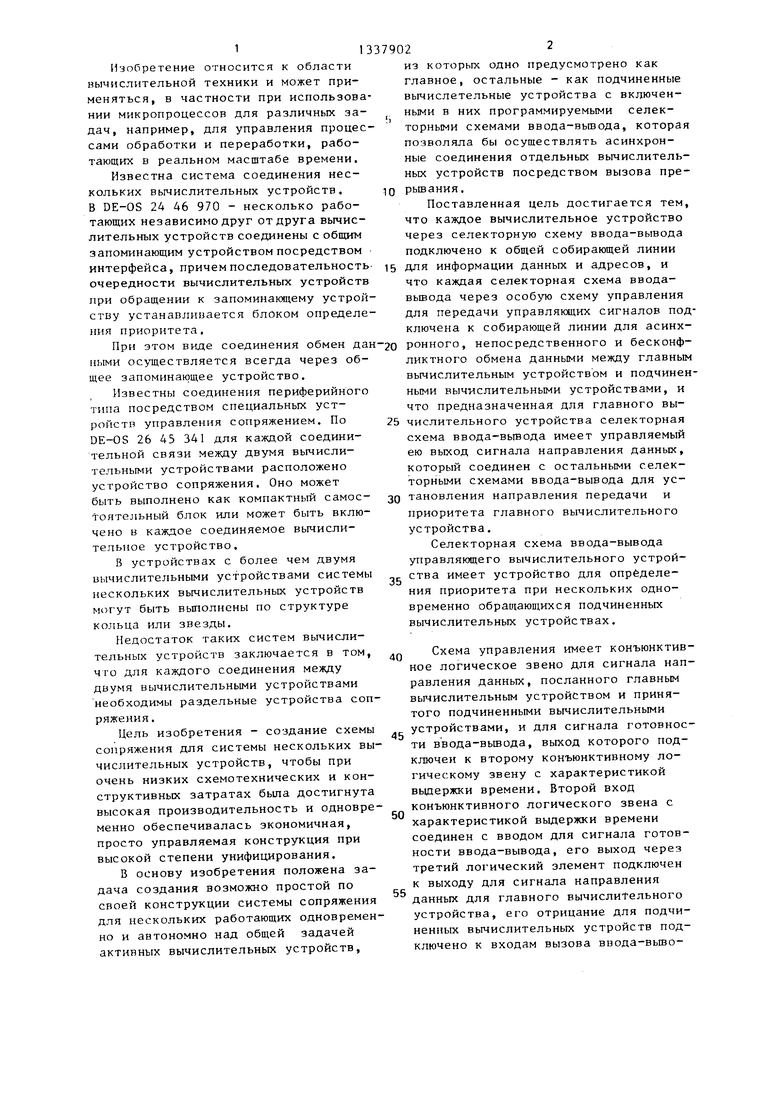

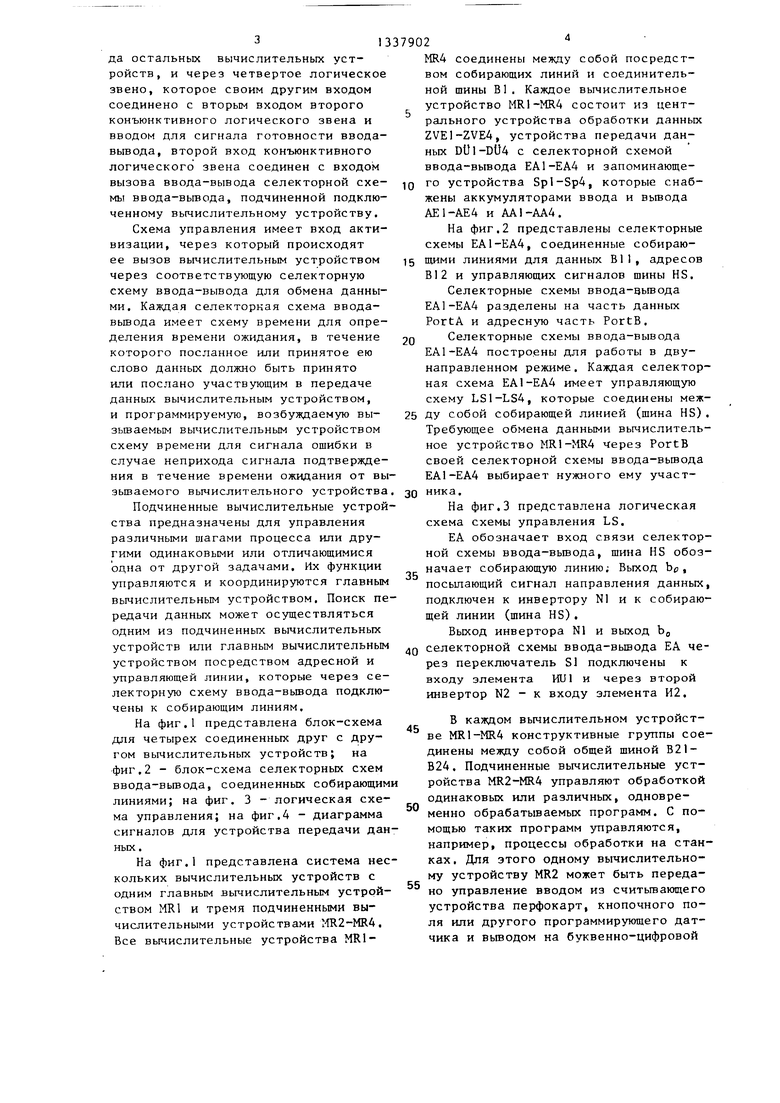

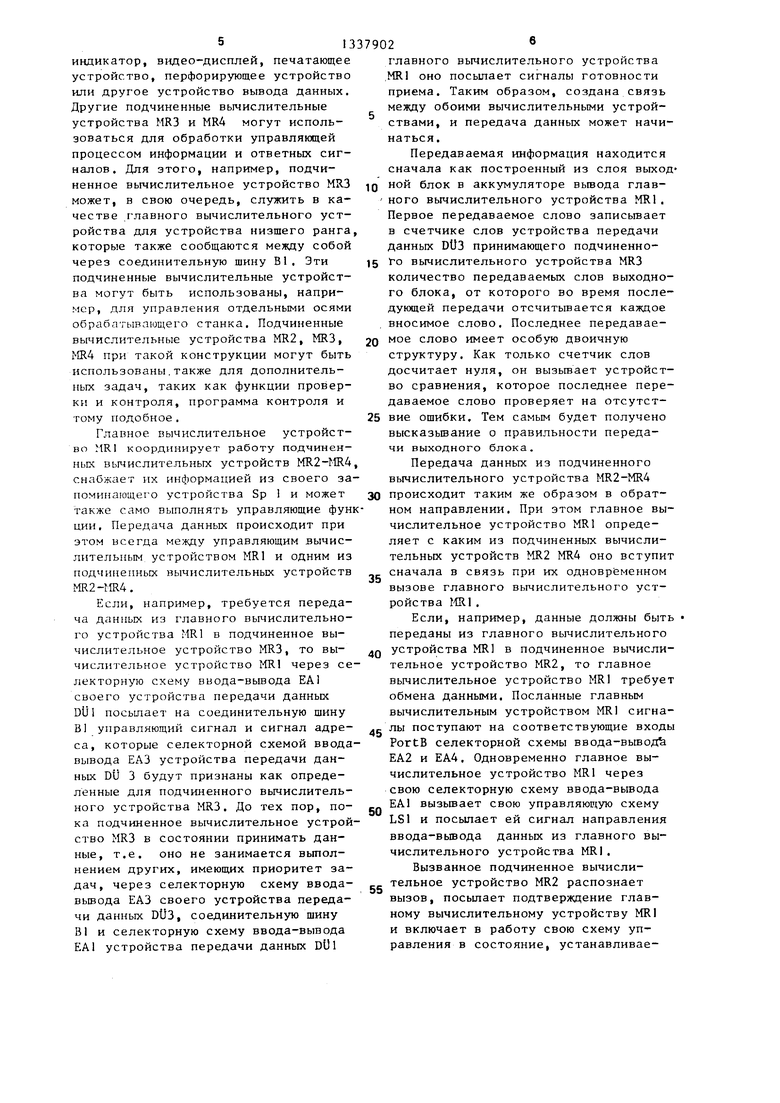

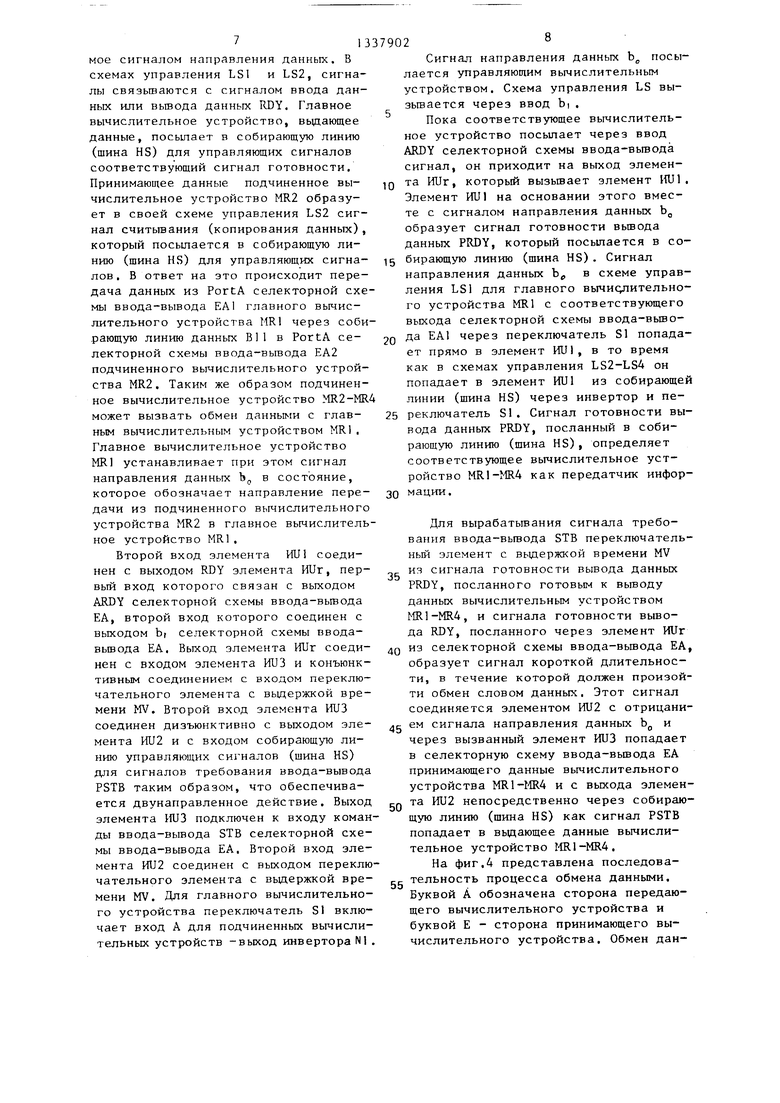

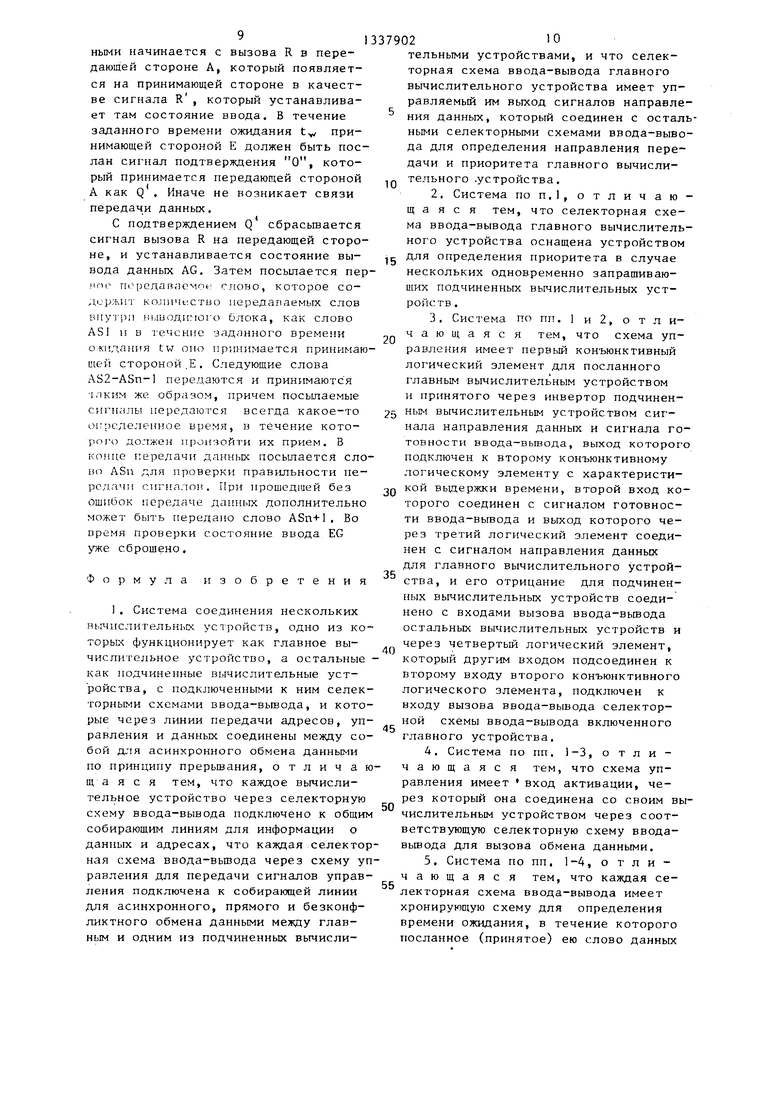

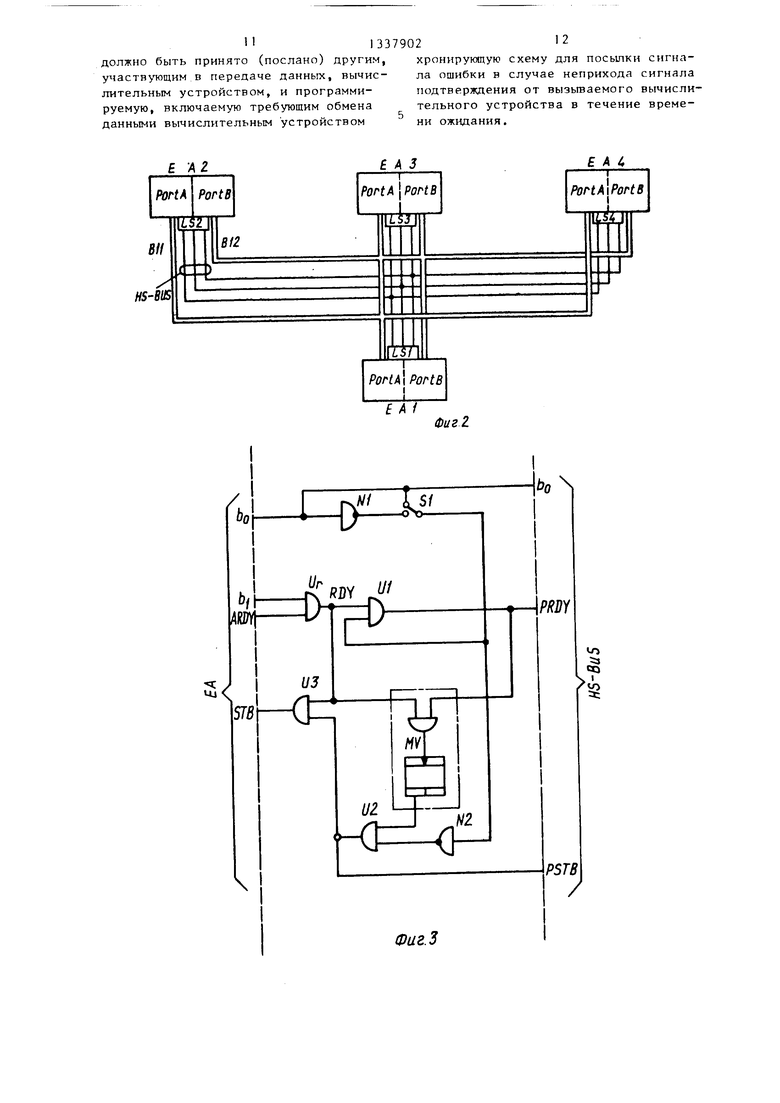

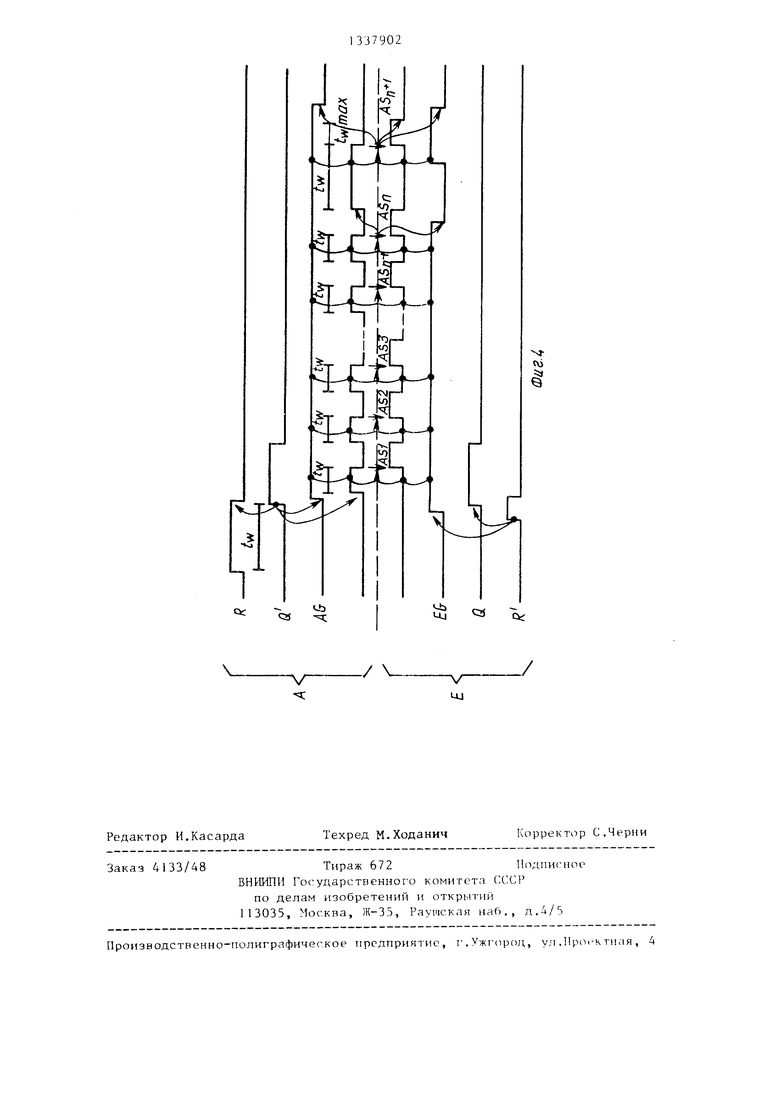

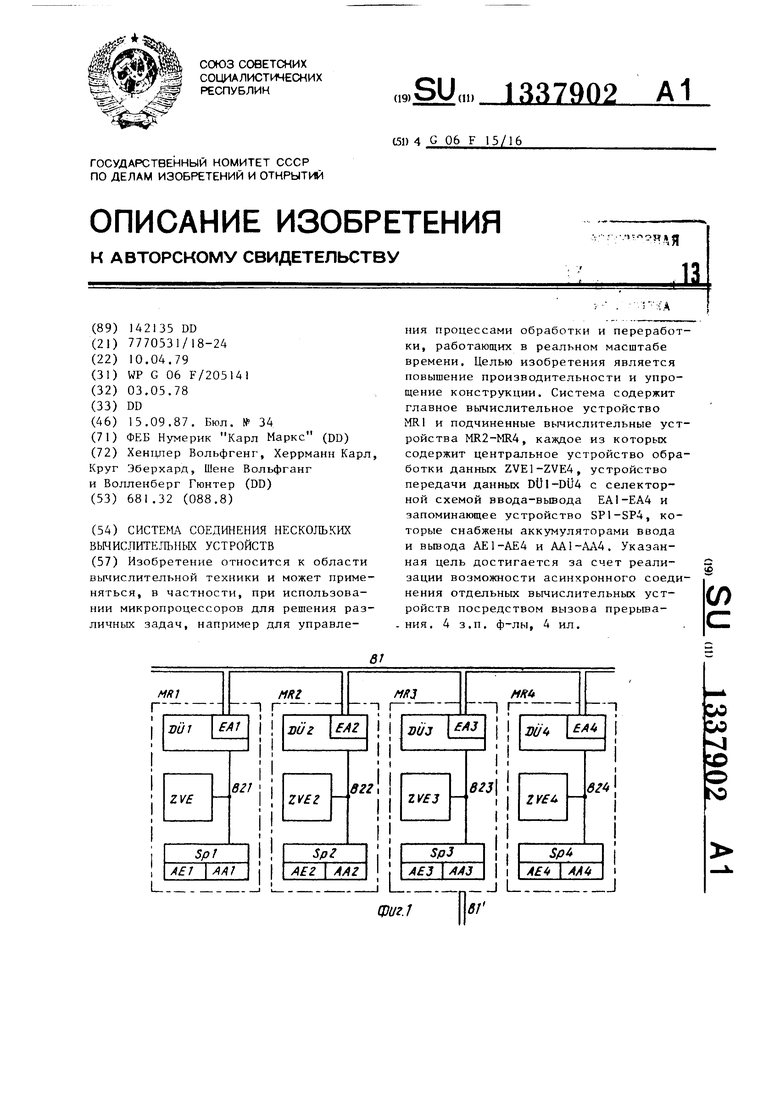

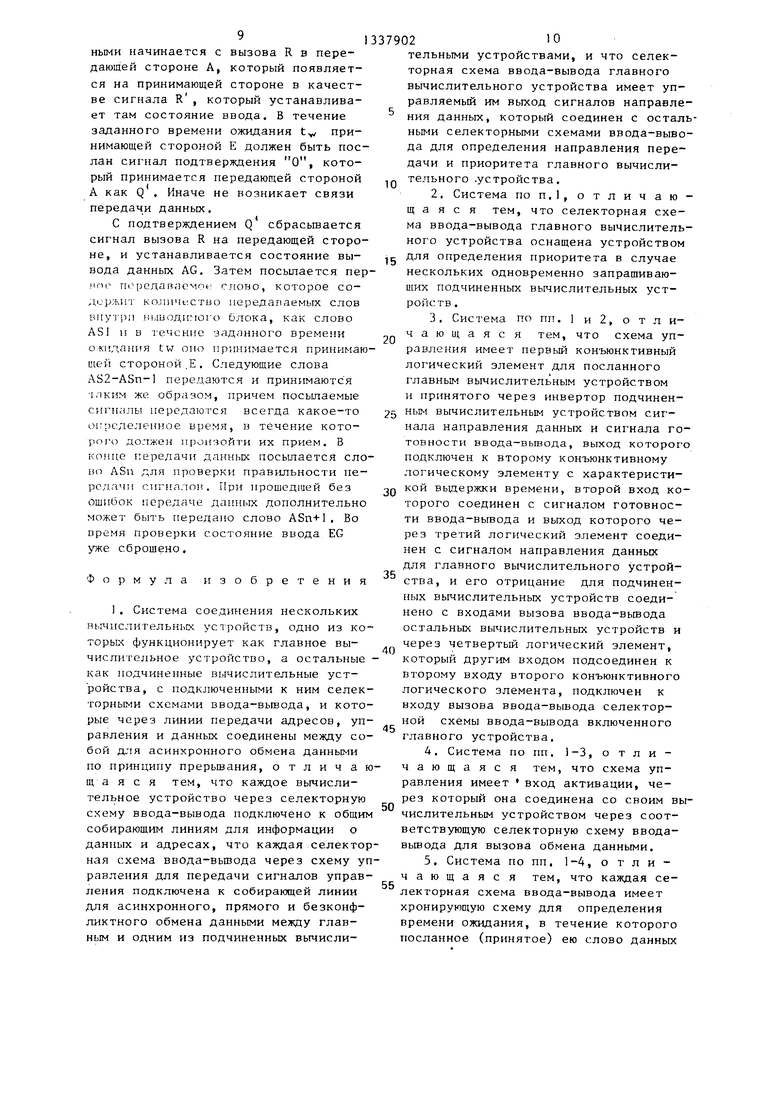

На фиг,1 представлена блок-схема для четырех соединенных друг с другом вычислительных устройств; на фиг.2 - блок-схема селекторньк схем ввода-вьгоода, соединенных собирающим линиями; на фиг. 3 - логическая схема управления; на фиг.4 - диаграмма сигналов для устройства передачи данных.

На фиг.1 представлена система нескольких вычислительных устройств с одним главным вычислительным устройством MR1 и тремя подчиненными вычислительными устройствами i-fRZ-MRA. Все вычислительные устройства MR1MR4 соединены между собой посредством собирающих линий и соединительной шины В1. Каждое вычислительное устройство MR1-MRA состоит из центрального устройства обработки данньк ZVE1-ZVE4, устройства передачи данных Dlll-DtJ4 с селекторной схемой ввода-вывода ЕА1-ЕА4 и запоминающего устройства Spl-Sp4, которые снабжены аккумуляторами ввода и вьшода АЕ1-АЕ4 и АА1-АА4.

На фиг.2 представлены селекторные схемы ЕА1-ЕА4, соединенные собирающими линиями для данных В11, адресов В12 и управляющих сигналов щины HS.

Селекторные схемы ввода-дьшода ЕА1-ЕА4 разделены на часть данных PortA и адресную часть PortB.

Селекторные схемы ввода-вывода ЕА1-ЕА4 построены для работы в двунаправленном режиме. Каждая селекторная схема ЕА1-ЕА4 имеет управляющую схему LS1-LS4, которые соединены межДУ собой собирающей линией (шина HS). Требующее обмена данными вычислительное устройство MR1-MR4 через PortB своей селекторной схемы ввода-вьшода ЕА1-ЕА4 выбирает нужного ему участника.

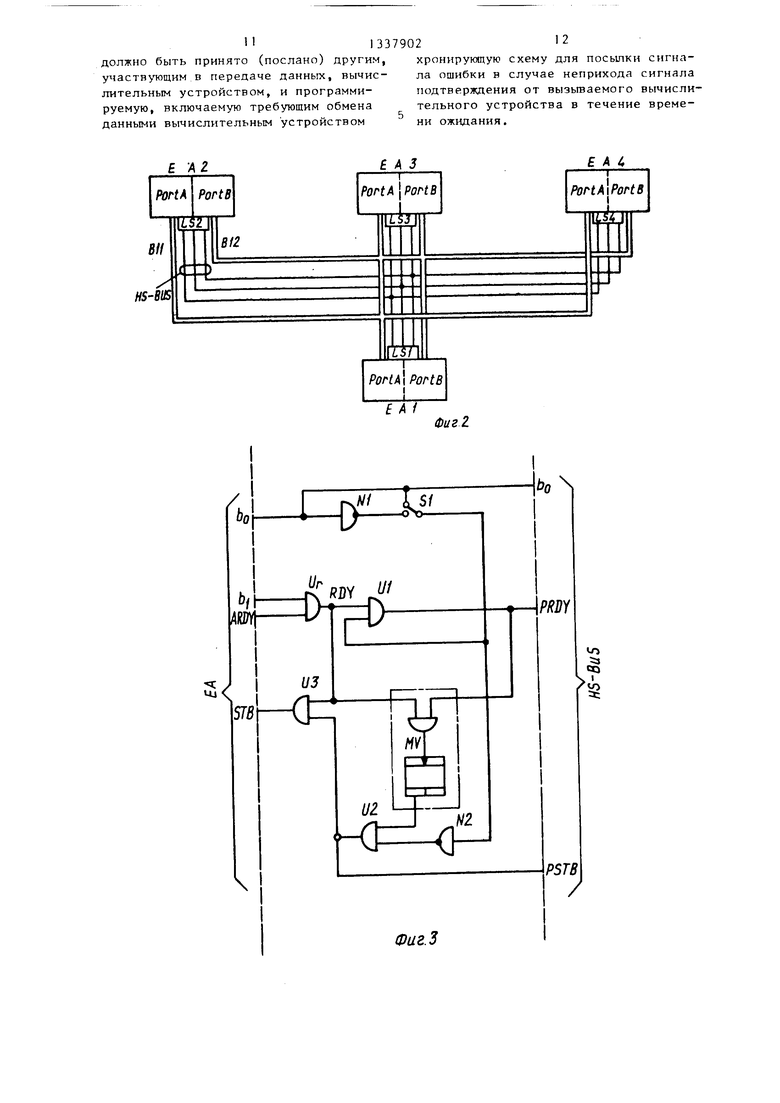

На фиг.З представлена логическая схема схемы управления LS.

ЕА обозначает вход связи селекторной схемы ввода-вьтода, щина HS обозначает собирающую ЛИНИЮ; Выход bo, посылающий сигнал направления данных, подключен к инвертору N1 и к собирающей линии (щина HS).

Выход инвертора N1 и выход bo

селекторной схемы ввода-вьшода ЕА через переключатель S1 подключены к входу элемента HUl и через второй инвертор N2 - к входу элемента И2.

В каждом вычислительном устройстве MR1-MR4 конструктивные группы соеинены между собой общей шиной В21- В24. Подчиненные вычислительные устройства MR2-MR4 управляют обработкой одинаковых или различных, одновременно обрабатываемых программ. С поощью таких программ управляются, например, процессы обработки на станках. Для этого одному вычислительному устройству MR2 может быть передано управление вводом из считьшающего устройства перфокарт, кнопочного поля или другого программирующего датчика и вьюодом на буквенно-цифровой

индикатор, видео-дисплей, печатающее устройство, перфорирующее устройство или другое устройство вывода данных. Другие подчиненные вычислительные устройства MR3 и MRA могут использоваться для обработки управляющей процессом информации и ответных сигналов. Для этого, например, подчиненное вычислительное устройство MR3 может, в свою очередь, служить в качестве главного вычислительного устройства для устройства низшего ранга которые также сообщаются между собой через соединительную шину В1. Эти подчиненные вычислительные устройства могут быть использованы, например, для управления отдельными осями обргабатывающего станка. Подчиненные вычислительные устройства MR2, MR3, MR4 при такой конструкции могут быть использованы.также для дополнительных задач, таких как функции проверки и контроля, программа контроля и тому подобное.

Главное вычислительное устройство MR1 координирует работу подчиненных вычислительных устройств MR2-MR4 снабжает их информацией из своего запоминающего устройства SP 1 и может также само выполнять управляющие фунции. Передача данных происходит при этом всегда между управляющим вычислительным устройством MR1 и одним из подчиненных вычислительных устройств MR2-MR4.

Если, например, требуется передача данных из главного вычислительного устройства MR1 в подчиненное вычислительное устройство MR3, то вычислительное устройство MR1 через селекторную схему ввода-вьшода ЕА1 своего устройства передачи данных DiJl посылает на соединительную шину В1 управляющий сигнал и сигнал адреса, которые селекторной схемой ввода вывода БАЗ устройства передачи данных DiJ 3 будут признаны как определенные для подчиненного вычислительного устройства MR3. До тех пор, пока подчиненное вычислительное устройство MR3 в состоянии принимать данные, т.е. оно не занимается вьтол- нением других, имеющих приоритет задач, через селекторную схему ввода- вывода ЕАЗ своего устройства передачи данных DtJ3, соединительную шину В1 и селекторную схему ввода-вывода ЕА1 устройства передачи данных DUl

5

0

главного вычислительного устройства MR1 оно посылает сигналы готовности приема. Таким образом, создана связь между обоими вычислительными устройствами, и передача данных может начинаться.

Передаваемая информация находится сначала как построенный из слоя выходной блок в аккумуляторе вьгоода глав- ного вычислительного устройства MR1. Первое передаваемое слово записьгоает в счетчике слов устройства передачи данных Dl)3 принимающего подчиненно- 5 го вычислительного устройства MR3

количество передаваемых слов выходного блока, от которого во время последующей передачи отсчитывается каящое вносимое слово. Последнее передаваемое слово имеет особую двоичную структуру. Как только счетчик слов досчитает нуля, он вызьшает устройство сравнения, которое последнее передаваемое слово проверяет на отсутствие ошибки. Тем самым будет получено высказьшание о правильности передачи выходного блока.

Передача данных из подчиненного вычислительного устройства MR2-MR4 происходит таким же образом в обратном направлении. При этом главное вычислительное устройство MR1 определяет с каким из подчиненных вычислительных устройств MR2 MR4 оно вступит сначала в связь при их одновременном вызове главного вычислительного устройства I d .

Если, например, данные должны быть переданы из главного вычислительного Q устройства MR в подчиненное вычислительное устройство MR2, то главное вычислительное устройство MR1 требует обмена данными. Посланные главным вычислительным устройством MR1 сигналы поступают на соответствующие входы PortB селекторной схемы ввода-вывод ЕА2 и ЕА4. Одновременно главное вычислительное устройство MR1 через свою селекторную схему ввода-вывода ЕА1 вызьшает свою управляющую схему LSI и посылает ей сигнал направления ввода-вьшода данньсх из главного вычислительного устройства MR1.

Вызванное подчиненное вычислительное устройство MR2 распознает вызов, посылает подтверждение главному вычислительному устройству Ж1 и включает в работу свою схему управления в состояние, устанавливае5

5

0

5

мое сигналом направления данных. В схемах управления LSI и LS2, сигналы связьшаются с сигналом ввода данных или вьшода данных RDY. Главное вычислительное устройство, вьдающее данные, посылает в собирающую линию (шина HS) для управляющих сигналов соответствующий сигнал готовности. Принимающее данные подчиненное вычислительное устройство MR2 образует в своей схеме управления LS2 сигнал считьшания (копирования данных), который посылается в собирающую линию (шина HS) для управляющих сигналов . В ответ иа это происходит передача данных из PortA селекторной схемы ввода-вывода ЕА1 главного вычислительного устройства MR1 через собирающую линию данных В11 в PortA селекторной схемы ввода-вывода ЕА2 подчиненного вычислительного устройства MR2. Таким же образом подчиненное вычислительное устройство MR2-MR может вызвать обмен данными с главным вычислительным устройством MR1, Главное вычислительное устройство MR1 устанавливает при этом сигнал направления данных Ъ в состояние, которое обозначает направление передачи из подчиненного вычислительного устройства MR2 в главное вычислительное устройство MR1.

Второй вход элемента HUl соединен с выходом RDY элемента Шг, первый вход которого связан с выходом ARDY селекторной схемы ввода-вьгоода ЕА, второй вход которого соединен с выходом Ьг селекторной схемы ввода- вьшода ЕА. Выход элемента Шг соединен с входом элемента ИиЗ и конъюнктивным соединением с входом переключательного элемента с выдержкой времени MV. Второй вход элемента ШЗ соединен дизъюнктивно с выходом элемента Ии2 и с входом собирающую линию управляющих сигналов (шина HS) для сигналов требования ввода-вывода PSTB таким образом, что обеспечивается двунаправленное действие. Выход элемента ШЗ подключен к входу команды ввода-вывода STB селекторной схемы ввода-вывода ЕА. Второй вход элемента Ии2 соединен с выходом переключательного элемента с выдержкой вре- тельность процесса обмена данными.

мени MV. Для главного вычислительного устройства переключатель SI включает вход А для подчиненных вычислительных устройств -выход инвертора N1 .

Буквой А обозначена сторона переда щего вычислительного устройства и буквой Е - сторона принимающего вы числительного устройства. Обмен да

Сигнал направления данных Ь посылается управляющим вычислительным устройством. Схема управления LS вы- зьшается через ввод b| .

Пока соответствующее вычислительное устройство посыпает через ввод ARDY селекторной схемы ввода-вьгаода сигнал, он приходит на выход элемента Шг, который вызьшает элемент Ш . Элемент Ш1 на основании этого вместе с сигналом направления данных Ь образует сигнал готовности вьшода данных PRDY, который посылается в собирающую линию (шина HS). Сигнал

направления данных Ъ в схеме управления LSI для главного вьмис;пительно- го устройства MR1 с соответствующего выхода селекторной схемы ввода-вьшода ЕА1 через переключатель S1 попадает прямо в элемент Ш1 , в то время как в схемах управления LS2-LS4 он попадает в элемент Ш1 из собирающей линии (шина HS) через инвертор и переключатель S1. Сигнал готовности вывода данных PRDY, посланный в собирающую линию (шина HS), определяет соответствующее вычислительное устройство MR1-MR4 как передатчик информации.

Для вырабатывания сигнала требования ввода-вьшода STB переключательный элемент с выдержкой времени MV из сигнала готовности вывода данных PRDY, посланного готовым к выводу данных вычислительным устройством MR1-MR4, и сигнала готовности вывода RDY, посланного через элемент Шг из селекторной схемы ввода-вьшода ЕА, образует сигнал короткой длительности, в течение которой должен произойти обмен словом данных. Этот сигнал соединяется элементом Ш2 с отрицани- ем сигнала направления данных Ь и через вызванный элемент ШЗ попадает в селекторную схему ввода-вьшода ЕА принимающего данные вычислительного устройства MRl-l-IRA и с выхода элемента Ш2 непосредственно через собирающую линию (шина HS) как сигнал PSTB попадает в вьщающее данные вычислительное устройство fiRl-MRA.

На фиг,4 представлена последова

Буквой А обозначена сторона передающего вычислительного устройства и буквой Е - сторона принимающего вычислительного устройства. Обмен данными начинается с вызова R в передающей стороне А, который появляется на принимающей стороне в качестве сигнала R , который устанавливает там состояние ввода, В течение заданного времени ожидания t принимающей стороной Е должен быть послан сигнал подтверждения О, который принимается передающей стороной А как Q , Иначе не возникает связи передачи данных.

С подтверждением Q сбрасьшается сигнал вызова R на передающей стороне, и устанавливается состояние вывода данных AG. Затем посылается пер- )1пе тгорсдавпемгк:: сково, которое содержит количество передапаемых слов внутри ныиодимого блока, как слово AS1 ив течение заданного времени окидания t:w оно принимается принимаю- ьчей стороной.Е. Следующие слова AS2-ASn-l пере.цаются и принимаютс я 1ЛКИМ же образом, причем посьшаемые сигналы передаются всегда какое-то определенное время, н течение кото- ро1ч) должен произойти их прием. В конце передачи данных посылается сло- цо ASn для проверки правильности передачи сигналоп. При прошедшей без Ошибок передаче данных дополнительно может быть передано слово ASn+1, Во время проверки состояние ввода EG утке сброшено.

Формула изобретения

1, Система соединения нескольких нычпслительньгх усаройств, одно из которых функционирует как главное вычислительное устройство, а остальные как подчиненньЕе В1,числительные устройства, с подключенными к ним селекторными схемами ввода-вьюода, и которые через линии передачи адресов, управления и данных соединены между собой для асинхронного обмена данными по принципу прерьшания, отличающаяся тем, что каждое вычислительное устройство через селекторную схему ввода-вывода подключено к общим собирающим линиям для информации о данных и адресах, что каждая селекторная схема ввода-вывода через схему управления для передачи сигналов управления подключена к собирающей линии для асинхронного, прямого и безконф- ликтного обмена данными мелоду главным и одним из подчиненных вычисли

0

тельными устройствами, и что селекторная схема ввода-вывода главного вычислительного устройства имеет управляемый им выход сигналов направления данных, который соединен с остальными селекторными схемами ввода-вывода для определения направления передачи и приоритета главного вычислительного .устройства,

2.Система поп,1,отличаю- щ а я с я тем, что селекторная схема ввода-вывода главного вычислительного устройства оснащена устройством

для определения приоритета в случае нескольких одновременно запрашивающих подчиненных вычислительных устройств ,

3.Система по пп, 1 и 2, о т л и- чающаяся тем, что схема управления имеет первый конъюнктивный логический элемент для посланного главным вычислительным устройством

и принятого через инвертор подчинен- 5 ным вычислительным устройством сигнала направления данных и сигнала готовности ввода-вьшода, выход которого подключен к второму конъюнктивному логическому элементу с характеристи- Q кой вьщержки времени, второй вход которого соединен с сигналом готовности ввода-вывода и выход которого через третий логический элемент соединен с сигналом направления данных для главного вычислительного устройства, и его отрицание для подчиненных вычислительных устройств соединено с входами вызова ввода-вьгоода остальных вычислительных устройств и через четвертый логический элемент, который другим входом подсоединен к второму входу второго конъюнктивного логического элемента, подключен к входу вызова ввода-вывода селекторной схемы ввода-вывода включенного главного устройства.

4.Система по пп. 1-3, о т л и - чающаяс я тем, что схема управления имеет вход активации, через который она соединена со своим вычислительным устройством через соответствующую селекторную схему ввода- вьюода для вызова обмена данными,

5.Система по пп. 1-4, о т л и - чающаяся тем, что каждая селекторная схема ввода-вывода имеет хронирующую схему для определения времени ожидания, в течение которого посланное (принятое) ею слово данных

5

0

5

0

5

11

должно быть принято (послано) другим, участвующим в передаче данных, вычислительным устройством, и программируемую, включаемую требующим обмена данными вычислительным устройством

i -М

1337902

12

хронирующую схему для посьтки сигнала ошибки в случае неприхода сигнала подтверждения от вызьгааемого вычислительного устройства в течение времени ожидания.

45

А 4

/

Фиг 2

r

Редактор И.Касарда Заказ 4133/48

Техред М.Ходанич

Корректор

Тираж 672Подписное

ВНИИПИ Государственного комитета (Х СР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.Д/5

Производственно-полиграфическое предприятие, f.Ужгород, ул .Проектная, 4

-/ V

л/

uj

У

Корректор С.Черни

| название | год | авторы | номер документа |

|---|---|---|---|

| КАТАЛИЗАТОР И СПОСОБ ПОЛУЧЕНИЯ РАЗВЕТВЛЕННЫХ НЕНАСЫЩЕННЫХ АЛЬДЕГИДОВ | 2012 |

|

RU2545069C2 |

| СПОСОБ ПОМОЩИ ПРИ ВОЖДЕНИИ И УСТРОЙСТВО ПОМОЩИ ПРИ ВОЖДЕНИИ | 2017 |

|

RU2743519C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ УМЕНЬШЕНИЯ ВРЕМЕНИ ОЖИДАНИЯ НА ИНТЕРФЕЙСЕ ПОСРЕДСТВОМ НАЛОЖЕНИЯ ПЕРЕДАВАЕМЫХ ПАКЕТОВ | 1996 |

|

RU2189698C2 |

| ЭЛЕКТРОМАГНИТНЫЙ ДВИГАТЕЛЬ | 2006 |

|

RU2381612C2 |

| Система для селективного обмена информацией между абонентами | 1974 |

|

SU668629A3 |

| Устройство для сопряжения устройств ввода-вывода с цвм | 1974 |

|

SU736083A1 |

| Устройство для регулирования мощности электрофильтра | 1972 |

|

SU602136A3 |

| УПРАВЛЯЮЩЕЕ УСТРОЙСТВО ОБЕСПЕЧЕНИЯ ПАРАЛЛЕЛЬНОЙ РАБОТЫ ДЛЯ ИНВЕРТОРНОГО ГЕНЕРАТОРА | 2012 |

|

RU2518905C2 |

| СПОСОБ СЖИЖЕНИЯ ПРИРОДНОГО ГАЗА ОХЛАЖДАЮЩИМИ СМЕСЯМИ, СОДЕРЖАЩИМИ ПО МЕНЬШЕЙ МЕРЕ ОДИН НЕНАСЫЩЕННЫЙ УГЛЕВОДОРОД | 2011 |

|

RU2556731C2 |

| РАСПРЕДЕЛЕННАЯ СИСТЕМА ИМИТАЦИОННОГО МОДЕЛИРОВАНИЯ БУРЕНИЯ | 2010 |

|

RU2503065C1 |

Изобретение относится к области вычислительной техники и может применяться, в частности, при использовании микропроцессоров для решения различных задач, например для управлеV . ния процессами обработки и переработки, работающих в реальном масштабе времени. Целью изобретения является повышение производительности и упрощение конструкции. Система содержит главное вычислительное устройство MR1 и подчиненные вычислительные устройства MR2-MR4, каждое из которых содержит центральное устройство обработки данных ZVE1-ZVE4, устройство передачи данных Dl)l-DU4 с селекторной схемой ввода-вьшода ЕА1-ЕА4 и запоминающее устройство SP1-SP4, которые снабжены аккумуляторами ввода и вьшода АЕ1-АЕ4 и AAI-AA4. Указанная цель достигается за счет реализации возможности асинхронного соединения отдельных вычислительных устройств посредством вызова прерьша- ния. 4 з.п. ф-лы, 4 ил. х (Л 00 00 Фиг л вГ

Авторы

Даты

1987-09-15—Публикация

1979-04-10—Подача