ПРЕДПОСЫЛКИ СОЗДАНИЯ НАСТОЯЩЕГО ИЗОБРЕТЕНИЯ

Область техники, к которой относится настоящее изобретение

Изобретение относится к способу и устройству для уменьшение общего числа периодов тактовых импульсов для передачи данных по каналу связи между кристаллами интегральных схем.

Описание известного уровня техники

Для передачи данных управления или синхронизации между кристаллами интегральных схем, например, на объединительной плате, во многих случаях применениях используют относительно небольшие каналы связи между кристаллами интегральных схем (например, четырехразрядные управляющие шины). Например, комплект кристаллов интегральных схем для использования с микропроцессором может быть более удобно изготовлен как два кристалла интегральных схем, причем первый кристалл принимает сигналы адресации и управления из шины процессора, в то время как другой кристалл принимает сигналы данных из шины процессора. Первый кристалл интегральной схемы управляет передачей данных второму кристаллу интегральной схемы по каналу связи между кристаллами интегральных схем.

Обычный протокол передачи сигнала управления, как правило, используют совместно с такими каналами связи между кристаллами интегральных схем для обеспечения передачи сигналов управления из передающего кристалла интегральной схемы одному или более принимающим кристаллам интегральных схем. В соответствии с обычным протоколом, команды, посылаемые по каналу связи между кристаллами интегральных схем, передают в форме пакета, где каждый командный пакет содержит одно или более командных слов, которым предшествуют слово преамбулы и кодовое слово типа пакета. Передачу управляющих сигналов синхронизируют посредством синхросигнала. Если по каналу связи между кристаллами интегральных схем команд не передается, то, как правило, по шине передается слово паузной комбинации до тех пор, пока не будет послан новый командный пакет.

Всякий раз, когда командные сигналы должны быть переданы по каналу связи между кристаллами интегральных схем из передающего кристалла интегральной схемы принимающему кристаллу интегральной схемы, передающий кристалл интегральной схемы сначала должен выдать командное слово начала пакета. Затем для указания на то, что данные в шине представляют начало действительного пакета команд, формируется синхросигнал. Синхросигнал, как правило, посылается в том же периоде тактовых импульсов, что и слово начала пакета. Преамбула иногда посылается в периоде тактовых импульсов перед словом начала пакета. Таким образом, принимающий кристалл интегральной схемы должен сначала сохранить преамбулу перед откликом на команду. Как можно видеть, в начале каждого пакета для посылки преамбулы перед посылкой остального командного пакета требуется один дополнительный период тактовых импульсов.

КРАТКОЕ ИЗЛОЖЕНИЕ СУЩНОСТИ НАСТОЯЩЕГО ИЗОБРЕТЕНИЯ

Изобретатель настоящего изобретения понял, что время ожидания связи может быть уменьшено посредством наложения командных пакетов, которые посланы по интерфейсу. В одном аспекте, предпочтительный вариант осуществления настоящего изобретения представляет собой способ уменьшения числа периодов тактовых импульсов, требуемых для передачи информационных пакетов по каналу связи между кристаллами интегральных схем. Канал связи между кристаллами интегральных схем соединен между передающим кристаллом интегральной схемы и принимающим кристаллом интегральной схемы. Способ предусматривает вывод первого информационного слова по каналу связи между кристаллами интегральных схем в первом временном интервале; запись первого информационного слова в передающем кристалле интегральной схемы в этом первом временном интервале так, чтобы первое информационное слово было доступно в течение второго последующего временного интервала; прием первого информационного слова принимающим кристаллом интегральной схемы в первом временном интервале; запись первого информационного слова в принимающем кристалле интегральной схемы в первом временном интервале так, чтобы первое информационное слово было доступно в течение второго последующего временного интервала; формирование второго информационного слова в передающем кристалле интегральной схемы во втором временном интервале; сравнение записанного первого информационного слова со вторым информационным словом в передающем кристалле интегральной схемы в течение второго временного интервала; и если записанное первое информационное слово аналогично второму информационному слову, вывод третьего информационного слова по каналу связи между кристаллами интегральных схем вместо второго информационного слова в течение второго временного интервала. Третье информационное слово передается в третьем временном интервале незамедлительно следующем за вторым временным интервалом, если записанное первое информационное слово не аналогично второму информационному слову.

В предпочтительном варианте осуществления первое информационное слово определяется так, чтобы увеличить вероятность того, что первое информационное слово будет аналогично второму информационному слову.

В другом предпочтительном варианте осуществления первое информационное слово содержит командное слово или слово паузной комбинации, второе информационное слово содержит преамбулу к транзакции командного пакета, а третье информационное слово содержит код типа пакета.

В еще одном предпочтительном варианте осуществления каждый временной интервал имеет длительность одного тактового интервала.

В другом варианте осуществления каждый временной интервал имеет длительность множества тактовых интервалов.

В дополнительном аспекте предпочтительный вариант осуществления настоящего изобретения содержит устройство для экономии периодов тактовых импульсов в течение транзакций информационного пакета в канале связи между кристаллами интегральных схем. Устройство содержит селекторную схему, имеющую выход и первый и второй входы. Выход имеет связь с каналом связи между кристаллами интегральных схем, а селекторная схема выбирает один из (первый или второй) входов в качестве выхода в ответ на селекторный сигнал. Устройство дополнительно содержит память для временного хранения данных, имеющее связь с выходом селекторной схемы, которое хранит выход первого информационного слова в канал связи между кристаллами интегральных схем в течение первого временного интервала; и компаратор, имеющий первый вход, имеющий связь с первым входом селекторной схемы, и второй вход, имеющий связь с памятью для временного хранения данных. Компаратор сравнивает первое информационное слово, хранимое в памяти для временного хранения данных, со вторым информационным словом на первом входе селекторной схемы в течение второго временного интервала. Компаратор дополнительно заставляет третье информационное слово на втором входе селекторной схемы выводиться вместо второго информационного слова посредством селекторной схемы в течение второго временного интервала, если первое и второе информационные слова содержат по существу одинаковую информацию.

В предпочтительном варианте осуществления селекторная схема содержит мультиплексор, а память для временного хранения информации содержит регистр.

В дополнительном варианте осуществления компаратор заставляет третье информационное слово на втором входе селекторной схемы выводиться посредством селекторной схемы, если первое и второе информационные слова имеют идентичный набор двоичных разрядов.

В другом предпочтительном варианте осуществления каждый временной интервал имеет длительность одного тактового интервала или, в альтернативном варианте, каждый временной интервал имеет длительность множества тактовых интервалов.

В еще одном аспекте предпочтительным вариантом осуществления настоящего изобретения является устройство для уменьшения числа периодов тактовых импульсов, требуемых для завершения транзакции данных по каналу связи между кристаллами интегральных схем. Устройство содержит средство для выбора выхода из первого и второго входов. Этот выход имеет связь с каналом связи между кристаллами интегральных схем. Устройство дополнительно содержит средство для хранения первого информационного слова в течение первого временного интервала. Средство для хранения имеет связь с выходом средства для выбора. Наконец, устройство содержит средство для сравнения первого информационного слова, хранимого в средстве для хранения, со вторым информационным словом на первом входе средства для выбора в течение второго временного интервала. Средство для сравнения заставляет третье информационное слово на втором входе средства для выбора выводиться вместо второго информационного слова с помощью средства для выбора в течение второго временного интервала, если первое и второе информационные слова содержат по существу одинаковую информацию.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

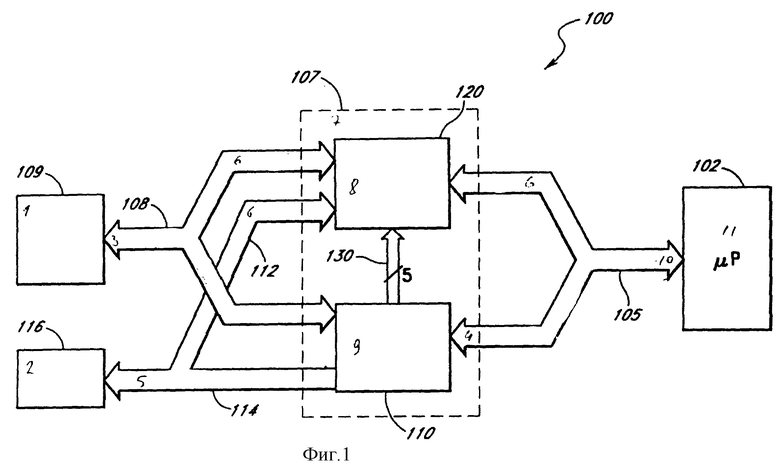

Фиг. 1 - упрощенная блок-схема вычислительной системы, содержащей кристаллы интегральных схем, соединенные посредством канала связи между кристаллами интегральных схем.

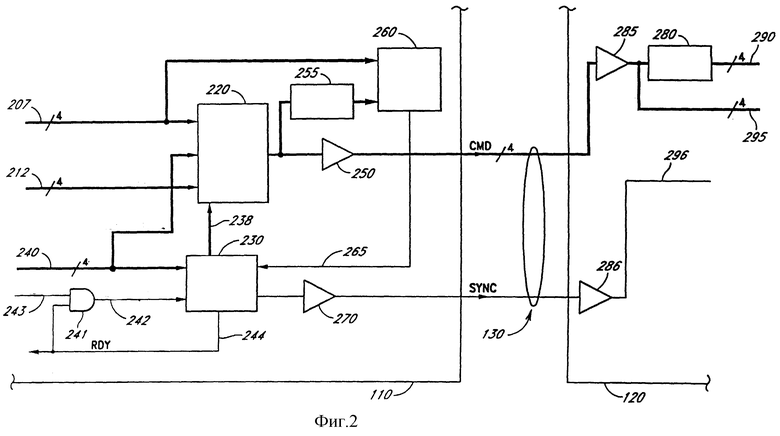

Фиг.2 - упрощенная блок-схема части интегральной схемотехники передающего кристалла интегральной схемы, показанного на фиг.1, на которой иллюстрируется механизм, соответствующий настоящему изобретению, экономии периодов тактовых импульсов вдоль канала связи между кристаллами интегральных схем.

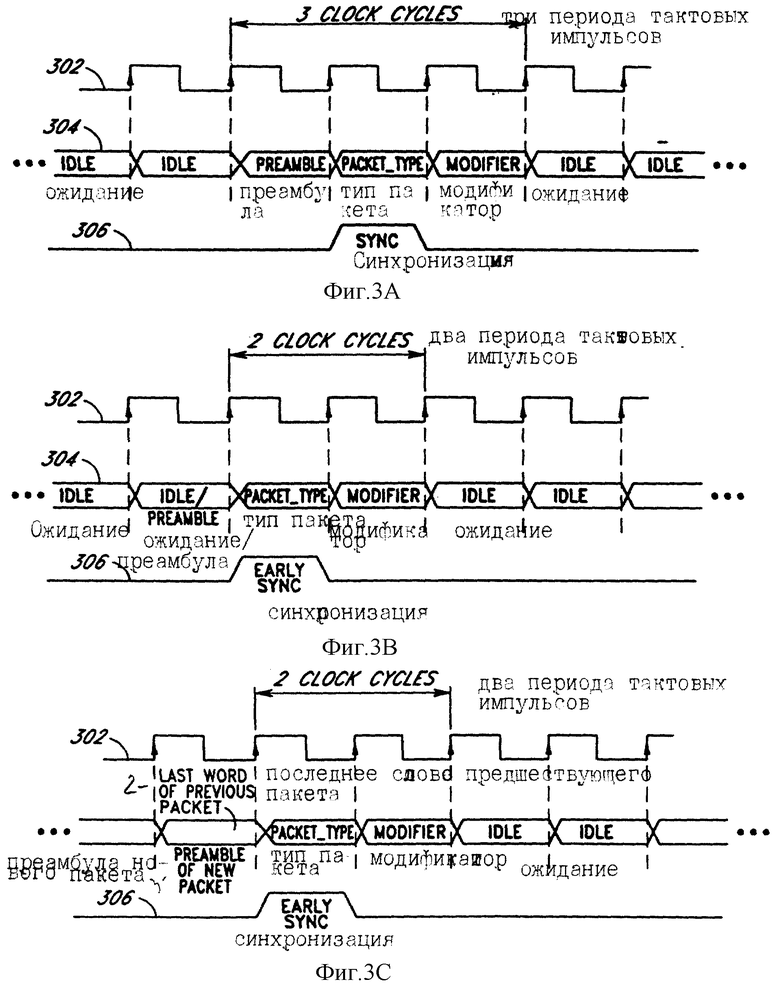

Фиг. 3А-3С - диаграммы синхронизации, на которых показано эффективные времена прохождения командных пакетов, посланных по каналу связи между кристаллами интегральных схем, а также иллюстрируются преимущества настоящего изобретения.

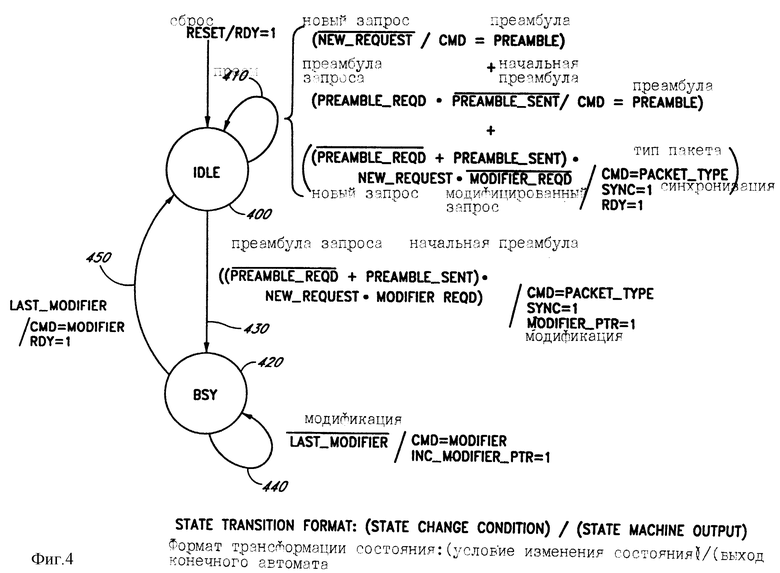

Фиг. 4 - диаграмма состояний, на которой показана работа конечного автомата, показанного на фиг. 2, в отношении формирования ранней преамбулы в соответствии с настоящим изобретением.

ПОДРОБНОЕ ОПИСАНИЕ НАСТОЯЩЕГО ИЗОБРЕТЕНИЯ

На фиг. 1 иллюстрируется упрощенная принципиальная блок-схема вычислительной системы 100, выбранной в качестве примера, в которой может быть использовано настоящее изобретение. Вычислительная система 100 содержит микропроцессор 102, который имеет связь с комплектом 107 кристаллов интегральных схем через шину 105 микропроцессора. Комплект 107 кристаллов интегральных схем имеет связь с главным и вспомогательными устройствами 109 программируемого интерфейса связи через шину 108 программируемых интерфейсов связи. Кроме того, комплект 107 кристаллов интегральных схем имеет связь с запоминающим устройством (например, динамическим запоминающим устройством с произвольной выборкой) через части 112, 114 передачи данных, адресации и управляющих сигналов шины памяти, так что комплект 107 кристаллов интегральных схем в этой вычислительной системе 100 действует как устройство сопряжения шина микропроцессора-шина памяти. Безусловно, квалифицированному специалисту в этой области техники будет очевидно, что вычислительная система 100, иллюстрируемая на фиг.1, с целью ясности пояснения настоящего изобретения очень упрощена.

Показанный комплект 107 кристаллов интегральных схем содержит два кристалла интегральных схем 110, 120, соединенных каналом 130 связи между кристаллами интегральных схем на объединительной плате в вычислительной системе 100. В одном варианте осуществления канал 130 связи между кристаллами интегральных схем содержит пятиразрядную управляющую шину, которую используют для передачи командных сигналов из передающего кристалла 110 интегральной схемы принимающему кристаллу 120 интегральной схемы. В одном варианте осуществления пятиразрядная управляющая шина фактически содержит пять линий, где четыре линии зарезервированы для передачи командных слов, а пятая линия - для передачи синхросигнала. Обычному квалифицированному в этой области техники специалисту будет очевидно, что если для одного варианта осуществления настоящего изобретения удобна четырехразрядная шина, то для других специальных случаев применения могут быть использованы шины с большим или меньшим числом разрядов. В этом варианте осуществления комплект 107 кристаллов интегральных схем состоит из двух кристаллов интегральных схем, поскольку число штырьковых выводов для соединения комплекта 107 кристаллов интегральных схем с шиной 108 программируемого интерфейса связи и с шиной 105 микропроцессора при исполнении комплекта 107 в виде одной интегральной схемы сделают эту интегральную схему слишком дорогой. Кристалл 120 интегральной схемы комплекта 107 кристаллов интегральных схем принимает линии передачи данных из шины 105 микропроцессора, в то время как кристалл 110 интегральной схемы комплекта 107 кристаллов интегральных схем принимает линии адресации и передачи сигналов управления из шины 105 микропроцессора. Также, как и в случае шины 105 микропроцессора, сигналы данных на шине 108 программируемого интерфейса связи передаются кристаллу 120 интегральной схемы и из него в комплекте 107 кристаллов интегральных схем, в то время как сигналы адресации и командные сигналы передаются кристаллу 110 интегральной схемы и из него. Аналогичным образом, между запоминающим устройством 116 и кристаллом 110 интегральной схемы по шине 114 имеет место обмен информационными данными, в то время как обмен информационными данными между запоминающим устройством 116 и кристаллом 120 интегральной схемы обеспечивается по шине 112.

Во время работы микропроцессор 102 передает сигналы данных адресации и команд другим системам на объединительной плате и из других систем на объединительной плате микропроцессору 102. Комплект 107 кристаллов интегральных схем действует как устройство сопряжения микропроцессор-память так, чтобы данные, адрес и команды, передаваемые из микропроцессора 102, были способны иметь эффективную связь с запоминающим устройством 116 и главным и вспомогательными устройствами 109 программируемого интерфейса связи по частям 112, 114 шины памяти и по шине 108 программируемого интерфейса связи, соответственно. Аналогичным образом, комплект 107 кристаллов интегральных схем действует как интерфейс для сигналов, передаваемых из главного и вспомогательных устройств 109 программируемого интерфейса связи микропроцессору 102 и запоминающему устройству 116 по шине 105 микропроцессора и шинам 112, 114 памяти. Командные сигналы передаются из кристалла 110 интегральной схемы кристаллу 120 интегральной схемы. Кристалл 110 интегральной схемы принимает сигналы адреса и команд из шины 105 микропроцессора и из шины 108 программируемого интерфейса связи, в то время как кристалл 120 интегральной схемы принимает сигналы данных из шины 105 микропроцессора, из части 112, соответствующей передаче данных, шины памяти и из шины 108 программируемого интерфейса связи.

На фиг.2 показана упрощенная блок-схема частей интегральной схемотехники кристаллов 110 и 120 интегральных схем, которые иллюстрируют схемотехнику, используемую в одном предпочтительном варианте осуществления настоящего изобретения для экономии периодов тактовых импульсов в процессе передач данных по каналу 130 связи между кристаллами интегральных схем. Как показано на фиг. 2, мультиплексор 220 выбирает данные пакета, посылаемые по каналу 130 связи между кристаллами интегральных схем.

Вход 207 PREAMBLE, вход 240 PACKET_TYPE и вход 212 MODIFIER этого пакета являются отдельными входами в мультиплексор 220. Мультиплексор 220 выбирает каждый вход 207, 240 и 212 в соответствии с возникающей необходимостью для образования каждого командного пакета, посылаемого по каналу 130 связи между кристаллами интегральных схем. Выход из мультиплексора 220 находится под контролем конечного автомата 230 через селекторную шину 238.

Конечный автомат 230 принимает данные на вход PARKET_TYPE по шине 240 и принимает данные на вход NEW_REQUEST по линии 242, при этом конечный автомат выполнен с возможностью определения на входе PARKET_TYPE вида данных, которые должны быть переданы по каналу 130 связи между кристаллами интегральных схем, и с возможностью приема данных преамбулы на вход PREAMBLE для следующего командного пакета. Линия 242 входа NEW_REQUEST соединяется с выходом логического элемента 241 И. Логический элемент 241 И принимает данные на первый вход по линии 243. Шина 240 и линия 243 имеют связь с внутренней схемотехникой кристалла 110 интегральной схемы. Конечный автомат 230 также обеспечивает выходы сигнала готовности следующего пакета, RDY, по линии 244 к схемотехнике в кристалле 110 интегральной схемы, причем этот сигнал готовности показывает, что конечный автомат 230 готов принимать и обрабатывать следующий командный пакет из схемотехники в кристалле 110 интегральной схемы. Линия 244 служит вторым входом в логический элемент 241 И.

Выход мультиплексора 220 имеет связь с каналом 130 связи между кристаллами интегральных схем через драйвер 250. Кроме того, выход мультиплексора 220 имеет связь с регистром 255. Выход регистра 255 служит в качестве первого входа в компаратор 260. Кроме того, вход 207 PREAMBLE является вторым входом компаратора 260. Выход компаратора 260 связан с входом PREAMBLE_ SENT конечного автомата 230 по линии 265. Конечный автомат 230 дополнительно обеспечивает синхронизирующий выход, SYNC, через драйвер 270.

Принимающий кристалл 120 интегральной схемы показан на фиг.2 для включения принимающего регистра 280, который удерживает (то есть задерживает) предшествующие данные тактирования из канала 130 связи между кристаллами интегральных схем. Задержанные данные на шине 290 и буферизованные данные связи между кристаллами интегральных схем на шине 295 и на линии 296, имеют связь с внутренней схемотехникой кристалла 120 интегральной схемы, так что эти данные служат в качестве управляющих входов в схемотехнику в принимающем кристалле 120 интегральной схемы.

В процессе работы, как только конечный автомат 230 выдает сигнал 244 RDY, показывающий, что конечный автомат 230 способен обрабатывать следующий пакет, а схемотехника в кристалле 110 интегральной схемы выдает сигнал NEW_ TASC по линии 243, по линии 342 выдает сигнал NEW_REQUEST, показывающий, что входы PREAMBLE, PACKET_TYPE и MODIFIER для следующего командного пакета доступны для выхода по каналу 130 связи между кристаллами интегральных схем.

Мультиплексор 220 выбирает один из входов PREAMBLE, PACKET_TYPE или MODIFIER под контролем конечного автомата 230 через селекторную шину 238. Данные PREAMBLE могут содержать, например, индекс буфера, в который данные должны быть переданы в кристалле 120 интегральной схемы. С другой стороны, вход MODIFIER содержит управляющие данные, которые должны быть переданы в буферы в принимающем кристалле 120 интегральной схемы. Вход PACKET_TYPE содержит информацию, относящуюся к посылаемой команде. В одном варианте осуществления, вход PACKET_ TYPE идентифицирует тип команды (то есть считывание программируемого интерфейса связи, запись запоминающего устройства и так далее). В дополнительном варианте осуществления, вход PACKET_TYPE определяет длину пакета (то есть содержит ли он PREAMBLE и число MODIFIER, как ожидается). В одном предпочтительном варианте осуществления самые общие операции соответствуют самым коротким пакетам, а в еще одном предпочтительном варианте осуществления время приема входа PACKET_TYPE является показателем для принимающего кристалла 120 интегральной схемы, что он должен начать или закончить процесс.

Данные с выхода мультиплексора 220 подаются на управляющую шину 130 через драйвер 250. Данные, имеющиеся в канале 130 связи между кристаллами интегральных схем последовательно записываются в регистре 280 при наличии следующего периода тактовых импульсов. Кроме того, выходные данные записываются в регистре 255 для одной длительности периода тактовых импульсов. В тот период времени, который требуется для записи данных с выхода мультиплексора в регистре 255, мультиплексор 220 выдает другой выходной сигнал по каналу 130 связи между кристаллами интегральных схем через драйвер 250.

В том же периоде тактовых импульсов, в котором регистр 280 тактирует данные на канале 130 связи между кристаллами интегральных схем, данные с выхода регистра 255 сравниваются с данными на входе 207 PREAMBLE. To есть вход PREAMBLE является первым входом компаратора 260, выход регистра 255, на котором осуществляется задержка в один период тактовых импульсов, связан со вторым входом компаратора 260, при этом данные, поступающие на вход PREAMBLE и выходные данные командного слова пакета предшествующего периода тактовых импульсов в управляющей шине 130 сравниваются в компараторе 260. Если данные, поступающие на вход PREAMBLE одинаковы с данными, хранимыми в регистре 255, то компаратор 260 формирует сигнал PREAMBLE_SENT, который поступает на управляющий вход конечного автомата 230 по линии 265.

Если конечный автомат 230 принимает сигнал NEW_REQUEST, 242, и выходной сигнал компаратора (то есть PREAMBLE_SENT) по линии 265, означающий, что командное слово канала связи между кристаллами предшествующего периода тактовых импульсов и сигнал PREAMBLE нового пакета, предназначенного для выхода в канал 130 связи между кристаллами интегральных схем, являются одинаковыми, то из конечного автомата 230 через драйвер 270 выдается сигнал SYNC и вместо сигнала PREAMBLE для передачи по каналу 130 связи между кристаллами интегральных схем через селекторную шину 238 выбирается сигнал PACKET_TYPE. Если сигнал PREAMBLE_ SENT не активен на линии 265, когда конечный автомат 230 принимает сигнал NEW_REQUEST на входе 242, а сигнал РАСКЕТ_ТУРЕ на входе 240 является типом, идентифицированным конечным автоматом 230, который требует вход PREAMBLE в свой командный пакет, то конечный автомат 230 выбирает вход 207 PREAMBLE через селекторную шину 238 для выхода мультиплексором 230 по каналу 130 связи между кристаллами интегральных схем.

Всякий раз, когда импульс SYNC является выходным сигналом по линии 271 через драйвер 270, сигнал PACKET_TYPE будет представлен в канале 130 связи между кристаллами интегральных схем. Импульс SYNC принимается кристаллом 120 интегральной схемы как управляющий сигнал, который показывает, что началась транзакция пакета данных. При приеме импульса SYNC, схемотехника внутри кристалла 120 хранимые в регистре 280 как данные преамбулы, поступившие на вход PREAMBLE к транзакции пакета данных, в то время как данные, находящиеся в то же время на шине 295 интерпретируются как данные, поступившие на вход PARKET_ TYPE. Таким образом, поскольку данные в регистре 280 являются одинаковыми с данными в регистре 255 (поскольку оба регистра хранят данные, которые были переданы в канал 130 связи между кристаллами интегральных схем в предшествующем периоде тактовых импульсов) и поскольку данные в регистре 255 одинаковы с данными, поступившими на вход PREAMBLE, то и данные в буфере 285 будут такими же, как входные данные преамбулы. Таким образом, входные данные преамбулы нового пакета нет необходимости посылать, если эти данные те же, что набор двоичных разрядов IDLE канала связи между кристаллами интегральных схем, или те же, что последнее слово предшествующего пакета, вследствие чего экономится число периодов тактовых импульсов в общей транзакции данных.

На фиг. 3А-3С показаны диаграммы синхронизации, на которых более ясно иллюстрируется способ, с помощью которого экономятся в соответствии с настоящим изобретением тактовые интервалы. На фиг.3А показана сигнальная синхронизация на канале связи между кристаллами интегральных схем, не обладающая преимуществами настоящего изобретения. Первый сигнал 302 представляет синхронный тактовый сигнал, который используется для тактирования слов данных пакета в кристаллах 110, 120 интегральных схем, в то время как сигнал 304 представляет сигналы слова данных пакета, представленные на четырехразрядной части CMD канала 130 связи между кристаллами интегральных схем (то есть другой, чем сигнал, представленный на линии SYNC). Наконец, сигнал 306 представляет сигнал SYNC, передаваемый по каналу 130 связи между кристаллами интегральных схем. Каждый выход слова CMD пакета на канале 130 связи между кристаллами интегральных схем представлен в течение длительности всего тактового интервала. Следовательно, для связи между передающим кристаллом 110 интегральной схемы и принимающим кристаллом 120 интегральной схемы требуется столько тактовых интервалов, сколько слов CMD в пакете.

Например, как показано на фиг. 3А, канал 130 связи между кристаллами интегральных схем простаивает в течение двух тактовых интервалов до сообщения слова PREAMBLE (например, индекса буфера, который идентифицирует буфер, в который должны быть переданы данные в последующей транзакции) в течение следующего периода тактовых импульсов. Следующие периоды тактовых импульсов используются для передачи данных на вход PACKET_TYPE (показывающего среди прочего тип команды) и слово MODIFIER (которое дополнительно определяет команду).

Начиная с выхода слова PREAMBLE, показанного на фиг.3А, общие три периода тактовых импульсов имеют место до тех пор, пока последнее слово MODIFIER не выйдет в канал 130 связи между кристаллами интегральных схем. Если определено, что слово PACKET_TYPE, следующее после слова PREAMBLE обеспечено на канале 130 связи между кристаллами интегральных схем, то для индикации наличия нового пакета обеспечивается сигнал 306 SYNC. Как кратко описано выше, сигнал SYNC предупреждает принимающий кристалл 120 интегральной схемы, что слова PREAMBLE и PACKET_TYPE были приняты на шинах 290 и 295. После этого принимающий кристалл 120 интегральной схемы интерпретирует данные, которые являются последующими на шине 295, как остальные слова CMD (если они есть) в пакете CMD. Например, в том случае, когда слово MODIFIER следует после слова PACKET_TYPE, как показано на фиг.3А, слово PACKET_TYPE показывает, что следующее слово CMD принадлежит к тому же пакету, так что принимающий кристалл 120 интегральной схемы считывает слово CMD на шине 295 в следующем периоде тактовых импульсов как ожидаемые данные MODIFIER.

На фиг.3В иллюстрируется способ, соответствующий настоящему изобретению, который приводит к экономии одного периода тактовых импульсов по сравнению с обычным протоколом, показанным на фиг.3А. Характерно то, что изобретатель понял, что принимая во внимание соотношения между словами CMD, передаваемыми по каналу связи между кристаллами интегральных схем, к принимающему кристаллу интегральной схемы в течение одной длительности периода тактовых импульсов может быть выпущено множество слов CMD. В частности, как иллюстрируется на фиг. 3В, общие два периода тактовых импульсов имеют место от конца слова паузной комбинации до тех пор, пока слово MODIFIER не выйдет в канал 130 связи между кристаллами интегральных схем. Имеют место только два периода тактовых импульсов, поскольку слово PREAMBLE нет необходимости посылать в том случае, когда слово PREAMBLE аналогично слову паузной комбинации. Как описано выше со ссылкой на фиг.2, делается сравнение слова PREAMBLE и слова CMD, посланного прежде в канал 130 связи между кристаллами интегральных схем. Если слово PREAMBLE аналогично предшествующему слову CMD (то есть в этом случае слову паузной комбинации), то слово PACKET_TYPE вместе с сигналом SYNC посылается вместо слова PREAMBLE. В этом случае обеспечивается начальный сигнал SYNC, так что пакет CMD для завершения требует только двух периодов тактовых импульсов. Определение, что слово паузной комбинации аналогично слову PREAMBLE, означает, что данные в регистре 280 аналогичны слову PREAMBLE, поскольку принимающий кристалл 120 интегральной схемы также регистрирует предшествующее слово IDLE в регистре 280. Таким образом, принимающий кристалл 120 интегральной схемы будет работать так, как если бы слово PREAMBLE было послано в предшествующем периоде тактовых импульсов. В этом случае слово PREAMBLE может быть заменено словом IDLE, которое было передано в предшествующем периоде тактовых импульсов, в котором должно было быть передано слово PREAMBLE. Следовательно, слово PREAMBLE может быть заменено словом PACKET_ TYPE для экономии периода тактовых импульсов во всем пакете CMD. То есть нет необходимости передавать индекс буфера, показанный входом 207 PREAMBLE (см. фиг.2) в канал 130 связи между кристаллами интегральных схем, поскольку слово IDLE, уже представленное в канале 130 связи между кристаллами интегральных схем, было использовано для замены индекса буфера. По этой причине, конечный автомат 230 управляет мультиплексором 220 для выбора слова PACKET_ TYPE вместо индекса буфера, так что в процессе следующего тактового интервала принимающий кристалл 120 интегральной схемы может принимать оба слова PREAMBLE и PACKET_TYPE.

В соответствии с одним аспектом настоящего изобретения, индекс буфера, который вероятнее всего имеет такой же набор двоичных разрядов, что и слово IDLE (подразумеваемое слово PREAMBLE), так что всякий раз, когда выбирается этот буфер, индекс буфера может быть тактирован в регистре в принимающем кристалле 120 интегральной схемы в том же периоде тактовых импульсов, что и предшествующее слово IDLE. В особенно предпочтительном варианте осуществления настоящего изобретения код слова IDLE модифицируется для соответствия подразумеваемому индексу буфера для увеличения вероятности совпадения слова PREAMBLE и слова IDLE. Безусловно, если индекс буфера в слове PREAMBLE не аналогичен слову IDLE, то прежде чем индекс буфера может быть зафиксирован в принимающем кристалле 120 интегральной схемы, должен иметь место дополнительный период тактовых импульсов. Однако в том случае, если индекс буфера (который содержит первую часть слова PREAMBLE) аналогичен слову IDLE, как показано на фиг. 3В, то сигнал SYNC может быть обеспечен незамедлительно в том же периоде тактовых импульсов, что и слово PACKET_TYPE, поскольку слово IDLE может служить в качестве замены индекса буфера.

На фиг. 3С показан тот случай, где имеют место последовательные пакеты CMD и где слово PREAMBLE второго пакета CMD имеет тот же набор двоичных разрядов, что и последнее слово CMD первого пакета CMD. Как показано на фиг. 3С, сигнал SYNC формируется непосредственно после того, как последнее слово предшествующего пакета CMD послано принимающему кристаллу 120 интегральной схемы. Поскольку это последнее слово пакета имеет аналогичный набор двоичных разрядов, что и слово PREAMBLE нового пакета, мультиплексор 220 вынужден выпустить слово PACKET_TYPE вместо слова PREAMBLE во время обеспечения сигнала SYNC. Следовательно, два периода тактовых импульсов проходит от одного конца первого пакета CMD до конца второго пакета CMD. С другой стороны, если слово PREAMBLE было послано отдельно (без использования последнего слова первого пакета в качестве слова PREAMBLE), для завершения второго пакета CMD потребуется три периода тактовых импульсов.

Поскольку содержимое первого пакета CMD определялось длиной этого пакета, принимающий кристалл 120 интегральной схемы не имеет трудностей при определении, имеется ли последнее слово CMD на шине 295. Кроме того, как только сигнал SYNC принимается кристаллом 120 интегральной схемы, информация, имеющаяся в регистре 280, рассматривается кристаллом 120 интегральной схемы как слово PREAMBLE нового пакета. Таким образом, информация на шине 295 используется принимающим кристаллом 120 интегральной схемы дважды - один раз при предшествующем тактовом сигнале в качестве последнего слова первого пакета CMD (дискретизированного на шине 295) и один раз в качестве слова PREAMBLE для второго пакета CMD (дискретизированного на шине 290).

Более подробное описание работы схемотехники в кристалле 110 интегральной схемы для случая, иллюстрируемого на фиг.3С, приведено ниже. Характерно, что, если последнее слово CMD первого пакета CMD было выходом из мультиплексора 220, то это слово CMD записывается в регистре 255 и сравнивается с последующим словом PREAMBLE, подаваемым в компаратор 260 шины 207. Если в компараторе 260 определено, что слово PREAMBLE аналогично предшествующему слову CMD, то по линии 265 формируется выходной сигнал компаратора и передается в конечный автомат 230, так что конечный автомат 230 заставляет мультиплексор 220 обеспечивать выход PACKET_TYPE, а не слово PREAMBLE. В то же самое время, конечный автомат 230 возбуждает сигнал SYNC в течение одного тактового интервала через драйвер 270. Таким образом, последнее слово CMD первого пакета CMD служит в качестве индекса буфера второго пакета CMD. Таким образом, период тактовых импульсов экономится в процессе последующих передаваемых сообщений пакета.

Фиг.4 - диаграмма состояний, которая представляет работу конечного автомата 230 в отношении формирования начального слова PREAMBLE в соответствии с настоящим изобретением. На практике, конечный автомат 230 обеспечит также управление другими элементами в передающем кристалле 110 интегральной схемы, но для обеспечения ясности иллюстрации настоящего изобретения эта функция конечного автомата 230 на упрощенной диаграмме состояний, показанной на фиг. 4, не представлена.

При инициировании сигнала RESET конечный автомат 230 входит в состояние 400 IDLE. Когда конечный автомат 230 находится в состоянии 400 IDLE, это показывает, что конечный автомат 230 готов принимать дополнительные пакеты CMD для выхода по каналу 130 связи между кристаллами интегральных схем. Конечный автомат 230 остается в состоянии 400 IDLE при трех разных условиях, как показано дорожкой 410 трансформации состояния, которая возвращается к состоянию 400 IDLE.

При первом условии, если сигнал NEW REQUEST (то есть сигнал, подаваемый по линии 242) не возбуждается, то конечный автомат 230 остается в состоянии 400 IDLE, а мультиплексор 220 обеспечивает выходы подразумеваемого слова PREAMBLE в качестве команды по четырехразрядной части шины CMD канала связи 130 между кристаллами интегральных схем через мультиплексор 220 и драйвер 250. Слово PREAMBLE предпочтительно устанавливается равным наиболее общедоступному буферу, таким образом, имеется более высокая вероятность того, что следующее действительное слово PREAMBLE равно данным, которые были посланы в предшествующем периоде тактовых импульсов.

Другое условие, при котором конечный автомат 230 остается в состоянии 400 IDLE, возникает, если возбуждается сигнал PREAMBLE_REQD (показывающий конечному автомату 230, что для нового пакета CMD, который должен быть передан по каналу 130 связи между кристаллами интегральных схем, требуется слово PREAMBLE), а сигнал PREAMBLE_SENT является неактивным (то есть показывающим, что слово CMD, посланное по каналу 130 связи между кристаллами интегральных схем в предшествующем тактовом интервале, не было равно слову PREAMBLE на шине 207. Таким образом, поскольку требуется слово PREAMBLE и поскольку слово CMD в канале 130 связи между кристаллами интегральных схем в предшествующем периоде тактовых импульсов не является словом PREAMBLE, конечный автомат 230 формирует селекторный сигнал к мультиплексору 220 по линии 238, который позволяет слову PREAMBLE на шине 207 пройти в канал 130 связи между кристаллами интегральных схем. Таким образом, сформированное слово CMD равно слову PREAMBLE.

Последнее условие, при котором конечный автомат 230 остается в состоянии 400 IDLE, возникает, если 1) сигнал PREAMBLE_REQD не возбужден или сигнал PREAMBLE_ SENT не возбужден; и 2) сигнал NEW_REQUEST возбужден, в то время как сигнал MODIFIER_REQD деактивирован. То есть, поскольку 1) слово PREAMBLE не требуется или слово CMD в канале 130 связи между кристаллами интегральных схем в предшествующем периоде тактовых импульсов равно слову PREAMBLE, которое должно быть послано; и 2) новый затребованный пакет имеет слова MODIFIER, это показывает, что, если текущий пакет требует слово PREAMBLE, то это слово PREAMBLE уже выпущено в предшествующем тактовом интервале и что текущий пакет заканчивается текущим словом PACKET_TYPE. Следовательно, конечный автомат 230 выполнен с возможностью принимать новый пакет для передачи по каналу 130 связи между кристаллами интегральных схем в следующем тактовом интервале. Таким образом, конечный автомат 230 остается в состоянии 400 IDLE.

При этом последнем условии, когда конечный автомат 230 остается в состоянии 400 IDLE, конечный автомат 230 заставляет послать слово PACKET_TYPE по каналу 130 связи между кристаллами интегральных схем через мультиплексор 220 и драйвер 250. Кроме того, через драйвер 270 возбуждается сигнал SYNC, в то время как сигнал RDY (готовности) также возбуждается по линии 244.

Конечный автомат 230 переходит из состояния 400 IDLE в состояние 420 BSY (занятое) по переходной дорожке 430 всякий раз, когда определяется, что 1) либо не требуется слово PREAMBLE, либо слово CMD в канале 130 связи между кристаллами интегральных схем в предшествующем периоде тактовых импульсов было равно слову PREAMBLE, которое должно быть послано; и 2) был сделан новый запрос, который требует слов MODIFIER. To есть 1) если сигнал PREAMBLE_ REQD не возбужден или сигнал PREAMBLE_SENT возбужден; и 2) если сигнал NEW_ REQUEST возбужден по линии 242, в то время как слово PACKET_TYPE показывает, что пакет CMD содержит одно или более слов MODIFIER, конечный автомат 230 переходит из состояния 400 IDLE в состояние 420 BSY. Таким образом, это показывает, что данные с входа 240 PARKET_TYPE должны быть переданы в канал 130 связи между кристаллами интегральных схем через мультиплексор 220 и драйвер 250, в то время как сигнал SYNC также возбуждается через драйвер 270. Кроме того, слово MODIFIER_PTR (которое является величиной, загружаемой в счетчик для подсчета числа слов MODIFIER после слова PACKET_TYPE текущего пакета) устанавливается равным единице. Конечный автомат 230 переходит в состояние BSY (то есть в состояние, где конечный автомат 230 не способен обрабатывать новый запрос до тех пор, пока не закончится передача текущего пакета).

Конечный автомат 230 остается в состоянии 420 BSY, как показано дорожкой 440 перехода, в то время как сигнал LAST_MODIFIER не возбужден (то есть, в то время как сигнал, который показывает, что последнее слово CMD пакета было выпущено в канал 130 связи между кристаллами интегральных схем является неправильным). Каждый раз переход осуществляется по дорожке 440, следующее слово CMD (то есть следующее слово MODIFIER из шины 212) проходит в канал 130 связи между кристаллами интегральных схем через мультиплексор 220 и драйвер 250. Кроме того, слово MODIFIER_PTR наращивается до тех пор, пока не достигнет последнего слова MODIFIER текущего пакета. Как только последнее слово пакета прошло в канал 130 связи между кристаллами интегральных схем, конечный автомат 230 переходит из состояния 420 BSY назад в состояние 400 IDLE по дорожке 450 трансформации состояния. Как показано на фиг.4. переход по дорожке 450 имеет место, если возбуждается сигнал LAST_MODIFIER. Это заставляет слово MODIFIER выходить в канал 130 связи между кристаллами интегральных схем равным последнему слову текущего пакета, в то время как конечный автомат 230 возбуждает сигнал RDY по линии 244.

Хотя настоящее изобретение было подробно описано выше, необходимо понять, что приведенное выше описание является иллюстративным, а не ограничительным. Обычному квалифицированному в этой области техники специалисту будет очевидно, что может быть сделано множество модификаций описанных вариантов осуществления без отклонения от сущности и объема настоящего изобретения. Например, обычному квалифицированному специалисту в этой области техники будет очевидно, что настоящее изобретение будет наиболее эффективным, когда осуществляется совместно с каналом связи между кристаллами интегральных схем, имеющим меньше двоичных разрядов в слове CMD, так что вероятность наличия идентичных слов CMD более значительна; однако на практике шины порядка пяти разрядов или более могут также быть выполнены в соответствии с настоящим изобретением. Кроме того, настоящее изобретение может быть выполнено последовательно, где слова CMD пакета посылаются последовательно по одной линии передачи сигналов между кристаллами интегральных схем. В этом случае, сигнал SYNC обеспечивает информацию границы слова CMD, а также означает наличие нового пакета. Другое исполнение может резервировать уникальный набор двоичных разрядов слова CMD, чтобы показать наличие сигнала SYNC, исключая, таким образом, необходимость отдельной линии SYNC. Другое исполнение может включать в себя специальные регистры в одном или в обоих передающем и принимающем кристаллах интегральных схем для разрешения более высокой скорости тактирования. В соответствии с этим, объем настоящего изобретения должен интерпретироваться принимая во внимание приведенную ниже формулу изобретения.

Изобретение относится к средствам для уменьшения общего числа периодов тактовых импульсов, необходимых для передачи данных по каналу связи между кристаллами интегральных схем. Техническим результатом является сокращение времени ожидания связи. Устройство содержит селекторную схему, память для временного хранения данных, компаратор. Способ описывает работу данного устройства. 3 с. и 9 з.п.ф-лы, 4 ил.

| US 4677544 А, 30.06.1987 | |||

| УСТРОЙСТВО ПАКЕТНОЙ ОБРАБОТКИ ЗАПРОСОВ | 1992 |

|

RU2035065C1 |

| ЛАЗАРЕВ В.Г | |||

| Интеллектуальные цифровые сети | |||

| Справочник | |||

| - М.: Финансы и статистика, 1996, с.88-93, 95-100 | |||

| US 5499385 А, 12.03.1996. | |||

Авторы

Даты

2002-09-20—Публикация

1996-06-27—Подача