Изобретение относится к автоматике и вычислительной технике и может найти применение для обработки хрома тографической, масспектросконической и другой информации в газовой, химической и нефтехимической отраслях промышленности..

Известен интегратор 13, содержащий входной операционный усилитель, преобразователь напряжение - частота корректор нулевой линии, блок управ- лег-шя, накопители и печатающее уст- ройства.

Недостатком интегратора является низкая точность интегрирования совмещенных пиков,

Известен также интегратор I 2 1, содержащий входной регистр, блоки вычитания, I, блоки памяти, счетчики ртмпульсов, триггеры, компараторы, вр.еменной селектор, элементы И, ИЛИ ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент задержки.

Недостатком данного интегратора является конструктивная сложность.

Кроме того известен интегратор 3 э содержагций преобразователь напряжения -- частота, подключенный выходом к счетному входу счетчика интеграла, и операционшш усилитель, соединенный входом с шиной ввода интегрируемого сигнала, а выходом - с входом блока выделения максимумов и минимумов, выход которого подключен к входу порогового блока, соединенного вторым входом с выходом операционного усилителя и с сигнальным входом преобразования напряжения - частота, подключенного управляющим входом к первому выходу порогового блока, соединенного вторым выходом с входом обнуления счетчика интеграла, подключенного входом управления считыванием к выходу блока выделения максимумов и минимумов. Пороговый блок интегратора, в частности, осуществляет блокировку преобразования напряжения -частота при уровнях входного напряжения, меньших по величине заданной полосы нечувствительности.

Недостатком интегратора является низкая точность интегрирования неразделенных пиков, так как в этих случаях в счетчике накапливается только суммарное значение площадей пиков без их разделения.

Целью изобретения является повьше ние точности интегрирования при наличии неразделенных пиков.

0

5

0

5

0

5

0

5

0

5

С этой целью в интегратор, содержащий преобразователь напряжения - частота, подключенный выходом к счетному входу счетчика интеграла, и one- рационшяй усилитель, соединенный входом с шиной ввода интегрируемого сигнала, а выходок - с входом блока выделения максимумов и минимумов, выход которого подключен к входу порогового блока, дополнительно введены блок вычитания, блок деления, блок вычисления поправочной площади, элементы задержки, триггер, ключи, элемент ИЛИ и переключатель, соединенный входом с выходом операционного усилителя, а выходом - с сигнальным входом первого ключа и через первый элемент задержки - с сигнальным входом второго ключа, подключенного выходом к выходу первого ключа и к первому входу блока вычитания, соединенного вторым входом с выходом блока .выделения максимумов и минимумов и с первым входом блока вычисления поправочной площадки, подключенного вторым входом через блок деления к выходу блока вычитания, выходом - к сигнальному входу третьего ключа, соединенного выходом с входом преобразователя напряжег-ше - частота и с выходом четвертого ключа, управляющим входом - с выходом элемента ИЛИ, подключенного первым входом к выходу второго элемента задержки, управляющему входу первого ключа и к входу обнуления счетчика интеграла, вторым входом - к единичному выходу триггера, управляющему входу второго ключа и к первому управляющему входу четвертого ключа, Соединенного сигнальным входом с выходом операционного усилителя, вторым управляющим входом - с выходом третьего элемента задержки, подключенного входом к нулевому выходу триггера, единичный установочный вход которого соединен с выходом порогового блока и с входом четвертого элемента задержки, а вход обнуления - с выходом четвертого элемента задержки.

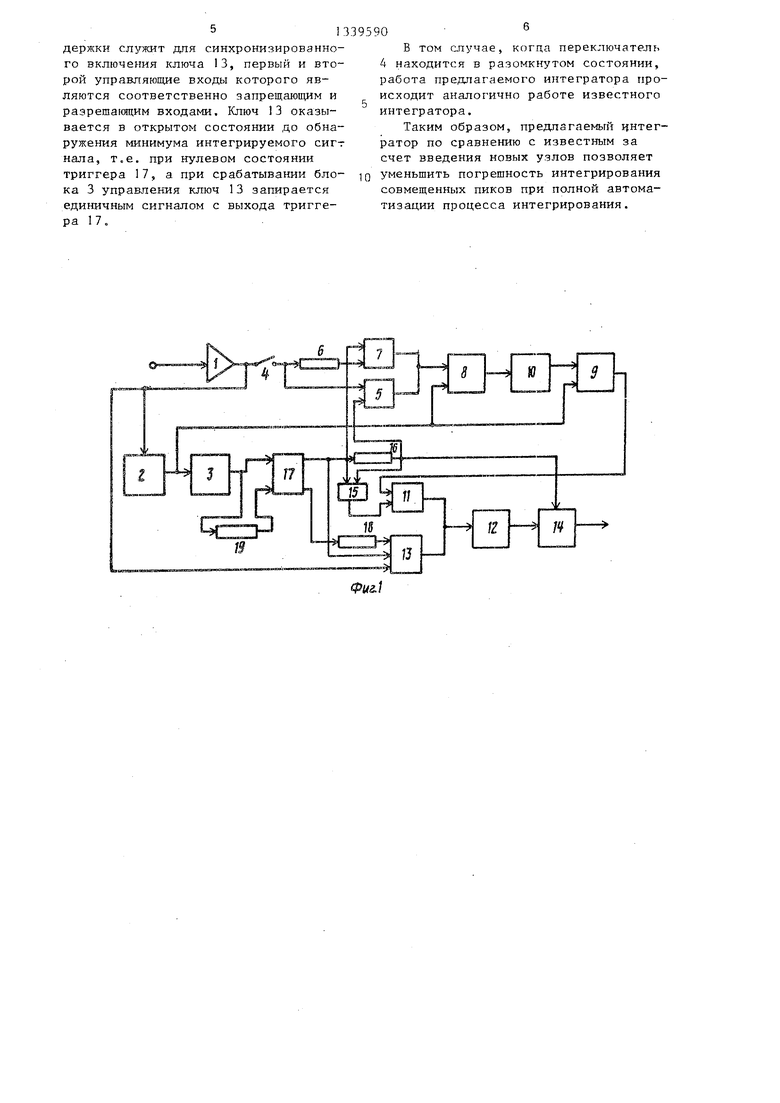

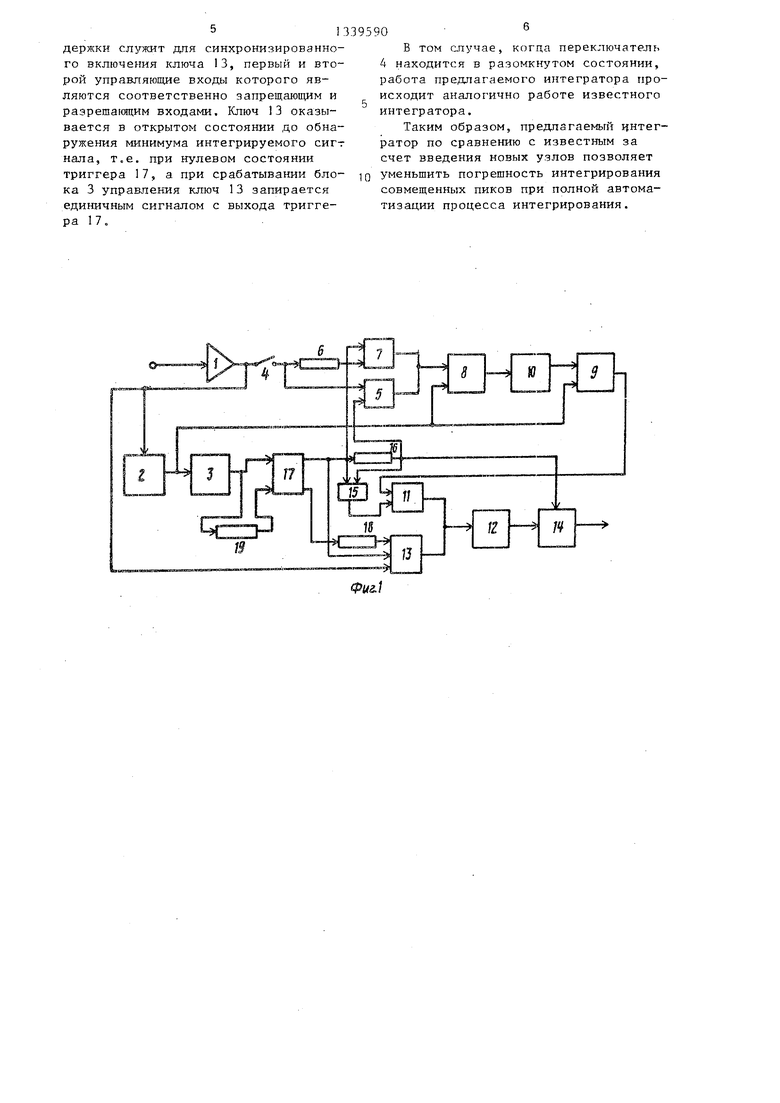

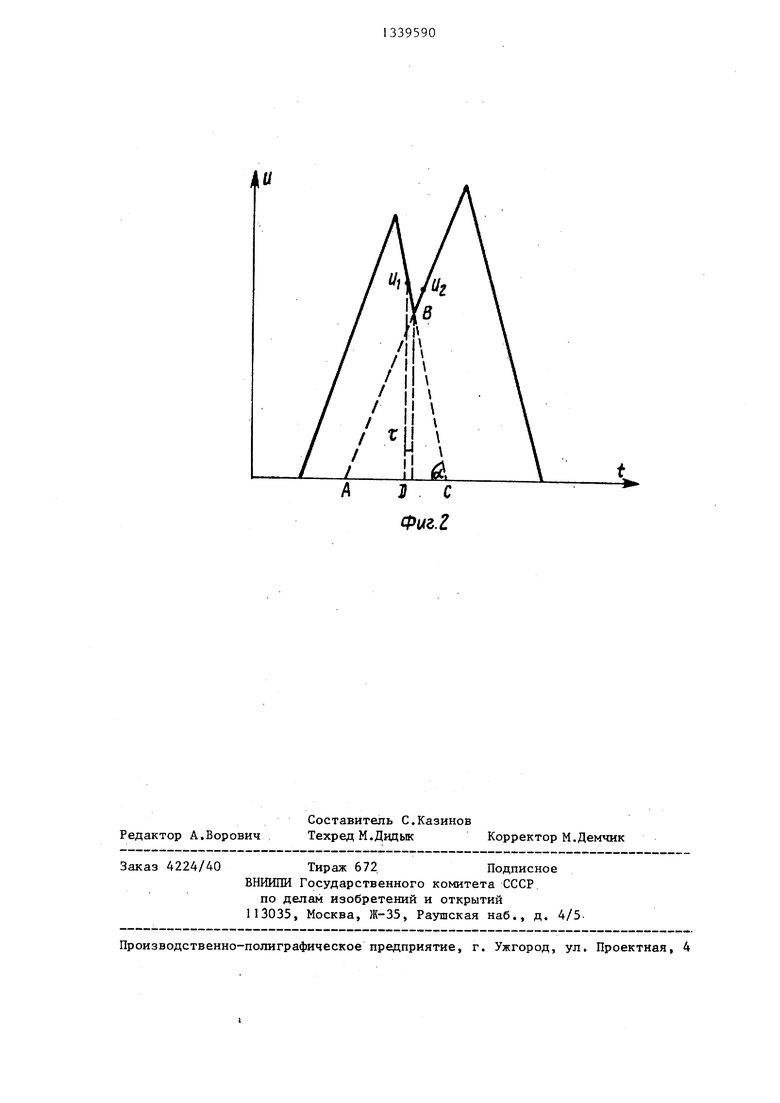

На фиг.1 представлена блок-схема интегратора; на фиг.2 - кривая совмещенных пиков.

Интегратор содержит операционный усилитель I, соединенный входом с шиной ввода интегрируемого сигнала, а выходом т с входом блока 2 вьщеления максимумов и минимумов, выход которого подключен к пходу порогового блока 3. Переключатель 4 соединен входом с выходом усилителя 7, а выходом с сигнальным входом первого ключа 5 и через первый элемент 6 задержки - с сигнальным входом второго ключа 7. Выход ключа 7 подключен к выходу ключа 5 и к первому входу блока 8 вычитания, соединенного вторым входом с выходом блока 2 вьщеления максимумов и минимумов и с первым входом блока 9 вычитания поправочной площадки. Блок 9 подключен вторым входом через блок 10 деления к выходу блока 8 вычитания, а выходом - сигнальному входу третьего ключа 11. Выход ключа 1I соединен с входом преобразователя 12 напряжение - частота и с выходом четвертого ключа 13. Выход преобразователя 12 подключен к счетному входу счетчика 14 интеграла, а управляющий вход ключа 11 соединен с выходом элемента ИЛИ 15. Элемент ИЛИ 15 подключен первым входом к выходу второго элемента 16 задержки, управляющему входу ключа 5 и к входу обнуления счетчика 14 интеграла, а вторым входом - к единичному выходу триггера 17, управляющему входу ключа 7 и к первому управляющему входу ключа 13. Ключ 13 соединен сигнальньш входом с выходом усилителя 1, а вторым управляющим входом - с выходом третьего элемента 18 задержки, подключенного входом к нулевому выходу триггера 17. Триггер 17 соединен единичным установочным входом с выходом блока.3 и с входом четвертого элемента 19 задержки, а входом обнуления - с .выходом элемента 19 задержки.

Интегратор работает следующим образом.

Входной сигнал подают на вход операционного усилителя 1 . В случае прохождения неразделенных пиков (фиг.2) блок 2 выдает сигнал минимума и, (точка Б на графике фиг.2), который по величине отличается от полосы нечувствительности. Тогда пороговый блок 3 формирует сигнал, переводящий триггер 17 в единичное состояние. При замкнутом переключателе 4 выходной сигнал усилителя 1 через элемент 6 задержки, осуществляющий задержку этого сигнала на время Т , поступает на сигнальный вход ключа 7, который находится в открытом состоянии

за счет поступленпя пя его управляю- ицш вход разрешающего сигнала с единичного выхода триггера 17, Напряже- ние с выхода ключа 7 (соответствую

щие точке U на графике фиг.2) поступает на блок 8 вычитания, на выходе которого формируется разность / и. - и, / . Блок 10 деления осу- ществляет деление этой разности на число, равное времени задержки элемента 6, следовательно, на выходе

блока 10 формируется сигнал, соответствующий тангенсу угла наклона нисходящей ветви графика (фиг.2): tgd ьи/,.

В блоке 9 происходи вычисление поправочной (дополнительный) площади ВВС первого из двух совмещенных пиков по формуле U , /2tg6(, которая может быть реализована, например, на основе последовательного выполнения операций возведения в квадрат и деления.

При наличии разрешающего сигнала на управляющем входе ключа 11, который поступает с выхода элемента ИЛИ. 15, выходное напряжение блока 9 поступает на вход преобразователя 12

напряжение - частота. Счетчик 14 производит суммирование поступающих импульсов и вьщает на печать площадь первого разделенного сигнала, после чего счетчик 14 обнуляется. Для вычисления площади восходящей ветви кривой используют элемент 16 задержки, время задержки которого совпадает с временем задержки элемента 6. Единичный сигнал с выхода триггера

17 после прохождения элемента 16 задержки поступает на управляющий вход ключа 5 и на элемент ИЛИ 15. Сам триггер 17 к этому моменту времени с помощью элемента 9 задержки переходит в нулевое состояние. Б результате ключ 7 оказывается закрытым, а ключ 5 - открытым и сигнал с выхода ключа 5, соответствующий точке U на графике фиг.2 обрабатывается блоками 8, 10 и 9 аналогично описанному. Напряжение, соответствующее поправочной площади uABD (фиг.2) восходящего участка кривой, преобразуется с помощью преобразователя 12 в соответствующее число импульсов и суммируется счетчиком 14. Последующие текущие значения сигнала кривой поступают на вход преобразователя 12 через ключ 13, при этом элемент 18 за

держки для синхронизированного включения ключа 13, первый и второй ynpaBj-сягощие входы которого являются соответственно запрещающим и разрешающим входами. Ключ 13 оказывается в открытом состоянии до обнаружения минимума интегрируемого сигнала, т.е. при нулевом состоянии триггера 17, а при срабатывании блока 3 управления ключ 13 запирается единичным сигналом с выхода триггера 17.

339590

В том спучае, когда переключатель 4 находится в разомкнутом состоянии, работа предлагаемого интегратора происходит аналогично работе известного интегратора.

Таким образом, предлагаемый интег- г ратор по сравнению с известным за

счет введения новых узлов позволяет 1Q уменьшить погрешность интегрирования совмещенных пиков при полной автоматизации процесса интегрирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для интегрирования хроматографической функции | 1983 |

|

SU1160443A1 |

| Устройство для интегрирования хроматографической функции | 1986 |

|

SU1383402A1 |

| Гибридное интегрирующее устройство | 1985 |

|

SU1316008A1 |

| Устройство для обработки хроматографической информации | 1980 |

|

SU896645A2 |

| Устройство для определения моментов появления экстремумов | 1989 |

|

SU1661980A2 |

| Устройство для коррекции базовой линии хроматографического сигнала | 1983 |

|

SU1105914A1 |

| Аналого-дискретное интегрирующее устройство | 1975 |

|

SU556463A1 |

| Устройство для измерения уровня радиопомех | 1987 |

|

SU1506396A1 |

| Устройство для регулирования тока | 1988 |

|

SU1582321A1 |

| Устройство для определения граничных точек хроматографического пика | 1986 |

|

SU1456973A1 |

Редактор А.Ворович

Составитель С.Казинов

Техред М.Дидьк Корректор М.Демчик

Заказ 4224/40 Тираж 672Подписное

БНКИПИ Государственного комитета СССР.

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5.

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3506818, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Техническая документация | |||

| .Прага, ЧССР, 1978. | |||

Авторы

Даты

1987-09-23—Публикация

1982-05-17—Подача