1

Изобретение относится к гибридной вычислительной технике и может быть использовано в аналого-цифровых вычислительных системах и устройствах автоматики для длительного интегрирования аналогового сигнала.

Цель изобретения - повышение точности интегрирования.

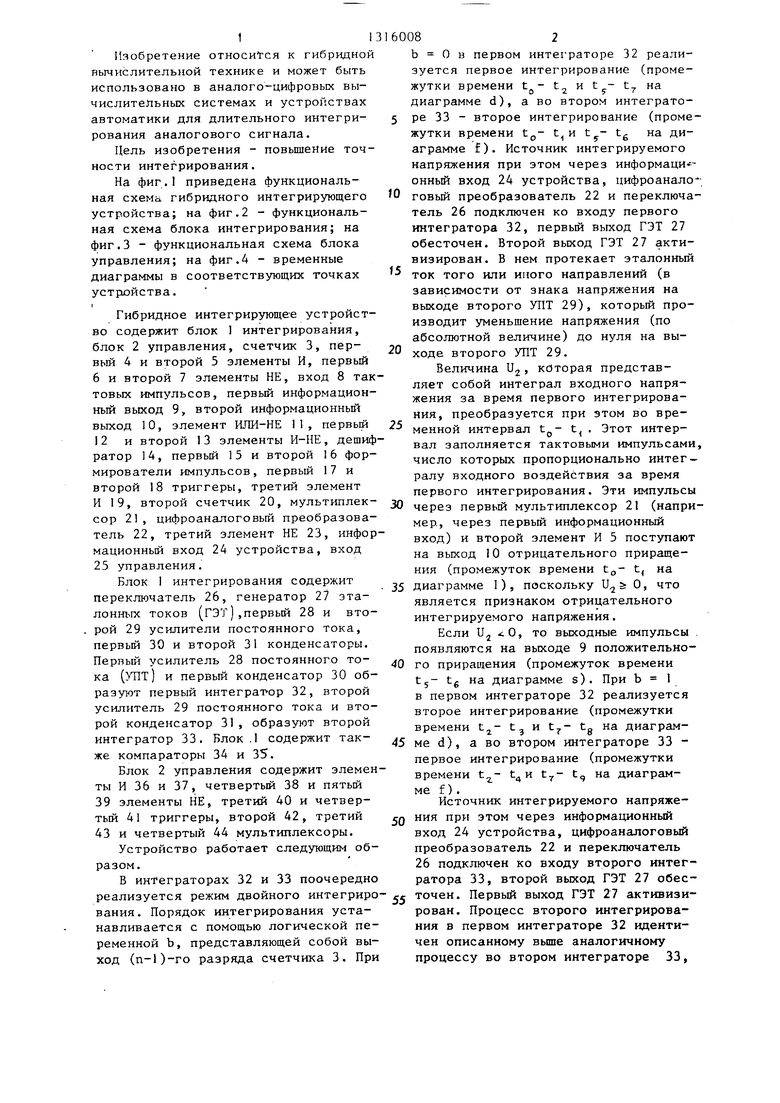

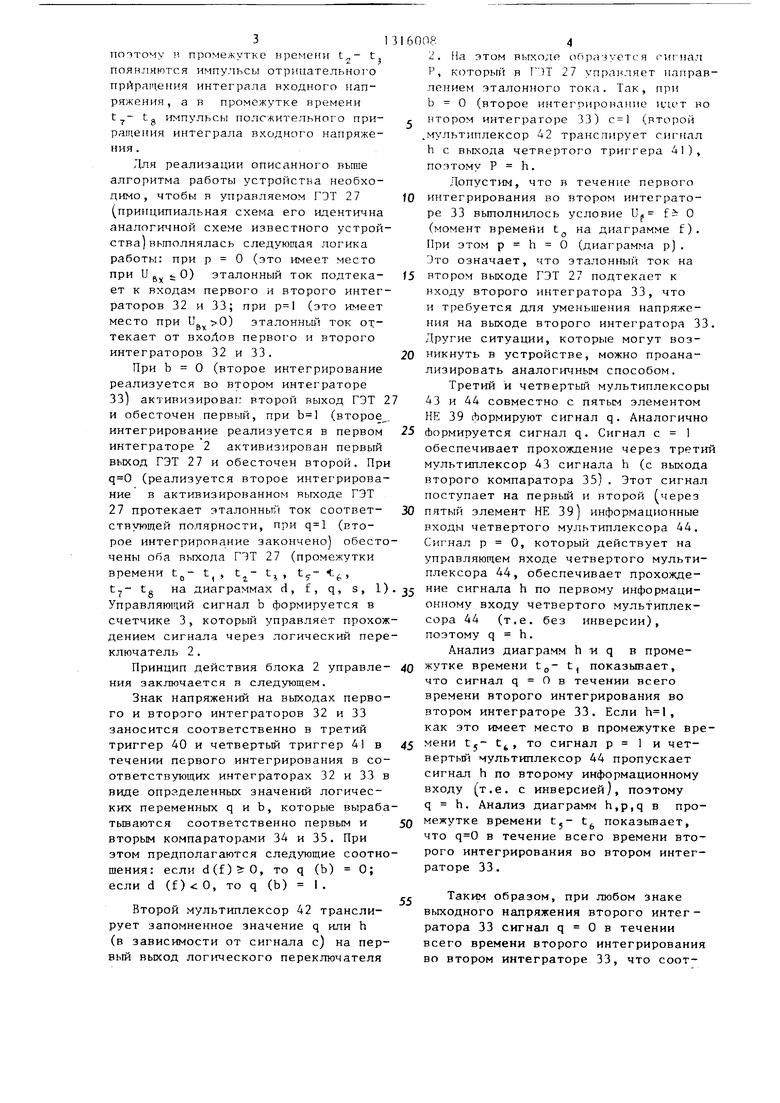

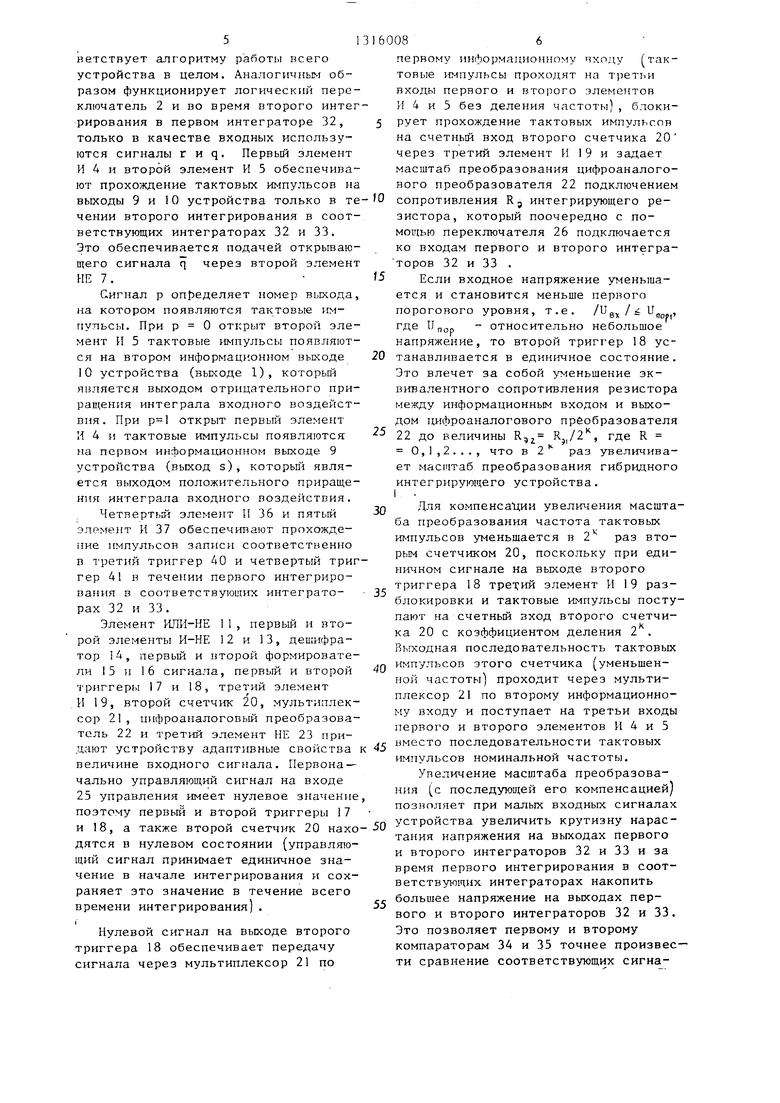

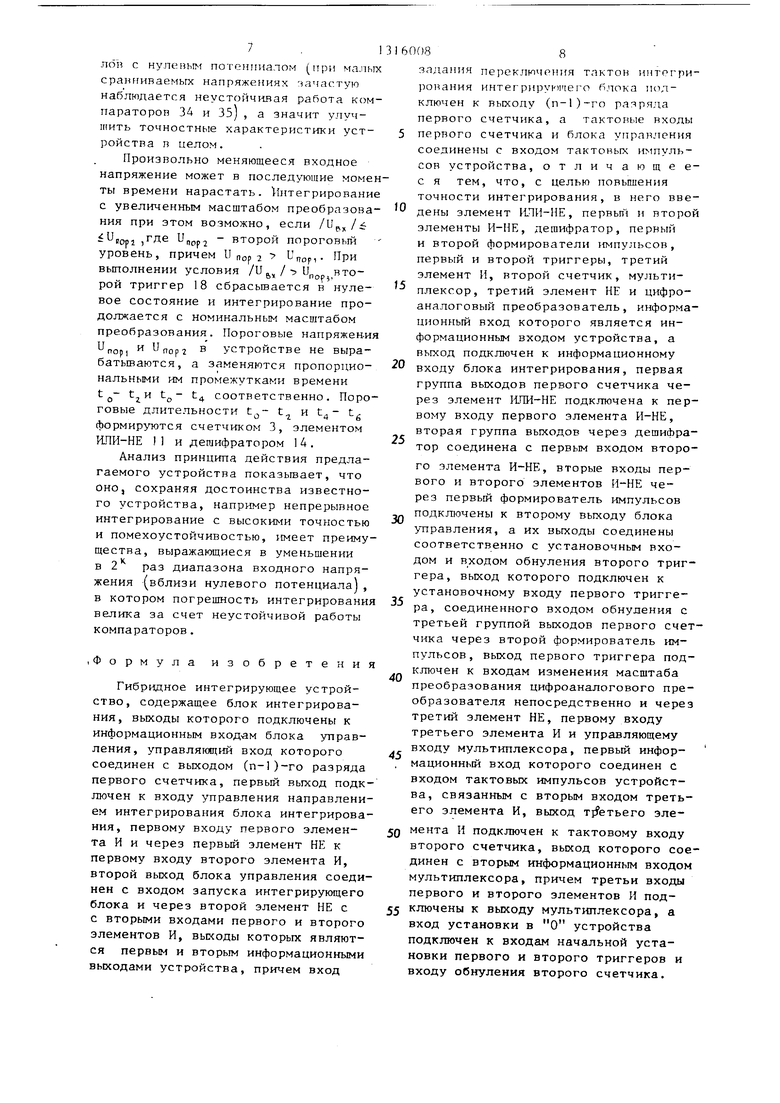

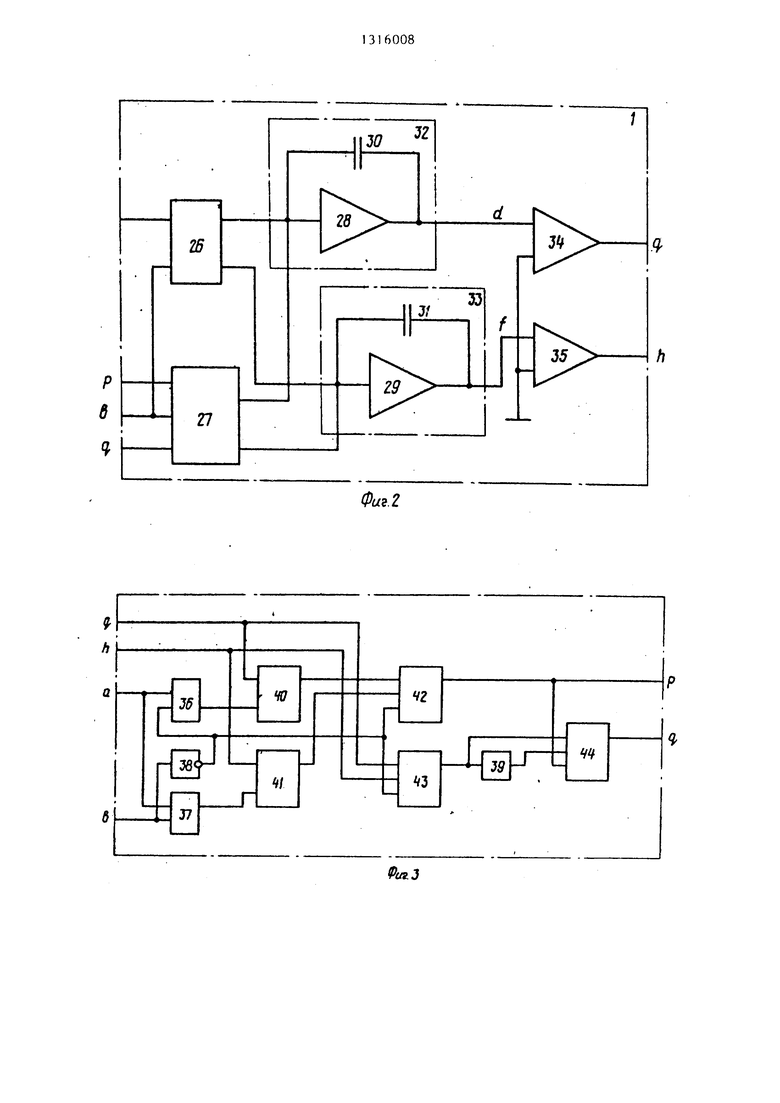

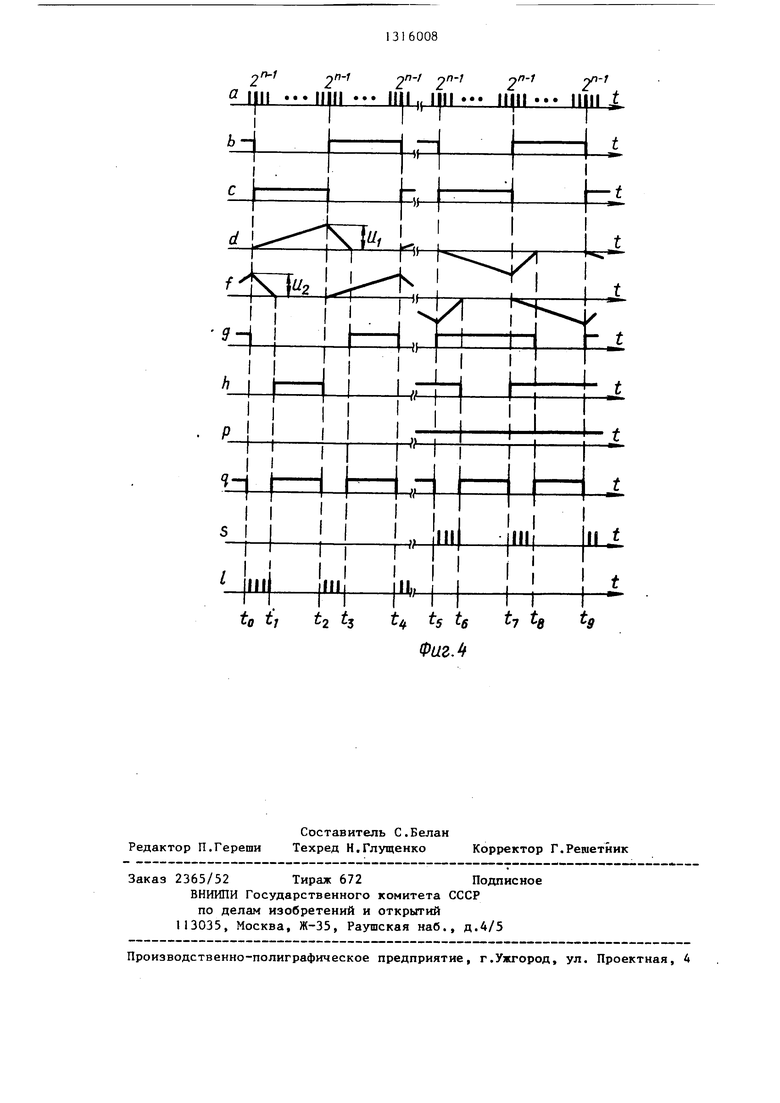

На фиг.1 приведена функциональная схема гибридного интегрирующего устройства; на фиг.2 - функциональная схема блока интегрирования; на фиг.3 - функциональная схема блока управления; на фиг.А - временные диаграммы в соответствующих точках устройства.

Гибридное интегрирующее устройство содержит блок 1 интегрирования, блок 2 управления, счетчик 3, первый 4 и второй 5 элементы И, первый 6 и второй 7 элементы НЕ, вход 8 тактовых импульсов, первый информационный выход 9 второй информационньо выход 10, элемент ИЛИ-НЕ 11, первый 12 и второй 13 элементы И-НЕ, дешифратор 14, первый 15 и второй 16 формирователи импульсов, первый 17 и второй 18 триггеры, третий элемент И 19, второй счетчик 20, мультиплексор 21, цифроаналоговый преобразователь 22, третий элемент НЕ 23, информационный вход 24 устройства, вход 25 управления.

Блок 1 интегрирования содержит переключатель 26, генератор 27 эта- ЛОНН11ГХ токов (ГЭТ),первый 28 и второй 29 усилители постоянного тока, первый 30 и второй 31 конденсаторы. Первый усилитель 28 постоянного тока (Т1Т) и первый конденсатор 30 образуют первый интеграрор 32, второй усилитель 29 постоянного тока и второй конденсатор 31, образуют второй интегратор 33. Блок.1 содержит также компараторы 34 и 35.

Блок 2 управления содержит элементы И 36 и 37, четвертый 38 и пятый 39 элементы НЕ, третий 40 и четвертый 41 триггеры, второй 42, третий 43 и четвертый 44 мультиплексоры.

Устройство работает следующим образом.

В интеграторах 32 и 33 поочередно реализуется режим двойного интегрирования. Порядок интегрирования устанавливается с помощью логической переменной Ь, представляющей собой выход (n-l)-ro разряда счетчика 3. При

082

b О в первом интеграторе 32 реализуется первое интегрирование (промежутки времени t и t на диаграмме d), а во втором интеграторе 33 - второе интегрирование (промежутки времени t,- t и tg на диаграмме f). Источник интегрируемого напряжения при этом через информаци - онньй вход 24 устройства, цифроанало

говый преобразователь 22 и переключатель 26 подключен ко входу первого интегратора 32, первый выход ГЭТ 27 обесточен. Второй выход ГЭТ 27 активизирован. В нем протекает эталонный

ток того или иного направлений (в зависимости от знака напряжения на выходе второго УПТ 29), который производит уменьшение напряжения (по абсолютной величине) до нуля на выходе второго УПТ 29.

Величина U2, которая представляет собой интеграл входного напряжения за время первого интегрирования, преобразуется при этом во временной интервал t . Этот интервал заполняется тактовыми импульсами, число которых пропорционально интегралу входного воздействия за время первого интегрирования. Эти импульсы

через первый мультиплексор 21 (например., через первый информационньй вход) и второй элемент И 5 поступают на выход 10 отрицательного приращения (промежуток времени t, на

диаграмме 1), поскольку U о, что является признаком отрицательного интегрируемого напряжения.

Если Uj 0, то выходные импульсы . появляются на выходе 9 положительного приращения (промежуток времени tj- tg на диаграмме s). При b 1 в первом интеграторе 32 реализуется второе интегрирование (промежутки времени t и tg на диаграмме d), а во втором интеграторе 33 - первое интегрирование (промежутки времени tg на диаграмме f).

Источник интегрируемого напряжения при этом через информационный вход 24 устройства, цифроаналоговый преобразователь 22 и переключатель 26 подключен ко входу второго интегратора 33, второй выход ГЭТ 27 обесточен. Первый выход ГЭТ 27 активизирован. Процесс второго интегрирования в первом интеграторе 32 идентичен описанному вьопе аналогичному процессу во втором интеграторе 33,

поэтому } . промежутке нремепп t - t поянляются импульсы отрицательного прйра1цения интеграла входного напряжения , а в промежутке времени tg импульсы положительного приращения интеграла входного напряжения .

Для реализации описанного выше алгоритма работы устройства необходимо, чтобы в управляемом ГЭТ 27 (принципиальная схема его идентична аналогичной схеме известного устройства выполнялась следующая логика работы: при р О (это имеет место при и t 0) эталонный ток подтекает к входам первого и второго интеграторов 32 и 33; при (это имеет место при ) эталонный ток оттекает от вхоДов первого и второго интеграторов 32 и 33.

При b О (второе интегрирование реализуется во втором интеграторе ЗЗ) активизироваг: второй выход ГЭТ 2 и обесточен первый, при (второе интегрирование реализуется в первом интеграторе 2 активизирован первый выход ГЭТ 27 и обесточен второй. При (реализуется второе интегрирование в активизированном выходе ГЭТ 27 протекает эталонный ток соответствующей полярности, при (второе интегрирование закончено| обесточены оба выхода ГЭТ 27 (промежутки времени t, , t, , t , tg на диаграммах d, f, q, s, 1) Управляющий сигнал b формируется в счетчике 3, который управляет прохождением сигнала через логический переключатель 2.

Принцип действия блока 2 управления заключается в следующем.

Знак напряжений на выходах первого и второго интеграторов 32 и 33 заносится соответственно в третий триггер 40 и четвертый триггер 4 в течении первого интегрирования в соответствующих интеграторах 32 и 33 в виде опргделенных значений логических переменных q и Ъ, которые выраба тьшаются соответственно первым и вторым компараторами 34 и 35. При этом предполагаются следующие соотношения: если d(f)5:0, то q (b) 0; если d (f) О, то q (b) 1 .

Второй мультиплексор 42 транслирует запомненное значение q или h (в зависимости от сигнала с) на первый выход логического переключателя

7. - 160084

2. На этом выходе опразуется сигнал Р, которы В Г М 27 управляет направлением эталонного тока. Так, при b О (второе интегрирование ivu T во г втором интеграторе 33) (второй .м льтиплексор 42 транслирует h с выхода четвертого триггера 41), поэтому Р h.

Допустим, что в течение первого

10 интегрирования во втором интеграторе 33 вьтолнилось условие U fi О (момент времени t на диаграмме f). При этом р h О (диаграмма р). Это означает, что эталонный ток на

15 втором выходе ГЭТ 27 подтекает к входу второго интегратора 33, что и требуется для уменьшения напряжения на выходе второго интегратора 33. Другие ситуации, которые могут воз20 никнуть в устройстве, можно проанализировать аналогичным способом.

Третий и четвертьпЧ мультиплексоры 43 и 44 совместно с пятым элементом НЕ 39 формируют сигнал q. Аналогично

25 формируется сигнал q. Сигнал с 1 обеспечивает прохождение через третий мультиплексор 43 сигнала h (с выхода второго компаратора 35). Этот сигнал поступает на первый и второй (через

30 пятый элемент НЕ 39) информационные входы четвертого мультиплексора 44. Сигнал р О, который действует на управляющем входе четвертого мультиплексора 44, обеспечивает прохожде 2 ние сигнала h по первому информационному входу четвертого мультиплексора 44 (т.е. без инверсии), поэтому q h.

Анализ диаграмм h и q в проме40 жутке времени t,- t, показывает, что сигнал q О в течении всего времени второго интегрирования во втором интеграторе 33. Если , как это имеет место в промежутке вре45 мени tj- t, то сигнал р 1 и четвертый мультиплексор 44 пропускает сигнал h по второму информационному входу (т.е. с инверсией), поэтому q h. Анализ диаграмм h,p,q в про50 межутке времени tj- t показьгоает, что в течение всего времени второго интегрирования во втором интеграторе 33.

ГС Таким образом, при любом знаке выходного напряжения второго ннтег - ратора 33 сигнал q О в течении всего времени второго интегрирования во втором интеграторе 33, что соот5

ветствует алгоритму работы всего устройства в целом. Аналогичным образом функционирует логический переключатель 2 и во время второго интегрирования в первом интеграторе 32, только в качестве входных используются сигналы г и q. Первый элемент И 4 и второй элемент И 5 обеспечивают прохождение тактовых импульсов на выходы 9 и 10 устройства только в течении второго интегрирования в соответствующих интеграторах 32 и 33. Это обеспечивается подачей открьшаю- щего сигнала q через второй элемент НЕ 7.

Сигнал р определяет номер выхода на котором появляются тактовые импульсы. При р О открыт второй элемент И 5 тактовые импульсы появляются на втором информационном выходе 10 устройства (выходе 1), которьп-i является выходом отрицательного приращения интеграла входного воздействия. При р открыт первьм элемент И 4 и тактовые импульсы появляются на первом информационном выходе 9 устройства (выход з), которьш является выходом положительного приращения интеграла входного воздействия.

Четвертый элемент И 36 и пятый элемент И 37 обеспечивают прохождение импульсов записи соответственно в третий триггер 40 и четвертый триггер 41 в течении первого интегрирования в соответствуюиигх интеграторах 32 и 33.

Элемент ИЛИ-НЕ 11, первый и второй элементы И-НЕ 12 и 13, дешифратор 14, первый и второй формирователи 15 и 16 сигн.ала, первый и второй триггеры 17 и 18, третий элемент И 19, второй счетчик 20, мультиплексор 21, пифроаналоговый преобразователь 22 и третий элемент НЕ 23 придают устройству адаптивные свойства величине входного сигнала. Первоначально управляющий сигнал на входе 25 управления имеет нулевое значение поэтому первьй и второй триггеры 17 и 18, а также второй счетчик 20 находятся в нулевом состоянии (управляющий сигнал принимает единичное значение в начале интегрирования и сохраняет это значение в течение всего времени интегрирования).

Нулевой сигнал на выходе второго триггера 18 обеспечивает передачу сигнала через мультиплексор 21 по

60086

первому информационному яходу fтактовые импульсы проходят на третьи входы первого и второго элементов И 4 и 5 без деления частоты), блокирует прохождение тактовых импульсов на счетный вход второго счетчика 20 через третий элемент И I9 и задает масштаб преобразования цифроаналого- вого преобразователя 22 подключением

О сопротивления Rg интегрирующего резистора, который поочередно с помощью переключателя 26 подключается ко входам первого и второго интегра- торов 32 и 33 .

5 Если входное напряжение уменьшается и становится меньше первого порогового уровня, т.е. uopi где и пор относительно небольшое напряжение, то второй трип-ер 18 ус0 танавливается в единичное состояние. Это влечет за собой уменьшение эквивалентного сопротивления резистора между информационным входом и выходом цифроаналогового преобразователя

22 до величины Яэ , где R 0,1,2..., что в 2 раз увеличивает масштаб преобразования гибридного

интегрирующего устройства. I

Q Для компенса ции увеличения масштаба преобразования частота тактовых импульсов уменьшается в 2 раз вторым счетчиком 20, поскольку при единичном сигнале на выходе второго триггера 18 третий элемент И 19 разблокировки и тактовые импульсы поступают на счетный вход второго счетчика 20 с коэффициентом деления 2 . Выходная последовательность тактовых

д импульсов этого счетчика (уменьшенной частоты проходит через мультиплексор 21 по второму информационному входу и поступает на третьи входы первого и второго элементов И 4 и 5

г вместо последовательности тактовых импульсов номинальной частоты.

Увеличение масштаба преобразования (с последующей его компенсацией) позволяет при малых входных сигналах

Q устройства увеличить крутизну нарастания напряжения на выходах первого и второго интеграторов 32 и 33 и за время первого интегрирования в соответствующих интеграторах накопить

большее напряжение на выходах первого и второго интеграторов 32 и 33. Это позволяет первому и второму компараторам 34 и 35 точнее произвести сравнение соответствующих сигналс5п с нулевьм потенциалом (при малых сранргиваемых напряжениях зачастую наблюдается неустойш-шая работа ком- параторон ЗА и 35), а значит улучшить точностные характеристики устройства в целом.

Произвольно меняющееся входное напряжение может в последующие моменты времени нарастать. Интегрирование с увеличенным масштабом преобразования при этом возможно, если Upppj ,где и„рр - второй пороговый уровень, причем U „ор 2 Ь ,,. При вьтолнении условия /Uj,,/ U второй триггер 18 сбрасьшается в нулевое состояние и интегрирование продолжается с номинальным масштабом преобразования. Пороговые напряжения и„д и Unopt в устройстве не выра- батьгоаются, а заменяются пропорциональными им промежутками времени t - tj, и tp - t соответственно. Пороговые длительности t.,- t и t - t формируются счетчиком 3, элементом ИЛИ-НЕ И и дешифратором 14.

Анализ принципа действия предлагаемого устройства показьгоает, что оно, сохраняя достоинства известного устройства, например непрерывное интегрирование с высокими точностью и помехоустойчивостью, имеет преимущества, выражающиеся в уменьшении в 2 раз диапазона входного напряжения (вблизи нулевого потенциала, в котором погрешность интегрирования велика за счет неустойчивой работы компараторов.

.Формула изобретения

Гибридное интегрирующее устройство, содержащее блок интегрирования, выходы которого подключены к информационным вход-ам блока управления, управляющий вход которого соединен с выходом (п-1)-го разряда первого счетчика, первый выход подключен к входу управления направлением интегрирования блока интегрирования, первому входу первого элемента И и через первый элемент НЕ к первому входу второго элемента И, второй выход блока управления соединен с входом запуска интегрирующего блока и через второй элемент НЕ с с вторыми входами первого и второго элементов И, выходы которых являются первым и вторым информационными выходами устройства, причем вход

5

задания переключения тактон интегрирования интегрирукмиего блока подключен к выходу (n-l)-ro разряда первого счетчика, а тактовые входы

первого счетчика и блока управления соединены с входом тактовых импульсов устройства, отличающее- с я тем, что, с целью пояьш1ения точности интегрирования, в него введены элемент ИПИ-ПЕ, первьш и второй элементы И-НЕ, дешифратор, первый и второй формирователи 1 мпульсов, первый и второй триггеры, третий элемент И, второй счетчик, мульти плексор, третий элемент НЕ и цифро- аналоговый преобразователь, информа- ционньгй вход которого является информационным входом устройства, а выход подключен к информационному

входу блока интегрирования, первая группа выходов первого счетчика через элемент I-UTH-HE подключена к первому входу первого элемента И-НЕ, вторая группа выходов через дешифратор соединена с первым входом второго элемента И-НЕ, вторые входы первого и второго элементов И-НЕ через первый формирователь импульсов подключены к второму выходу блока управления, а их выходы соединены соответственно с установочным входом и входом обнуления второго триггера, выход которого подключен к установочному входу первого триггера, соединенного входом обнуления с третьей группой выходов первого счетчика через второй формирователь импульсов, выход первого триггера подключен к входам изменения масштаба преобразования цифроаналогового преобразователя непосредственно и через третий элемент НЕ, первому входу третьего элемента И и управляющему входу мультиплексора, первый информационный вход которого соединен с входом тактовых импульсов устройства, связанным с вторым входом третьего элемента И, выход тгУетьего элеQ мента И подключен к тактовому входу второго счетчика, выход которого соединен с вторым информационным входом мультиплексора, причем третьи входы первого и второго элементов И под5 ключены к выходу мультиплексора, а вход установки в О устройства подключен к входам начальной установки первого и второго триггеров и входу обнуления второго счетчика.

0

0

5

2Б

р в

П

h

W

32

3it

J/

33

29

,л-/

ОЛ-/о / о -/0/7-/9 -/

g МП «ит нНцИп i HIM-t

IГ III

| название | год | авторы | номер документа |

|---|---|---|---|

| Гибридное интегрирующее устройство | 1984 |

|

SU1168972A1 |

| Гибридное интегрирующее устройство | 1985 |

|

SU1418768A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки (ЭЛТ) | 1988 |

|

SU1509862A1 |

| Устройство для воспроизведения запаздывающих функций | 1983 |

|

SU1173424A1 |

| Многоканальное измерительное устройство | 1988 |

|

SU1617430A1 |

| Устройство для воспроизведения функций | 1982 |

|

SU1119041A1 |

| Устройство для отображения векторов на экране электронно-лучевой трубки | 1985 |

|

SU1304014A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛЫ ВРЕМЕНИ | 2014 |

|

RU2552605C1 |

| Цифровой интегрирующий вольтметр | 1990 |

|

SU1798711A1 |

| Устройство управления | 1984 |

|

SU1229721A1 |

Изобретение относится к гибридной вычислительной технике и может быть использовано в аналого-цифровых вычислительных системах и устройствах автоматики для длительного интегрирования аналогового сигнала. Цель изобретения - повьшение точности интегрирования. Устройство содержит блок 1 интегрирования, блок 2 управления, первый 3 и второй 20 счетчики, первьй 4, второй 5 и третий 19 элементы И, первый 6, второй 7 и третий 23 элементы НЕ, элемент ИЛИ-НЕ 11, первый 12 и второй 13 элементы И-НЕ, дешифратор 14, первый 15 и второй 16 формирователи сигнала, первый 17 и второй 18 триггеры, мультиплексор 21, цифро-аналоговый преобразователь 22. Устройство позволяет производить непрерьшное интегрирование с высокой точностью и уменьшить в 2 раз диапазон входного напряжения (вблизи нулевого потенциала), в котором погрешность интегрирования велика за счет неустойчивой работы компараторов. 4 ил. «е (Л 2if со о о о 00

| Способы и средства интегрирующего преобразования | |||

| Сб | |||

| Приборы, средства автоматизации и системы уп- | |||

| равления, сер.ТС5 Электроизмерительные приборы, М.: ЦНИИТЭИприбо- ростроения, 1982, вып.2, с | |||

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

| Очистной комбайн | 1984 |

|

SU1168709A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-07—Публикация

1985-07-31—Подача