1

Предлагаемое аналого-дискретное интегрирующее устройство может быть применено в вычислительной технике, в частности в гибридных вычислительных устройствах для длительного и точного интегрирования ироизвольно из.меняющихся аналоговых напряжений.

Известны аналого-цифровые интеграторы, предназначенные для использования в вычислительной технике, которые содержат аналоговый интегратор, компараторы, реверсивный счетчик для накопления интеграла 1.

Суммирование приращений интеграла входного напряжения происходит при достижении выходной величиной аналогового интегратора порогового значения с последующим сбросом аналогового интегратора в нуль. Реализация такого принципа работы приводит к достаточно сложной структурной схеме, так как требует введения в нее специальных узлов; генератора тактов, управляющего счетчика, устройства управления. Кроме того, у этого интегратора довольно большие погрещности изза накопления ошибки дрейфа нуля и потери информации о входной величине за время сброса в нуль аналогового интегратора.

Известны также аналого-дискретные интегрирующие устройства, которые используются для длительного ннтегрирования сигналов, снимаемых с аналоговых датчиков, содержащие аналоговый интегратор, пороговые элементы, преобразователь полярности входного сигнала, аналоговые ключи и счетчик для накопления интеграла 2. Такие устройства имеют ограниченное ирименение, так как обеспечивают возможность интегрирования знакопостоянного аналогового напряжения.

Паиболее близким к изобретению является аналого-дискретный интегратор, на базе которого построено устройство для замера расхода жидкости, содержащий интегратор, вход которого через блок преобразования полярности соединен с входом устройства, а выход - с входами компараторов, выходы которых иодключены к логическому элементу ИЛИ, выход логического элемента ИЛИ соединен с формирователем счетных импульсов, и счетчик для накопления результата интегрирования 3.

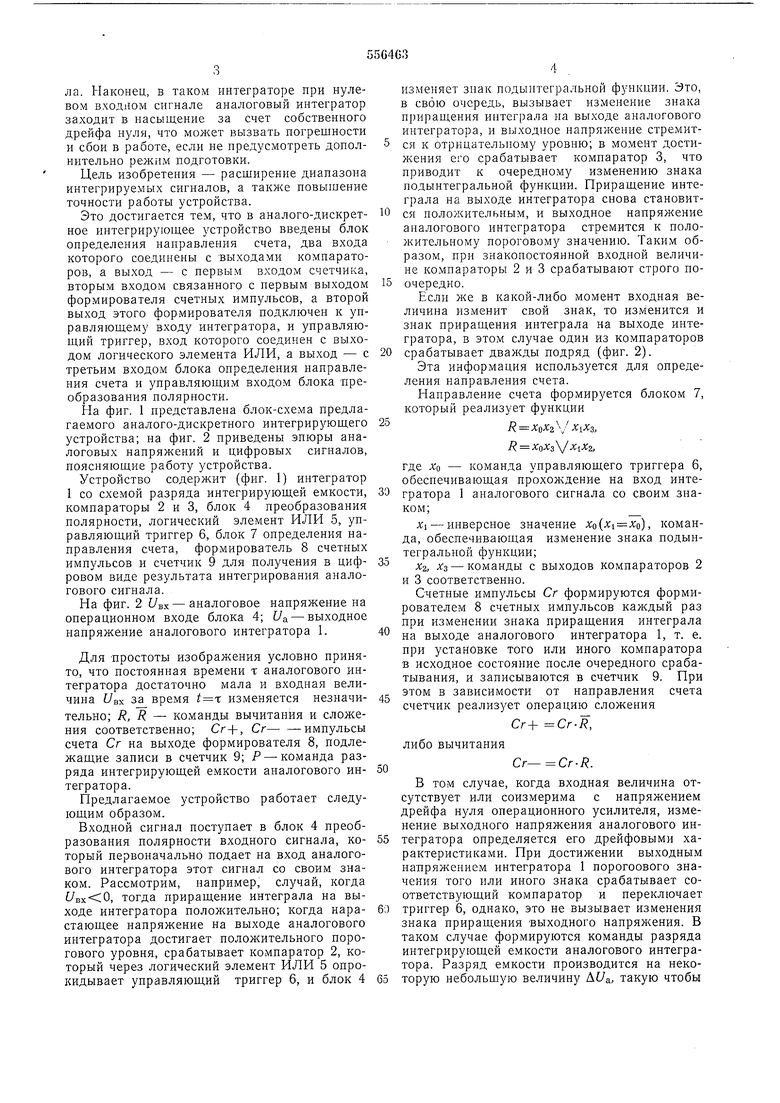

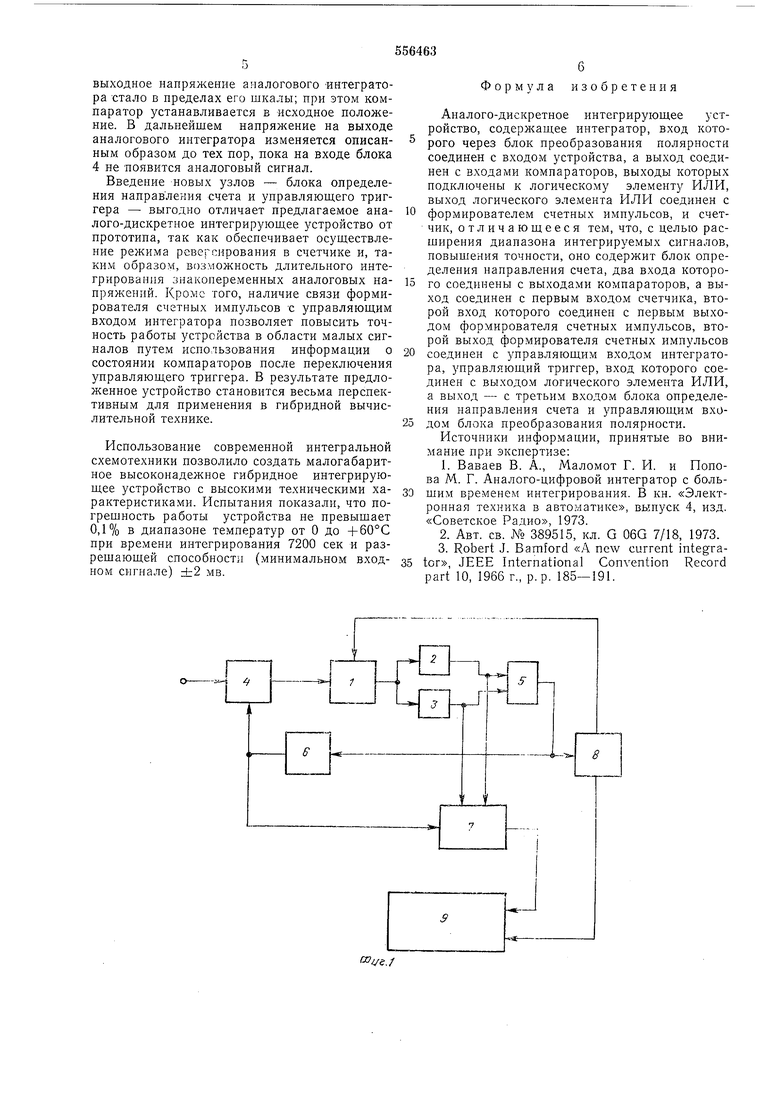

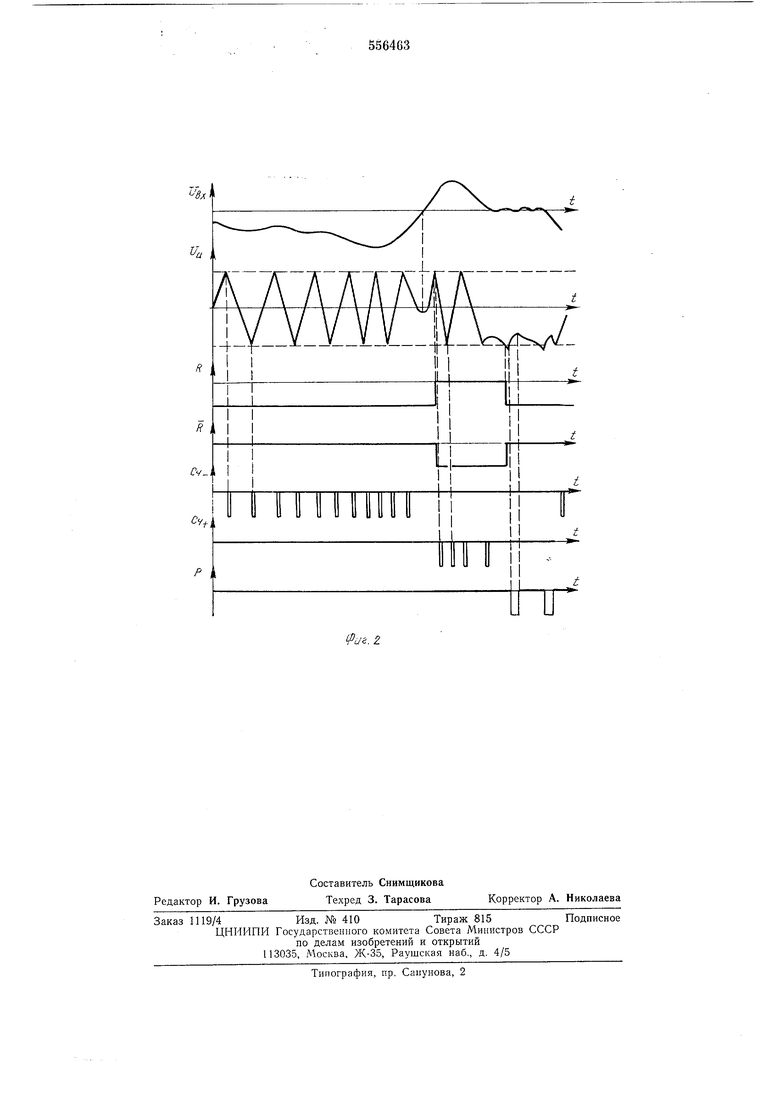

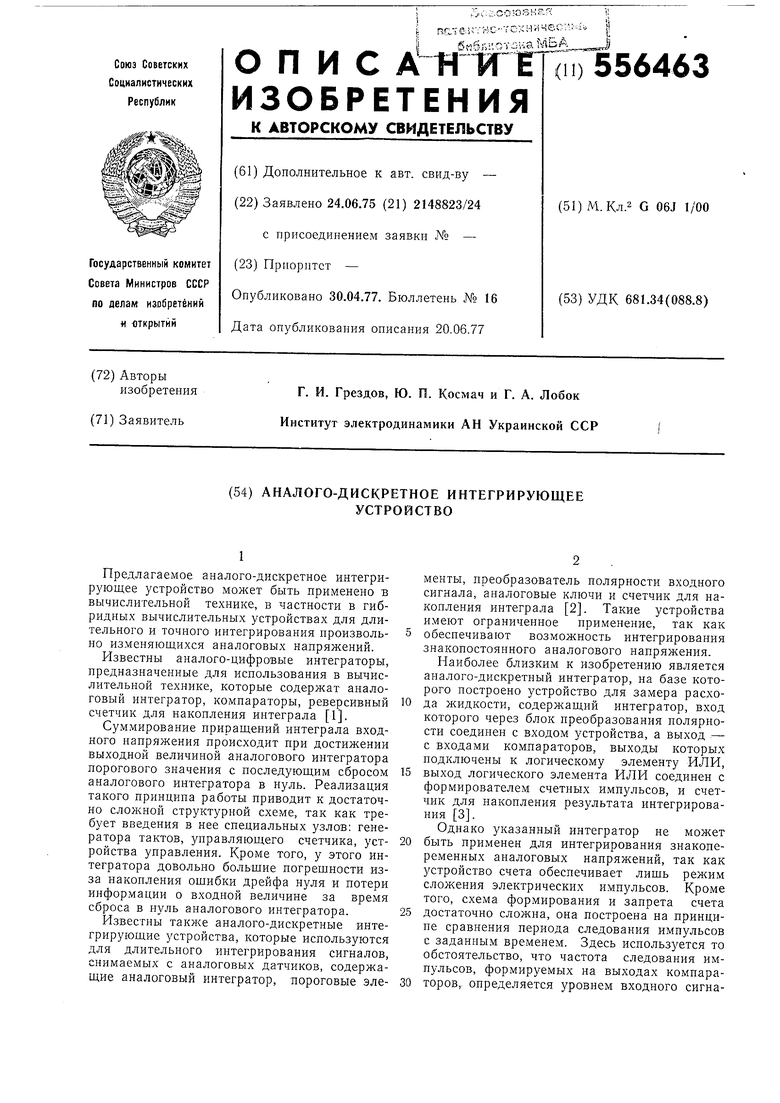

Однако указанный интегратор не может быть применен для интегрирования знакопеременных аналоговых напряжений, так как Зстройство счета обеспечивает лишь сложения электрических импульсов. Кроме того, схема формирования и запрета счета достаточно сложна, она построена на принципе сравнения периода следования импульсов с заданным временем. Здесь использзется то обстоятельство, что частота следования импульсов, формируемых на выходах компараторов, определяется уровнем входного сигнала. Наконец, в таком интеграторе при нулевом входном сигнале аналоговый интегратор заходит в насыщение за счет собственного дрейфа нуля, что вызвать погрешности и сбои в работе, если ие иредусмотреть доиолнительно режим подготовки. Цель изобретения - расширение диапазона интегрируемых сигналов, а также иовышение точности работы устройства. Это достигается тем, что в аналого-дискретное интегрирующее устройство введены блок определения направления счета, два входа которого соединены с выходами компараторов, а выход - с иервым входом счетчика, вторым входом связанного с первым выходом формирователя счетных импульсов, а второй выход этого формирователя подключен к управляющему входу интегратора, и управляющий триггер, вход которого соединен с выходом логического элемента ИЛИ, а выход - с третьим входом блока определения направления счета и управляющим входом блока преобразования полярности. На фиг. 1 иредставлена блок-схема предлагаемого аналого-дискретного интегрирующего устройства; иа фиг. 2 приведены эпюры аналоговых напряжений и цифровых сигналов, поясняющие работу устройства. Устройство содержит (фиг. 1) интегратор 1 со схемой разряда интегрирующей емкости, компараторы 2 и 3, блок 4 преобразования полярности, логический элемент ИЛИ 5, управляющий триггер 6, блок 7 определения направления счета, формирователь 8 счетных импульсов и счетчик 9 для получения в цифровом виде результата интегрирования аналогового сигнала. На фиг. 2 УВХ-аналоговое напряжение на операционном входе блока 4; /а - выходное напряжение аналогового интегратора 1. Для простоты изображения условно принято, что постоянная времени т аналогового интегратора достаточно мала и входная величина t/Bx за время изменяется незначительно; R, R - команды вычитания и сложения соответственно; Сг+, Сг- -импульсы счета Сг на выходе формирователя 8, подлежащие записи в счетчик 9; Р - команда разряда интегрирующей емкости аналогового интегратора. Предлагаемое устройство работает следующим образом. Входиой сигнал поступает в блок 4 преобразования полярности входного сигнала, который первоначально подает на вход аналогового интегратора этот сигнал со своим знаком. Рассмотрим, например, случай, когда , тогда приращение интеграла на выходе интегратора положительно; когда нарастающее напряжение на выходе аналогового интегратора достигает полол ительного порогового уровня, срабатывает компаратор 2, который через логический элемент ИЛИ 5 опрокидывает управляющий триггер 6, и блок 4 изменяет знак подынтегральной функции. Это, в свою очередь, вызывает изменение знака приращения интеграла иа выходе аналогового интегратора, и выходное иапряжение стремится к отрицательному уровню; в момент достижения его срабатывает компаратор 3, что приводит к очередпому изменеиию знака подынтегральной функции. Приращение интеграла на выходе интегратора снова становится положительным, и выходное напрял ение аналогового интегратора стремится к положительному пороговому значению. Таким образом, при знакопостоянной входной величине компараторы 2 и 3 срабатывают строго поочередно. Если в какой-либо момент входная величина изменит свой зиак, то изменится и знак приращения иитеграла на выходе интегратора, в этом случае один из комиараторов срабатывает двалады подряд (фиг. 2). Эта информация используется для определения направления счета. Направление счета формируется блоком 7, который реализует функции R,X{)Xz у , R ХоХз /XiX2, где хо - команда уиравляющего триггера 6, обесиечивающая прохол дение на вход интегратора 1 аналогового сигнала со своим знаком;Xi - инверсное значение Xo(), команда, обеспечивающая изменение знака подынтегральной функции; Х2, Хз - команды с выходов компараторов 2 и 3 соответственно. Счетные импульсы Сг формируются формирователем 8 счетных импульсов каждый раз при изменении знака приращения иитеграла на выходе аналогового интегратора 1, т. е. при установке того или иного компаратора в исходное состояние после очередного срабатывания, и записываются в счетчик 9. При этом в зависимости от направления счета счетчик реализует операцию сложения Сг+ Cr-R, либо вычитания . В том случае, когда входная величина отсутствует или соизмерима с напряжением дрейфа нуля операционного усилителя, изменение выходного напряжения аналогового интегратора определяется его дрейфовыми характеристиками. При достижении выходным иапрял :ением интегратора 1 порогоового значения того или ииого знака срабатывает соответствующий компаратор и переключает триггер 6, однако, это не вызывает изменения знака приращения выходного напрял :ения. В таком случае формируются команды разряда интегрирующей емкости аналогового интегратора. Разряд емкости производится на некоторую небольшую величину ALa, такую чтобы

выходное напряжение аналогового интегратора стало в пределах его шкалы; при этом компаратор устанавливается в исходное положение. В дальнейшем напряжение на выходе аналогового интегратора изменяется описанным образом до тех пор, пока на входе блока 4 не появится аналоговый сигнал.

Введение новых узлов - блока определения направления счета и управляюш,его триггера - выгодно отличает предлагаемое аналого-дискретное интегрируюш,ее устройство от прототипа, так как обеспечивает осуществление режима реверсирования в счетчике и, таким образом, возможность длительного интегрирования знакопере.менных аналоговых напряжений. Кроме того, наличие связи формирователя счетных импульсов с управляюш,им входом интегратора позволяет повысить точность работы устройства в области малых сигналов путем использования информации о состоянии компараторов после переключения управляюш.его триггера. В результате предложенное устройство становится весьма перспективным для применения в гибридной вычислительной технике.

Использование современной интегральной схемотехники позволило создать малогабаритное высоконадежное гибридное интегрируюш,ее устройство с высокими техническими характеристиками. Испытания показали, что погрешность работы устройства не превышает 0,1% в диапазоне температур от О до +60°С при времени интегрирования 7200 сек и разрешаюш;ей способности (минимальном входном сигнале) ±2 мв.

6 Формула изобретения

Аналого-дискретное интегрирующее устройство, содержащее интегратор, вход которого через блок преобразования полярности соединен с входом устройства, а выход соединен с входами компараторов, выходы которых подключены к логическому элементу ИЛИ, выход логического элемента ИЛИ соединен с формирователем счетных импульсов, и счетчик, отличающееся тем, что, с целью расширения диапазона интегрируемых сигналов, повышения точности, оно содержит блок определения направления счета, два входа которого соединены с выходами компараторов, а выход соединен с первым входом счетчика, второй вход которого соединен с первым выходом формирователя счетных импульсов, второй выход формирователя счетных импульсов соединен с управляющим входом интегратора, управляющий триггер, вход которого соединен с выходом логического элемента ИЛИ, а выход - с третьим входом блока определения нанравления счета и управляющим входом блока преобразования полярности.

Источники информации, принятые во внимание ири экснертизе:

1.Ваваев В. А., Маломот Г. И. и Попова М. Г. Аналого-цифровой интегратор с большим временем интегрирования. В кн. «Электронная техника в автоматике, вьшуск 4, изд. «Советское Радио, 1973.

2.Авт. св. № 389515, кл. G 06G 7/18, 1973.

3.Robert J. Bamford «А new current integrator, JEEE International Convention Record part 10, 1966 г., p.p. 185-191.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-дискретное интегрирующее устройство | 1979 |

|

SU875407A1 |

| Аналого-дискретное интегрирующее устройство | 1986 |

|

SU1432563A2 |

| Аналого-дискретное интегрирующее устройство | 1986 |

|

SU1377875A1 |

| Аналого-дискретное интегрирующее устройство | 1985 |

|

SU1327128A1 |

| Гибридное интегрирующее устройство | 1985 |

|

SU1316008A1 |

| Гибридное интегрирующее устройство | 1985 |

|

SU1418768A1 |

| Гибридное интегрирующее устройство | 1984 |

|

SU1168972A1 |

| Аналого-цифровой интегратор | 1979 |

|

SU842868A1 |

| Аналого-цифровой фильтр | 1980 |

|

SU873387A1 |

| Дискретно-аналоговый интегратор | 1986 |

|

SU1372337A1 |

Р

Авторы

Даты

1977-04-30—Публикация

1975-06-24—Подача