Изобретение относится к вычислительной, преобразовательной и испытательной технике и может быть нспользовано при исследовании, проектироваиии и наладке управляемых вентильных преоб.разователей, в частности, для замены натурного эксперимента моделирования при проектировании однофазного мостового тиристорного преобразователя.

Известно устройство для моделирования тиристорного преобразователя, содержащее модель тиристорного преобразователя, состоящую из входного операционного усилителя, первого инвертора с ограничителем в цепи обратной связи, интегратора, функционального преобразователя, источника смещающего напряжения. Модель тиристорного преобразователя представляет собой следящую релейную систему, генерирующую пилообразное напряжение и преобразующую его с помощью функционального преобразователя в отрезки синусоиды. Кроме этого, устройство содержит формирователь выходного напряжения, включающий первый дополнительный инвертор, сумматор, выходной операционный усилитель, вторбй дополнитель- ,

ный инвертор с ограничителем в.цепи обратной связи, источник смещающего н&пряжения, датчик тока нагрузки. При этом выход функционального преобразователя через разделительные элементы (диоды) подключен, соответственно, к входу первого дополнительного инвертора и первому входу сумматора, второй и третий

10 входы которого подк.гаочены к источнику смещающего напряжения и через второй дополнительный инвертор - к датчику тока нагрузки, выходы первого дополнительного инвертора и

15 сумматора соединены с входом выходного операционного усилителя.

Это устройство моделирует напряжение на выходе тиристорного преобразователя в режимах прерывистого

20 и непрерывного тока, не моделируя при этом сам ток 1.

Однако данное устройство недостаточно точно отражает токи и напряжения моделируемых преобразовате25лей, а также режимы их работы.

Кроме того, отрезки синусоиды, имитирующие напряжения фаз, формируют с помощью функциональных преобразователей, которые не относятся к точным решающим блокам АВТ.

Наиболее близким по технической сущности к предлагаемому техническому решению является устройство для моделирования вентильного преобразователя, содержащее блок формирования входной ЭДС, блок формирования коммутационной ЭДС, блок формирования импульсов управления, компаратор, нуль-орган, сумматор, интегратор, инвертор, сумматор-интегратор, блбк формирования напряжения нагрузки, блоки переключателе источник трехфазного напряжения, выходы которого подключены к соответствующим входам блока формирования импульсов управления и первым трем входам блока формирования входной ЭДС и блока формирования коммутационной ЭДС, блок управления режимом работы интеграторов и переключателей, первый вход которого под клкгчен к выходу блока формирования импульсов управления и к четвертым входам блока формирования входйой ЭДС и блока формирования коммутационной ЭДС, второй вход подключен к выходу Компаратора, первый выход соединен с первыми управляющими входами блоков перекл очателёй, второй выход соединен с вторьми управляющими входс1ми блоков переключателей и входом управления режимом работы сумматора-интегратора, третий выход подключен к входу управления режимо работы интегратора, выход которого подключен к входу блока формировани напряжения нагрузки и через- инверто подключен к входу нуль-органа, выход которого подключен к третьему входу блока управления режимом рабо ты интеграторов и переключателей, выход инвертора через первый блок переключателей подключен к первому входу сумматора, второй вход которо через второй блок переключателей подключен к выходу блока формирования входной ЭДС, третий вход сумматора подключен к выходу блока формирования напряжения нагрузки, выход инвертора подключен к первому входу компаратора, второй входкоторого подключен к выходу сумматора-интегратора, выход которого соединен с его первым входом, второй вход сумматора-интегратора подключен к выходу сумматора и через третий блок переключателей соединен с входом

,интегратора, третий вход сумматораинтегратора подключен к выходу инвертора, а четвертый его вход соединен с выходом блока формирования коммутационной ЭДС.

В известном устройстве моделирую напряжение входной ЭДС,выходной ток и напряжение на нагрузке преобразователя. Отсутствуют решающие блоки для моделирования тока, потребляемого преобразователем 2.

Однако в известном устройстве невозможно определять энергетически характеристики преобразователя, что сужает область его применения.

Кроме того, в известном устройстве не предусмотрено такое изменение структуры модели, при котором моделируется одновременное, открытие пар тиристо эов, включенных параллельно индуктивности питающей сети или нагрузке в мостовом однофазном преобразователе. Это ,не позволяет моделировать режим работы однофазного мостового преобразователя при поочередном управлении тиристорами, что также сужает область его применения.

Недостаткрм известного устройства является также то, что переход от одной структуры модеЛн к другой осуществляется путем одновременной подачи сигналов управления на включаемый и выключаемый интеграторы, что недостаточно точно отражает логику функционирования преобразователя и при работе устройства в реальном масштабе времени приводит к его неустойчивости.

Кроме ТОГС1, точность устройства понижается за счет того, что момент наступления режима прерывистого тока нагрузки определяется в аналоговой части прототипа моментом сравнения аналоговых величин на компа-раторе, который имеет больший разброс момента срабатывания, чем логические элементы.

Цель изобретения - повышение точности и быстродействия устройства.

Поставленная цель достигается тем,что в устройство для моделирования вентильного преобразователя, содержащее источник фазового напряжения, выходы которого соединены соответственно с первыми группами входов блока формирования сигналов управления и блока формирования входной ЭДС, блок формирования напряжения нагрузки, нуль-орган и компаратор, выход которого подключен к первому входу блока управления, второй вход которого соединен с выходом блока формирования сигналов управления, введены блок моделирования контуров тока и блок задания режима, первая группа выходов которого подключена к второй группе входов блока формирования сигналов управления, первая и вторая группа выходов которого соединены соответственно с входами блока задания режима и с первой группой входов блока управления, вторая группа входс5в которого подключена к второй группе выходов блока задания режима первый и второй выходы которого соединены соответственно с первьми входами блока моделирования контуров тока и нуль-органа, выход которого подключен к третьему входу блока управления, первая группа выходов которого соединена с второй группой входов блока формирования входной ЭДС, выход которого подключен к первому входу блока формирования напряжения нагрузки и второму входу блока моделирования контуров тока, третий вход которого соединен с первым выходом источника фазного напряжения, первый выход блока моделирования контуров тока подключен к первому входу компаратора, -второй вьаход блока моделирования контуров тока соединен с вторыми входами компаратора и нуль-органа, выход .блока управления подключен к второму входу блока формирования напряжения нагрузки и к четвертому входу блока моделирования контуров тока, группа управляющих входов которого соединена соответственно с второй.и. третьей группой выходов блока управления, четвертый вход которого подключен к второму выходу источника фазного напряжения,

Блок моделирования контуров тока содержит сумматоры, ключи, элементы НЕ, интеграторы и сумматоринтегратор, первый вход которого является третьим входом блока , выход сумматора-интегратора соединен с его вторым входом и через цепочку из последовательно соединенных первого ключа и первого элемента НЕ подключен к первому входу первого сумматора, выход которого является первым выходс№1 блока, вторь входом которого является первый вход второго сумматора, выход которого соединен с первым входом первого интегратора, выход которого подключен к первому входу второго интегратора и к входам второго ключа и второго элемента НЕ, выход которого соединен с вторым входом второго сумматора и с входом третьего ключа, выходы второго и третьего ключей подключены соответственно к входам третьего сумматора, выход которого соединен с третьим входом сумматора-интегратора, выход которого через четвертый ключ подключен к второму входу первого сумматора, выход четвертого сумматора соединен с BTOpbW входом второго интегратора, выход которого через цепочку последовательно соединенных третьего элемента НЕ .и пятого ключа подключен к второму входу первого интегратора, вход четвертого элемен,та НЕ является первым входом блока, а выход четвертого элемента НЕ непосредственно соединен с третьим входом второго сумматора и через ,пятый элемент НЕ подключен к первому

входу четвертого сумматора, вход которого соединен с выходом третьего элемента НЕ, являющимся вторьни выходом блока, группой управляющих входов которого являются соответственно управляющие входы интеграторов и ключей.

При этом блок формирования сигналов управления содержит сумматоры, компараторы, элементы 2И, ИЛИ и

0 2-2И-ИЛИ, элементы дифференцирования и интегратор, выход которого соединен с первыми входами первого и второго компараторов и первого сумматора, выход которого подключен к

5 первым входам третьего и четвертого компараторов, выход второго сумматора соединен с входом пятого компаратора, выход которого является выходом блока, первой, группой входов которого являются соответственно

0 входы второго сумматора, шестого и седьмого компараторов и интегратора, второй группой входов блока являются вторые входы первого , второго, третьего и четвертого компараторов,

5 выходы шестого и седьмого компараторов соединены соответственно с первьами входами элементов 2И и с первым и вторым входами элемента 2-2И-ИЛИ, третий и четвертый входы

0 которого подключены соответственно к выходам первого и четвертого компараторов, а выход элемента 2-2И-ИЛИ связан с входом первого элемента дифференцирования, выходы второго

5 и третьего компараторов соединены соответственно с вторыми входами элементов 2Й, вькоды которых подключены к входам элемента ИЛИ, выход которого соединен с входом второго

0 элемента дифференцирования, выходы элементов дифференцирования и элементов 2И являются соответственно первой и второй группами выходов блока.

5

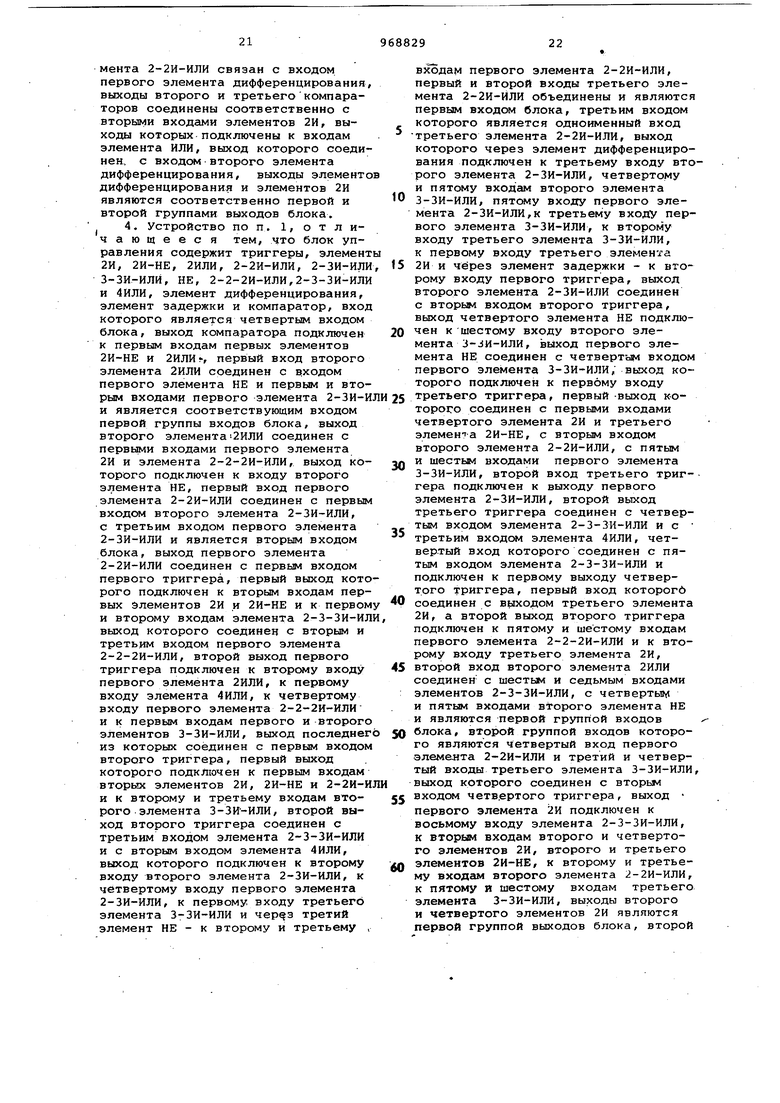

Блок управления содержит триггеры, элементы 2И, 2И-НЕ, 2ИЛИ, 2-2И-ИЛИ, 2-ЗИ-ИЛИ, 3-ЗИ-ИЛИ, НЕ , 2-2-2И-ИЛИ, 2-3-ЗИ-ИЛИ и 4ИЛИ,элемент дифференцирования, элемент за0держки и компаратор, вход которого является четвертьм входом блока, выход компаратора подключен к первьм входам первых элементов 2И-НЕ и 2ИЛИ, первый вход второго элемента

5 2ИЛИ соединен с входом первого элемента НЕ, первым и вторым входами первого элемента 2-ЗИ-ИЛИ и является соответств.ующим входом первой группы входов блока, выход второго элемен0та 2ИЛИ соединен с первыми входами первого элемента 2И и элемента 2-2-2И-ИЛИ, выход которого подключен к входу второго элемента НЕ, первый вход первого элемента 2-2И-ИЛИ сое5динен с первьм входом второго элемента 2-ЗИ-ИЛИ, с третьим входом первого элемента 2-ЗИ-ИЛИ и являетс вторые входом блока,, выход первого элемента 2-2И-ИЛИ соединен с первым вводом первого триггера, первый выход которого подключен к вторым входам первых элементов 2И и 2И-НЕ и к первому и вторсмлу входам элемен та 2-3-ЗИ-ИЛИ, выход которого соеди нен с вторым и третьим входом первого элемента 2-2-2И-ИЛИ, второй выход первого триггера подключен к второму входу первого элемента 2ИЛИ к первому входу элемента 4ИЛИ, к четвертому входу первого элемента 2-2-2И-ИЛИ и к первым входам первог и второго элементов 3-ЗИ-ИЛИ, выход последнего иэ которых соединен с первым входом второго триггера/ первый вьоход которого подключен к первым входамвторых элементов 2И 2И-НЕ и 2-2И-ИЛИ и к второму и третьему /входам второго элемента 3-ЗИ-ИЛИ, второй выход второго триг гера соединен с третьим входом элемента 2-3-ЗИ-ИЛИ и с вторым входом элемента 4ИЛИ, выход которого подкл чён к второму входу второго элемент 2-ЗИ-ИЛИ, к четвертому входу первог элемента 2-ЗИ-ИЛИ, к первому входу третьего элемента 3-ЗИ-ИЛИ, и через третий элемент НЕ - к второму и третьему входам первого элемента 2-2И-ИЛИ, первый и второй входы третьего элемента 2-2И-ИЛИ объединены и являются первым входом блока третьим входом которого является одноименный вход третьего элемента 2-2И-ИЛИ, выход которого через элемент дифференцирования подключен к третьему входу второго элемента .2-ЗИ-ИЛИ, четвертому и пятсяиу входам второго элемента 3-ЗИ-ИЛИ, пятому входу первого элемента 2-ЗИ-И третьему входу первого элемента 3-ЗИ-ИЛИ, к второму входу третьего элемента 3-ЗИ-ИЛИ, к первому входу третьего элемента 2И и ,череэ элемент задержки - к второму входу первого триггера, выхой второго элемента 2-ЗИ-ИЛИ соединен с вторым входом второго триггера, выход четвертого элемента НЕ подключен к шестому входу вто рого элемента 3-ЗИ-ИЛИ, выход перво элемента НЕ соединен с четвертым входом первого элемента 3-ЗИ-ИЛИ, выход которого подключен к первому входу третьего триггера, первый выход которого соединен с первыми вхо дами четвертого элемента 2И и треть го элемента 2И-НЕ, с вторым входом второго элемента 2-2И-ИЛИ, с пя тым и шестым входами первого элемента 3-ЗИ-ИЛИ, второй вход третьего триггера подключен к выходу первого элемента 2-ЗИ-ИЛИ, .второй выход третьего триггера соединен с четвертым входом элемента 2-3-ЗИ-ИЛИ и с третьим входом элемента 4ИЛИ, четвертый вход которого соединен с пятым входом элемента 2-3-ЗИ-ИЛИ и подключен к первсму выходу четвертого триггера, первый вход которого соединен с выходом третьего элемента 2И, а второй выход второго триггера подключен к пятому и шестому входам первого элемента 2-2-2И-И,ЛИ и к второму входу третьего элемента 2И, второй вход второго элемента 2ИЛИ соединен с шестым и седьмым входами элементов 2-3-ЗИ-ИЛИ, с четвертым и пятым входамк втор/)го элемента НЕ и является первой группой входов блока, второй группой входов которого являются четвертый вход первого элемента 2-2И-ИЛИ и третий и четвертый входы , третьего элемента 3-ЗИ-ИЛИ, выход которого соединен с вторым входом четвертого триггера, выход первого элемента 2И подключен к восьмому входу элемента 2-3-ЗИ-ИЛИ, к вторым входам второго и четвертого элементов 2И, второго и третьего элементов 2И-НЕ, к второму и третьему входам второго элемента 2-2И-ИЛИ, к пятсму и шестому входам третьего элемента 3-ЗИ-ИЛИ, выходы второго и четвертого элементов 2И являются первой группой выходов блока, второй группой выходов которого являются выходы элементов 2-3-ЗИ-ИЛИ, 2-2-2И-ИЛИ и второго элемента 2-2И-ИЛИ, выходы первых элементов 2И-НЕ, 2ИЛИ, второ(Го элемента НЕ и второго и третьего элементов 2И-НЕ являются третьей группой выходов блока. На фиг.1 приведена функциональная схема устройства; на фиг.2 - то же, . блока моделирования контуров тока; на фиг.З - то же, блока формирования сигналов управления; на фиг.4 то же,.блока управления; на фиг.5 то же, блока задания режима.f Устройство, (фиг.1) содержит источник 1 фазного напряжения, блок 2 формирования входной ЭДС, блок 3 моделирования контуров Тока, блок 4 формирования напряжения нагрузки, компаратор 5, нуль-орган 6, блок 7 формирования сигналов управления, блок 8 управления, блок 9 задания режима. При этом выходы источника 1 фазного напряжения соединены соответственно с первой группой входов блока 7 формирования сигналов управления и блока 2 формирования входной ЭДС. Второй вход блока 8 управления соединен с выходом блока 7 формирования сигналов управления. Первая группа выходок блока 9 задания режима подключена к второй группе входов блока 7 формирования сигналов управления, первая и вторая группы выходов которого соединены соответственно с входами блока 9 задания режима и с первой группой входов блока 8 управления, вторая группа входов которого подключена к второй группе выходов блока 9 задания режима, первый и второй выходы которого соединены соответственно с первыми входами блока 3 моделирования контуров тока и нуль-органа 6. Выход нуль-органа 6 подключен к третьему входу блока В управления, первая группа выходов которого соединена с второй группой входов блока 2 формирования входной ЭДС, выход которого подключен к первому входу блока 4 формирования напряжения нагрузки и второму входу блока 3 моделирования контуров тока, третий вход которого соединен с первым выходом источника 1 фазного напряжения.

Первый выход блока 3 моделирования контуров тока подключен к первом входу компаратора 5, Второй выход блока 3 моделирования контуров тока соединен с вторыми входами компараТора 5 и нуль-органа 6. Выход блока 8 управления подключен к второму входу блока 4 формирования напряжени нагрузки и к четвертому входу блока 3 моделирования контуров тока, первая и вторая группы управляющих входов которого соединены соответственно с второй и третьей группами выходов блока 8 управления, четвертый вход которого подключен к второму выходу источника 1 фазного напряже1НИЯ.

Источник 1 фазного напряжения генерирует синусоидальное напряжение, частота и амплитуда которого может изменяться вручную, и предназначен для моделирования напряжения фазы питания преобразователя.

Блок 2 формирования входной ЭДС содержит сумматор и управляемые ключи. На первый и второй входы сумматора через ключи подают сигналы соответственно с прямого и инверсного выходов источника 1. Коэффициенты передачи сумматора по обоим входа м равны единице.

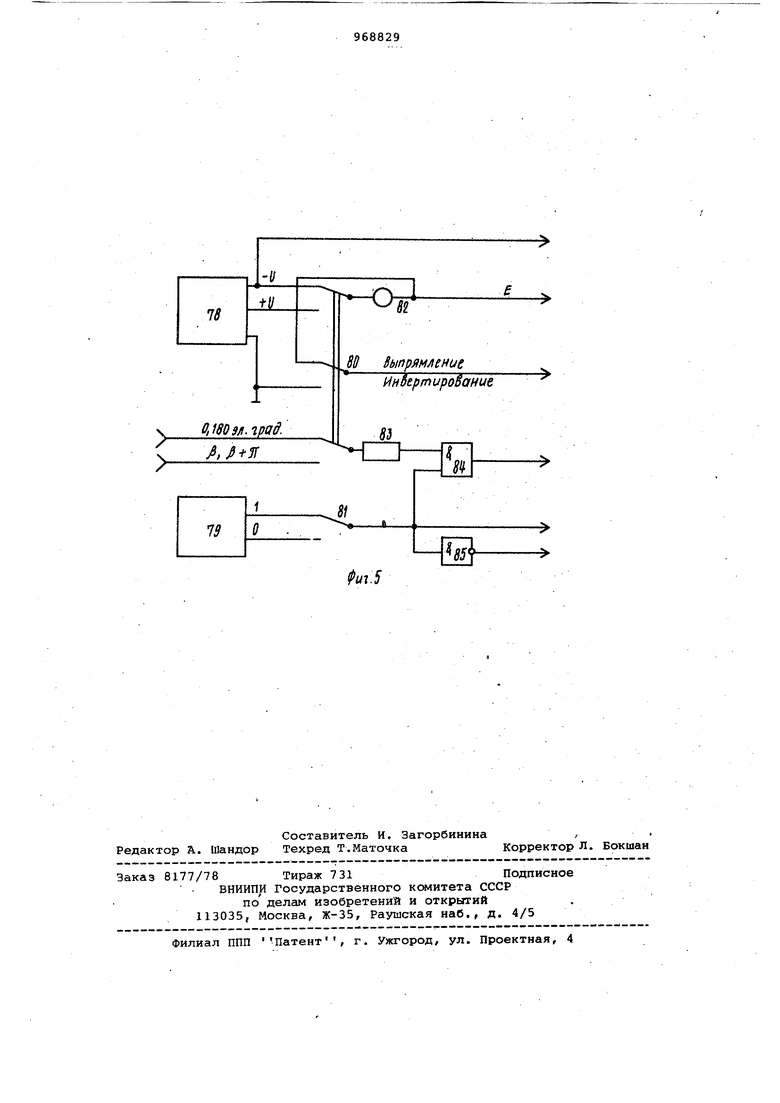

Блок 3 моделирования контуров тока (фиг.2) содержитинтеграторы 10 и 11, сумматор-интегратор 12, сумматоры 13 - 16, ключи 17 - 21, а также инверторы 22 - 26. При этом первый вход сумматора-интегратора 12 является третьим входом блока 3, выход сумматора-интегратора 12 соединен с его вторым входом и через цепочку из последовательно-соединенных первого ключа 17 и первого инвертора 22 подключен к первому входу первого сумматора 13, выход которого является первым выходом блока 3. Вторым входом блока 3 является первый вход второго сумматора 16, выход которого соединен с первым входом первого интегратора 10, выход которого подключен к первому входу второго интегратора 11 и к входам второго ключа 20 и второго инвертора 26, выход которого соединен с вторым входом второго сумматора 16 и с входом третьего ключа 19.

Выходы второго и третьего ключей (20, 19) подключены соответственно к входам третьего сумматора 15, выход которого соединен с третьим входом сумматора-интегратора 12, тыход которого через четвертый ключ 18 подключен к второму входу первог сумматора 13. Выход четвертого сумматора 14 соединен с вторым входом второго интегратора 11, выход которого через цепочку последовательно соединенных третьего инвертора 25 и пятого ключа 21 подключен к второму входу первого интегратора 10.

Вход четвертого элемента инвертора 23 является первым входом блока 3, а выход четвертого инвертора 23 непосредственно соединен с третьим входслч второго сумматора 16 и через пятый .инвертор 24 подключен к первому входу четвертого сумматора 14, вход которого соединен с выходом третьего инвертора 25, являющимся вторым выходом блока 3, первой и второй группой управляющих входов которого являются соответственно управляющие входы интеграторов и ключей. Управляющие входы показаны на фиг.2 стрелками, подходящими снизу к управляемым решающим блокам.

Блок 3 предназначен для моделирования тока в нагрузке da/ в цепи фазы (1ф), тока коммутации (i) путем сшивки решений соответствующих дифференциальных уравнений.

Блок 4 формирования напряжения нагрузки, содержит усилитель и управляемый ключ.

Компаратор 5 определяет момент окончания интервалов коммутации в режиме симметричного управления тиристорами при сравнении -тока коммутации с током в нагрузке.

Нуль-орган 6 определяет конец интервалов коммутации в режиме поочередного управления тиристорами моментом достижения током коммутации величины равной нулю.

Блок 7 формирования сигналов управления (фиг.З) содержит два диода 27 и 28, два сумматора 29 и 30, интегратор 31, компараторы 32 - 38, элемент 2-2И-ИЛИ 39, два элемента 2И 40 и 41, элемент ИЛИ 42, элементы 43 и 44 дифференцирования, блоки 15 и 46 постоянных коэффициентов.

Выход интегратора 31 соединен с первыми входами первого и второго компараторов 35 и 37 и первого сум-. матог-а 30, выход которого подключен к .первым входам третьего и четвертого компараторов 36 и 38. Выход второго сумматора 29 соединен с входом пятого компаратора 32, выход которого является выходом блока 7, первой группой входов которого являются соответственно входы второго сумматора 29, шестого 33 и седьмого 34 компараторов и интегратора 31.

Второй группой входов блока 7 являются вторые входы первого 35, второго 37, третьего 36 и четвертого 38 компараторов. Выходы шестого 33 и седьмого 34 компараторов (Соединены соответственно с первыми входами элементов 2И 40 и 41 и с первым и вторым входами элемента 2-2И-ИЛИ 39 третий и четвертый входы которого подключены соответственно к выходам первого 35 и четвертого 36 компараторов, а выход элемента 2-2И-ИЛИ 39 связан с входом первого элемента 43 дифференцирования. Выходы второго 37 и третьего 38 компараторов соединены соответственно с вторыми входами элементов 2И 40 и 41, выходы которых подключены к входам элемента ИЛИ 42, выход которого соединен с входом второго элемента 44 дифференцирования. Выходы элементов 43 и 44 дифференцирования и элементов 2И 40 и 41 являются соответственно первой и второй группами выходов блока 7.

Блок 7 моделирует систему импульсно-фазового управления тиристорами, построенную по вертикальному принципу. При этом на компараторах 35 и 36 постоянное напряжение, выставляемое блоком 45 постоянного коэффициента и имитирующее напряжение управления У2, сравнивается с нарастающими напряжениями, сдвинутыми на 180 эл. град и получаемыми на выходе интегратора 31 и сумматора 30. Эти же нарастающие напряжения сравниваются на компараторах 37 и 38 с постоянным напряжением, задаваемым блоком 46 и имитирующим напря жение управления У1. Фронты импульсов на выходах компараторов 37 и 38, соответствуют углам управления oL и 0 + К , которые управляют работой пар тиристоров при симметричном управлении , а фронты импульсов на выходах компараторов 35 и 36 соответ-г ствуют углам Управления jb и (Ъ + ТС п служат для управления тиристорами (совместно с предьщущими углами) при поочередном управлении.

Компараторы 33 и 34 служат для имитации условий соотношения напряжений на тиристоре, при которых возможен запуск. Схема из диодов 27

и 28, сумматора 29 и компаратора 32 вьадает импульсы, фронты которых сооветствуют О и 180 эл.град.

Схема из элемента 39 и 43 формирует короткие импульсы, соответствующие углам и /, ч-К. Аналогично элементы 40, 41, 42 и 44 формируют короткие импульсы, соответствующие углам ot и об +1С . Кроме того, на выходах элементов 40 и 41 формируются сигналы, разрешающие запуститься соответствующим триггерам блока 8.

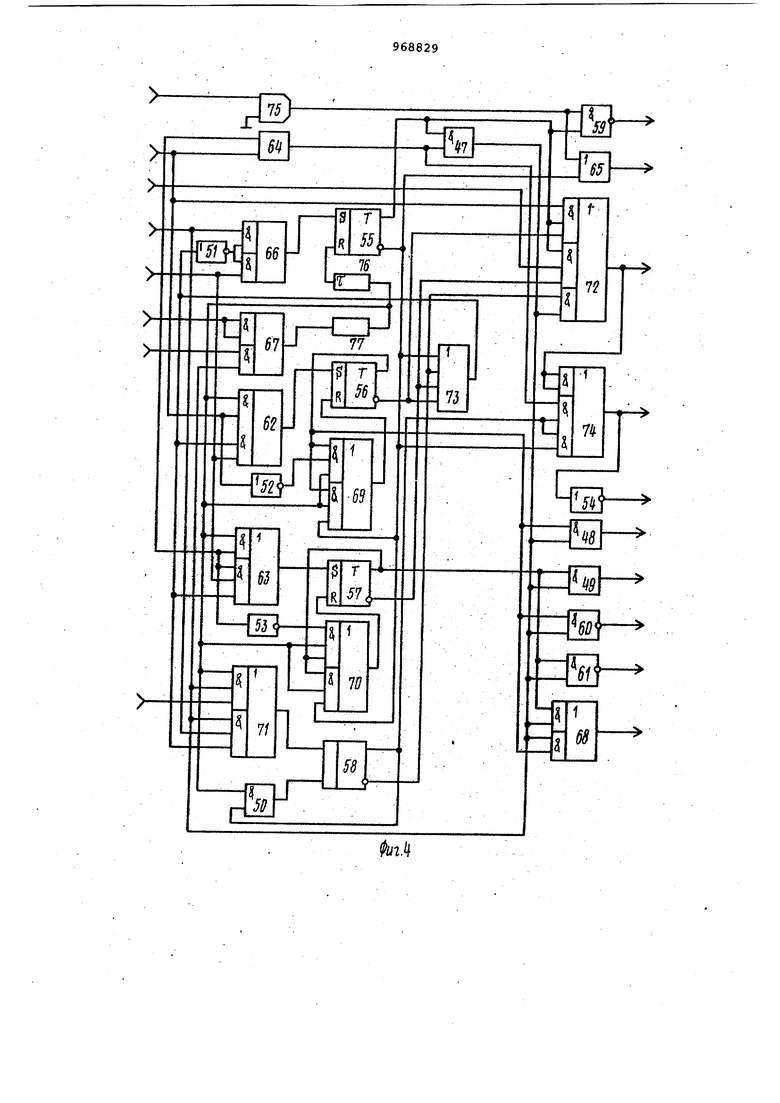

Блок 8 ,управления (фиг.4) содержит элементы 2И 47 - 50, НЕ 51 - 54 RS-триггеры 55 - 58, элементы 2И-НЕ 59 - 61, 2-ЗИ-ИЛИ 62 И 63, 2ИЛИ 64 if 65, 2-2И-ИЛИ 66 - 68, 3-ЗИ-ИЛИ 69 - 71, 2-3-.ЗИ-ИЛИ 72, 4ИЛИ 73, 2-2-2И-ЙЛИ 74, компаратор 75, элемент 76 задержки, элемент 77 дифференцирования.

Вход компаратора 75 является четвертым входом блока 8. Выход компаратора 75 подключен к первым входам первых элементов 2И-НЕ 59 и 2ИЛИ 65..

Первый вход второго элемента 2ИЛИ 64 соединен с входом первого элемента НЕ 52, первым и вторьм входами Первого элемента 2-ЗИ-ИЛИ 62, седьмым входом элемента 2-3-ЗИ-ЙЛИ 72 и является соответствующим входом первой группы входов блока 8.

Выход второго элемента 2ИЛЙ 64 соединен с первыми входами первого элемента 2И 47 и элемента 2-2-2И-ИЛ 74, выход которого подключен к входу второго элемента НЕ 54.

Первый вход первого элемента 2-2И-ИЛИ 66 соединен с первым входом второго элемента 2-ЗИ-ИЛИ 63, с третьим входом первого элемента 2-ЗИ-ИЛИ 62 и является вторым входом блока 8.

Выход .первого элемента 2-2И-ИЛИ соединен с первым входом первого триггера 55, первый выход которого подключен к вторьвл входам первых элементов 2И47 и 2И-НЕ 59 и к первому и второму вхопам элемента 2-3-ЗИ-ИЛИ 72, выход которого соединен с вторым и третьим входсяи элемента 2-2-2И-ИЛИ 74.

Второй выход первого триггера 55 подключен к второму входу первого элемента 2ИЛИ 65, к первому входу элемента 4ИЛИ 73, к четвертому вход элемента 2-2-2И-ИЛИ 74 и к первым вхрдам первого 69 и второго 70 элементов 3-ЗИ-ИЛИ, выход последнег из которых соединен с первым входом второго триггера 57, первый выход которого подключен к первым входам вторых элементов 2И 49, 2И-НЕ 61 и 2-2И-ЙЛИ 68 и к второму и третьему входам второго элемента 3-ЗИ-ИЛИ 70

Второй выход второго триггера 57 соединен с третьим входом элемента 2-3-ЗИ-ИЛИ 72 и с вторым входом эл мента 4ИЛИ 73, выход которого подключен к второму входу второго эле мента 2-ЗИ-ИЛИ 63, к четвертому входу первого элемента 2-ЗИ-ИЛИ 62 к первому входу третьего элемента 3-ЗИ-ИЛИ 71 и через третий элемент НЕ 51 к второму и третьему входам первого элемента .2-2И-ИЛИ 66. Первый и второй входы третьего элемента 2-2И-ИЛЙ 67 объединены и являются первым входом блока 8, третьим входом которого является одноименный вход третьего элемента 2-2И-ИЛИ 67, выход которого чер элемент дифференцирования 77 подключей к третьему входу второго элемента 2-ЗИ-ИЛИ 63, четвертому и пятому входам второго элемента 3-ЗЙ-ИЛИ 70, пятому входу первого элемента 2-ЗИ-ИЛИ 62, к второму и третьему входу первого элемента 3-ЗИ-ИЛИ 69, к второму входу третье го элемента 3-ЗИ-ИЛИ 71, к первому входу третьего элемента 2И 50 и через элемент 76 задержки - к второ му входу первого триггера 55. Выход второго элемента 2-ЗИ-ИЛИ соединен с вторым входом второго триггера 57. Выход четвертого элемента НЕ 53 подключен к шестому входу второго элемента 3-ЗИ-ИЛИ 70 Выход первого элемента НЕ 52 соединен с четвертым входом первого элемента 3-ЗИ-ИЛИ 69, выход которог подключен к первому входу третьего триггера 56, первый выход которого соединен с первыми входами четвертого элемента 2И 48 и третьего элемента 2И-НЕ 60, с вторым входом второго элемента 2-2И-ИЛИ 68, с пятым и шестым входами первого элемента 3-ЗИ-ИЛИ 69, Второй вход третьего триггера 5 подключен к выходу первого элемента 2-ЗИ-ИЛИ 62. Второй выход третьего триггера 56 соединен с четвертым входом элемента 2-3-ЗИ-ИЛИ 72 и с третьим входом элемента 4ИЛИ 73, четвертый вход которого соединен с пятым входом элемента 2-3-ЗИ-ИЛИ 72 и подклю чен к первому выходу четвертого три гера 58, первый вход которого соединен с выходом-третьего элемента 12И 50. Второй выход четвертого триггера 58 подключен к пятому и шестому входам элемента 2-2-2И-ИЛИ 74 и к второму входу третьего элемента 2И 50. ВтЪрой вход второго элемента 2ИЛИ 64 соединен с шестым входом элемента 2-3-ЗИ-ИЛИ 72, с четвертым и.пятым входами второго элемента 2-ЗИ-ИЛИ 63 и являются первой группой входов блока 8. Второй группой входов блока 8 являются четвертый вход первого элемента 2-2И-ИЛИ 66 и третий и четвертый входы третьего элемента 3-ЗИ-ИЛИ 71, выход которого соединен с вторым входом четвертого триггера 58. Выход первого элемента 2И 47 подключен к восьмому входу элемента 2-3-ЗИ-ИЛИ 72, к вторым входам второго 49 и четвертого 48 элементов 2И, второго 61 и третьего .60 элементов 2И-НЕ, к третьему и четвертому входам второго элемента 2-2И-ИЛИ 68, к пятому и шестому входам третьего элемента 3-ЗИ-ИЛИ 71, к четвертому входу третьего элемента 2-2И-ИЛИ 67. Выходы второго 49 и четвертого 48 элементов 2И являются первой группой выходов блока 8, второй группой выходов которого являются выходы элементов 2-3-ЗИ-ИЛИ 72, 2-2-2И-ИЛИ 74 и второго элемента 2-2И-ИЛИ 68, выходы первых элементов 2И-НЕ 59, 2ИЛИ 65, второго- элемента НЕ 54 и второго 61 и третьего 60 элементов 2И-НЕ являются третьей . группой выходов блока 8. Блок 8 управления преобразует при непрерывном токе нагрузки угол управления в сигнал запуска интервала коммутации. В этом случае запуск интервала полной проводимости происходит в момент достижения током коммутации величины, равной значению тока в нагрузке. Импульс, фиксирующий этот момент, поступает с выхода компаратора 5 на второй вход блока 8 И означает конец интервала коммутации и начало интервала проводимости. При прерывистом режиме тока нагрузки интервал полной проводимости запускается непосредственно углом управления, минуя интервал коммутации. Слежение эа прерыванием тока в нагрузке осуществлено в -известном устройстве на нуль-органе. В предлагаемом устройстве для повышения быстродействия и точности это сделано в блоке 8 путем слежения с помощью элемента 73 4ИЛИ за состоянием триггеров, формирующих временные интервалы. При этом, если ни один из триггеров не включен, то это и соответствует прерывистому режиму тока нагрузки. Четыре триггера 55 - 58 блока 8 формируют основные временные интервалы, комбинации которых, в соответствии с логикой процессов, происходящих в преобразователе, поступают с выходов блока 8 на входы управления аналоговых элементов предлагаемого устройства. Начальное состояние триггеров соответствует выключенному состоянию всех тиристоров преобразователя . Блок 9 задания режима (фиг.5) содержит источник 78 постоянного напряжения-, источник 79 логических нуля и единицы, переключатели 80 и 81, блок 82 постоянного коэффициент элемент 83 дифференцирования, элемент 2И 84 и элемент НВ 85. При этом инверсный выход источни ка 78 соединен с третьим выходом блока 9 и первым входом переключате ля 80, первый выход которого соединен через блок 82 постоянного коэффициента с первым выходом блока 9 и с третьим входом переключателя 80 Прямой выход источника 78 соеди нен с вторым входом переключателя 80, второй выход которого соединен с четвертым вькодом блока 9, а четвертый вход - с нулевым выходом источника 78. Пятый и шестой входы переключателя 80 подсоединены соответственно к первому и второму вход блока 9. Третий выход переключателя 80 соединен через элемент 83 дифференцирования с первым входом элемента 84, выход которого соединен с пятым выходом блока 9, а второй вход - с шестым выходом блока 9, а также с выходом переключателя 81, первый вхол которого соединен с выходом логической единицы источника 79, а второй вход - с выходом логического нуля этого источника. Выходы 3,4 и 5,6 блока являются соответственно первой и второй груп пами выхода блока 9, первой группой входов которого являются входы 1 и 2. Блок 9 эадания режима преднаэначен для установки устройства в поло жение, соответствующее моделировани работы преобразователя в режимах выпрямления или инвертирования, сим метричного или поочередного управле ния тиристорами, а также для проведения экспериментов на модели. Для этого блок 9 содержит источник 78 постоянного напряжения с прямым и инверсным выходами для .задания с помощью переключателя 80 знака противо-ЭДС (на первом выходе блока 9), противо-ЭДС или нуля (на четвертом выходе блока 9), а также постоянного напряжения (на третьем выходе блока 9). Источник 79 логических нуля и ; единицы блока 9 управляет логическо частью модели. Так, логические сигналы, подаваемые переключателем 81 на второй и шестой выходы блока 9 задают нуль-органу 6 и блоку 8 режи моделированиялогики симметричного или поочередного управления тиристорами. При поочередном управлении подаютчерез элемент 8Д переключате лями 80 и 81, на пятый выход блока 9 сигналы р и () +1С (формируемые элементом 83 дифференцирования)7 Пр этом блок 8 получает четыре угла управления и тем самым имитируется подача импульсов управления на каждый тиристор моделируемого моста. Сигналы на четвертом выходе блока 9 задают блоку 7, а сигналы на первом выходе - блоЛу 3 режим моделирования выпрямления или инвертирования путем задания полярности (переключателем 80) и величины противо-ЭДС (Е) блоком 82 постоянного коэффициента. Устройство работает следующим образом. В исходном положении выставляют амплитуду и частоту сигналов источника 1, значения коэффициентов передачи решающих усилителей блоков 2, 3, 4, 7, соответствующие моделируемой схеме преобразователя;, амплитудой и полярностью противо-ЭДС задают из блока 9 режим моделирования выпРямления или инвертирования, а количеством и значением углов управления - режим моделирования симметричного или поочередного управления тиристорами.После этого устройство переводят в режим решения, в течение которого происходит имитация работы преобразователя путем решения дифференциальных уравнений, соответствующих текущему интервалу работы преобразователя. Всего при имитации работы.преобразователя в режиме выпрямления или инвертирования, симметричного или поочередного управления тиристорами однофазного мостового преобразователя, в устройстве чередуют решение четьфех уравнений: - уравнение для тока i контура , 1 с-м сеть-нагрузка d-ic-H . ta,Etc e-aa-it-H. - уравнение для тока i| контура короткое замыкание-нагрузка -|jJ.ta E-a44, - уравнение для тока- 1ф контура сеть-короткое замыкание - абе-а,й, - уравнение для напряжения и, на нагрузке Од + е в этих уравнениях - постоянные коэффициенты, определяемые структурой преобразователя и его параметрами . Уравнение (1) решает схема иэ сумматора 16, инвертора 26, интегратора 10. Уравнение (2) решает схема из сумматора 14, интегратора 11, инвертора 2 5, ключа 21. . Уравнение (3) решает схема сумматора-интегратора 12. Напряжение на нагрузке формирую в блоке 4 из участков значений/ е, для соответствующих интервалов. Ключи 17 и 18 выделяют участки значений 1ф для каждого интервала коммутации, преобразуют их с помощ первого инвертора 22 и первого сум матора 13 в нарастающие и с выхода сумматора 13 подают на общий вход компаратора 5 и нуль-органа б в ка честве тока коммутации i. Ток в нагрузке формируют на вто ром интеграторе 11 из участков зна чений lj,.v, , 1ц. Участки тока ij вы резают ключом 21. Ток в питающей ф зе (1ф) формируют на выходе сумматора-интегратора 12 из участков то ка коммутации и тока i, выделенных на выходе сумматора 15 ключами 19 и 20. Сшивка вьщеленных участков и решений интеграторов реализуется на самих интеграторах с использованием режима индивидуального управления. При этом интеграторы мог находиться в двух режимах: Возврат и Решение. В режиме Возврат на выходе интегратора устанавливается напряжение, равное по величине и обратное по знаку напряжению, а в режиме Решение интегратор интегрирует сумму напря жений, приложенную к его входам (за исключением входа начальных условий). Так как время установления напряжения на интеграторах существенно больше, чем время смены их режимов, то за время переключения режимов напряжение на выходе интегратора практически не меняется, что обеспечивает непрерывность сшивки. Кроме того, для повышения надеж ности работы устройства сшивка pea лизуется по следующему алгоритму, подавая на вход навальных условий интегратора напряжение предыдущего участка и интегрируя уравнение для последующего, получают, при перехо де интегратора из состояния Возврат в состояние Решение непрерывную сшивку напряжений этих участков. Это происходит за счет того, что в это время у интегратора предыдущего участка происходит . Решение смена состояний из Возврат,. причем Решение пре дыдущего участка продолжается еще некоторое время после перехода в Решение последующего. Сшивкой мгновенных значений токов в рагрузке, в фазе питающей сети и напряжения на нагрузке, а также вьщелением соответствующих участков кривых управляют комбинации временных интервалов, которые формируют в блоке 8 управления. Инверторы 23 и 24 выполняют функции развязки. Для образования комбинаций временных интервалов при симметричном управлении в блоке 8 формируют с помощью трех триггеров три временных интервала: интервал коммутации 1 и интервалы полной проводимости А и В. При имитации поочередного режима дополнительно формируют с помощью четвертого триггера интервал С полной проводимости. Комбинации временных интервалор состоят из связок пар интервалов двух видов относительно ТЗ . Первый вид - это связь интервалов коммутации с интервалс1ми полной проводимости: Ол А, DA В, плс. Условия их непрерывности: D л А О, ОлВ -О, ОлС 0. Этиусловия показывают, что управляемый такими связками интегратор контура коммутации отключится лишь после включения интегратора контура полной проводимости, тем самым переключение происходит с некоторым перекрытием как временных интервалов, так и участков аналоговых кривых. Второй вид пар связок - это связь интервалов полной проводимости с интервалами коммутации: А Л D, В Л D, CAD. Условия их непрерывности: АЛО 0, , СЛ:Ь 0. Формирование временных интервалов, непрерывных связок, их комбинаций, а также распределение комбинаций временных интервалов между входами управления аналоговых элементов устройства осуществляется в блоке 8 управления. Основные преимущества предлагаемого устройства перед иэвестными состоят в том, что предлагаемое устройство моделирует мгновенные значения тока и напряжения источника фазного напряжения, питающего преобразователь, а также значения тока и напряжения в нагрузке в режимах выпрямления и инвертирования при симметричном и поочередном управлении тиристорами. .Кроме того, устройство позволяет сравнивать динамические и статические характеристики преобразователя при двух способах управления тиристорами, работает в реальном масштабе времени и позволяет снимать регулировочные и нагрузочные характеристики преобразователя, зависимости угла коммутации от угла управления и угла коммутации от тока нагрузки, а также проводить сравнение энергетических показателей преобразователя при симметричном и поочередном управлении тиристорами однофазного мостового преобразователя.

Формула изобретения

1.Устройство для моделирования вентильного преобразователя, содержащее источник фазного напряжения, вьоходы которого соединены соответственно с первыми группами входов блока формирования сигналов управления и блока формирования входной ЭДС/ блок формирования напряжения нагрузки, нуль-орган и компаратор, выход которого подключен к первому входу блока управления, второй вход которого соединен с выходом блока формирования сигналов управления, отличающееся тем, что,

с целью повышения точности и быстродействия, в устройство введены блок моделирования контуров тока и блок задания режима, первая группа выходов которого подключена к второй группе входов блока формирования сигналов управления, первая и вторая группы выходов которого соединены соответственно с входами блока задания режима и с первой группой входов блоков управления, вторая группа входов которого подключена к второй группе выходов блока задания режима первый и второй выходы которого соединены соответственно с первыми входами блока моделирования контуров Тока и нуль-органа, выход которого подключен к третьему входу блока управления, первая группа выходов которого соединена с второй группой входов блока формирования входной ЭДС, выход которого подключен к первому входу блока формирования напряжения нагрузки и второму входу блока моделирования контуров тока, третий вход которого соединен с первым выходом источника фазного напряжения, первый выход блока моделирования контуров тока подключен к первому входу компаратора, второй выход блока моделирования контуров тока соединен с вторыми входами компаратора и нуль-органа, выход блока управления подключен к второму входу блока формирования напряжения нагрузки и к четвертому входу блока моделирования контуров тока, группа управляющих входов которого соединена соответственно с второй и третьбьй группой выходов блока управления, четвертый вход которого подключен к второму выходу источника фазного напряжения.

2.Устройство по п. 1, о т л ичающеес я тем, что блок моделирования контуров тока содержит сумматоры, ключи, элементы НЕ, интеграторы и сумматор-интегратор, первый вход которого является.третьим входом блока, выход сумматораинтегратора соединен с его вторым

входом и через цепочку из последовательно соединенных первого ключа и первого элемента НЕ подключен к первому входу первого сумматора, выход которого является первым выходом блка , вторым вводом которого является первый вход второго сумматора, выход которрго соединен с первьлм J входом первого интегратора, выход которого подключен к первому входу второго интегратора и к входам второго ключа и второго элемента НЕ, Выход которого соединен с вторым входом второго сумматора и с входом третьего ключа, выходы второго и третьего лючей подключены соответственно к входам третьего сумматора выход которого соединен с третьим входом сумматора-интегратора, выход которого через четвертый ключ подключен к второму входу первого сумматора , выход четвертого сумматора соединен с вторым входом второго интегратора, выход которого через цепочку последовательно соединенных третьего элемента НЕ и пятого ключа подключен к второму входу первого интегратора, вход четвертого элемента НЕ является первым входсял блока, а четвертого элемента НЕ непосредственно соединен с третьин входом второго сумматора и через пятый элемент НЕ подключен к первом входу четвертого сумматора, вход которого соединен с выходом третьего элемента НЕ, являющимся вторым выходом блока, группой управляющих входов которого являются управляющие входы ключей и интеграторов.

3, Устройство по п. 1, отличающееся тем, что блок формирования сигн.алов управления содержит сумматоры,компараторы, элементы 2И, ИЛИ и 2-2И-ИЛИ, элементы дифференцирования и интегратор, выход которого соединен с первыми входами первого и второго компараторов и первого сумматора, выход которого подключен к первым входам третьего и четвертого компараторов, выход второго сумматора соединен с входом пятого компаратора, выход которого является выходом блока, первой группой входов которого являются соответственно входы второго сумматора, шестого и седьмого компараторов и интегратора, второй группой входов блока являются вторые входы первого второго, третьего и четвертого компараторов , выходы шестого и седьмог компараторов соединены соответственно с первьми входами элементов 2И и с первым и вторым входами элемента 2-2И-ИЛИ, третий и. четвертый входы которого подключены соответственно к выходам первого и четвертого компараторов, а выход элемента 2-2И-ИЛИ связан с входом первого элемента дифференцирования, выходы второго и третьегокомпараторов соединены соответственно с вторыми входами элементов 2И, выходы которых подключены к входам элемента ИЛИ, выход которого соединен, с входомвторого элемента дифференцирования, выходы элементо дифференцирования и элементов 2И являются соответственно первой и второй группами выходов блока. I 4. Устройство по п. 1, отличающееся тем, что блок управления содержит триггеры, элемент 2И, 2И-НЕ, 2ИЛИ, 2-2И-ИЛИ, 2-ЗИ-ИЛИ 3-ЗИ-ИЛЙ, НЕ, 2-2-2И-ИЛИ,2-3-ЗИ-ИЛИ и 4ИЛИ, элемент дифференцирования, элемент задержки и компаратор, вход которого является четвертым входом блока, выход компаратора подключен к первым входам первых элементов 2И-НЕ и 2ИЛИ V первый вход второго элемента 2ИЛИ соединен с входом первого элемента НЕ и первым и вторым входами первого элемента 2-ЗИ-И и является соответствующим входом первой группы входов блока, выход второго элемента12ИЛИ соединен с первь1ми входами первого элемента 2И и элемента 2-2-2И-ИЛИ, выход которого подключен к входу второго элемента НЕ, первый вход первого элемента 2-2И-ИЛИ соединен с первым входом второго элемента 2-ЗИ-ИЛИ, с третьим входом первого элемента 2-ЗИ-ИЛИ и является вторым входом блока, выход первого элемента 2-2И-ИЛИ соединен с первым входом первого триггера, первый выход которого подключен к вторым входам первых Элементов 2И и 2И-НЕ и к первом и второму входам элемента 2-3-ЗИ-ИЛ выход которого соединен с вторым и третьим входом первого элемента 2-2-2И-ИЛИ, второй выход первого триггера подключен к второму входу первого элемента 2ИЛИ, к первому входу элемента 4ИЛИ, к четвертому входу первого элемента 2-2-2И-ИЛИ и к первым входам первого и второго элементов 3-ЗИ-ИЛИ, выход последнег из которых соединен с первым входом второго триггера, первый выход которого подключен к первым входам вторых элементов 2И, 2И-НЕ и 2-2И-И и к второму и третьему входам второго элемента 3-ЗИ-ИЛИ, второй выход второго триггера соединен с третьим входом элемента 2-3-ЗИ-ИЛИ и с вторым входом элемента 4ИЛИ, выход которого подключен к второму входу второго элемента 2-ЗИ-ИЛИ, к четвертому входу первого элемента 2-ЗИ-ИЛИ, к первому входу третьего элемента 3-ЗИ-ИЛИ и третий элемент НЕ - к второму и третьему ,

входам первого элемента 2-2И-ИЛИ, первый и второй входы третьего элемента 2-2И-ЙЛИ объединены и являются первым входом блока, третьим входом которого является одноименный вход третьего элемента 2-2И-ИЛИ, выход которого через элемент дифференцирования подключен к третьему входу второго элемента 2-ЗИ-ИЛИ, четвертому и пятому входам второго элемента 3-ЗИ-ИЛИ, пятому входу первого элемента 2-ЗИ-ИЛИ,к третьему входу первого элемента 3-ЗИ-ИЛИ, к второму входу третьего элемента 3-ЗИ-ИЛИ, к первому входу третьего элемента 2И и через элемент задержки - к второму входу первого триггера, выход второго элемента 2-ЗИ-ИЛИ соединен с вторым входом второго триггера, ВЕлход четвертого элемента НЕ подключен к шестому входу второго элемента З- и-или, выход первого элемента НЕ соединен с четвертым входом первого элемента 3-ЗИ-ИЛИ, выход которого подключен к первому входу третьего триггера, первый -выход которого соединен с первыми входами четвертого элемента 2И и третьего элемен7-а 2И-НЕ, с вторым входом второго элемента 2-2И-ИЛИ, с пятым и шестым входами первого элемента 3-ЗИ-ИЛИ, второй вход третьего триггера подключен к выходу первого элемента 2-ЗИ-ИЛИ, второй вьтход третьего триггера соединен с четвертым входом элемента 2-3-ЗИ-ИЛИ и с третьим входом элемента 4ИЛИ, четвертый вход которого соединен с пятым входом элемента 2-3-ЗИ-ИЛИ и подключен к первому выходу четвертого триггера, первый вход которогб соединен с вькодом третьего элемента 2И, а второй выход второго триггера подключен к пятому и шестому входам первого элемента 2-2-2И-ИЛИ и к второму входу третьего элемента 2И, второй вход второго элемента 2ИЛИ соединен с шестьм и седьмым входами элементов 2-3-ЗИ-ИЛИ, с четвертым и пятым входами вт орого элемента НЕ и являются первой группой входов блока, второй группой входов которого являются четвертый вход первого элемента 2-2И-ИЛИ и третий и четвертый входы третьего элемента 3-ЗИ-ИЛИ выход которого соединен с вторьм входом четвертого триггера, выход первого элемента 2И подключен к восьмому входу элемента 2-3-ЗИ-ИЛИ, к вторьвм входам второго и четвертого элементов 2И, второго и третьего элементов 2И-НЕ, к второму и третьему входам второго элемента 2-2И-ИЛИ, к пятому я шестому входам третьего элемента 3-ЗИ-ИЛИ, выходы второго и четвертого элементов 2И являются первой группой выходов блока, второй

группой выходов-которого являются выходы элементов 2-3-ЗИ-ИЛИ,2-2-2ИИЛИ и 2-2И-ИЛИ, выходы первых элементов 2И-НЕ 2ИЛИ, второго элемента НЕ и второго и третьего элементов 2Й-НЕ являются третьей группой выходов блока.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 644242, кл, G Об G 7/62, 1977.

2.Авторское свидетельство СССР № 526922, кл, G 06 G 7/62, 1974 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования вентильного электродвигателя | 1988 |

|

SU1596357A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Вентильный электропривод | 1986 |

|

SU1319221A1 |

| Преобразователь аналогового сигнала в частоту с импульсной обратной связью | 1988 |

|

SU1587633A1 |

| Измерительное устройство к балансировочному станку | 1984 |

|

SU1221516A1 |

| Устройство для измерения интенсивности линии в оптическом спектре | 1987 |

|

SU1509625A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| Стабилизатор переменного напряжения | 1988 |

|

SU1534434A1 |

| Измерительное устройство к балансировочному станку | 1987 |

|

SU1415092A1 |

iDi

/ w i. / I ч/ w ч/ V

/

Q

«N w

Р 7kC (

Инбертиробание

О.Шзилрад.

81

%f

Авторы

Даты

1982-10-23—Публикация

1981-01-06—Подача