Изобретение относится к области измерительной и вычислительной техники и может быть использовано для аналого-цифрового преобразования преимущественно узкополосных сигналов.

Цель изобретения - расширение области применения за счет обеспечения возможности преобразования сиг- .налов с широким спектром частот.

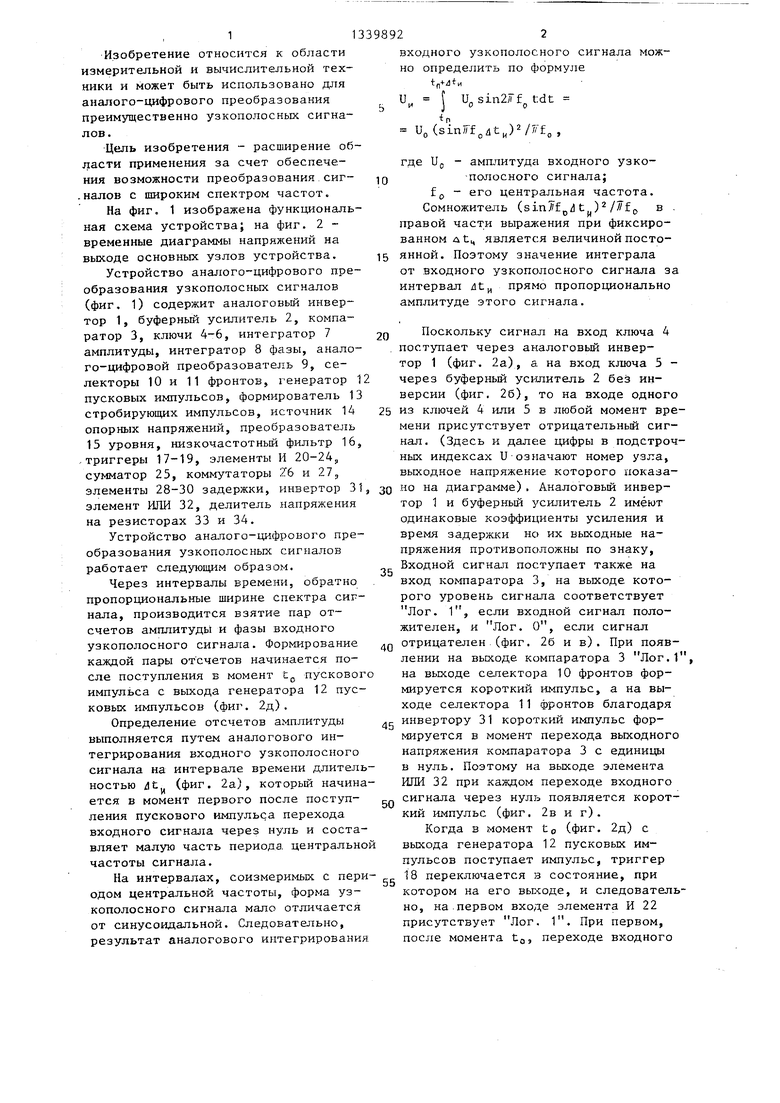

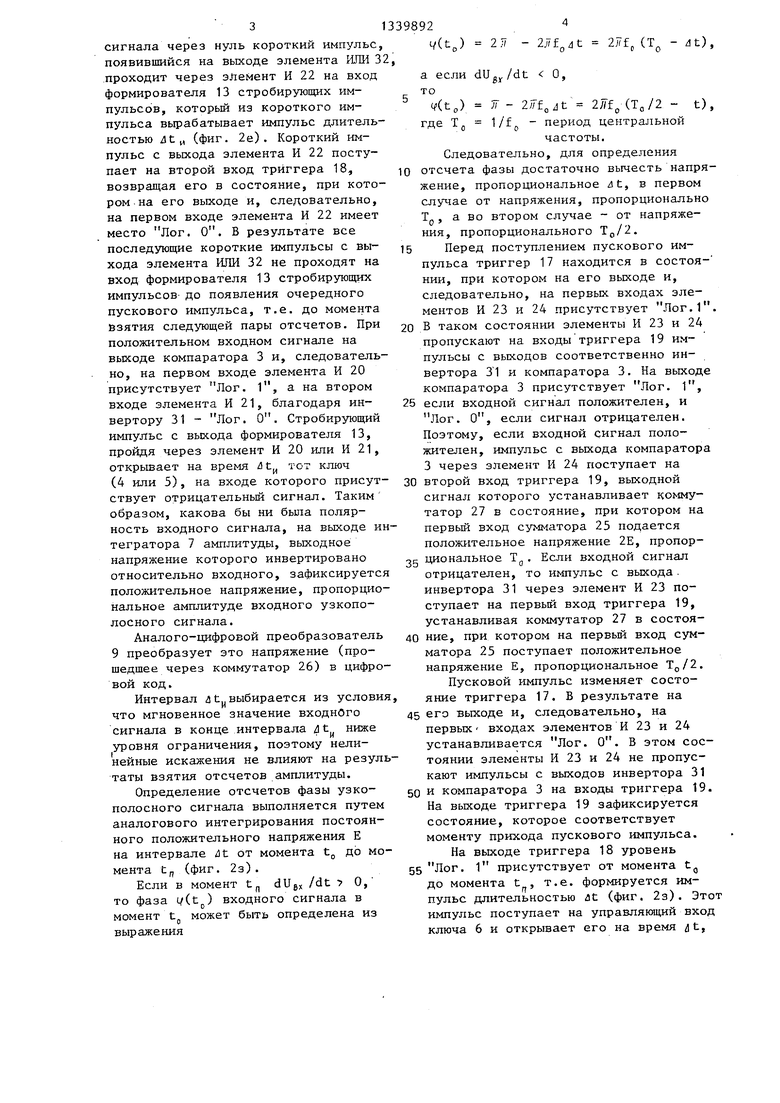

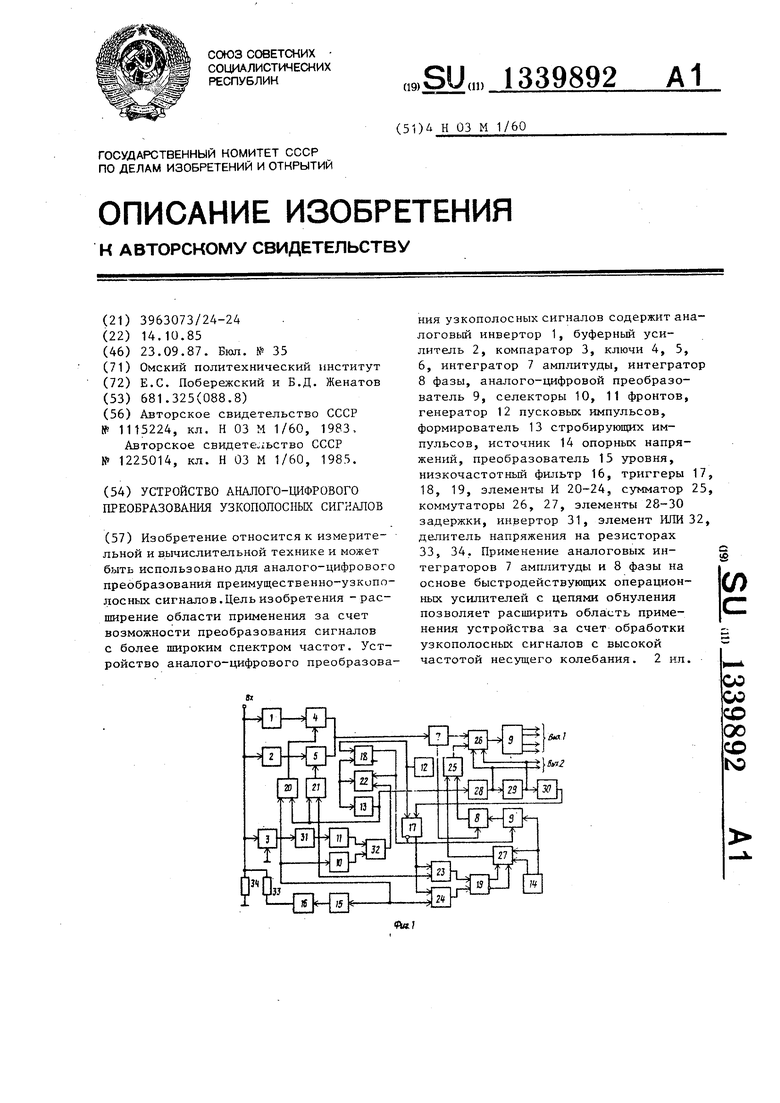

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 - временные диаграммы напрялсений на выходе основных узлов устройства.

Устройство аналого-цифрового преобразования узкополосных сигналов (фиг. 1) содержит аналоговый инвертор 1, буферный усилитель 2, компаратор 3, ключи 4-6, интегратор 7 амплитуды, интегратор 8 фазы, аналого-цифровой преобразователь 9, селекторы 10 и 11 фронтов, генератор 1 пусковых импульсов, формирователь 13 стробирующих импульсов, источник 1А опорных напряжений, преобразователь 15 уровня, низкочастотньй фильтр 16, -триггеры 17-19, элементы И 20-24, сумматор 25, коммутаторы 26 и 27, элементы 28-30 задержки, инвертор 31 элемент ИЛИ 32, делитель напряжения на резисторах 33 и 34.

Устройство аналого-цифрового преобразования узкополосных сигналов работает следующим образом.

Через интервалы времени, обратно пропорциональные ширине спектра сигнала, производится взятие пар отсчетов амплитуды и фазы входного узкополосного сигнала. Формирование каждой пары от счетов начинается после поступления в момент t пусковог импульса с выхода генератора 12 пусковых импульсов (фиг. 2д).

Определение отсчетов амплитуды выполняется путем аналогового интегрирования входного узкополосного сигнала на интервале времени длительностью it (фиг. 2а), который начинается в момент первого после поступления пускового имлульса перехода входного сигнала через нуль и составляет малую часть периода, центрально частоты сигнала.

Иа интервалах, соизмеримых с периодом центральной частоты, форма узкополосного сигнала мало отличается от синусоидальной. Следовательно, результат аналогового интегрирования

входного узкополосного сигнала но определить по формуле

Up sin2yi f t;dt

U„(siпFf„dtJV/ f„

где

Uo fo амплитуда входного узкополосного сигнала; его центральная частота. Сомножитель (sinJf.it )/Jf в - правой части выражения при фиксированном дtц является величиной постоянной. Поэтому значение интеграла от входного узкополосного сигнала за интервал ut прямо пропорционально амплитуде этого сигнала.

0

0

Поскольку сигнал на вход ключа 4 поступает через аналоговый инвертор 1 (фиг. 2а), а на вход ключа 5 - через буферньй усилитель 2 без инверсии (фиг. 2б), то на входе одного

5 из ключей 4 или 5 в любой момент времени присутствует отрицательный сигнал. (Здесь и далее цифры в подстрочных индексах U-означают номер узла, выходное напряжение которого показано на диаграмме). Аналоговый инвертор 1 и буферный усилитель 2 имеют одинаковые коэффициенты усиления и время задержки но их выходные напряжения противоположны по знаку. Входной сигнал поступает также на вход компаратора 3, на выходе которого уровень сигнала соответствует Лог. 1, если входной сигнал положителен, и Лог. О, если сигнал

Q отрицателен (фиг. 26 и в). При появлении на вьсходе компаратора 3 Лог.1, на выходе селектора 10 фронтов формируется короткий импульс, а на выходе селектора 11 фронтов благодаря

с инвертору 31 короткий импульс формируется в момент перехода выходного напряжения компаратора 3 с единицы в нуль. Поэтому на выходе элемента ИЛИ 32 при каждом переходе входного сигнала через нуль появляется короткий импульс (фиг. 2в и г).

Когда в момент to (фиг. 2д) с выхода генератора 12 пусковых импульсов поступает импульс, триггер 18 переключается з состояние, при котором на его , и следовательно, на первом входе элемента И 22 присутствует Лог. 1. При первом, после момента t, переходе входного

5

0

3

сигнала через нуль короткий импульс появившийся на вькоде элемента ЯПИ 3 проходит через элемент И 22 на вход формирователя 13 стробируюпщх импульсов, которьш из короткого импульса вырабатывает импульс длительностью 4tt, (фиг. 2е) . Короткий импульс с выхода элемента И 22 поступает на второй вход триггера 18, возвращая его в состояние, при котором на его выходе и, следовательно, на первом входе элемента И 22 имеет место Лог. О. В результате все последующие короткие импульсы с выхода элемента ИЛИ 32 не проходят на вход формирователя 13 стробирующих импульсов до появления очередного пускового импульса, т.е. до момента взятия следующей пары отсчетов. При положительном входном сигнале на

выходе компаратора 3 и, следовательно, на первом входе элемента И 20 присутствует Лог. 1, а на втором входе элемента И 21, благодаря инвертору 31 - Лог. О. Стробирующий импульс с выхода формирователя 13, пройдя через элемент И 20 или И 21, открывает на время t тот ключ (4 или 5), на входе которого присутствует отрицательный сигнал. Таким образом, какова бы ни бьиа полярность входного сигнала, на выходе интегратора 7 амплитуды, выходное напряжение которого инвертировано относительно входного, зафиксируется положительное напряжение, пропорциональное амплитуде входного узкополосного сигнала.

Аналого-цифровой преобразователь 9 преобразует это напряжение (прошедшее через коммутатор 26) в цифровой код.

Интервал лt.выбирается из условия что мгновенное значение входного сигнала в конце интервала /3t ниже уровня ограничения, поэтому нелинейные искажения не влияют на результаты взятия отсчетов амплитуды.

Определение отсчетов фазы узкополосного сигнала выполняется путем аналогового интегрирования постоянного положительного напряжения Е на интервале At от момента t до момента С„ (фиг. 2з).

Если в момент t dUj, /dt 7 О, то фаза L/(tp) входного сигнала в момент tji может быть определена из выражения

частоты.

Следовательно, для определения отсчета фазы достаточно вычесть напряжение, пропорциональное 4t, в первом случае от напряжения, пропорционально Тр, а во втором случае - от напряжения, пропорционального То/2.

Перед поступлением пускового импульса триггер 17 находится в состоя- НИИ, при котором на его выходе и, следовательно, на первых входах элементов И 23 и 24 присутствует Лог.1. В таком состоянии элементы И 23 и 24 пропускают на входы триггера 19 импульсы с выходов соответственно инвертора 31 и компаратора 3. На выходе компаратора 3 присутствует Лог. 1, если входной сигнал положителен, и Лог. О, если сигнал отрицателен. Поэтому, если входной сигнал поло3 через элемент И 24 поступает на

30 второй вход триггера 19, выходной сигнал которого устанавливает коммутатор 27 в состояние, при котором на первый вход сумматора 25 подается положительное напряжение 2Е, пропор25 циональное Т. Если входной сигнал отрицателен, то импульс с выхода. инвертора 31 через элемент И 23 поступает на первый вход триггера 19, устанавливая коммутатор 27 в состоя40 ние, при котором на первый вход сумматора 25 поступает положительное напряжение Е, пропорциональное То/2. Пусковой импульс изменяет состояние триггера 17. В результате на

45 его выходе и, следовательно, на первых- входах элементов И 23 и 24 устанавливается Лог. О. В этом состоянии элементы И 23 и 24 не пропускают импульсы с выходов инвертора 31

50 и компаратора 3 на входы триггера 19

На выходе триггера 19 зафиксируется

состояние, которое соответствует

моменту прихода пускового импульса.

На выходе триггера 18 уровень

55 Лог. 1 присутствует от момента t до момента t , т.е. формируется импульс длительностью at (фиг. 2з). Эт импульс поступает на управляющий вхо ключа 6 и открывает его на время it,

в течение которого интегратор 8 фазы интегрирует -положительное напряжение Е.

Выходное напряжение интегратора 8 фазы интегратора 8 фазы инвертирован относительно входного. На выходе ин- тег ратора 8 фазы фиксируется отрицательное напряжение, пропорциональное ut (фиг. 2к), которое подается на второй вход сумматора 25. На первом входе сумматора 25 присутствует положительное напряжение 2Е или Е в зависимости от знака входного сигнала в момент .

Таким образом, на выходе сумматор 25 оказывается зафиксированным напряжение, пропорциональное (t) (фиг. 2л), которое через коммутатор поступает на вход аналого-цифрового преобразователя 9 и преобразуется в цифровой код.

Импульс с выхода элемента 28 задержки устанавливает коммутатор 26 в состояние, при котором выходное напряжение интегратора 7 амплитуды поступает на вход аналого-цифрового преобразователя 9 и вьщается в коде по выходной информационной шине. Продолжительность этого состояния не- Сколько меньше половины И1гтервала дискретизации. Импульс с выхода элемента 29 задержки устанавливает коммутатор 26 в состояние, при кото ррм на вход аналого-цифрового пре- образователя 9 поступает напряжение с выхода сумматора 25, пропорциональное фазе входного сигнала. Импульсы, поступающие на выходную адресную шину, определяют порядок счи- тывания амплитуды и фазы преобразуемого входного сигнала.

Импульс с выхода элемента 30 задержки устанавливает интегратор 7 амплитуды и интегратор 8 фазы в исходное состояние, а триггер 17 - в состояние, когда на его выходе присутствует Лог. 1.

Узкополосный сигнал, поступивший на вход устройства аналого-цифрового преобразования;, может быть подвержен не только двухстороннему симметричному (фиг. 2а и б), но и одностороннему или двухстороннему несимметричному ограничению.

При одностороннем нессиметричном ограничении происходит смещение нулевого уровня и, следовательно, на выходе компаратора 3 формируется сигнал, у которого длительность Лог. 1 больше длительности Лог. О, если напряжение смещения положительно, и, наоборот, если напряжение смещения отрицательно. Преобразователь 15 уровня, сдвигая уровень выходного сигнала компаратора 3, превращает ег в биполярный с одинаковыми амплитудами положительной и отрицательной частей периода. При отсутствии смещения нулевого уровня сигнал на выходе преобразова.теля 15 уровня оказываетс равным не только по амплитуде, но и по длительности положительной и отрицательной частей периода. Следовательно, в этом случае постоянная составляющая напряжения на выходе преобразователя 15 уровня, выделяемая низкочастотным фильтром 16 равна нулю. При смещении нулевого уровня входного сигнала длительности положительной и отрицательной частей периода на выходе преобразователя 15 уровня становятся различными и низкочастотный фильтр 16 вьщеляет напряжение, пропорциональное по величине и противоположное по знаку смещению. Это напряжение, поступая на входную шину через делитель напряжения на резистора.х 33 и 34, компенсирует смещение нулевого уровня входного узкополосного сигнала.

Применение аналоговых интеграторо амплитуды и фазы позволяет преобразовать узкополосные сигналы с центральной частотой на порядок более высокой.,чем в известном устройстве. Поскольку в предлагаемом устройстве важна относительная узко- полосность колебания, увеличение центральной частоты позволяет обрабатывать сигналы с более широким спектром, что расширяет область применения устройства.

Формула изобретения

Устройство аналого-цифрового преобразования узкополосных сигналов, содержащее аналоговьш инвертор и буферный усилитель, входы которых объединены, аналого-цифровой преоб- К азователь, низкочастотный фильтр, три триггера, три элемента задержки, компаратор, первый вход которого соединен с выходом делителя напряжения и является входной шиной, второй вход подключен к имне нулевого

потенциала, а выход соединен с входом первого селектора фронтов, с первым входом первого элемента И и через инвертор - с первым входом второго элемента И и входом второго селектора фронтов, выход которого соединен с первым входом элемента ИЛИ, второй вход которого подсоединен к выходу первого селектора фронтов, а выход - к первому входу третьго элемента И, выход которого подключен к входу формирователя строби- рующих импульсов, а второй вход - к прямому выходу первого триггера, вход установки в 1 которого соединен с выходом генератора пусковых импульсов, и объединен с входом установки в 6 второго триггера, вход установки в 1 которого подключен к выходу первого элемента задержки, прямой выход второго триггера соединен с первыми входами четвертого и пятого элементов И, первьш и второй, входы делителя напряжения соединены соответственно с шиной нулевого потенциала и выходом низкочастотного фильтра, вторые входы первого и второго элементов И объединены, отличающееся тем, что, с целью расширения области применения за счет обеспечения возможности преобразования сигналов с широким спектром частот, в него введен преобразователь уровня, сумматор, два коммутатора, источник опорных напряжений, интегратор фазы и интегратор амплитуды, три ключа, информационные входы первого и второго из которых соответственно подключены к выходам аналогового инвертора и буферного усилителя, вход которого является входной шиной, выходы первого и второго ключей объединены и соединены с информационным входом интегратора амплитуды, выход которого соединен с первым информационным входом первого коммутатора, второй информационньй вход которого

соединен с выходом сумматора, а выход - с входом аналого-цифрового преобразователя, выходы которого

являются выходной информационной шиной, первый и второй выходы источника опорных напряжений соединены соответственно: с первым и вторым информационными входами второго коммутатора, выход которого подключен к первому входу сумматора, второй вход которого через последовательно соединенные интегратор фазы и третий ключ соединен с вторым

информационньш входом второго коммутатора, первый и второй управляющие входы которого подключены соответственно к прямому и инверсному выходам третьего триггера, входы установок в 1 и О которого соединены с выходами соответственно четвертого и пятого элементов И, второй вход четвертого элемента И подключен к выходу инвертора, второй

вход пятого элемента И соединен с вькодом компаратора и через преобразователь уровня - с входом низкочастотного фильтра, входы обнуления интеграторов амплитуды и фазы объединены и подключены к выходу первого элемента задержки, вход которого через последовательно соединенные второй и третий элементы задержки подключен к выходу формирователя

стробирующих импульсов и к второму входу первого элемента И, выходы первого и второго элементов И соединены с управляющими входами соответственно первого и второго ключей,

управляющий вход третьего ключа соединен с прямым выходом первого триггера, вход установки в О которого подключен к выходу третьего элемента И, выходы второго и третьего элементов задержки соединены соответственно с первым и вторым управляющими входами первого коммутатора и являются вйходной адресной ши - ной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство аналого-цифрового преобразования узкополосных сигналов | 1984 |

|

SU1225014A1 |

| Аналого-цифровой преобразователь узкополосных сигналов | 1983 |

|

SU1115224A2 |

| Устройство для оценки характеристик узкополосного случайного процесса | 1983 |

|

SU1117650A1 |

| Аналого-цифровой преобразователь узкополосных сигналов | 1981 |

|

SU999157A1 |

| Устройство для передачи и приема двух сигналов по одному проводу | 1989 |

|

SU1741281A1 |

| АНАЛИЗАТОР КАЧЕСТВА ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 1999 |

|

RU2145716C1 |

| Преобразователь угла поворота вала в код | 1982 |

|

SU1125643A1 |

| Преобразователь ток-частота с импульсной обратной связью | 1987 |

|

SU1552377A1 |

| Аналого-цифровой фильтр | 1980 |

|

SU873387A1 |

| Устройство для автоматического контроля нагрева горных машин | 1991 |

|

SU1758242A1 |

Изобретение относится к измерительной и вычислительной технике и может быть использовано для аналого-цифрового преобразования преимущественно-узкопо- лоснмх сигналов. Цель изобретения -расширение области применения за счет возможности преобразования сигналов с более широким спектром частот. Устройство аналого-цифрового преобразования узкополосных сигналов содержит аналоговый инвертор 1, буферный усилитель 2, компаратор 3, ключи 4, 5, 6, интегратор 7 амплитуды, интегратор 8 фазы, аналого-цифровой преобразователь 9, селекторы 10, 11 фронтов, генератор 12 пусковых импульсов, формирователь 13 стробирующих импульсов, источник 14 опорных напряжений, преобразователь 15 уровня, низкочастотный фильтр 16, триггеры 17, 18, 19, элементы И 20-24, сумматор 25, коммутаторы 26, 27, злементы 28-30 задержки, инвертор 31, элемент ИЛИ 32, делитель напряжения на резисторах 33, 34. Применение аналоговых интеграторов 7 амплитуды и 8 фазы на основе быстродействующих операционных усилителей с цепями обнуления позволяет расширить область применения устройства за счет обработки узкополосных сигналов с высокой частотой несущего колебания. 2 ил. uD сл оо 00 со 00 со го

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-09-23—Публикация

1985-10-14—Подача