мента И-НЕ, вход сброса счетчика является вторым входом таймера,

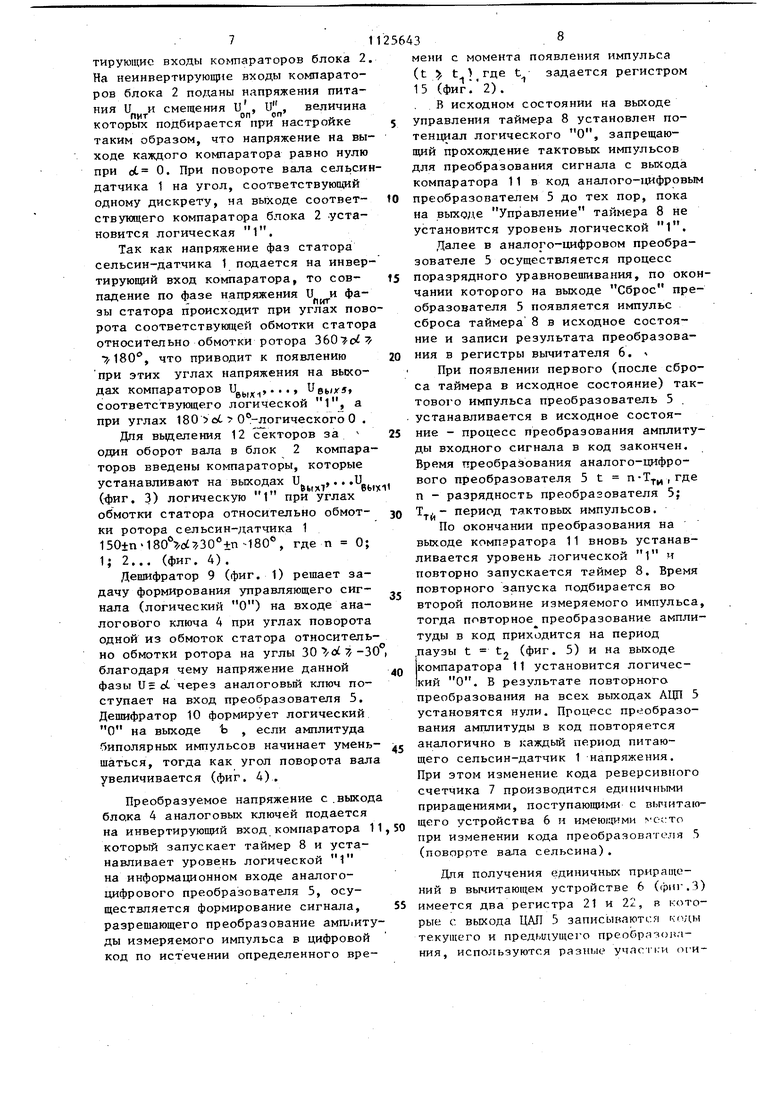

3, Преобразователь по п.1, отличающийся тем, что блок вьгчитания содержит триггер, элемент И, инвертор, регистр текущего состояния, регистр предьщущего состояния, два блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, три блока элементов И, сумматор, шину опорного напряжения, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, з равляющий вход первого блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ является управйяю1цим входом блока вычитания и через инвертор подключен к управляющему входу второго блока элементов ИСКПЮЧАНИЦЕЕ ИЛИ, информационные входы регистра текущего состояния являются информационными входами блока вычитания, выходы регистра текущего состояния через второй блок элементов ИСКЛЮЧАНЛЦЕЕ ИЛИ подключены к первой группе входов первого блока элементов И и к информационным входам регистра предьщущего состояния, выходы которого через первый 6J10K элементов ИСКЛЮЧАНЩЕЕ ИЛИ подключены к первой группе входов второго блока элементов И, вторые группы входов первого и второго блоков элементов И являются входом сброса блока вычитания и подключены к первому входу элемента И. и к входу триггера, выход которого подключен к управляющему входу регистра текущего состояния и к второму входу элемента И, выход которого подключен к управляющему входу регистра предьщущего состояния, выходы первого и второго блоков элементов И подключены к входам сумматора, вход переноса которого подключен к шине опорного напряжения, а выходы - к входам третьего блока элементов И, выходы первого и последнего разрядов сумматора подключены к входам элемента ИСКЛЮЧАЩЕЕ ИЛИ, выходы третьего элементов И и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ являются выходами блока вычитания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота валаВ КОд | 1979 |

|

SU836643A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ МАКСИМАЛЬНОЙ МОЩНОСТИ НА ВАЛУ | 2008 |

|

RU2368879C1 |

| Преобразователь угла поворота вала в код | 1982 |

|

SU1035629A1 |

| СПОСОБ ЗАТЯЖКИ РЕЗЬБОВЫХ СОЕДИНЕНИЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2008 |

|

RU2381098C2 |

| Дискретно-цифровой электропривод | 1985 |

|

SU1350800A1 |

| Преобразователь угол-код | 1984 |

|

SU1187273A1 |

| Устройство для измерения и контроля параметров аналого-цифровых преобразователей | 1981 |

|

SU1005297A1 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1119051A1 |

| Устройство управления весовым порционнымдОзАТОРОМ | 1979 |

|

SU836532A1 |

1. ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД, содержащий сельсин-датчик угла поворота вала вход которого подключен к выходу источника напряжения питания, бпок компараторов, выходы которого подключены к входам первого девшфратора, аналого-цифровой прео6разоватепЬ| информационные вькоды которого сое- динены с информационными входаЙ блока вычитания, выходы которого подключены к счетным входам реверсивного счетчика, блок аналоговых ключей, отличающийся тем, что, с целью повышения точнос и преобразователя, в него введены вто- рой дешифратор, элемент И, таймер и компаратор, источник напряжения питания выполнен ИМПУЛЬСНЫМ, выход источника напряжения питания подключен к первому входу блока компараторов, остальные входы которого подключены к выходам сельсин-датчика угла поворота вала, выходы первого дешифратора через элемент И подкп чены к управляющему входу блока, вычитания, первые три выхода блока компараторов через второй дешифратор подключены к управляющим входам блока аналоговых ключей, информационные входы которого подключены к вы,ходам сельсин-датчика угла поворота вала, а выход - к первому входу аналого-гщфрового преобразователя и к инверсному входу компаратора, выход которого подключен к первому входу таймера и второму входу ана- . лого-цифрового преобразователя, выход бброса которого подключен к одноименному входу блока вычитания и второму входу таймера, выходы котоё рого подключены к третьему и четвер. тому .входам аналого-цифрового преобразователя, цифровые выходы которого подкл ечены к информационньм . входам блока вычитания, управлякпций выход Iаналого-цифрового преобразо§ вателя подключен к прямому входу компаратора. 2. Преобразователь по п.1, отличающийся тем, что, таймер содержит два элемента И-НЕ,генератор тактовых импульсов, триггер, счет9) 4 чик и инверт н, первый вход первого элемента И-НЕ является.первым входом DO таймера, выход первого элемента И-НЕ подключен к первому входу триггера, выход которого подключен к первому входу второго элемента И-НЕ, ввжод которого подключен к счетному входу счетчика, выход которого является одним, выходом т1аймера и через инвертор подключен к второму входу первого элемента И-НЕ и второму входу тоигге-. . I ра, выход генератора тактовых импульсов является другим выходом таймера и подключен к второму входу второго эле

Изобретение относится к области систем передачи информации об угловом положен 1И объекта и может найти применение в системах автоматизации промышленных установок.

Известен преобразователь угла поворота вала в код, содержащий сельсин-датчик, последовательно соединенные блок демодуляторов, блок компараторов, логическое устройство,аналого-цифровой преобразователь и арифметическое устройство, блок памяти, сумматор, управляющий вход которого подключен к управляющем выходу логического устройства, а другой вход подключен к выходу фазового детектора, воделякацего базовый угол ti 1«

Недостатком преобразователя является невысокая точность преобразования в связи с влиянием на результат измерений колебаний амплитуды питающего напряжения.

Наиболее близким к изобретению является преобразователь, содержащий сельсин-датчик и последовательно соединенные блок компараторов, дешифратор, 6hoK аналоговых ключей.

аналогО-1ЩФРОВОЙ преобразователь, блок вычитания и реверсивный счетчик, причем информационные входы блока аналоговых ключей объедине.ны с соответствзпрщими входами блока |компараторов, три демодулятора, входы которых подключены к выходам сель.син-датчика, а вьгходы - к входам блока компараторов, а управляющий

выход дешифратора подключен к другому входу аналого-цифрового преобразователя С2Х

Недостатком известного преобразователя является невысокая точность

преобразования. Обладая низкой методической погрешностью, преобразователь характеризуется высокой фазовой погрешностью и влиянием величины и формы питающего напряжения на результат измерений.

Причина фазовой погрешности заключается в том, что фильтр низких частот, лежащий в основе демодулятора, вносит существенное запаздывание

по фазе измеряемого сигнала. Вторая погрешность при прямоугольной форме 1питающего сельсин напряжения вызывает при формировании каждого импул са динамические искажения его фронтов, что выражается в последующем изменении амплитуды измеряемого сигнала. При гармонической форме напряженияJпитающего сельсин, динами ческих искажений нет, но амплитуда сигнала менее стабильна, чем при им пульсном питании. Цель изобретения - повышение точ ности преобразователя. I , . - Поставленная цель достигается тем, что в преобразователь угла поворота вала в код, содержащий сельсин-датчик угла поворота вала,вход которого подключен к вькоду источника напряжения питания, блок компараторов, вькоды которого подключены к входам первого дешифратора, ана лого-цифровой преобразователь, инфор мационные выходы которого соединены с информационными входами блока вычитания, выходы которого подключены к счетным входам реверсивного счет- чика, блок аналоговых ключей, введен второй дешифратор, элемент И, таймер и компаратор, источник напряжения питания, вьшолнен импульсным, выход источника напряжения питания подключен к первому входу блока компараторов, остальные входы которого подключены к выходам сельсин-датчика угла поворота вала, выходы первого дешифратора через элемент И подклю- чены к управляющему входу блока вычитания , первые три выхода блока ком параторов через второй дешифратор подключены к управляющим входам бло. ка аналоговых ключей, информахщонные входы которого подключены к выходам сельсин-датчика угла поворота вала, а выход - к первому входу аналого-цифрового преобразователя и к и версному входу компаратора, выход которого подключен к первому входу таймера и второму входу аналогоцифрового преобразователя, вьрсод сброса которого подключен к одноимен ному входу блока вычитания и второму входутаймера, выходы которого подключены к третьему и четвертому входам аналого-цифрового преобразователя, цифровые выходы которого подкл чены к информационным входам блока вычитания, управляющий выход аналого цифрового преобразователя подключен к прямому входу компаратора. При этом таймер содержит два элемента И-НЕ, генератор тактовых импульсов, триггер, счетчик и инвертор, первый вход первого элемента Й-НЕ является первым входом таймера, выход первого элемента И-НЕ подключен к первому входу триггера, выход которого .подключен к первому входу второго элемента И-НЕ, выход которого подключен к счетному вз«оду счетчика, выход которого является одним выходом таймера и через инвертор подключен к второму входу первого элемента И-НЕ и второму входу триггера,выход генератора тактовых импульсов является другим выходом таймера и подключен к второму входу второго элемента И-НЕ, вход сброса счетчика является вторым входом таймера. Кроме того, блок вычитания содержит триггер, элемент И, инвертор, регистр текущего состояния, регистр предыдущего состояния, два блока элементов ИСКЛЮЧАИМЦЕЕ ИЛИ, три блока элементов П, сумматор, шину опорного напряжения, элемент ИСКЛЮЧАЩЕЕ ИЛИ, управляюпщй вход первого блока элементов ИСКЛЮЧАЩЕЕ ИЛИ является управляющим входом блока вычитания и через инвертор подключен к управляимцему входу второго блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, информ§ционные входы регистра текущего состояния являются информационными входами блока вычитания, выходы регистра текущего состояния через второй блок элементов ИСКЛЮЧАЩЕЕ ИЛИ подключены к первой группе входов первого блока элементов И и к информационным входам регистра предьщущего состояния, выходы которого через первьй блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к первой группе входов второго блока элементов И, вторые группы входов первого и второго блоков элементов И являются входом сброса блока вычитания и подключены к первому входу элемента И и к входу триггера, выход которого подключен к управляющему входу регистра текущего состояний и к второму входу элемента И, выход которого подключен к управляющему вхо- , ду регистра предыдущего состояния, выходы первого и второго блоков элементов И подключены к входам сумматора, вход переноса которого подключен к пине опорного напряжения, а выходы - к входам третьего блока

элементов И, выходы первого и последнего разрядов сумматора подключены к входам элемента ИСКПЮЧАКНЦЕЕ ИЛИ, выходы третьего блока элементов И и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ являются выходами блока вычитания.

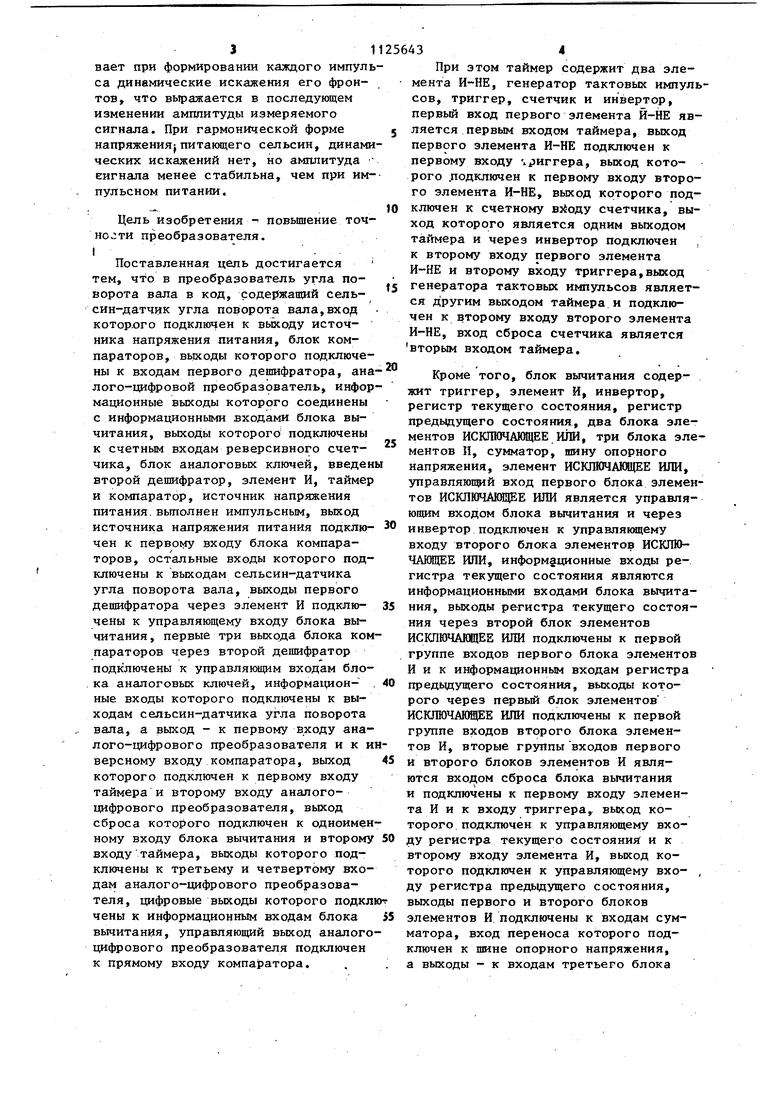

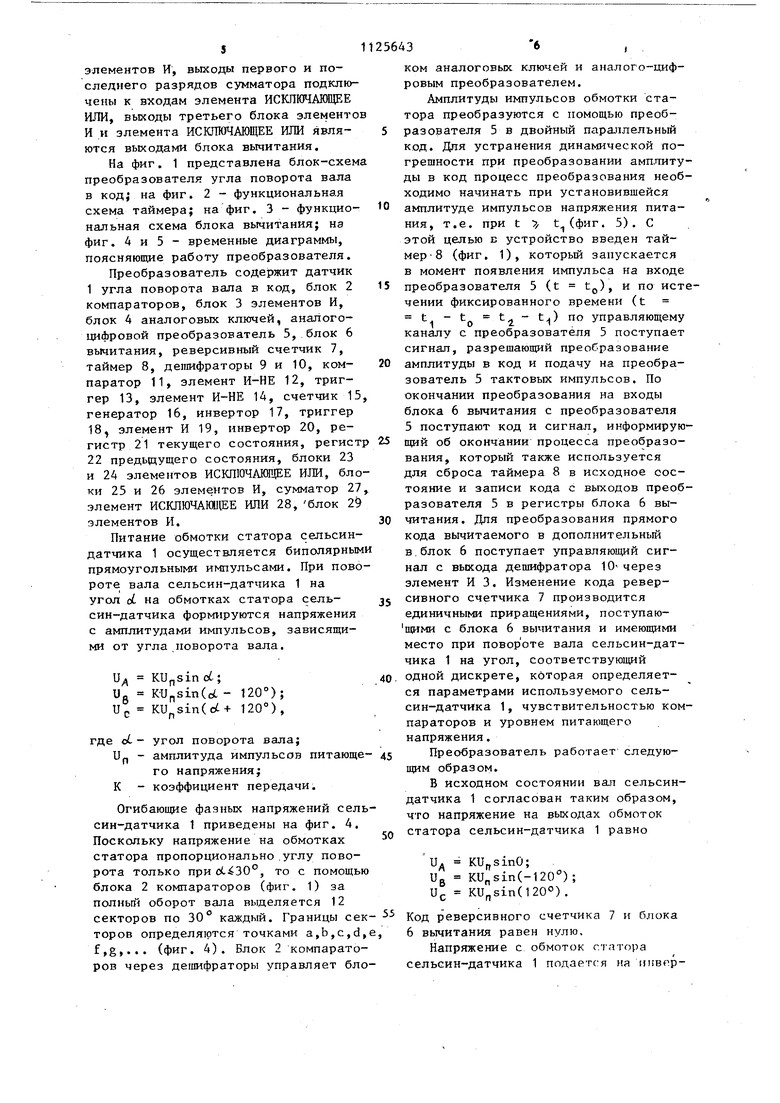

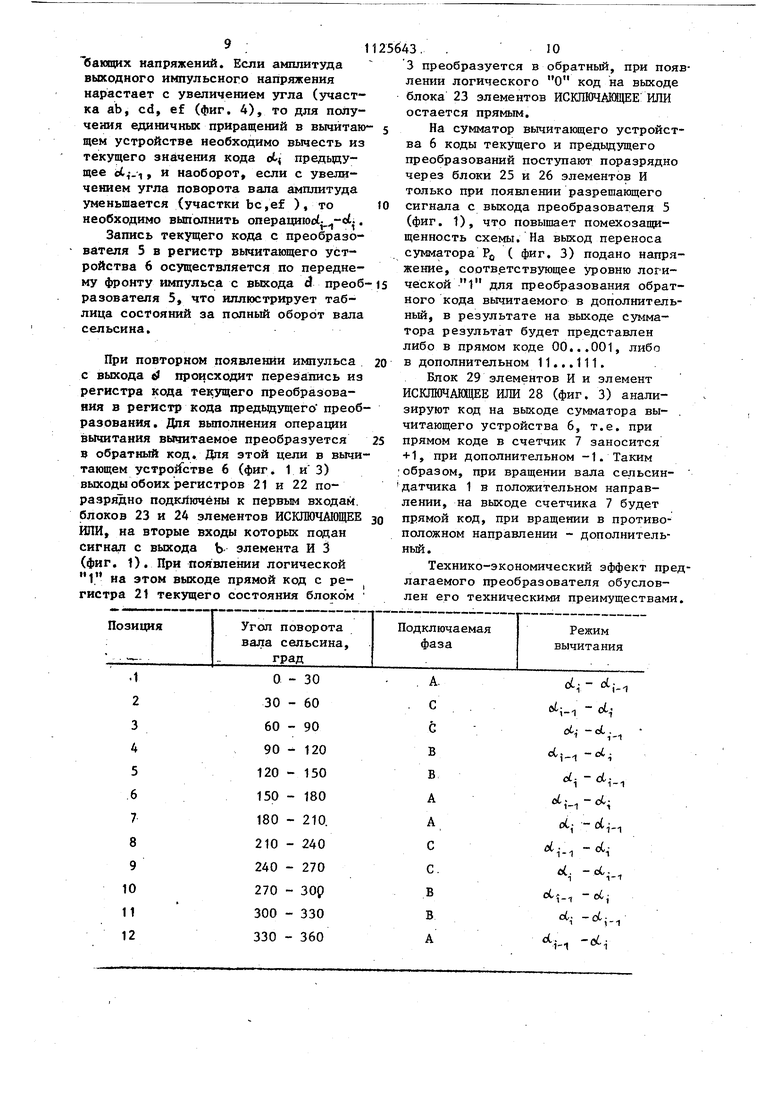

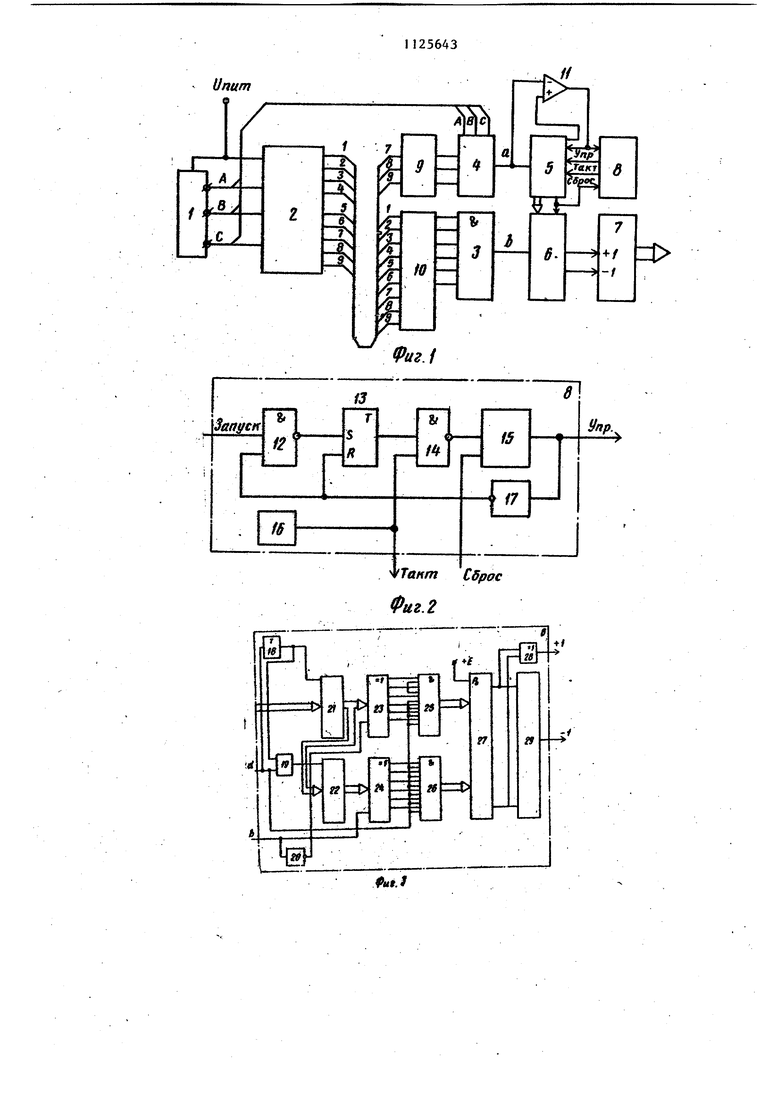

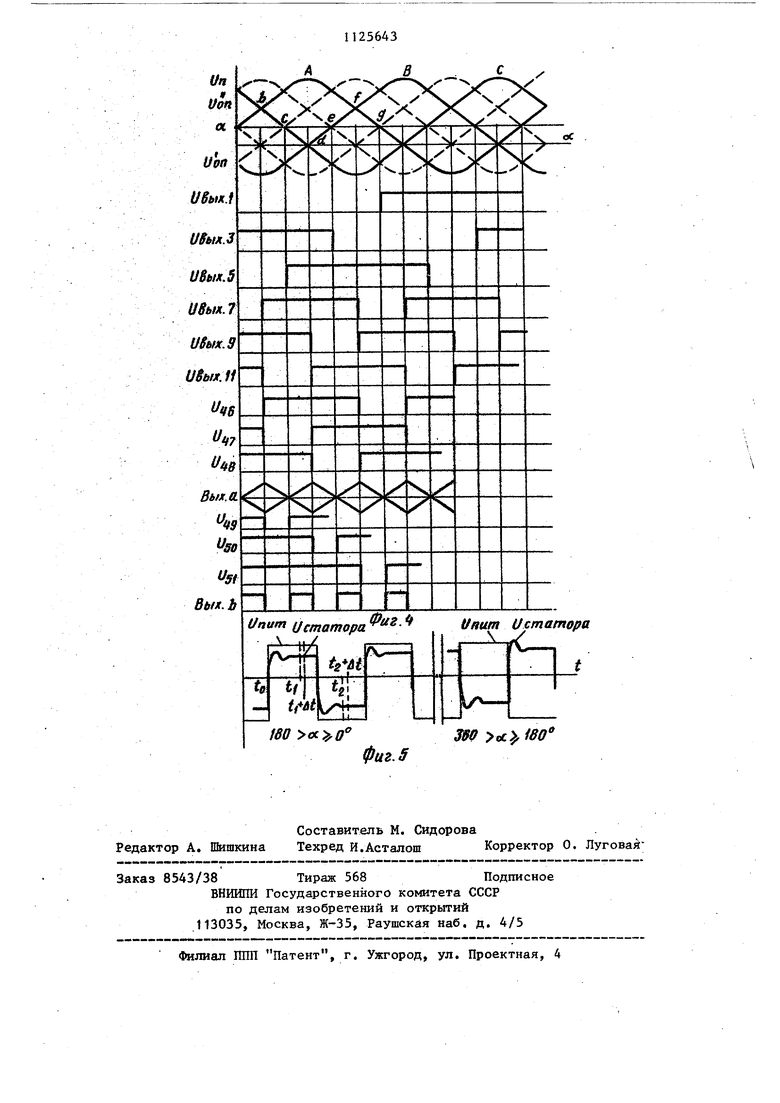

На фиг, 1 представлена блок-схема преобразователя угла поворота вала в код, на фиг. 2 - функциональная схема таймера; на фиг, 3 - функциональная схема блока вычитания; на фиг. 4 и 5 - временные диаграммы, поясняющие работу преобразователя.

Преобразователь содержит датчик 1 угла поворота вала в код, блок 2 компараторов, блок 3 элементов И, блок 4 аналоговых ключей, аналогоцифровой преобразователь 5, блок 6 вычитания, реверсивный счетчик 7, таймер 8, дешифраторы 9 и 10, компаратор 11, элемент И-НЕ 12, триггер 13, элемент И-НЕ 14, счетчик 15 генератор 16, инвертор 17, триггер 18 элемент И 19, инвертор 20, регистр 21 текущего состояния, регист 22 предьдущего состояния, блоки 23 и 24 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блоки 25 и 26 элементов И, сумматор 27, элемент ИСКЛЮЧАЩЕЕ ИЛИ 28, блок 29 элементов И. Питание обмотки статора сельсиндатчика 1 осуществляется биполярными прямоугольными импульсами. При повороте вала сельсин-датчика 1 на угол d на обмотках статора сельсин-датчика формируются напряжения с амплитудами импульсов, зависящими от угла,поворота вала. и KUpSin cL ; Ug KUnsinCol - 120°); Up ( 120°), где oL - угол поворота вала; Up - амплитуда импульсов питающего напряжения; К - коэффициент передачи. Огибающие фазных напряжений сель син-датчика 1 приведены на фиг, 4. Поскольку напряжение на обмотках статора пропорционально .углу поворота только при , то с помощью блока 2 компараторов (фиг, 1) за полньй оборот вала выделяется 12 секторов по 30° каждый. Границы сек торов определяются точками a,b,c,d,e f,g,... (фиг. 4). Блок 2 компараторов через дешифраторы управляет блоком аналоговых ключей и аналого-цифровым преобразователем.

Амплитуды импульсов обмотки статора преобразуются с помощью преобразователя 5 в двойный параллельный код. Для устранения динамической погрешности при преобразовании амплитуды в код процесс преобразования необходимо начинать при установившейся амплитуде импульсов напряжения питания, т,е. при t У/ t(фиг. 5). С этой целью в устройство введен таймер -8 (фиг. 1), который запускается в момент появления импульса на входе преобразователя 5 (t t), и по истечении фиксированного времени (t t - t t) no управляющему каналу с преобразователя 5 поступает сигнал, разрешающий преобразование амплитуды в код и подачу на преобразователь 5 тактовых импульсов. По окончании преобразования на входы блока 6 вычитания с преобразователя 5 поступают код и сигнал, информирующий об окончании процесса преобразования, который также используется для сброса таймера 8 в исходное состояние и записи кода с выходов преобразователя 5 в регистры блока 6 вычитания. Для преобразования прямого кода вычитаемого в дополнительньй в,блок 6 поступает управляющий сигнал с выхода дешифратора 10 через элемент И 3. Изменение кода реверсивного счетчика 7 производится единичными приращениями, поступающими с блока 6 вычитания и имеющими место при повороте вала сельсин-датчика 1 на угол, соответствующий одной дискрете, которая определяется параметрами используемого сельсин-датчика 1, чувствительностью компараторов и уровнем питающего напряжения. Преобразователь работает следующим образом. В исходном состоянии вал сельсиндатчика 1 согласован таким образом, что напряжение на выходах обмоток статора сельсин-датчика 1 равно и KUf,sinO; Ug KUnSin(-120) ; Uc KUnSin(120°) . Код реверсивного счетчика 7 и блока 6 вычитания равен нулю, Напряжение с обмоток статора сельсин-датчика 1 подается на iiuBfipтирующие входы компараторов блока 2 На неинвертирующяе входы компараторов блока 2 поданы н чпряжения питания и и смещения u, U, величина питол СП которых подбирается при настройке таким образом, что напряжение на вы ходе каждого компаратора равно нулю при ot 0. При повороте вала сельси датчика 1 на угол, соответствующий одному дискрету, на выходе соответствукщего компаратора блока 2 .установится логическая 1. Так как напряжение фаз статора сельсин-датчика 1 подается на инвер тирующий вход компаратора, то совпадение по фазе напряжения U и фазы статора происходит при углах пов рота соответствую1цей обмотки статор относительно обмотки ротора : 180, что приводит к появлению при этих углах напряжения на выходах компараторов Ug,,..., Ugb/xs, соответствующего логической 1, а при углах 180 ot О -логического О . Для вьвделения 12 секторов за один оборот вала в блок 2 компара торов введены компараторы, которые устанавливают на выходах U U ,, т чi,7ti Ь вы (.фиг. 3) логическую 1 при углах обмотки статора относительно обмотки ротора сельсин-датчика 1 150±п-180%о 7/30±п-180, где п 0; 1| 2... (фиг. 4). Дешифратор 9 (фиг. 1) решает задачу формирования управляющего сигнала (логический О) на входе аналогового ключа 4 при углах поворота одной из обмоток статора относитель но обмотки ротора на углы благодаря чему напряжение данной фазы и ot через аналоговый ключ поступает на вход преобразователя 5. Дешифратор 10 формирует логический О на выходе Ъ , если амплитуда биполярных импульсов начинает умень шаться, тогда как угол поворота вал увеличивается (фиг. 4). Преобразуемое напряжение с.выход блока 4 аналоговых ключей подается на инвертирующий вход компаратора 1 который запускает таймер 8 и устанавливает уровень логической 1 на информационном входе аналогоцифрового преобразователя 5, осуществляется формирование сигнала, разрешающего преобразование амш1иту ды измеряемого импульса в цифровой код По истечении определенного времени с момента появления импульса (t t ) где t задается регистром 15 (). В исходном состоянии на вьсходе управления таймера 8 установлен потенциал логического О, запрещающий прохождение тактовых импульсов для преобразования сигнала с выхода компаратора 11 в код аналого-цифровым преобразователем 5 до тех пор, пока на выходе Управление таймера 8 не установится уровень логической 1. Далее в аналого-цифровом преобразователе 5 осуществляется процесс поразрядного уравновешивания, по окончании которого на выходе Сброс преобразователя 5 появляется импульс сброса таймера 8 в исходное состояние и записи результата преобразования в регистры вычитателя 6. При появлении первого (после сброса таймера в исходное состояние) тактового импульса преобразователь 5 устанавливается в исходное состояние - процесс преобразования амплитуды входного сигнала в код закончен. Время преобразования аналого-цифрового преобразователя 5 t п-Т,,где п - разрядность преобразователя 5; период тактовых импульсов. По окончании преобразования на выходе компаратора 11 вновь устанавливается уровень логической 1 и повторно запускается таймер 8. Время повторного запуска подбирается во второй половине измеряемого импульса, тогда повторное преобразование акплитуды в код приходится на период .паузы t t2 (фиг. 5) и на выходе компаратора 11 установится логический О. В результате повторного преобразования на всех выходах АЦП 5 установятся нули. Процесс преобразования амцлитуды в код повторяется аналогично в каждый период питающего сельсин-датчик 1 напряжения. При этом изменение кода реверсивного счетчика 7 производится единичными приращениями, поступающими с вычитающего устройства 6 и имею1:и-тми c;:тo при Изменении кода преобразовятеля 5 (повороте вапа сельсина). Для получения единичных приращений в вьп{итаю1цем устройстве 6 (фиг.З) имеется два регистра 21 и 22, в которые с выхода ЦДЛ 5 записыкаются коды текущего и предыдущего преобра-золлния, используются разны( участей (тги915акяцих напряжений. Если амплитуда выходного импульсного напряжения нарастает с увеличением утла (з астка аЬ, cd, ef (фиг. 4), то для получения единичных приращений в вычитаю щем устройстве необходимо вычесть из текущего значения кода ot- предьдущее i)C,-.i, и наоборот, если с увеличением угла поворота вала амплитуда уменьшается (участки bc,ef ), то необходимо выполнить операци1оЫ| -с.. Запись текущего кода с преобразователя 5 в регистр вычитающего устройства 6 осуществляется по переднему фронту импульса с выхода d преоб разователя 5, что иллюстрирует таблица состояний за полный оборот вала сельсина. При повторном появлении импульса с выхода происходит перезапись из регистра кода текущего преобразования в регистр кода предьщущего преоб разования. Для вьшолнения операции вычитания вычитаемое преобразуется в обратный код. Для зтой цели в вычи тающем устройстве 6 (фиг. 1 и 3) выходы обоих регистров 21 и 22 поразрядно пoдкJiючёны к первым входам блоков 23 и 24 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, на вторые входы которых подан сигнал с выхода Ь- элемента И 3 (фиг. 1). При появлении логической 1. на этом выходе прямой код с регистра 21 текущего состояния блоком 3. .10 3 преобразуется в обратный, при появлении логического О код на выходе блока 23 элементов ИСКПЮЧАЩЕЕ: ШШ остается прямым. На сумматор вычитающего устройства 6 коды текущего и прёдьздущего преобразований поступают поразрядно через блоки 25 и 26 элементов И только при появлении разрешающего сигнала с выхода преобразователя 5 (фиг. 1), что повышает помехозащищенность схемы. На выход переноса сумматора PC ( фиг. 3) подано напр-чжение, соответствующее уровню логической 1 для преобразования обратного кода вычитаемого в дополнительный, в результате на выходе сумматора результат будет представлен либо в прямом коде 00...001, либо в дополнительном 11... 111. Блок 29 элементов И и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 28 (фиг. 3) анализируют код на выходе сумматора вы- . читающего устройства 6, т.е. при прямом коде в счетчик 7 заносится +1, при дополнительном -1. Таким образом, при вращении вала сельсиндатчика 1 в положительном направлении, на выходе счетчика 7 будет прямой код, при вращении в противоположном направлении - дополнительньй. Технико-экономический эффект предлагаемого преобразователя обусловлен его техническими преимуществами.

fe./

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент СМ № 4262666 кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Преобразователь угла поворота вала в код | 1973 |

|

SU470841A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| , | |||

Авторы

Даты

1984-11-23—Публикация

1982-12-03—Подача