достигается за счет того, что в состав устройства входят блок синхронизации 1, счетчик адреса 8, блок постоянной памяти 3, счетчик адреса 4, входной регистр 5, регистр констант 6, входной регистр 7, блок памяти 8, умножитель 9, сумматор 10, умножи1

Изобретение относится к цифровой вычислительной технике и может быть использовано в системах и устройствах цифровой обработки информации для преобразования временной последовательности действительных отсчетов входного сигнала в частотную и обратно-частотной последовательности во временную.

Целью Изобретения является упрощение устройства за счет использования алгоритма преобразования Хартли-Фурье.

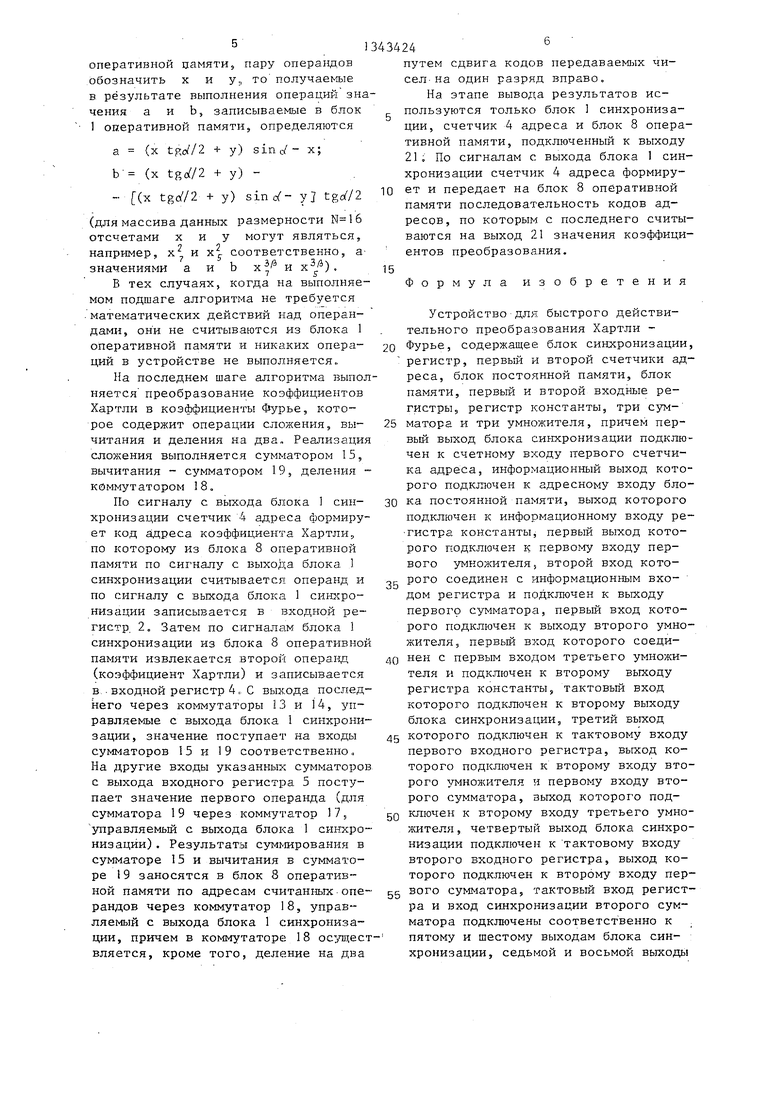

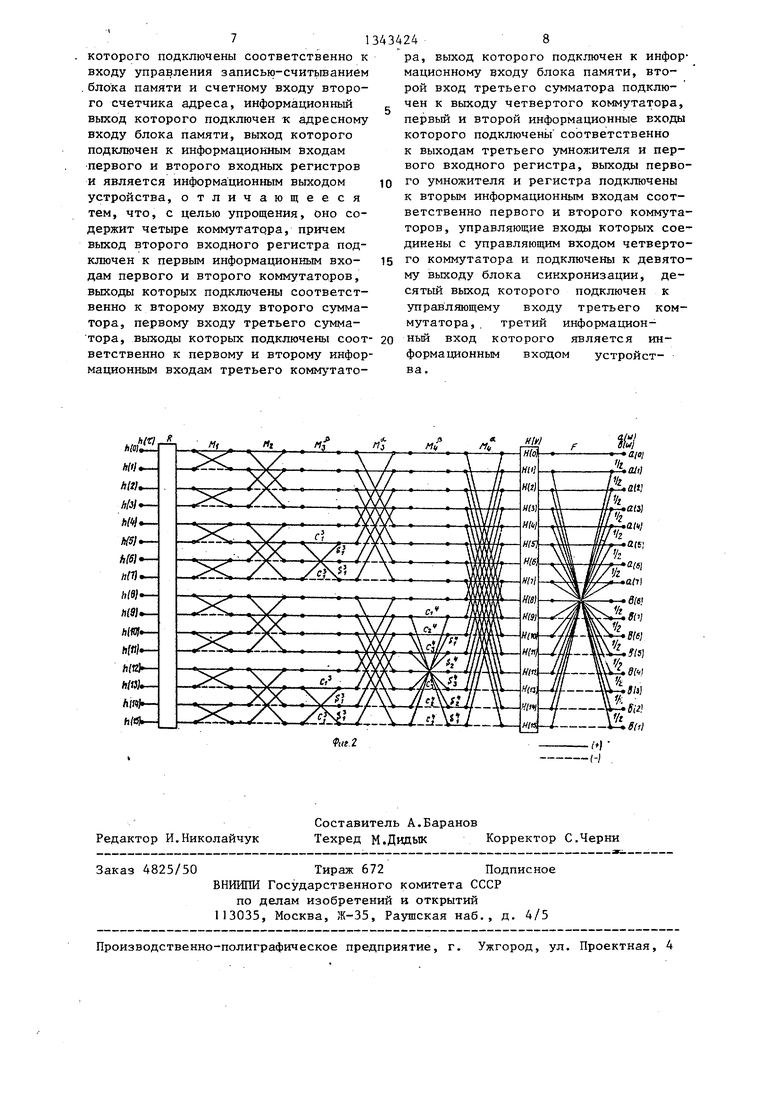

На фиг.1 показана струкстурная схема устройства; на фиг.2 - граф алгоритма Хартли-Фурье для размерности массива данных. N 16,

Устройство содержит блок 1 синхронизации, счетчик 2 адреса, блок 3 постоянной памяти, счетчик 4 адреса, входной регистр 5, регистр 6 конс- .TaHTj входной регистр 7, блок 8 оперативной памяти, умножитель 9, сумматор 10, умножитель 11, промежуточный регистр 12, коммутаторы 13 и 14, сумматор 15, умножитель 16, коммута.- торы 17 и 18, сумматор 19 и имеет информационньш вход 20 и информационный выход 21.

Выполнение гармонического преобразования включает четьфе этапа: ввод исходной информации,, вычисление коэффициентов Хартли, преобразование коэсЬФициентов Хартли в коэффициенты Фурье, вывод результатов преобразования ,

На этапе ввода используются только .блок ,1 синхронизации, счетчик 4 адреса, блок 8 оперативной памяти и коммутатор 18.

По сигналу с вьшода блока I синхронизации на управляющий вход коммутатора 18 последний производит под343424

тель 11, регистр 12, коммутаторы 13, и,- сумматор 15, умножитель 16, коммутаторы 17, 18, сумматор 19, инфор-- мационные вход 20 и выход 21 устройства и введены сбответствую- щие связи между узлами устройства. 2 ил.

ключение входа 20 к входу блока 8 оперативной памяти. Счетчик 4 адреса формирует и последовательно передает на вход блока 8 оперативной памяти двоично-инверсную последовательность адресов, по которой в последний записывается исходная информация и тем самым выполняется шаг R преобразования в соответствии с графом на фиг.2. Этап вычисления коэффициентов

Хартли включает в себя два вида процедур. Первая процедура не содержит операций.умножения и реализуется при выполнении первых двух шагов алгорит

ма преобразования Хартли и на последних подшагах (подшагах ) его последующих шагов.

Блок 1 синхронизации по своему выходу дает сигнал, по которому счетчик 4 адреса последовательно формирует пару адресов операндов, участвующих в данный момент в преобразовании. Первый операнд, считанный из блока 8 оперативной памяти по адресу из счетчика 4 адреса, по сигналу с выхода блока 1 синхронизации записывается в входной регистр 5, а второй операнд по сигналу с выхода блока 1 синхронизации - в входной регистр 7 .

С выхода входного регистра 5 первый операнд поступает на вход сумматора 15 и через коммутатор 17, управляемый с выхода блока 1 синхронизации, на вход сумматора 19. Второй операнд

с выхода входного регистра 7 через коммутаторы 13 и 14, управляе1 1е с выхода блока 1 синхронизации, поступают на сумматоры 15 и 19 соответственно. Управляющий сигнал по выходу

блока 1 синхронизации задает на сумматоре 15 выполнение операции сложения. Сумматор 19 постоянно работает в режиме вычитания из операнда, пос

тупающего на один его вход, операнда по другому входу. Результат суммирования с выхода сумматора 15 через коммутатор 18, управляемый по выходу блока 1 синхронизации, поступает в блок 8 оперативной памяти и фиксиру- ,ется в нем по адресу первого из считанной пары операндов. Результат вы- :читания из сумматора 19 записывается в блоке 8 оперативной памяти на место второго операнда. Адреса записи поступают с выхода счетчика 4 адреса Затем из блока 8 оперативной памяти производится считывание в входные регистры 5 и 7 очередных операндов и процедура обработки повторяется.

Вторая процедура содержит операции умножения на тригонометрические коэффициенты и реализуется на всех шагах алгоритма, исключая первые два и последний. Здесь по сигналу с выхода блока 1 синхронизации счетчик 4 адреса задает в блок 8 оперативной памяти код, по которому из него по сигналу .с выхода блока 1 синхронизации считывается первый операнд и фиксируется в входном регистре 5 по сигналу с выхода блока 1 синхронизации. Одновременно по сигналу с выхода блока 1 синхронизации счетчик 2 адреса формирует и подает на блок 3 постоянной памяти код требуемого тригонометрического коэффициента. Значение коэффициента считывается из блока 3 постоянной памяти и фиксируется в регистре 6 констант по сигналу с выхода блока 1 синхронизации. Длина слова блока 3 постоянной памяти и, соответственно, длина регистра 6 констант в два раза превьшают длину слова остальных блоков устройства При этом в первой части слов, считываемых из блока 3 постоянной памяти и хранимых в регистре 6 констант, содержатся значения тангенсов, которые передаются в качестве сомножителей на умножители 9 и 16, а во второй половине - значения синусов, которые поступают на вход первого сомножителя умножителя 11.

В умножителе 9 происходит перемножение операнда, поступающего с выхода входного регистра 5, на тригонометрический коэффициент, приходящий с выхода регистра 6 констант, и результат передается на вход суммато ра 10. На другой вход сумматора 10 поступает значение второго операнда с

5

0

5

0

5

0

5

0

5

выхода входного регистра 7, которое было записано в последний из блока 8 оперативной памяти по сигналу с выхода блока 1 синхронизации. Адрес второго операнда задается в блок 8 оперативной памяти из счетчика 4 адреса по сигналу с выхода блока 1 синхронизации. Сумматор 10 вьтолняет сложение значений, поступивших на его вы- ходы, результат передается на вход умножителя 11 и на промежуточный регистр 12, где он фиксируется по сигналу с выхода блока 1 синхронизации.

На вход умножителя 11 поступает значение синусного коэффициента с выхода регистра 6 констант, произведение передается на вход коммутатора 13 и по сигналу с выхода блока 1 синхронизации поступает на вход сумматора 15, на другом входе которого имеется код операнда с выхода входного регистра 5. С выхода блока 1 синхронизации на управляющий вход сумматора 15 поступает сигнал, задающий в нем выполнение вычитания операнда по первому входу из операнда по второму входу. Результат операции передается на входы коммутатора 18 и умножителя 16. По сигналу с выхода блока I синхронизации коммутатор 18 передает поступивщее на его вход значение в блок 8 оперативной памяти, где оно по сигналу с выхода блока i синхронизации записывается на место считанного первым операнда, адрес которого задается счетчиком 4 адреса по команде с выхода блока 1 синхронизации.

На вход умножителя 16 с выхода регистра 6 констант поступает зйачение тангенсного коэффициента. Получаемое на выходе умножителя 16 произведение через коммутатор 17, управляемый сигналом с выхода блока 1 синхронизации, подается на вход сумматора 19, на другой вход которого с выхода промежуточного регистра 12 через коммутатор 14, управляемый с выхода блока 1 синхронизации, поступает значение второго операнда. Результат вычитания с выхода сумматора 19 подается через коммутатор 18 в блок 8 оперативной памяти и фиксируется в нем по сигналу с выхода блока 1 синхронизации по адресу второго из считанной пары операндов, задаваемому счетчиком 4 адреса по сигналу с выхода блока 1 синхронизации. Таким образом, если исходную, считанную из блока 1

оперативной памяти, пару опера1адов обозначить X и у, то получаемые в результате выполнения операций зна чения а и Ь, записываемые в блок 1 оперативной памяти, определяются

а (х tpc//2 + у) sine/- х;

Ь- (х tp, + у) - (х tg(y /2 + у) sincY- yj tgof-yz

(для массива данных размерности отсчетами х и у могут являться, например, х, и х| соответственно, а- значениями а и b и х) .

В тех случаях, когда на выполняемом подшаге алгоритма не требуется

математических действий над операндами, они не считываются из блока 1 оперативной памяти и никаких операций в устройстве не выполняется,.

На последнем шаге алгоритма выпол няется преобразование коэффициентов Хартли в коэффициенты Фурье, которое содержит операции сложения, вычитания и деления на два. Реализация сложения выполняется сумматором 15, вычитания - сумматором 19, деления - коммутатором 18.

По сигналу с выхода блока 1 синхронизации счетчик 4 адреса формирует код адреса коэффициента Хартли, по которому из блока 8 оперативной памяти по сигналу с выхода блока 1 синхронизации считывается операнд и по сигналу с выхода блока 1 синхронизации записывается в входной регистр. 2, Затем по сигналам блока 1 синхронизации из блока 8 оперативной памяти извлекается второй операвд (коэффициент Хартли) и записывается в,. входной регистр 4. С вьпсода последнего через коммутаторы 13 и 14, управляемые с выхода блока 1 синхронизации, значение поступает на входы сумматоров 15 и 19 соответственно. На другие входы указанных сумматоров с выхода входного регистра 5 поступает значение первого операнда (для сумматора 19 через коммутатор 17,

управляемый с выхода блока 1 си1-гхро- низации). Результаты суммирования в сумматоре 15 и вычитания в сумматоре 19 заносятся в блок 8 оперативной памяти по адресам считанныхоперандов через коммутатор 18, управ- ляeIv ый с выхода блока 1 синхронизации, причем в коммутаторе 18 ос:/щест вляется, кроме того, деление на два

43424

путем сдвига кодов передаваемых чисел- на один разряд вправо.

На этапе вывода результатов используются только блок 1 синхронизации, счетчик 4 адреса и блок 8 оперативной памяти, подключенный к выходу 21, По сигналам с выхода блока 1 синхронизации счетчик 4 адреса формиру- 10 ет и передает на блок 8 оперативной памяти последовательность кодов адресов, по которым с последнего считываются на выход 21 значения коэффици- ентов преобразования.

15

Формула изобретения

Устройство для быстрого действительного преобразования Хартли 20 Фурье, содержащее блок синхронизации, регистр, первый и второй счетчики адреса, блок постоянной памяти, блок памяти, первьщ и второй входные регистры, регистр константы, три сум25 матера и три умножителя, причем первый выход блока синхронизации подключен к счетному входу первого счетчика адреса, информационный выход которого подключен к адресному входу бло30 ка постоянной памяти, выход которого подключен к информационному входу ре- гистра константы, первый выход которого подключен к первому входу первого умножителя, второй вход кото- ос рого соединен с информационным входом регистра и подключен к выходу первого сумматора, первый вход которого подключен к выходу второго умножителя, первый вход которого соеди40 нен с первым входом третьего умножителя и подключен к второму выходу регистра константы, тактовый вход которого подключен к второму выходу блока синхронизации, третий выход

45 которого подключен к тактовому входу первого входного регистра, выход которого подключен к второму входу второго умножителя и первому входу второго сумматора, выход которого под5Q ключен к второму входу третьего умножителя, четвертый выход блока синхронизации подключен к тактовому входу второго входного регистра, выход которого подключен к второму входу перgg вого сумматора, тактовый вход регистра и вход синхронизации второго сумматора подключены соответственно к . пятому и шестому выходам блока синхронизации, седьмой и восьмой выходь

71

которого подключены соответственно к входу управления записью-считьгоанибм блока памяти и счетному входу второго счетчика адреса, информационный выход которого подключен к адресному входу блока памяти, выход которого подключен к информационным входам первого и второго входных регистров и является информационным выходом устройства, отличающееся тем, что, с целью упрощения, оно содержит четыре коммутатора, причем выход второго входного регистра подключен к первым информационным входам первого и второго коммутаторов, выходы которых подключены соответственно к второму входу второго сумматора, первому входу третьего сумматора, выходы которых подключены соот ветственно к первому и второму инфор мационным входам третьего коммутато 434248

ра, выход которого подключен к информационному входу блока памяти, второй вход третьего сумматора подключен к выходу четвертого коммутатора, первый и второй информационные входы которого подключень соответственно к выходам третьего умножителя и первого входного регистра, выходы перво- 10 го умножителя и регистра подключены к вторым информационным входам соответственно первого и второго коммутаторов, управляющие входы которых соединены с управляющим входом четверто- 15 го коммутатора и подключены к девятому выходу блока синхронизации, десятый выход которого подключен к управляющему входу третьего коммутатора, третий информацион- 20 ный вход которого является информационным входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации быстрого преобразования Хартли | 1987 |

|

SU1444815A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| Устройство для реализации быстрого преобразования Фурье | 1984 |

|

SU1233166A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для реализации быстрого преобразования Фурье | 1989 |

|

SU1672469A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для реализации быстрого преобразования Фурье последовательности с нулевыми элементами | 1983 |

|

SU1119025A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано в системах и устройствах цифровой обработки сигналов ДЛЯ преобразования временной последовательности действительных отсчетов сигналов в частотную и обратно- частотной последовательности во временную. Цель изобретения - упрощение устройства. Поставленная цель сл со 4 СО i(ik ю 4

л/г/

Редактор И.Николайчук

Составитель А.Баранов

Техред М.Дидык Корректор С.Черни

Заказ 4825/50Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Процессор быстрого преобразования фурье | 1979 |

|

SU788114A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для реализации быстрого преобразования фурье | 1977 |

|

SU734708A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-07—Публикация

1986-04-07—Подача