347153

Изобретение относится к импульс

НОЙ технике и может быть использовано в качестве С триггера в интегральных логических цифровых устройствах.

Цель изобретения повышение помехоустойчивости D-триггера на полевых транзисторах.

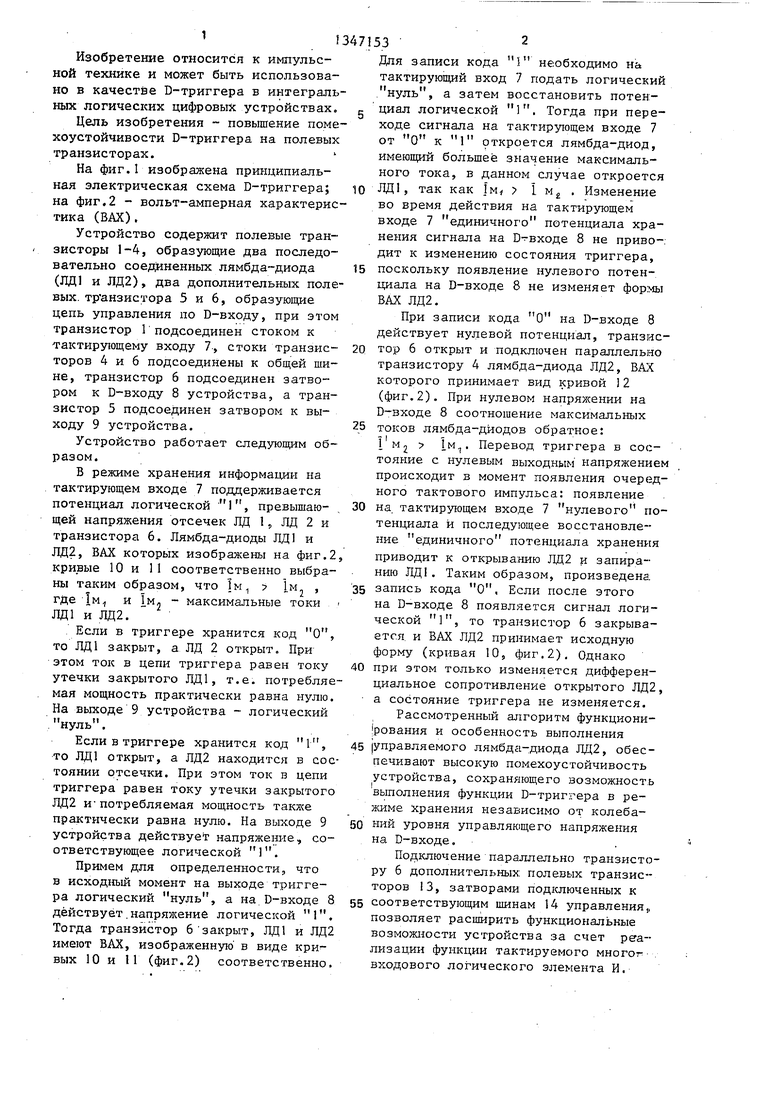

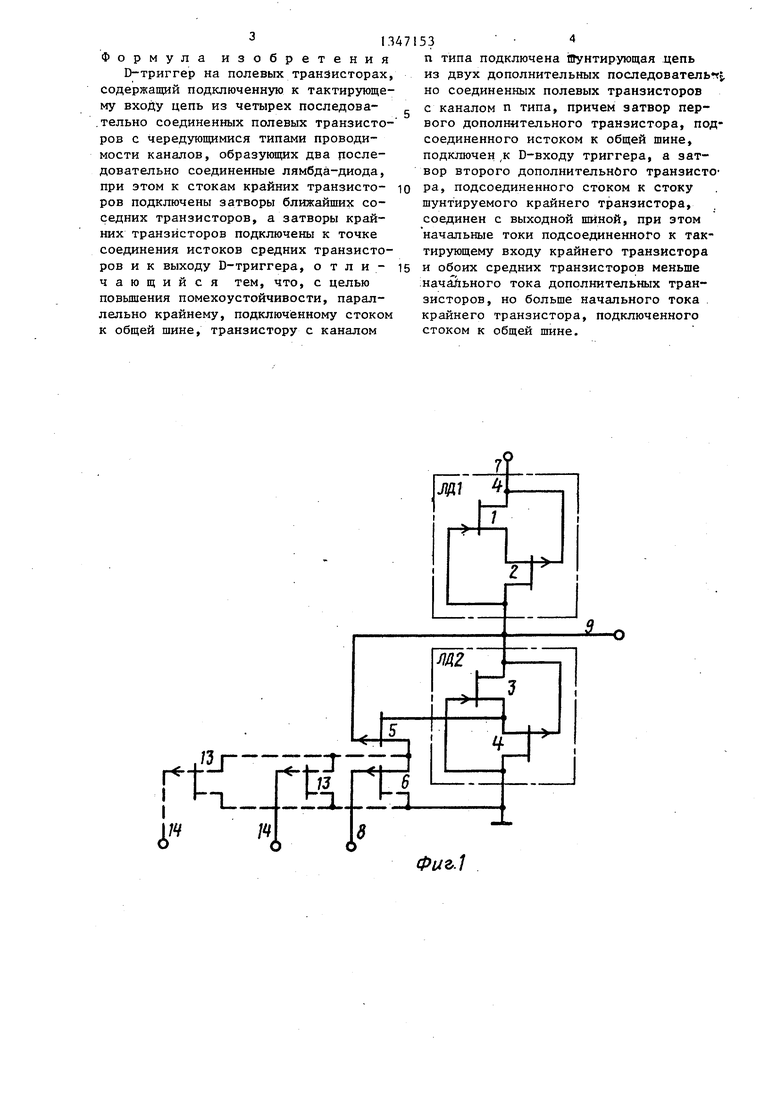

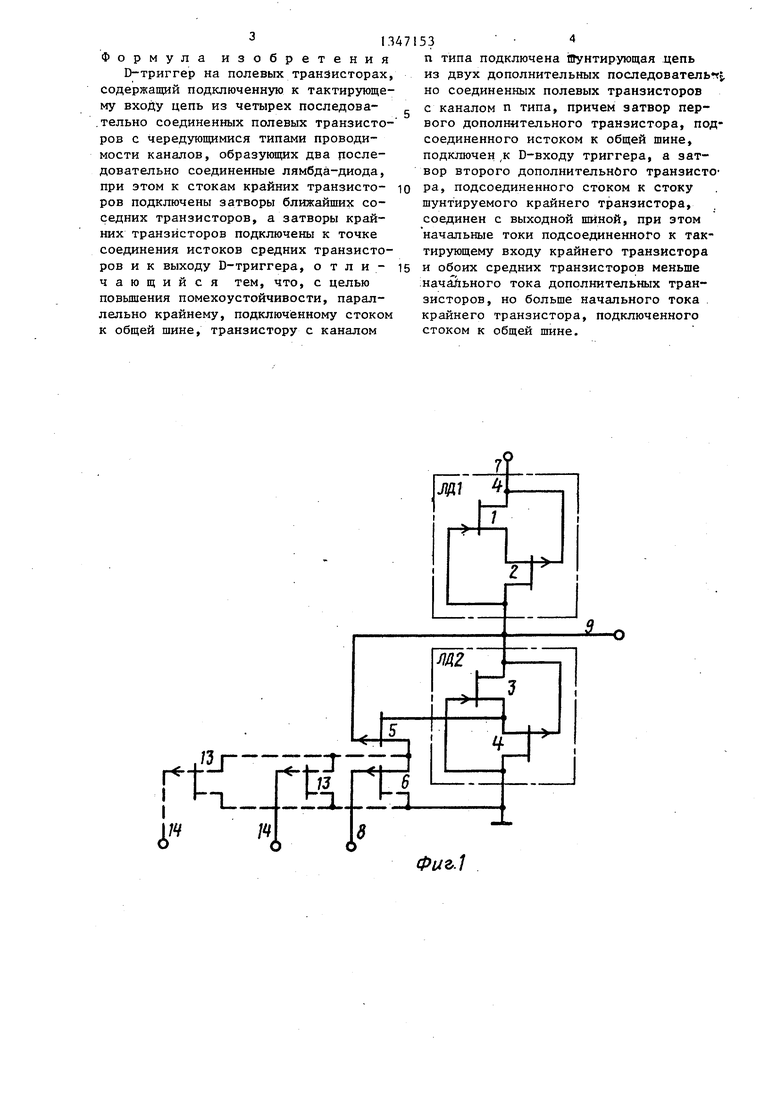

На фиг.1 изображена принципиальная электрическая схема D-триггера; на фиг.2 - вольт-амперная характеристика (ВАХ).

Устройство содержит полевые транзисторы 1-4, образующие два последовательно соединенных лямбда-диода (ЛД1 и ЛД2), два дополнительных полевых, тр анзистора 5 и 6, образующие цепь управления по D-входу, при этом транзистор Г подсоединен стоком к тактирующему входу 7., стоки транзисторов 4 и 6 подсоединены к общей шине, транзистор 6 подсоединен затвором к D-входу 8 устройства, а транзистор 5 подсоединен затвором к выходу 9 устройства.

Устройство работает следующим образом.

В режиме хранения информации на тактирующем входе 7 поддерживается потенциал логической , превышаю- щей напряжения отсечек ЛД 1, ЛД 2 и транзистора 6. Лямбда-диоды ЛД и ЛД2, ВАХ которых изображены на фиг.2 кривые 10 и 11 соответственно выбраны таким образом, что 1м, где IM.,

iMj ,

и IM, - максимальные токи ДД1 и ЛД2.

. Если в триггере хранится код О, то ЛД1 закрыт, а ЛД 2 открыт. При этом ток в цепи триггера равен току утечки закрытого ЛД1, т.е. потребляемая мощность практически равна нулю. На выходе 9 устройства - логический .нуль.

Если в триггере хранится код 1, то ЛД1 открыт, а ЛД2 находится в состоянии отсечки. При этом ток в цепи триггера равен току утечки закрытого ДД2 и-потребляемая мощность также практически равна нулю. На выходе 9 устройства действуе г напряжение, соответствующее логической 1.

Примем для определенности, что в исходный момент на выходе триггера логический нуль, а на D-входе 8 действует.напряжение логической 1. Тогда транзистор 6 закрыт, ЛД1 и ДД2 имеют ВАХ, изображенную в виде кривых 10 и 11 (фиг.2) соответственно.

Для записи кода 1 необходимо на.

тактирующий вход 7 подать логический

нуль.

а затем восстановить потенII 1 ч

циап логической 1 . Тогда при переходе сигнала на тактирующем входе 7 от О к 1 откроется лямбда-диод, имеющий большее значение максимального тока, в данном случае откроется ЛД1, так как 1м| 1 м . Изменение во время действия на тактирующем входе 7 единичного потенциала хранения сигнала на D-входе 8 не приводит к изменению состояния триггера, поскольку появление нулевого потенциала на D-входе 8 не изменяет ВАХ ЛД2.

При записи кода О на D-входе 8 действует нулевой потенциал, транзистор 6 открыт и подключен параллельно транзистору 4 лямбда-диода ЛД2, ВАХ которого принимает вид кривой I2 (фиг.2). При нулевом напряжении на Б входе 8 соотношение максимальных токов лямбда-диодов обратное:

I MJ IM,. Перевод триггера в состояние с нулевым выходным напряжением происходит в момент появления очередного тактового импульса: появление на. тактирующем входе 7 нулевого по

5

тенциала и последующее восстановление единичного потенциала хранения приводит к открыванию ДД2 и запиранию ЛД1 . Таким образом, произведена, запись кода О, Если после этого на D-входе 8 появляется сигнал логической 1, то транзистор 6 закрывается, и ВАХ ЛД2 принимает исходную форму (кривая 10, фиг,2), Однако

0 при этом только изменяется дифференциальное сопротивление открытого ЛД2, а состояние триггера не изменяется.

Рассмотренный алгоритм функциони- рования и особенность выполнения

5 |управляемого лямбда-диода ЛД2, обеспечивают высокую помехоустойчивость устройства, сохраняющего возможность выполнения функции D-триггера в режиме Хранения независимо от колеба0 НИИ уровня управляющего напряжения на D-входе.

Подключение параллельно транзистору 6 дополнительных полевых транзисторов 13, затворами под1шюченных к

5 соответствующим шинам 14 управления,, позволяет расцирить функциональные возможности устройства за счет реализации функции тактируемого многог-. входового логического элемента И.

Формула изобретения D-триггер на полевых транзисторах, содержащий подключенную к тактирующему входу цепь из четырех последова- .тельно соединенных полевых транзисторов с чередующимися типами проводимости каналов, образующих два последовательно соединенные лямбда-диода, при этом к стокам крайних транзисторов подключены затворы ближайших соседних транзисторов, а затворы крайних транзисторов подключены к точке соединения истоков средних транзисторов и к выходу D-триггера, о т л и - чающийся тем, что, с целью повьшения помехоустойчивости, параллельно крайнему, подключённому стоком к общей шине, транзистору с каналом

5

7

5

0

153 4 п типа подключена ЯГунтирующая .цепь из двух дополнительных последоватепь г. но соединенных полевых транзисторов с каналом п типа, причем затвор первого дополнительного транзистора, подсоединенного истоком к общей шине, подключен ,к D-входу триггера, а затвор второго дополнительного транзистора, подсоединенного стоком к стоку шунтируемого крайнего транзистора, соединен с выходной щиной, при этом начальные токи подсоединенного к тактирующему входу крайнего транзистора и обоих средних транзисторов меньше начального тока дополнительных транзисторов, но больше начального тока . крайнего транзистора, подключенного стоком к общей шине.

Фиг.1

12

;/

.2

Редактор Г.Волкова

Составитель Э.Сапежко

Техред И.Верес Корректор В.Бутяга

Заказ 5126/50 Тираж 899 -Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий И3035, Москва, , Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, кл. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Компаратор тока | 1986 |

|

SU1370758A1 |

| Устройство с лямбда-характеристикой | 1989 |

|

SU1647886A1 |

| Генератор импульсов | 1983 |

|

SU1163462A1 |

| Запоминающий элемент | 1980 |

|

SU903980A1 |

| Цифровое управляемое сопротивление | 1974 |

|

SU530447A1 |

| ПОЛУПРОВОДНИКОВОЕ КЛЮЧЕВОЕ УСТРОЙСТВО С ПОЛЕВЫМ УПРАВЛЕНИЕМ | 2001 |

|

RU2199795C2 |

| Резистивный узел сеточной модели | 1983 |

|

SU1120366A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ | 1987 |

|

SU1530058A1 |

| Генератор импульсов | 1977 |

|

SU661721A1 |

| Устройство для температурной защиты группы электродвигателей | 1989 |

|

SU1700672A2 |

Изобретение относится к импульсной технике и может быть использовано в качестве D-триггера в интегральных логических цифровых устройствах. Цель изобретения - повышение помехот устойчивости D-триггера на полевых транзисторах. Устройство содержит подкпюченну к тактирующему входу цепь из четырех последовательно соединенных полевых транзисторов с чередующимися типами проводимости каналов, образующих два последовательно соединенных лямбда-диода. При эуом параллельно крайнему, подключенному стоком к общей шине транзистору подключена шунтиру5рщая цепь из двух соединенных последовательно транзисторов с тем же типом проводимости канала. Затвор первого дополнительного транзистора, подсоединенного истоком к общей шине, подключен к D-входу триггера, а затвор второго дополнительного транзистора, подсоединенного стоком к стоку шунтируемого крайнего транзистора, соединен с выходом устройства. 2 ил. i (Л .00 сл со

| ТРИГГЕР НА ПОЛЕВЫХ ТРАНЗИСТОРАХВПТБФОНД | 1973 |

|

SU453785A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-10-23—Публикация

1984-09-20—Подача