(54) ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания | 1980 |

|

SU928406A1 |

| Запоминающий элемент | 1978 |

|

SU788174A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| Устройство для контроля разряда источников питания постоянного тока | 1988 |

|

SU1629864A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| СТАБИЛИЗАТОР НАПРЯЖЕНИЯ ПИТАНИЯ ЭЛЕКТРОННЫХ СХЕМ | 2019 |

|

RU2727713C1 |

| Усилитель считывания на полевых транзисторах | 1987 |

|

SU1464210A1 |

| Устройство для контроля разряда источников питания постоянного тока | 1990 |

|

SU1798710A1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

| Способ считывания информации из элементов памяти на полевых транзисторах и формирователь сигналов считывания | 1989 |

|

SU1697118A1 |

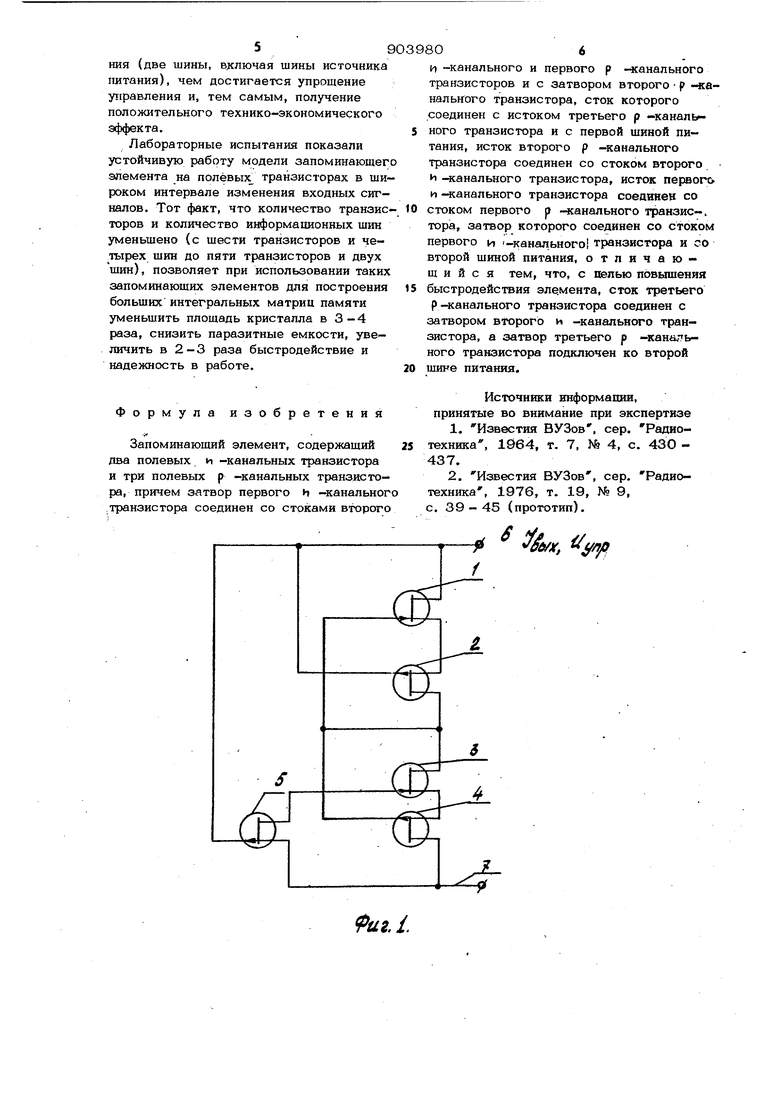

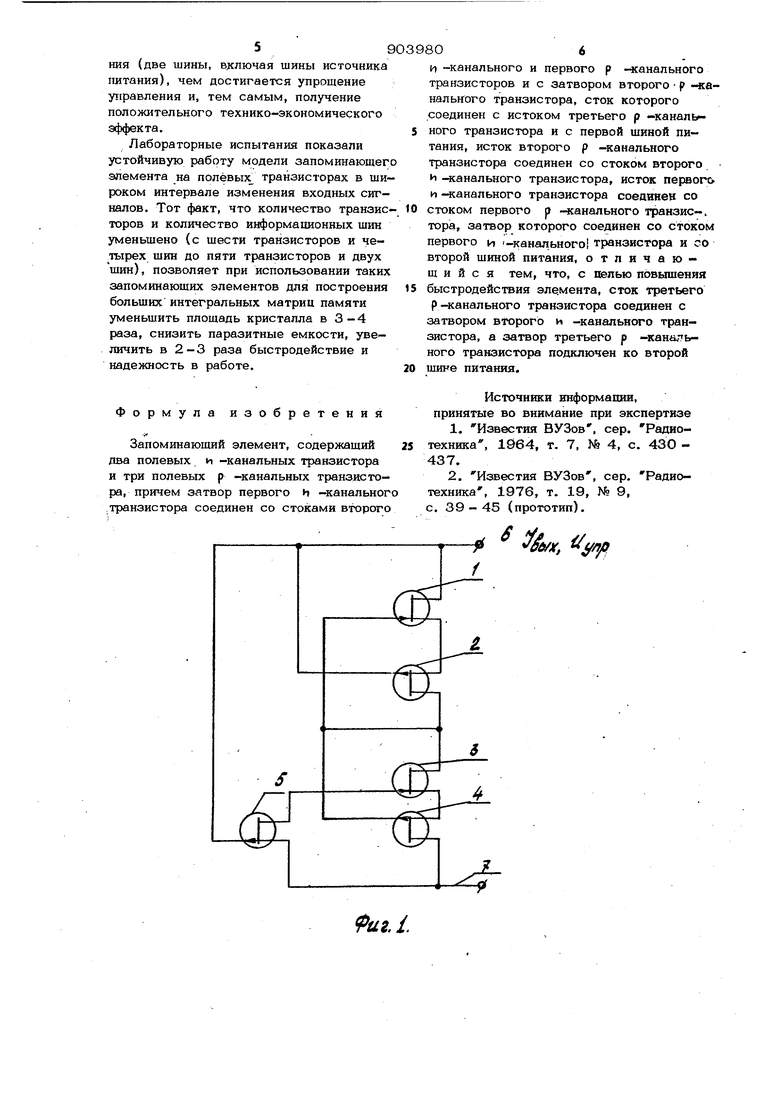

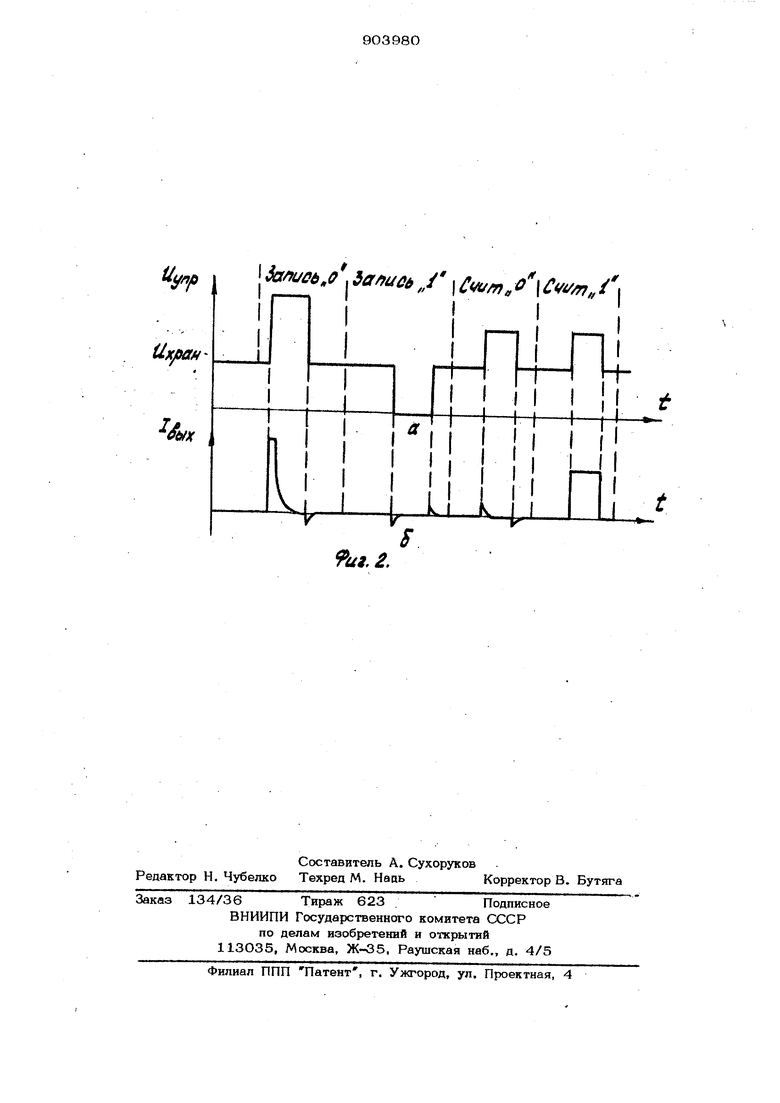

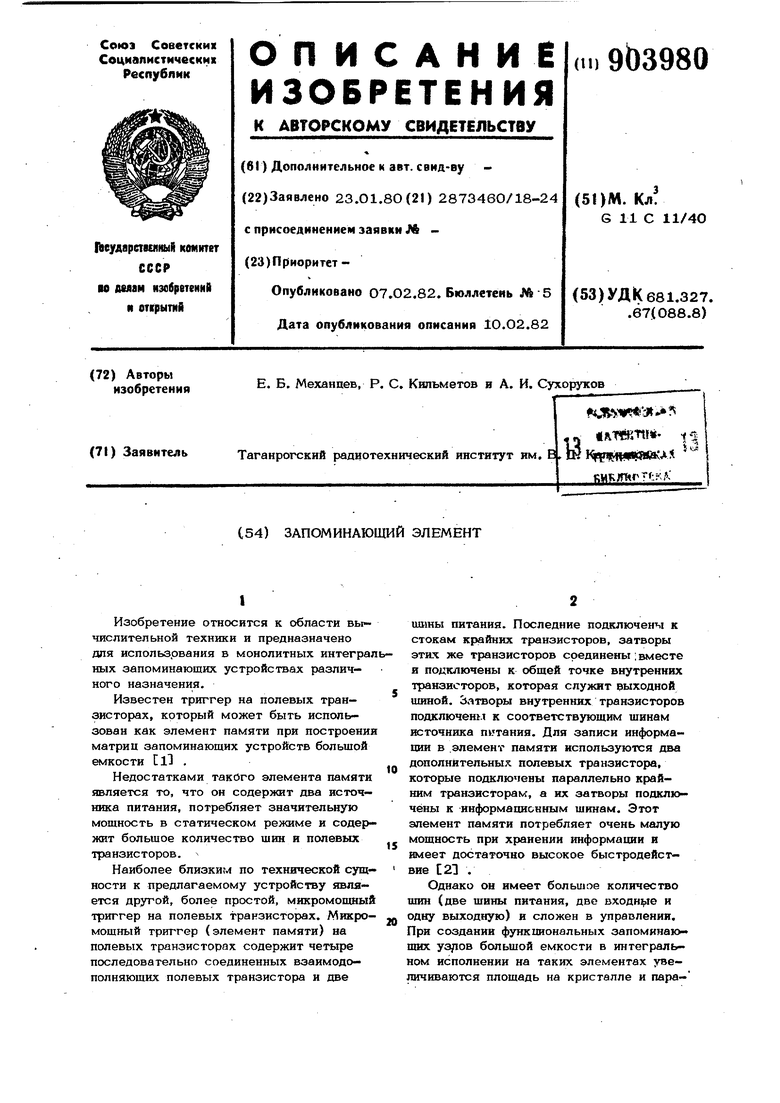

Изобретение относится к области вычислительной техники и предназначено для использования в монолитных интеграл ных запоминающих устройствах различного назначения. . Известен триггер на полевых транзисторах, который может быть использован как элемент памяти при построении матриц запоминающнх устройств большой емкости Ell . Недостатками такого элемента памяти является то, что он содержит два источника питания, потребляет значительную мощность в статическом режиме и содержит большое количество шин и полевых транзисторов. Наиболее близким по технической сущности к предлагаемому устройству является другой, более простой, микромощный триггер на полевых транзисторах. Микромощный триггер (элемент памяти) на полевых транзисторах содержит четыре последовательно соединенных взаимодополняющих полевых транзистора н две шины питания. Последние подключены к стокам крмзйних тринзисторов, затворы этих же транзисторов соединены ; вместе и подключены к общей точке внутренних транзисторов, которая служит выходной шиной. Затворы внутренних транзисторов подключены к соответствующим шинам источника питания. Для записи информации в .элемент памяти используются два дополнительных полевых транзистора, которые подключены параллельно крайним транзисторам, а их затворы подключены к информашюнным шинам. Этот элемент памяти потребляет очень малую мощность при хранении информации и имеет достаточно высокое быстродействие 23 . Однако он имеет большое количество шин (две шины питания, две входн1 1е и одну выходную) и сложен в управлении. При создании функциональных запоминающих y3fioB большой емкости в интегральном исполнении на таких элементах увеличиваются площадь на кристалле и пара- 390 зитные емкости, снижается .быстродействие и надежность в работе. Цель изобретения - упрощение запоминающего элемента и повышение его быстродействия за счет уменьшения паразитных емкостей. Указанная цель достигается тем, что в запоминающем элементе, содержащем два полевых и -канальных транзистора и три полевых р -канальных транзистора причем затвор первого и -канального транзистора соединен со стоками второго и -канального и первого р -канального транзисторов, и с затвором второго р-канального транзистора, сток которого сцеД1инен с истоком третьего р -канального транзистора и с первой шиной питания, исток- второго р-гканального транзистора соединен со стоком второго и -канального транзистора, исток первого и -«анального транзистора соединен со стоком первого р -канального транзистора, затвор которого соединен со стоком первого и -канального транзистора и со второй шиной питания, сток третьего р нка нального транзистора соединен с затвором второго и -канального транзистора, а затвор третьего р -канального транзистора подключен ко второй шине питания. На фиг. 1 изображена принципиальная схема конкретного исполнения запоминаю щего элемента ; на фиг. 2 - временные диаграммы работы. Запоминающий элемент содержит пять полевых транзисторов: первый транзистор 1 и -типа, первый транзистор 2 р -типа второй транзистор 3 и -типа, второй транзистор 4 р -типа, третий транзистор 5 р -типа - и две шины 6 и 7 питания подключенные соответственно к стокам крайних транзисторов. Шины питания совмещены с шинами управления Затворы крайних транзисторов соединены вместе и подключены к общей точке тран зисторов 2 и 3, затвор первого транзистора р -типа подключен к-шине б питания, а в цепь затвора второго транзистора и -типа включен третий транзистор 5 Р -типа, сток которого соединен с затвором второго транзистора и -типа, исток - с шиной 7 питания, а затвор - с шиной 6 питания. Напряжение отсечки третьего транзистора 5 р -типа выбрано таким, что оно превьпиает сумму напряжений отсечки пары транзисторов 1 и 2 и транзисторов 3 и 4. 0 Запоминающий элемент работает следующим образом. Транзисторы 1 и 2, 3 и 4 образуют попарно приборы с отрицательным сопро- тивлением - Л -диоды, включенные последовательно. Л -диоды выбраны таким образом, что максимальный ток верхнего диода больше максимального тока нижнего диода. В режиме хранения информации на шине 6 поддерживается положительный потенциал (U хрон ), величина которого больше напряжения отсечки Л -диодов, но меньше напряжения отсечки третьего транзистора 5 р -типа. Если в запоми- нающем элементе хранится код О, то верхний Л -диод закрыт, а нижний открыт. Ток в цепи запоминающего элемента равен остаточному току закрытого Л.:-тДиода. Коду 1 соответствует состояние, при котором верхний Л -диод открыт, а нижний закрыт. Ток в цепи также равен току утечки запертого -Л- -диода. Таким образом, в статических состояниях О и ток в цепи запомршаюшего элемента практически не протекает и потребляемая мощность составляет малую величину. При записи кода О в шину 6 подается положительный импульс, величина которого превьпиает напряжение отсечки третьего транзистора 5 р -типа. Транзистор 5 закрывается и вольт-амперная характеристика нижнего А -диода деформируется в пентодную, а напряжение на его аноде уменьшается до нуля. При снятии импульса запоминающий элемент сохраняет это состояние. Для записи кода в шине 6 потенциал уменьшается от и хран до нуля, при этом за счет того, что максимальный. ток верхнего А -диода больше максимального тока нижнего А -диода, при снятии импульса потенциал на аноде нижнего А -диода увеличивается до Охран, и запоминающий элемент сохраняет это состояние. Считывание информации осуществляется подачей импульса положительной полярности в шину 6 амплитуда которого выбирается из условия неразрушающего считывания и,.ц,п, С Ujan, при этом в выходной цепи запоминающего элемента течет большой информационный ток, если хранится код 1, и малый, если хранится код О . Таким образом, использование в запоминающем элементе третьего транзистора Р -типа позволяет уменьшить общее количество шин до минимального значе- ния (две шины, вдспючая шины источника питания), чем достигается упрощение управления и, тем самым, получение положительного технико-экономического эффекта. Лабораторные испытания показали устойчивую работу модели запоминающего элемента на полевых транзисторах в широком интервале изменения входных снггналов. Тот факт, что количество транзисторов и количество ишЦюрмационных шин уменьшено (с шести транзисторов и четарех шин до пяти транзисторов и двух шин), позволяет при использовании таких запоминающих элементов для построения больших интегральных матриц памяти уменьшить площадь кристалла в 3-4 раза, снизить паразитные емкости, увеличить в 2-3 раза быстродействие и надежность в работе.

Формула изобретения

Запоминающий элемент, содержащий два полевых и -канальных транзистора и три полевых р -канальных транзистора, причем затвор первого h -канального транзистора соединен со стоками второго 9

Источники информашш, принятые во внимание при экспертизе

с. 39 - 45 (прототип). 80 и -канального и первого р -«анального транзисторов и с затвором второгор -каналыгого транзистора, сток которого соединен с истоком третьего р -каналыного транзистора и с первой шиной питания, исток второго р -канального транзистора соединен со стоком второго и -канального транзистора, исток первого, и -канального транзистора соединен со .«.в V - j,,, .nnwF f стоком первого р -«анального гранзис-. тора, затвор которого соединен со стоком первого и -канального транзистора и со второй шиной питания, отличающ и и с я тем, что, с пелью повьшения быстродействия элемента, сток третьего р/ анального транзистора соединен с затвором второго и -канального транзистора, а затвор третьего р -канального транзистора подключен ко второй шине питания.

Г. .

иг. L

и,

fy/7/

UxjMiM9иг. г.

Авторы

Даты

1982-02-07—Публикация

1980-01-23—Подача