13

Изобретение относится к импульсной технике и может быть использовано в измерительных устройствах

Целью изобретения является повьпле- ние надежности путем упрощения счетного устройства

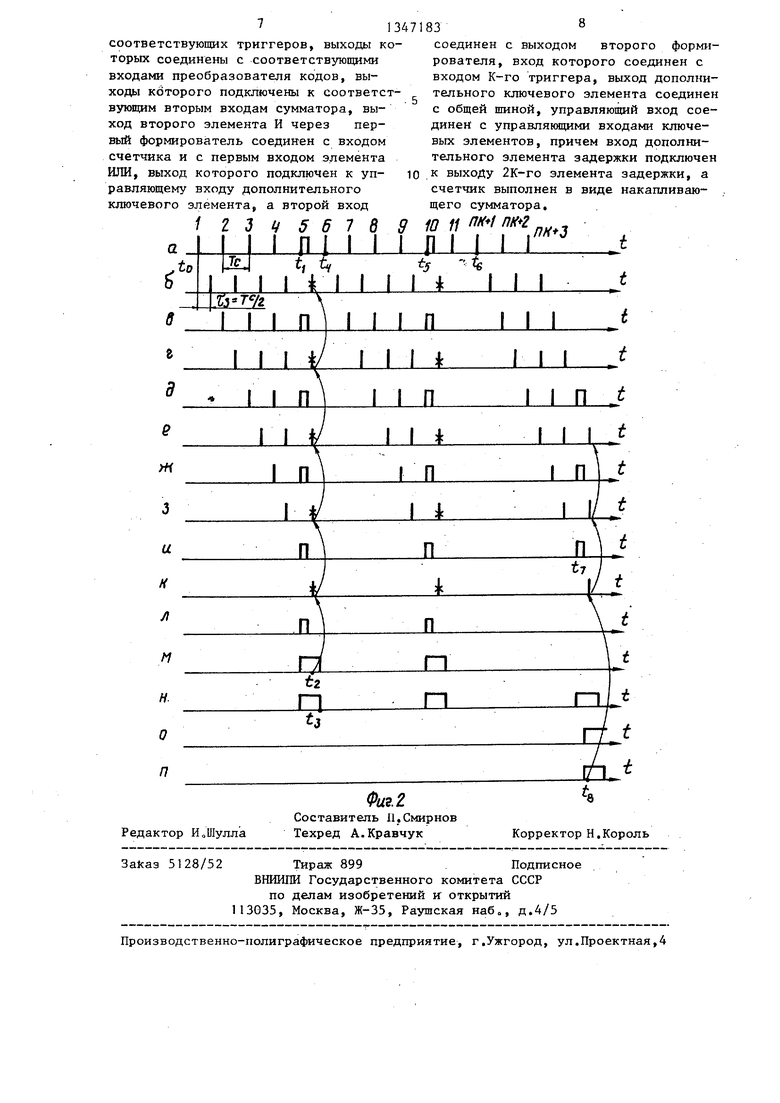

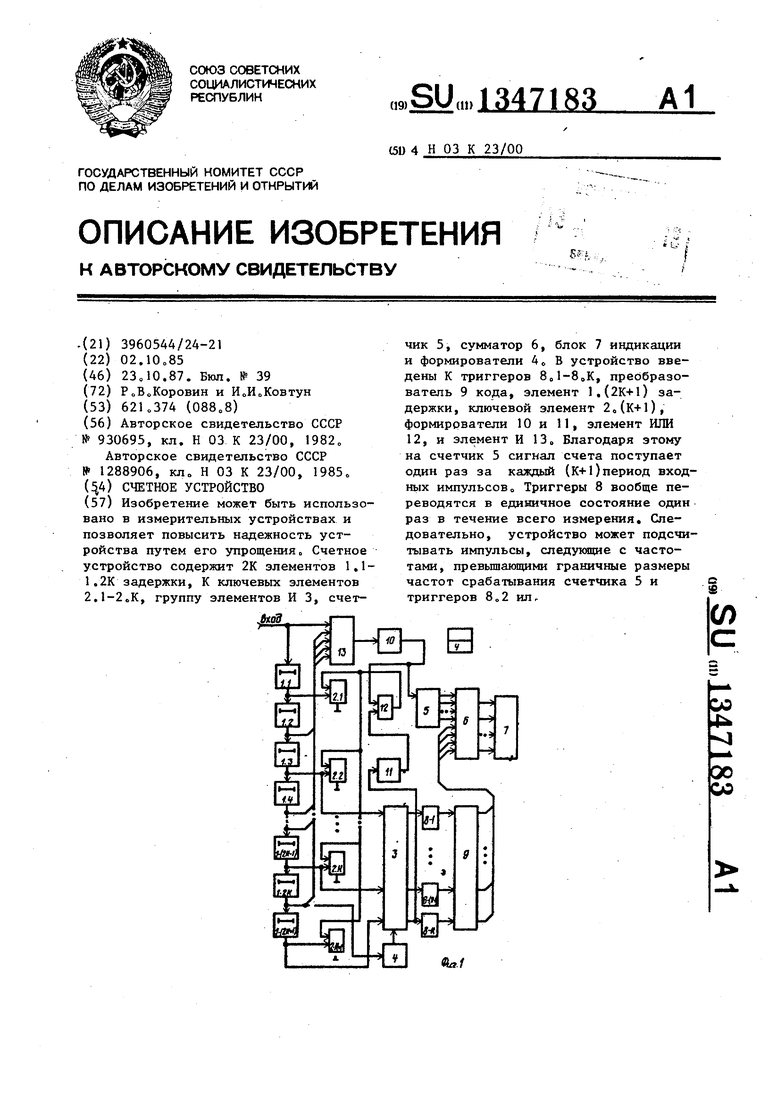

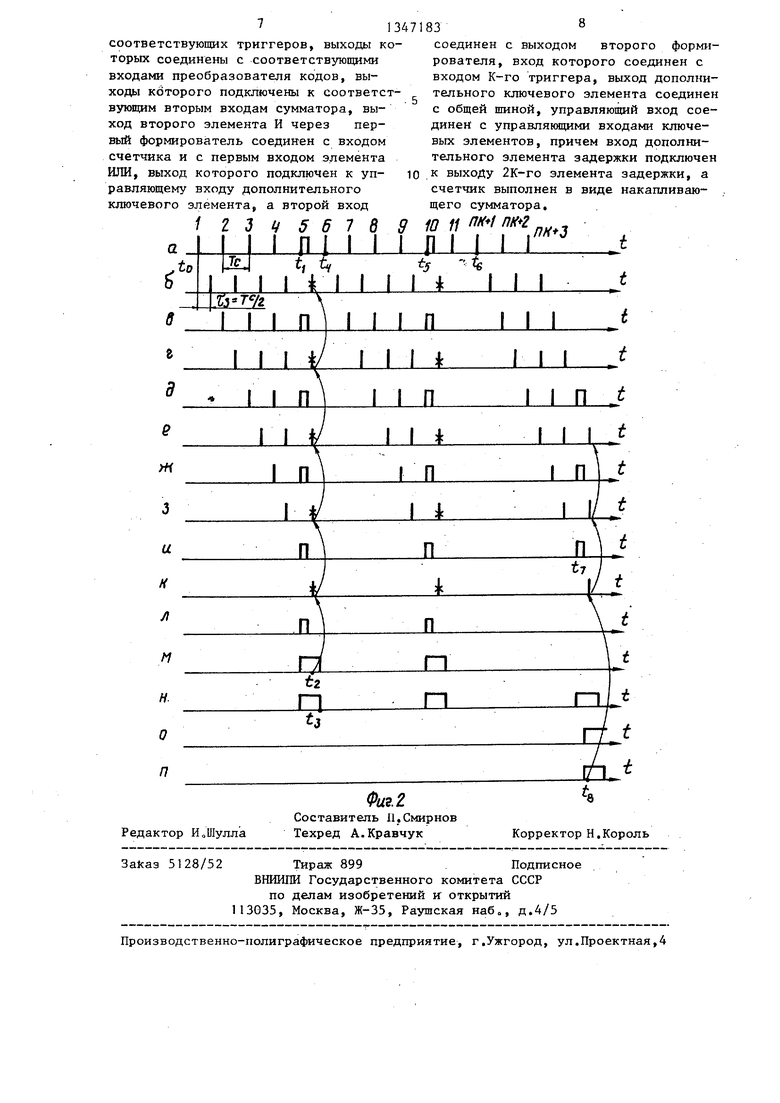

На фиг,, 1 представлена функциональная схема счетного устройства; на фиг о 2 - временные диаграммы, поясня- ющие его работу

Счетное устройство (фиг) содержит 2К посаедовательно соединенных элементов I„ - о2К задержки, вход первого из которых подключен к вхо- ду устройства, К ключевых элементов 2о1 - 2,К, управляющие входы которых объединены, выходы подключены к об- щей шине, группу первых элементов -И 3, первые входы каждого из которых соединены с выходом основного формирвателя 4, вход которого подключен к выходу 2К-ГО элемента 1,2К за,цержки.

счетчик 5, выходы которого соединены с соответствующими первыми входами сумматора 6, выходы которого подключены к соответствующим входам блока 7 индикации Устройство также содержит К триггеров 8о1 - 8оК, преобразователь 9 кодов, дополнительш;1й 2К+1-Й элемент „2К+1 -задержки, дополнительный К+1-Й ключевой элемент 2о(К+1), первый 10 и второй 1i формирователи, элемент ИЛИ 12 и второй элемент И 13 входы которого соединены с входами соответствующих нечетных элементов задержки, выходы которых соединены с входами соответствующих ключевых элементов, выходы всех нечетных элементов задержки, кроме первого, соединены с вторыми входами соответствующих первых элементов И 3 группьх, выходы которых подключены к входам соответствующих триггеров 8, выходы которых соединены с соответствующими входами преобразователя 9 кодов, выходы которого подключены к соотве т ствующим вторым входам сумматора 6, выход второго элемента И 13 через первый формирователь 40 соединен с входом счетчика 5 и с первым входом элемента ИЛИ 12, выход которого подключен к управляющему входу дополнительного ключевого элемента, а второй вход соединен с выходом второго формирователя 11, вход которого соединен с входом К-го триггера 8, выход дополнительн ого ю-почевого элемента 2,К+1 соединен с общей.шиной.

управляющий вход соединен с управляющими входами ключевых элементов, причем вход дополнительного элемента задержки подключен к выходу 2К-го элемента задержки, а счетчик выполнен в виде накапливающего сумматора.

Устройство работает следующим об- разомо

Все элементы I -1о(2К+1) задержки устройства выполнены идентичными, причем длительность задержки Т в каждом из этих элементов обеспечивает условие

Т,/2,

где Tf - стабильный период повторения входных сигналов устройства,

Первый 10 и основной 4 формирователи импульсов также выполнены идентичными, каждый из них формирует на выходе прямоугольный импульс, фрон- том привязанный к фронту входного

сигнала, причем длительность .ti этих выходных импульсов выбирается из условия

s- Ч,

t

2 т, - t,

tj.1 -. - 3 Bi

где tg - длительность входных импульсов устройства

Второй формирователь 11 импульсов формирует прямоугольный импульс длительностью t, фронтом привязанный к спаду входного сигнала, при этом

длительность соотношения

U-2

определяется из

.

Ключевые элементы 2 - устройства,

У которых при подаче на управляющий вход сигнала вход -оказывается практически закорочен с выходом, благодаря чему потенциал цепи, к которой подключен вход, оказывается практически равен потенциалу общей шины, Тое, нулю При отсутствии сигнала на управляющем .входе ключевого элемента его входное сопротивление достаточно велико и он практически

не шунтирует соединенную с ним цепь.

Счетчик 5 производит суммирование с накоплением кода числа К+1 под действием каждого сигнала с выхода перв(Ьо формирователя 0 импульсов,

Преобразователь 9 кодов преобразует позиционный код с группы триггеров 8 (1 соответствует наличию напряжения на выходе триггера) в соответствующий двоично-десятичный

код числа триггеров, на выходе которых код 1. Выходной двоично-десятичный код преобразователя 9 соответствует коду, в котором работает счетчик 5.

Сумматор 6 вырабатывает на своем выходе код числа, равного сумме кодов, поступающих от преобразователя 9 кодов и счетчика 5,, Сумматор может быть реализован в виде п счечиков и п-1 сумматоров, выход последнего из которых содержит информацию о сумме кодов о

На временных диаграммах (фиг.2) ч - последовательность входных импульсов; (Г, I, г e.,3ift ,и., к - импульсы на выходе элементов задержки при Л - импульс на выходе элемента И 13; лс , н импульсы на выхо- дах формирователей 10 и 4 соответственно; о - импульс на входе триггера 8.К; г- импульс на выходе формирователя 11 .

Для наглядности входная последова тельность (фиг.2а), а также задержанные импульсы изображены в виде единичного скачка по переднему фронту реального импульса, например пятого, десятого и т„д. Кроме того, в моменты tj - tg (фиго2) стрелками показаны импульсы, исключенные с выхода нечетных элементов задержки (зачеркнуты) ф

Устройство работает следующим образом

В исходном состоянии до подачи на вход устройства измеряемой последовательности импульсов (фиг.2Л) момент tp на выходах формирова- телей 10-4 импульсов сигналы отсутствуют, что соответствует подаче запрещающего сигнала на первые входы первых элементов И 3 группы,электронные ключи 2 запертыо Триггеры 8 и счетчик 5 находятся в исходном нулевом состоянии (цепи установки счетчика 5 и триггеров 8 не показаны) блок 7 индикации индицирует .нулевой результат суммирования кодов преоб- разователя 9 кодов и счетчика 5,

Процесс подсчета импульсов начинается после подачи на вход устройства последовательности импульсов Эти импульсы проходят через элемен- ты 1 задержки о Через интервал времени , после момента поступления первого импульса последовательности на вход устройства он начинается на вы

5 0

5 0

0 5 0

g

5

ходе первого элемента I.1 задержки (фиГо2 Г), еще через tj - на выходе второго элемента 1 ,2 задержки(фиг.26), а на входе устройства в этот момент - второй импульс входной последовательности (фиг,2а)о Еще через f первый входной импульс доходит до выхода третьего элемента 1.3 задержки (фиг.2г), а второй входной импульс в этот же момент времени появляется на выходе первого элемента 1,1 задержки (фиг„2сО и т,До Таким образом, входная импульсная последовательность продвигается по цепочке элементов задержки, периодически появляясь на выходах нечетных элементов задержки (фиго2,,«с, сг) . Запертые ключи 2 не шунтируют выходы нечетных элементов задержки и не препятствуют продвижению последовательности сигналов вдоль цепочки элементов 1 задержки.

Через 2К с после поступления на вход первого импульса исследуемой последовательности он появляется на выходе элемента 1о2К задержки (фиг,2а)„ К этому моменту второй входной импульс доходит до выхода элемента 1,(2К-2)(фига2ж), третий - до выхода элемента 1,(2К-4)(фиг.2) и т,До К-й входной импульс появляется на выходе элемента 1о2 (фиг.2Л), а К+1-Й импульс - на входе устройства (фиг„2, момент 4), К-4-1-Й импульс с входа устройства и все предьщущие импульсы с выходов четных элементов задержки поступают на логический элемент И, который срабатывает (фиго2) и запускает формирователь 10 импульсов Последний вырабатывает импульсный сигнал (), поступающий на счетчик 5, в который вводится код числа К+1, Кроме того, сигнал с«выхода формирователя 10 импульсов подается через элемент. ИЛИ 12 на управляющие входы ключевых элементов 2, которые под воздействием этого сигнала открываются и начинают шунгировать выходы нечетных элементов задержки ( момент t).

В тот же момент времени t,, , когда срабатывает логический элемент И 13, сигнал первого входного импульса с выхода элемента 1о2К задержки поступает на основной формирователь 4 импульсов, который вырабатывает импульс (фиг„2н,), поступающий на первые входы элементов И 3 и откры5134

для прохождения сигналов

вакиции их

с выхода нечетных элементов I задержки на установочные (единичные) входы триггеров 8с Однако, когда открыты ключевые элементы 2, сигналы на вторых входах элементов И 3 отсутствуют и триггеры 8 остаются в своих исходных нулевых состояниях с, Кроме TorOj открытые ключевые элементы-2, шунтируя выходы нечетных элементов 1 задержки на время, в течение которого сигналы с нечетных элементов задержки должны перейти в четные элементы за

держки, препятствуют такому переходу, 15 нал счета поступает один раз за кажблагодаря чему к моменту t окончания импульсов, формирователей 10 и 4 в цепочке элементов задержки сигналы отсутствуют. Если не считать кода числа К+1 в счетчике 5 и индикации этого числа блоком 7 индикации, устройство возвращается в свое исходное состояние

На очередную порцию из К+1 входного им.пульса (фиГо2Ч., интервал tj-) , устройство реагирует аналогично, поэтому перед поступлением на вход устройства 2К+3 входного импульса в счетчике 5 записывается код

дые К+1 период входных импульсов, триггеры 8 переводятся в единичное состояние один раз в течение всего измерения, значит предлагаемое уст- 20 ройство может подсчитывать импульсы, следующие с частотами, превьшающими граничные частоты срабатйвания счетчика и триггеров о

25 Формула изобретения

Счетное устройство, содержащее 2К последовательно соединенных элементов задержки, вход первого

35

числа 2(К+1), а само это число инди- 30 из которых подключен к входу устрой- цируется блоком 7 индикации. Так устройство работает до тех пор, пока в исследуемой последовательности входных импульсов не останется количество импульсов меньше, чем К+1 (фиго2 г, с момента t,,) о

В момент поступления первого из этой пачки импульса на выход элемента 1о2К задержки (фиГо2 х, t) сигналы ,есть не на всех входах элемента И 13, поэтому этот элемент не срабатывает, а формирователь 10 импульсов не запускается. Но от сигнала на выходе элемента 1о2К срабатывает основной формирователь 4 импульсов (фиг,2н.) открывает элементы И 3 группы и все импульсы последней пачки, присутствующие на выходах четных элементов 1 задержки, поступают на установочные входы триггеров 8, переводя их в единичное состояние о Сигнал с входа последнего триггера 8К (фиг„2й) запускает формирователь 11 импульсов (фиГо2«), который через логический элемент ИЛИ 12 открывает электронные ключи 2, изымающие из дальнейшей работы импульсы, распространяющиеся по цепочке элементов задержки (фиг о2и,-момент tg ) «

ства, К ключевых элементов, управляющие входы которых объединены, выходы подключены к общей шине, группу первых элементов И, первые входы каждого из которых соединены с выходом основного формирователя,, вход Которого подключен к выходу 2К-го элемента задержки, счетчик, выходы которого соединены с соответствующи4Q ми первыми входами сумматора, выходы которого подключены к соответствующим входам блока индикации, отличающееся тем, что, с целью повьш ения надежности устройстдр- ва путем его упрощения, в него введены К триггеров, .преобразователь кода, дополнительный 2К+1-Й элемент задержки, дополнительный К+1-и ключевой элемент, первый и второй формирпвате50

55

ли, элемент ИЛИ и второй элемент И, входы которого соединены с входами соответствующих нечетных элементов задержки, выходы которых соединены с входами соответствующих ключевых элементов, выходы всех нечетных элементов задержк;и, кроме первого, соединены с вторыми входами соответствующих первых элементов И группы, выхода которых подключены к входам

Преобразователь 9 кодов вырабатывает двоично-десятичный код числа триггеров, перешедших в единичное состояние, сумматор 6 суммирует код с выхода преобразователя 9 с кодом, имеющимся в счетчике 5, а блок 7 индикации показывает число, равное числу импульсов, поступивших на вход устройства После перевода триггеров 8 и счетчика 5 в исходное нулевое состояние устройство готово к подсчету очередной серии импульсов

Таким образом, на счетчик 5 сигдые К+1 период входных импульсов, триггеры 8 переводятся в единичное состояние один раз в течение всего измерения, значит предлагаемое уст- ройство может подсчитывать импульсы, следующие с частотами, превьшающими граничные частоты срабатйвания счетчика и триггеров о

Формула изобретения

Счетное устройство, содержащее 2К последовательно соединенных элементов задержки, вход первого

из которых подключен к входу устрой-

ства, К ключевых элементов, управляющие входы которых объединены, выходы подключены к общей шине, группу первых элементов И, первые входы каждого из которых соединены с выходом основного формирователя,, вход Которого подключен к выходу 2К-го элемента задержки, счетчик, выходы которого соединены с соответствующими первыми входами сумматора, выходы которого подключены к соответствующим входам блока индикации, отличающееся тем, что, с целью повьш ения надежности устройства путем его упрощения, в него введены К триггеров, .преобразователь кода, дополнительный 2К+1-Й элемент задержки, дополнительный К+1-и ключевой элемент, первый и второй формирпвате

и, элемент ИЛИ и второй элемент И, входы которого соединены с входами соответствующих нечетных элементов задержки, выходы которых соединены с входами соответствующих ключевых элементов, выходы всех нечетных элементов задержк;и, кроме первого, соединены с вторыми входами соответствующих первых элементов И группы, выхода которых подключены к входам

1347

соответствующих триггеров, выходы которых соединены с соответствующими входами преобразователя кодов, выходы которого подключены к соответствующим вторым входам сумматора, выход второго элемента И через первый формирователь соединен с входом счетчика и с первым входом элемента ИЛИ, выход которого подключен к уп- ю равляющему входу дополнительного ключевого элемента, а второй вход

5128/52

Тираж 899Подписное

ВНИИШ Государственного комитета СССР

по делам изобретений к открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

8

соединен с выходом второго формирователя, вход которого соединен с входом К-го триггера, выход дополнительного ключевого элемента соединен с общей щиной, управляющий вход соединен с управляющими входами ключевых элементов, причем вход дополнительного элемента задержки подключен к выходу 2К-ГО элемента задержки, а счетчик выполнен в виде накапливающего сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для счета количества импульсов | 1986 |

|

SU1406781A1 |

| Преобразователь двоичного сигнала в квазитроичный сигнал | 1983 |

|

SU1109926A1 |

| Счетное устройство | 1985 |

|

SU1288906A1 |

| Преобразователь двоичного кода во временной интервал | 1987 |

|

SU1453597A1 |

| Цифровой частотомер | 1988 |

|

SU1636786A1 |

| Кольцевая система громкоговорящей связи с временным разделением каналов | 1990 |

|

SU1699359A3 |

| Устройство для контроля аналого-цифрового преобразователя | 1986 |

|

SU1585897A1 |

| СИСТЕМА ЦИФРОВОГО ТЕЛЕВИДЕНИЯ | 2001 |

|

RU2208917C2 |

| Устройство для автоматической регистрации радиотелеграфных сигналов | 1983 |

|

SU1092747A1 |

| Анализатор амплитуд и частот формант речевого сигнала | 1981 |

|

SU953658A1 |

Изобретение может быть использо вано в измерительных устройствах и позволяет повысить надежность устройства путем его упрощения Счетное устройство содержит 2К элементов 1,1 1.2К задержки, К ключевых элементов 2,1-2«К, группу элементов И 3, счетjhod чкк 5, сумматор 6, блок 7 индикации и формирователи 4«, В устройство введены К триггеров 8 о 1-8„К, преобразователь 9 кода, элемент l,(2K+l) задержки, ключевой элемент 2о(К+1), формирователи 10 и 11, элемент ИЛИ 12, и элемент И 13„ Благодаря этому на счетчик 5 сигнал счета поступает один раз за каждый (К+1)период входных импульсов. Триггеры 8 вообще переводятся в единичное состояние один раз в течение всего измерения. Следовательно, устройство может подсчитывать импульсы, следукицие с частотами, превышающими граничные размеры частот срабатывания счетчика 5 и триггеров 8„2 ил. (Л бЬ./

| Устройство фазовой автоподстройки частоты | 1979 |

|

SU930695A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-10-23—Публикация

1985-10-02—Подача