Изобретение относится к вычислительной технике и может применяться в устройствах преобразования информации в вычислительно-управляюсшх системах автоматики.

Целью изобретения является повышение точности преобразования.

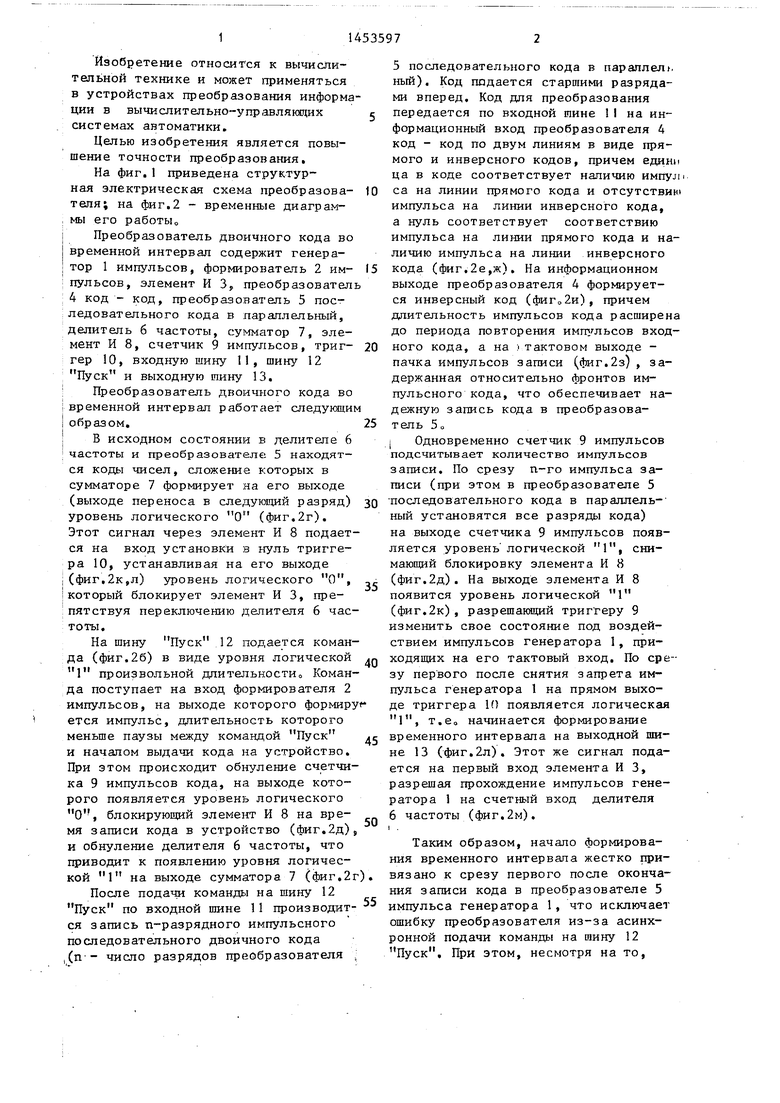

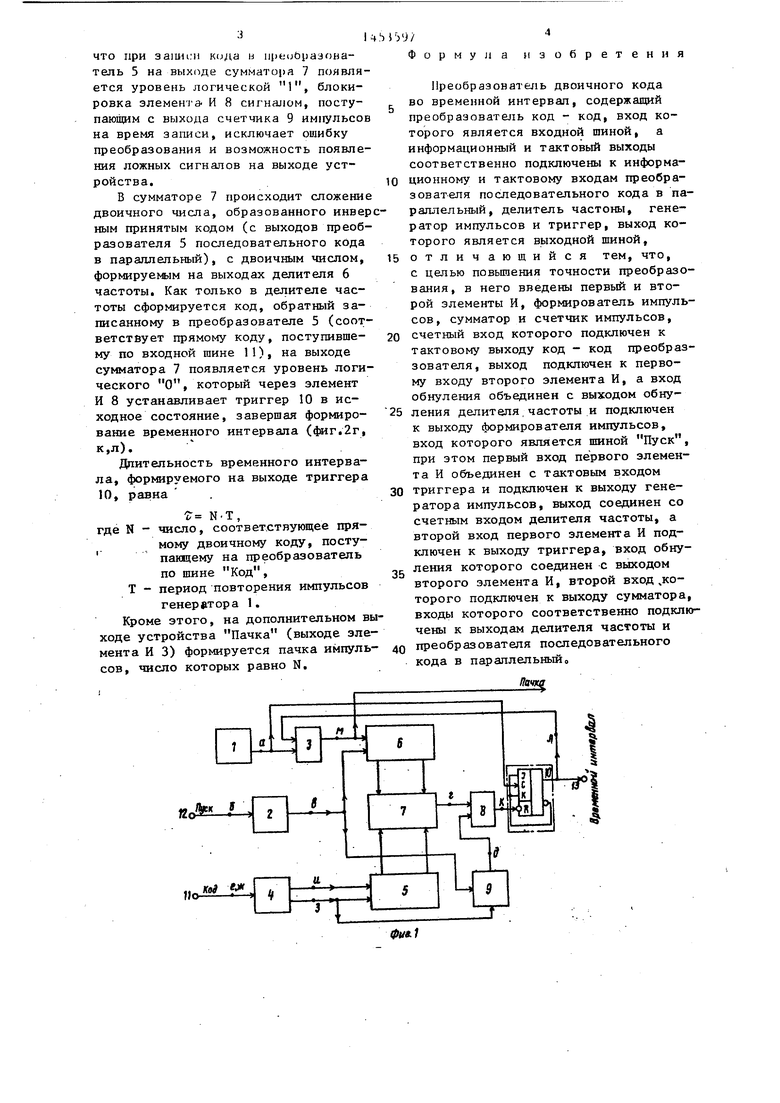

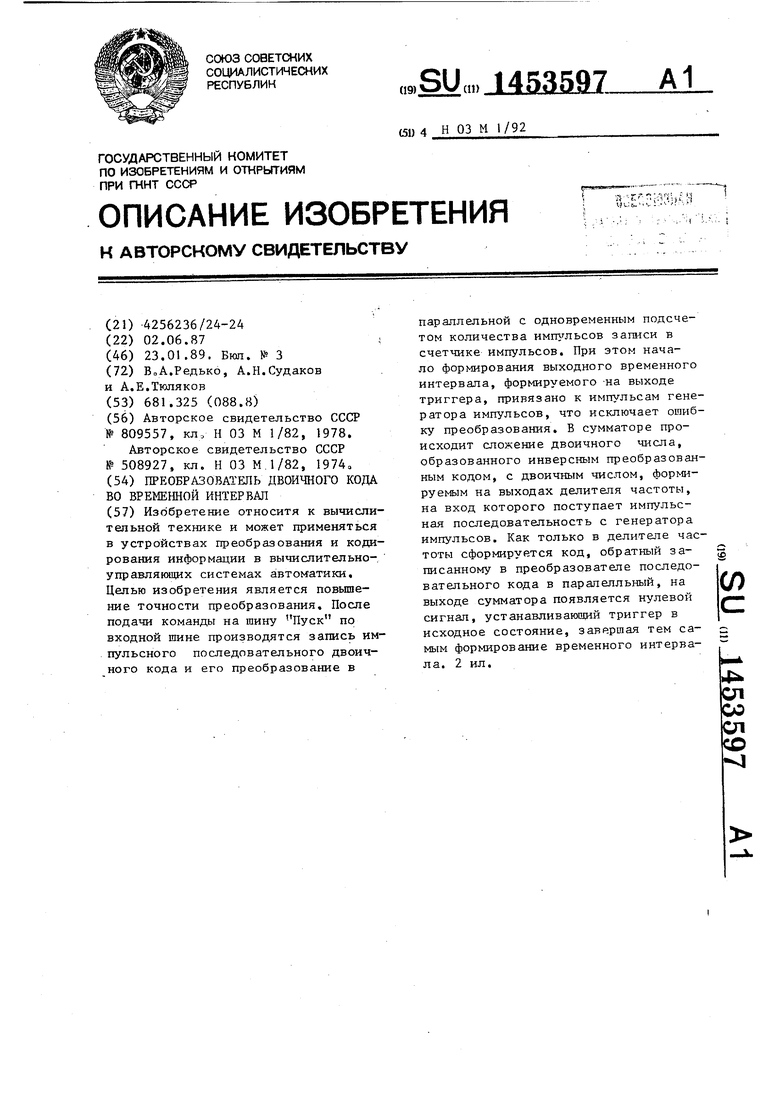

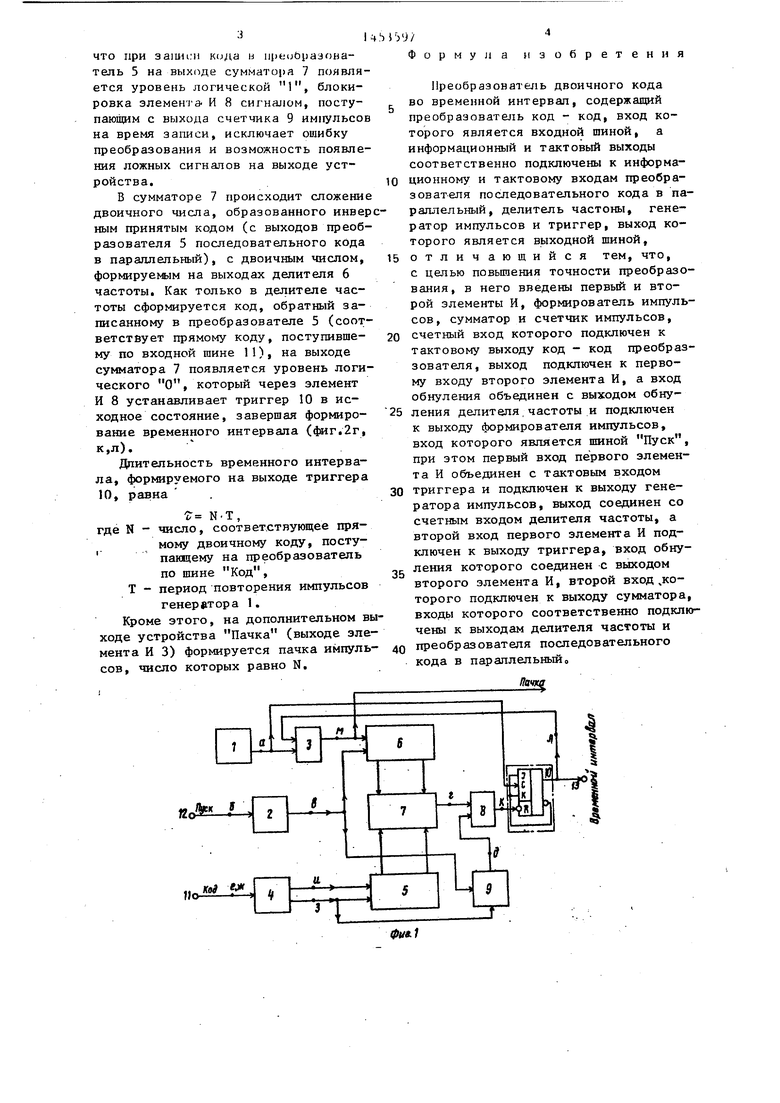

На фиг.1 приведена структурная электрическая схема преобразова- теля; на фиг.2 - временные диаграм- , мы его работы

I Преобразователь двоичного кода во I временной интервал содержит генера- I тор 1 импульсов, формирователь 2 им- ; пульсов, элемент И 3, преобразовател ; 4 код - код, преобразователь 5 пос- : ледовательного кода в параллельный, делитель б частоты, су1 1матор 7, элемент И 8, счетчик 9 импульсов, триг- гер 10, входную шину 11, шину 12 Пуск и выходную шиьгу 13. I Преобразователь дгюичного кода во ; временной интервал работает следующим I образом,

I В исходном состоянии в делителе 6 ; частоты и преобразователе 5 находятся коды чисел, сложение которых в сумматоре 7 формирует на его выходе (выходе переноса в следующий разряд) уровень логического О (фиг,2г). Этот сигнал через элемент И 8 подается на вход установки в нуль триггера 10, устанавливая на его выходе i (фиг,2к,л) уровень логического О, I который блокирует элемент И 3, пре- ;пятствуя переключению делителя 6 частоты.

На шину Пуск 12 подается команда (фиг.26) в виде уровня логической 1 произвольной длительности Команда поступает на вход формирователя 2 импульсов, на выходе которого формиру ется импульс, дпительность которого меньше паузы между командой Пуск и началом выдачи кода на устройство. При этом происходит обнуление счетчика 9 импульсов кода, на выходе которого появляется уровень логического О, блокирующий элемент И В на время записи кода в устройство (фиг,2д)9 и обнуление делителя 6 частоты, что приводит к появлению уровня логической 1 на выходе сумматора 7 (фиг,2г

После подачи команды на шину 12 Пуск по входной шине 11 производится запись п-разрядного импульсного последовательного двоичного кода ,(п - число разрядов преобразователя

5 последовательного кода в параллель ный). Код подается старшими разрядами вперед. Код для преобразования передается по входной шине 1I на информационный вход преобразователя 4 код - код по двум линиям в виде прямого и инверсного кодов, причем един ца в коде соответствует наличию импу са на линии прямого кода и отсутстви импульса на линии инверсного кода, а нуль соответствует соответствию импульса на линии прямого кода и наличию импульса на линии инверсного кода (фиг.2е,ж). На информационном выходе преобразователя 4 формируется инверсный код (фиго2и), причем длительность импульсов кода расширен до периода повторения имщ льсов входного кода, а на ) тактовом выходе - пачка импульсов записи (фиг,2з) , задержанная относительно фронтов импульсного кода, что обеспечивает надежную запись кода в преобразователь 5о

i Одновременно счетчик 9 импульсов подсчитывает количество импульсов записи. По срезу п-го импульса записи (при этом в преобразователе 5 последовательного кода в параллель- ный установятся все разряды кода) на выходе счетчика 9 импульсов появляется уровень логической 1, сни- маюший блокировку элемента И 8 (фиг,2д). На выходе элемента И 8 появится уровень логической 1 (фиг,2к), разрешающий триггеру 9 изменить свое состояние под воздействием импульсов генератора 1, при- ходяшлх на его тактовый вход. По срезу первого после снятия запрета импульса генератора 1 на прямом выходе триггера 10 появляется логическая 1, т,е, начинается формирование временного интервала на выходной шине 13 (фиг,2л), Этот же сигнал подается на первый вход элемента ИЗ, разрешая прохождение импульсов генератора 1 на счетный вход делителя

6 частоты (фиг,2м),

I .

Таким образом, начало формирования временного интервала жестко привязано к срезу первого после окончания записи кода в преобразователе 5 импульса генератора 1, что исключает ошибку преобразователя из-за асинхронной подачи команды на ошну 12 Пуск, При этом, несмотря на то.

что при заши;и кч},а н иреибраэоьа- тель 5 на выходе сумматора 7 появляется уровень логической 1, блокировка элемен а И 8 сигналом, поступающим с выхода счетчика 9 импульсов на время записи, исключает ошибку преобразования и возможность появления ложных сигналов на выходе устройства,

В сумматоре 7 происходит сложение двоичного числа, образованного инверным принятым кодом (с выходов преобразователя 5 последовательного кода в параллельный), с двоичным числом, формируемым на выходах делителя 6 частоты. Как только в делителе частоты сформируется код, обратный записанному в преобразователе 5 (соответствует прямому коду, поступившему по входной шине 11), на выходе сумматора 7 появляется уровень логического О, который через элемент И 8 устанавливает триггер 10 в исходное состояние , завершая формирование временного интервала (фиг,2г,

к,л).

Дпительность временного интервала, формируемого на выходе триггера

10, равна.

2Г N T,

где N - число, соответстнующее прямому двоичному коду, посту- паищему на преобразователь

по шине Код, Т - период повторения импульсов

генерцтора 1.

Кроме этого, на дополнительном входе устройства Пачка (выходе элемента И 3) формируется пачка импульсов, число которых равно N,

Формула изобретения

Преобразователь двоичного кода во временной интервал, содержащий преобразователь код - код, вход которого является входной шиной, а информационный и тактовый выходы соответственно подключены к информа0 ционному и тактовому входам преобразователя последовательного кода в параллельный, делитель частоны, генератор импульсов и триггер, выход которого является выходной шиной,

5 отличающийся тем, что, с целью повьш1ения точности преобразования, в него введены первый и второй элементы И, формирователь импульсов, сумматор и счетчик импульсов,

0 счетный вход которого подключен к

тактовому выходу код - код преобраз- зователя, выход подключен к первому входу второго элемента И, а вход обнуления объединен с выходом обну5 ления делителя,частоты и подключен к выходу формирователя импульсов, вход которого является шиной Пуск , при этом первый вход первого элемента И объединен с тактовым входом

0 триггера и подключен к выходу генератора импульсов, выход соединен со счетным входом делителя частоты, а второй вход первого элемента И подключен к выходу триггера, вход обнуления которого соединен с выходом второго элемента И, второй вход .которого подключен к выходу сумматора, входы которого соответственно подключены к выходам делителя частоты и 40 преобразователя последовательного кода в параллельный

Пачка

аПППППП„ПГ| |ПП„ПППППППП ,t

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2433528C2 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1001098A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| Устройство для преобразования двоичного кода во временной интервал | 1986 |

|

SU1363475A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Устройство для извлечения квадратного корня из напряжения | 1989 |

|

SU1721615A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПЛОТНОСТИ РАСПРЕДЕЛЕНИЯ ВЕРОЯТНОСТЕЙ СЛУЧАЙНОГО ПРОЦЕССА | 2000 |

|

RU2174706C1 |

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1988 |

|

SU1541663A1 |

| Широкодиапазонный логарифмический аналого-цифровой преобразователь | 1988 |

|

SU1580557A1 |

Изобретение относитя к вычислительной технике и может применяться в устройствах преобразования и кодирования информации в вычислительно- управляющих системах автом атики. Целью изобретения является повьппе- ние точности преобразования. После подачи команды на шину Пуск по входной шине производятся запись импульсного последовательного двоичного кода и его преобразование в параллельной с одновременным подсчетом количества имщшьсов записи в счетчике импульсов. При этом начало формирования выходного временного интервала, формируемого -на выходе триггера, привязано к импульсам генератора импульсов, что исключает ошибку преобразования. В сумматоре происходит сложение двоичного числа, образованного инверсным преобразованным кодом, с двоичным числом, формируемым на выходах делителя частоты, на вход которого поступает импульсная последовательность с генератора импульсов. Как только в делителе частоты сформируется код, обратный записанному в преобразователе последовательного кода в паралелльный, на выходе сумматора появляется нулевой сигнал, устанавливающий триггер в исходное состояние, завершая тем самым формирование временного интервала. 2 ил. (/) сд 00 СП

м

Ипй

Фиг.2

| Преобразователь кода во временнойиНТЕРВАл | 1978 |

|

SU809557A1 |

| Преобразователь двоичного кода вовременной интервал | 1974 |

|

SU508927A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-01-23—Публикация

1987-06-02—Подача