Изобретение относится к вычислительной технике и предназначено для контроля быстродействующих аналогот цифровых преобразователей (АЦП) и обеспечивает достоверность контроля за счет получения информации о точности А1Щ с погрешностью, не превышающей части кванта характеристики преобразователя А1Щ.

Цель изобретения - повышение достоверности контроля и расширение области применения за счет контроля биполярных преобразователей.

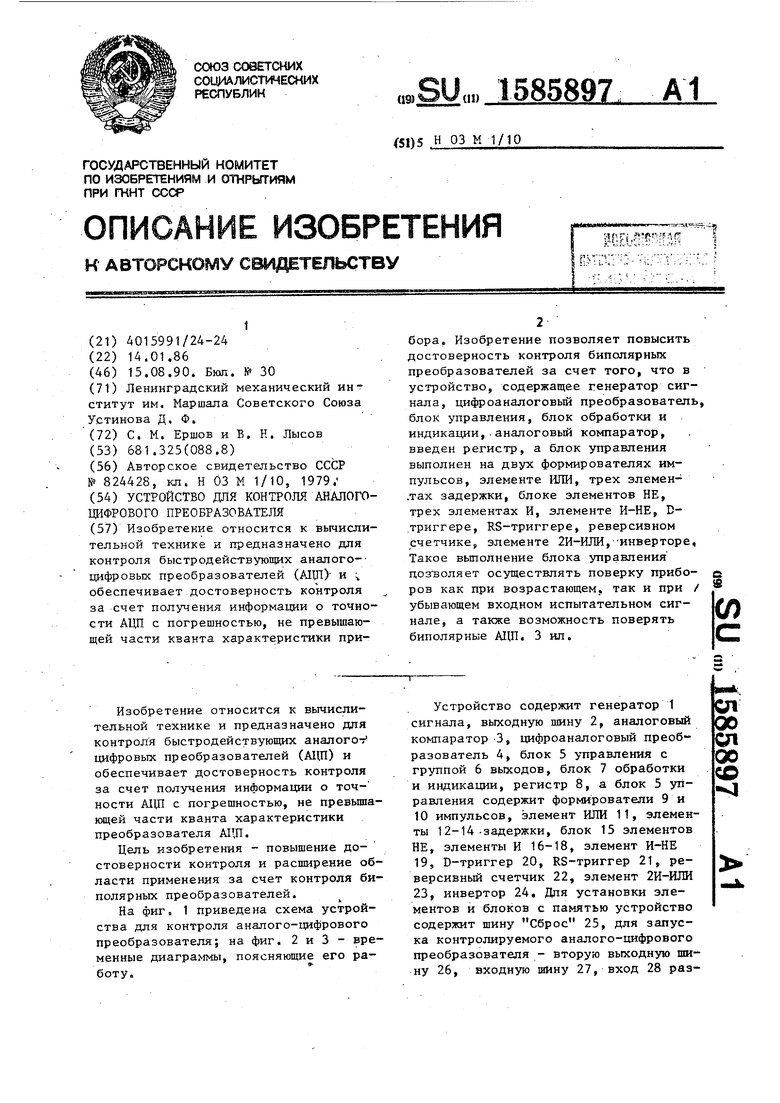

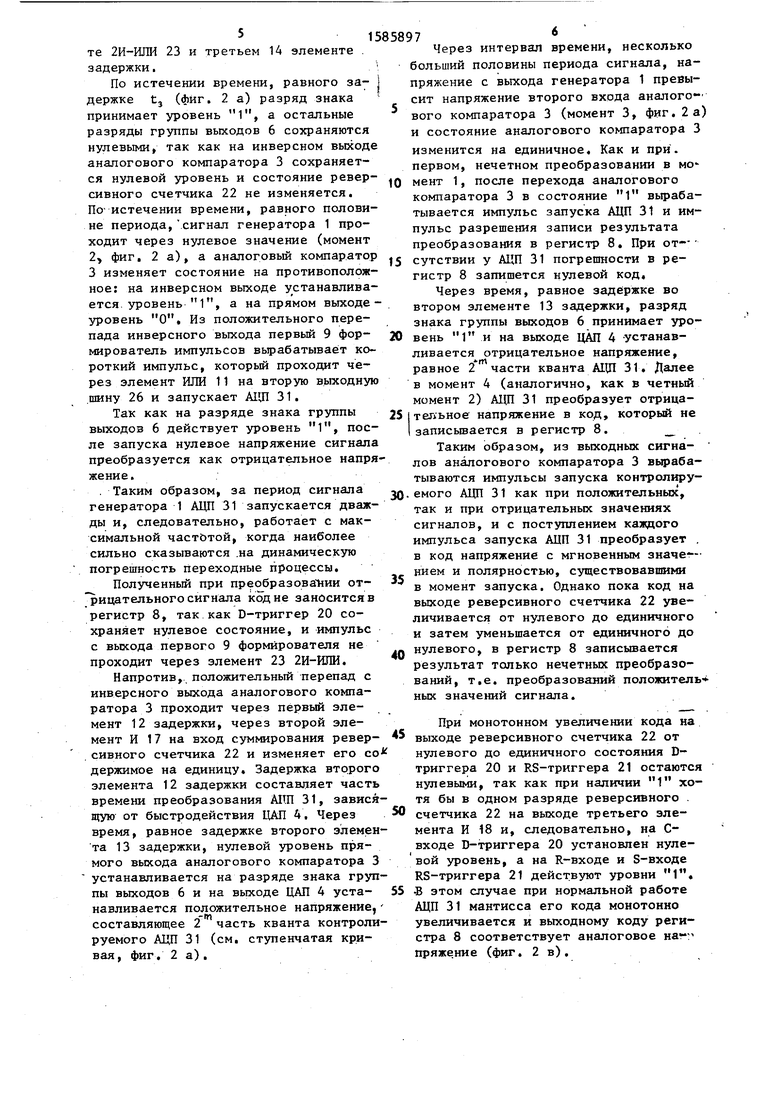

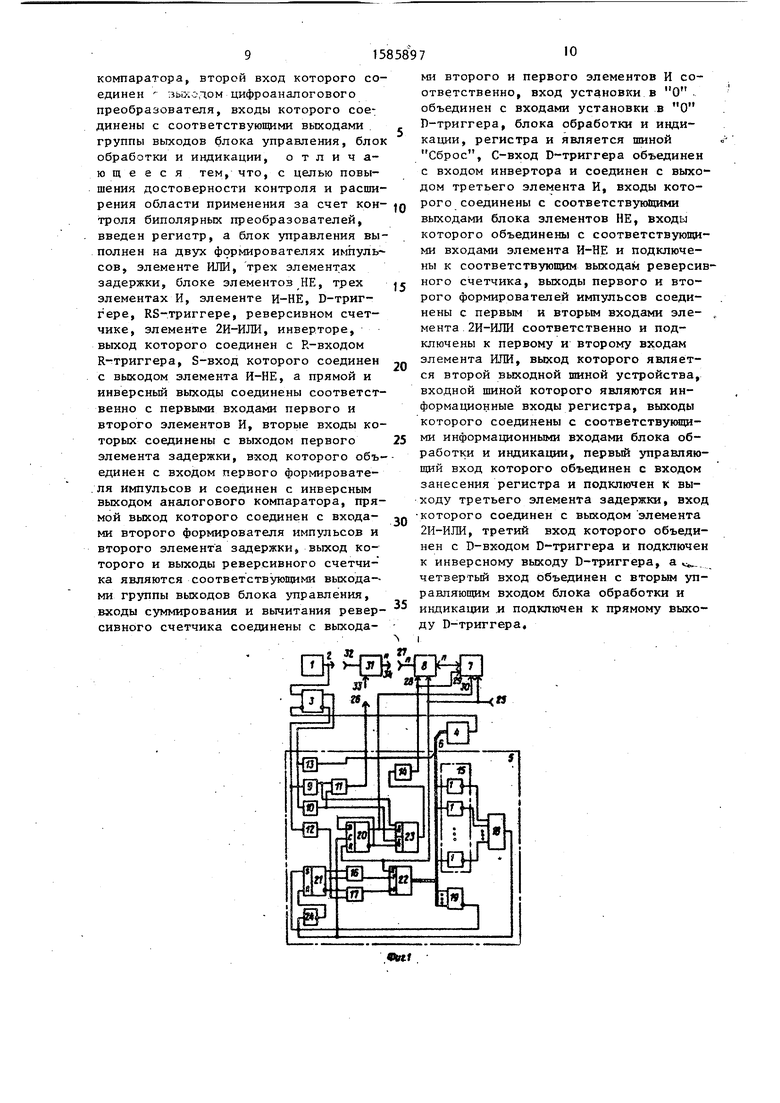

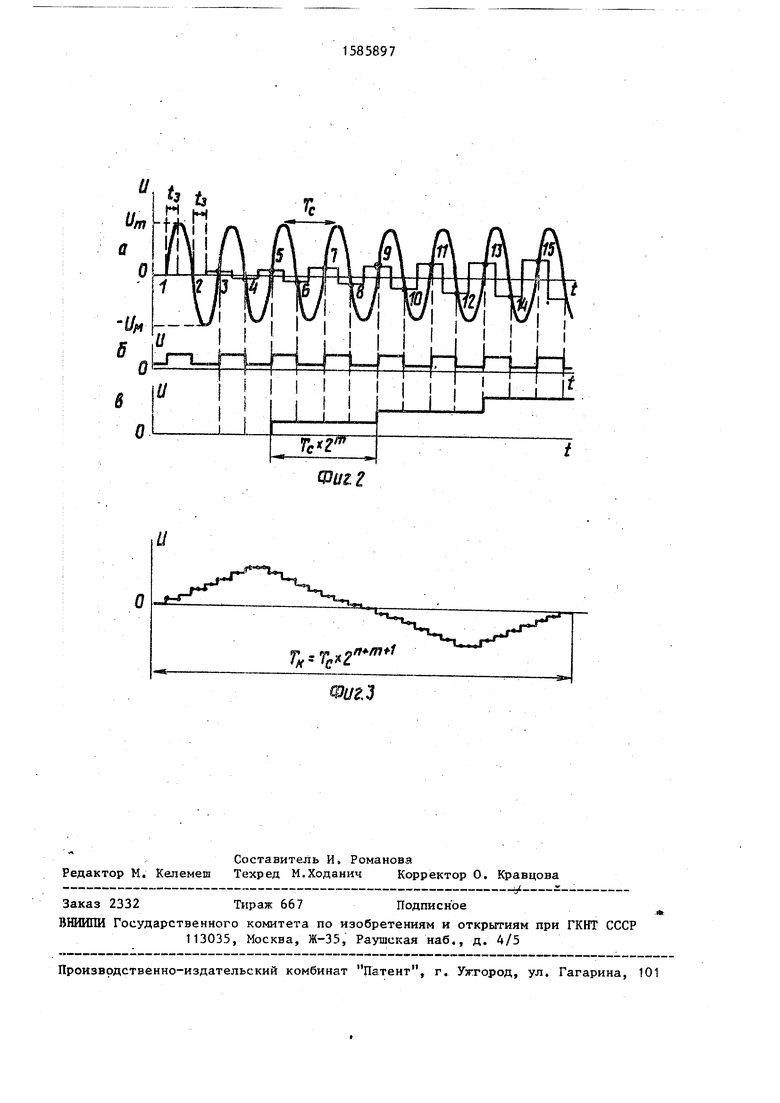

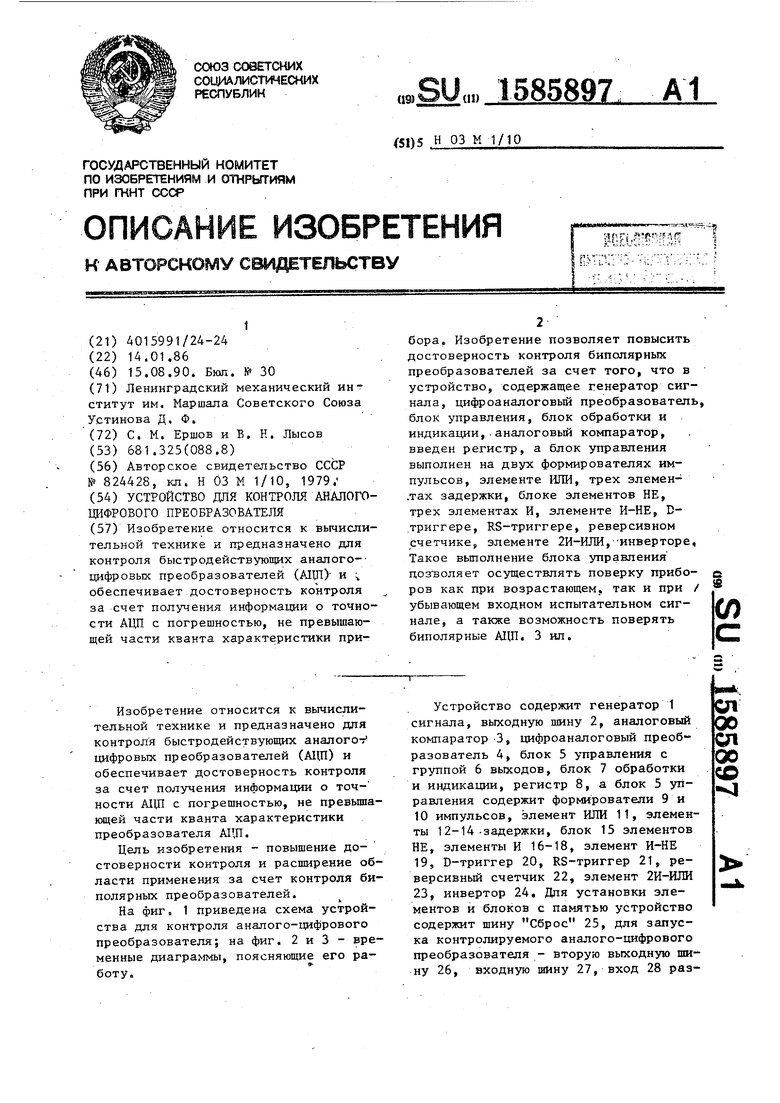

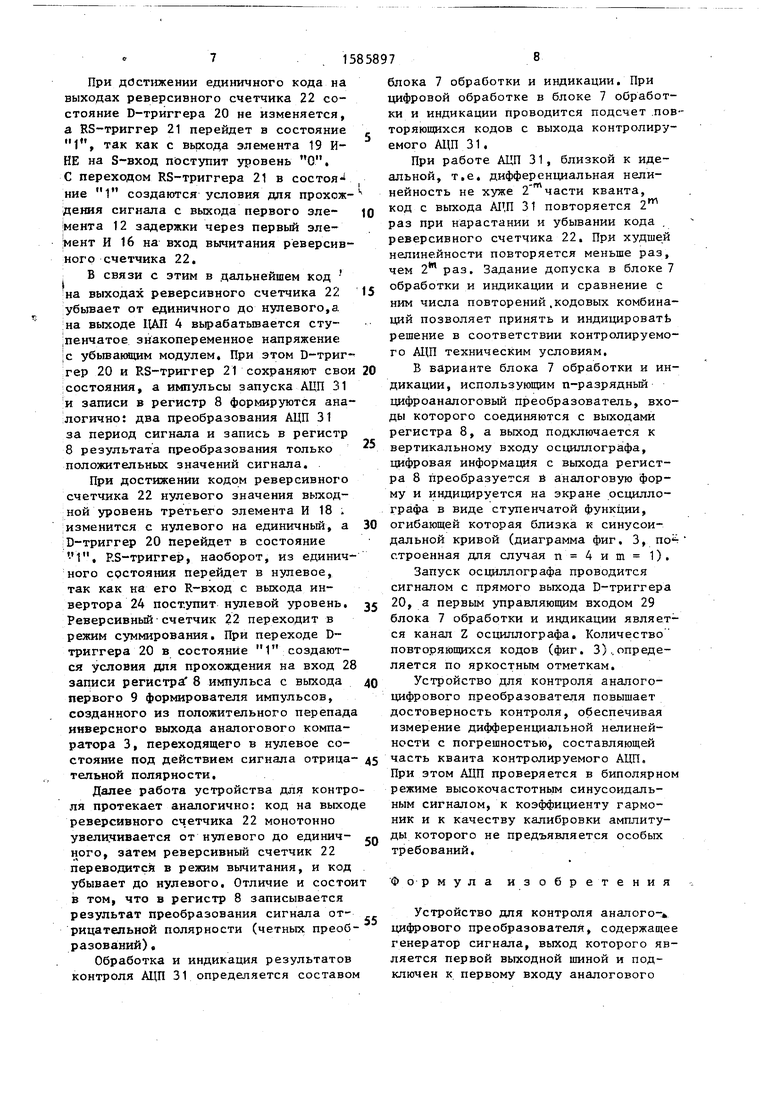

На фиг. 1 приведена схема устройства для контроля аналого-цифрового преобразователя; на фиг. 2 и 3 - временные диагра пу ы, поясняющие его работу.

Устройство содержит генератор 1 сигнала, выходную шину 2, аналоговый компаратор -3, цифроаналоговый преобразователь 4, блок 5 управления с группой 6 выходов, блок 7 обработки и индикации, регистр 8, а блок 5 управления содержит формирователи 9 и 10 импульсов, элемент ИЛИ 11, элементы 12-14 -задержки, блок 15 элементов НЕ, элементы И 16-18, элемент И-НЕ 19, D-триггер 20, RS-триггер 21, реверсивный счетчик 22, элемент 2И-ИЛИ 23, инвертор 24, Дпя установки элементов и блоков с памятью устройство содержит шину Сброс 25, для запуска контролируемого аналого-цифрового преобразователя - вторую выходную шину 26, входную шИну 27, вход 28 разел

сх ел

00

со

иешеияя записи рагнстра 8 и пераый 29 п .«.орой 30 :;яп)авля1ощиа входы блока 7 обработки и индика1дан,

Контролируемтл аналого-цифровой преобрадозатель 31 имеет входную шиИ группу ВЫ1СО

нулевое насосто-

i-;yj.feBoe

- Л 22 .:ий

анан

пу 32, шичу 33 запуска дов 34„

Перед проведгиие - контроля первая выход,. .цина 2 и з гор.пя зыходная щи- на 26 устройства соади;гя отся соотает- стзенно с входной umiioii 32 и с Ш-1ной 33 за1 у-:ка KOHTpoj inpy jMOi o ./ЩИ 3, а rriyuTia выходов 3- /ЩИ 3 юдключйатся к вход;юн ,кк5ие 27 устройства,, Прг контроле п-разрядного АЦП в составе, устройства контроля используется (n-i-ni)-разрядный JJ/JT -3 (uM-m-l)-разрядный peKiepcKBiibm счетчик,

Устройстзо З ситроля АЦП работает со7едующ{-гм образом,

После постзггигеы1- я csu iiana сброса по тине Сброс 25 элементы и блоки с naMi Vbio (-.Е,1 };{заю 1ч;я в нулевое :лИе.; пг i pynrfe 1.;ы;;:о/ ов 6 блока 5 усТ Л;ав;зикае ся мулевон к ;зьгходи6е лй.)Жеиие ЦАП 4 равно кз лш, LKI ;з ;;ором висг де аналогового KOMjapaTopa 3 декст куе пряжение При сбросе в япие ppRept.KKKorо C40 j- Еги: ::а очч:я ; poBH i ;:;С Гмч ььосодах блока 15 зль:мв;;;ток НЕ на вы- у:сде трс . ьсго 8 элеме:нч а И к на :зы- гсоде .--eHT3 И--НЕ 19,. Ввиду Э1 01;о ка В-БХодс ера 2 устанаЕливается уронаиь ,, а па П-входе того :же «ркггчп; - уровень О, С инкерсного Еькода RP -rpHrrepa 21 гоступает фo вень 1 ия верзый Е;:ОД второго 7 элемента И; что обеспечивает прохож- денке на вход сум-ировалия реверс1шио го счетчика 22 ;пyльcc в сигнала с уровпем М с Bi-,:iKo;;,a перзого , } 2 элемента задержки,

-

Анапогячно при сбросе 1)-триггер 2 устананливаатся в иупеиоа состояние, а на О-триггера 20 поступает Г/ровень I с выхода третьего 18 эле- П энта И, Уровень 1 инверснох- о выхода D-трлггера 20 обеспечивает прохождение «оротхого импульса с уровнем с -зъкоца второго U) формирователя 1-и шульсов через элемент 2И--ИЛИ 23 К третий 14 элемент задержки на вход 28 регистра 8 и на первый 29 хтсравляющий вход Слока 7 обработки и индикапли g

0

15

20

25

30

JQ 35

45

Если до сброса в нулевое состояние Б-триггер 20 находился в единичном состоянии, то при сбросе -на прямом выходе D-триггера 20 возникает перепад напряжения, запускающий по второму управляющему входу 30 блок 7 обработки и индикации, В противном случае запуск блока 7 обработки и индикации происходит в процессе работы устройства контроля в момент времени, когда и.::менится состояние D-триггера 20 с ::;;;нничного на нулевое.

Работа устройства в динамике. Генератор 1 вырабатывает синусои- дал.ьное напряжение, частота которого не превь шает похювины максимальной . частоты преобразования А1Щ 3, а раз- MiS.x превышает двуполярный диапазон преобразования (фиг, 2 а). Диапазон цкфрсаналогового преобразователя А устанавливается не менее диапазона

.контролируемого АЦП 31.

Аналоговый компаратор 3 сравнива- 4iT cvIгнaл генератора 1 с нулевым на- 1С ;: яжением. поступающим на его второй lizoA с ЦАП 4 и вырабатывает при наличии превышения нулевого уровня противофазные сигналы на прямом и и нверс- н. в(:1кода-%5 Положительный импульс ( риг, 26) с прямого выхода аналого- ЕС-го компаратора 3 проходит через второй 13 sjiSMeHT задержки на разряд знака :группь выходов 6 блока 5 управ- л..-н.;я и -а вход второго 10 формирователя импульсов а Второй 10 формирова- импульсов вьграбатывает из поло- ;oo ie.jTbHoro перепада сигнала прямого Ьп;хода аналогового компаратора 3 короткий импульс которьш проходит чаре; элемент ИЛИ 11 на вторую выходную на-:; ну 26 и запускает АЦП ЗК Величина :-:адерхски второго 13 элемента задержки равна времени преобразования, а поэто - му на разряде знака группы выходов6 сохраняется в момент запуска АЦП31 ну7;:еЕой уровень,: Ввиду этого (при гфенебрежимо малых задержках в аналоговом компараторе 3,, первом 9 и вто- 10 формирователях, импульсов, элементе I-iJIli 11)А1Щ 31 преобразует практически нулевой сигнал как сигнал по- ло Л Нтелькой полярности в нулевой код, Занесение полученного кода в регистр 8 происходит после окончания преобразования, так как на вход 28 разрешения записи сигнал с выхода второго 10 фор-v 1 Шрователя импульсов поступает с за- держк.ой-, .равной запаздыванию в элементе 2И-ИЛИ 23 и третьем 14 элементе задержки.

По истечении времени, равного задержке t, (фиг. 2 а) разряд знака

принимает уровень 1, а остальные разряды группы выходов 6 сохраняются нулевыми, так как на инверсном выходе аналогового компаратора 3 сохраняется нулевой уровень и состояние реверсивного счетчика 22 не изменяется. По истечении времени, равного половине периода, сигнал генератора 1 проходит через нулевое значение (момент 2, фиг, 2 а), а аналоговый компаратор 3 изменяет состояние на противоположное: на инверсном выходе у станавлива- ется. уровень 1, а на прямом выходе- уровень О, Из положительного перепада инверсного выхода первьй 9 формирователь импульсов вырабатывает короткий импульс, который проходит через элемент ИЛИ 11 на вторую вьгходную шину 26 и запускает А1Щ 31,

Так как на разряде знака группы выходов 6 действует уровень 1, после запуска нулевое напряжение сигнала преобразуется как отрицательное напряжение.

. Таким образом, за период сигнала генератора 1 АЦП 31 запускается дважды и, следовательно, работает с максимальной частЬтой, когда наиболее сильно сказываются .на динамическую погрешность переходные процессы.

Полученный при преобразовании от- рицательногосигнала код не заносится в регистр 8, так.как D-триггер 20 сохраняет нулевое состояние, и импульс с выхода первого 9 формирователя не проходит через элемент 23 2И-ИЛИ,

Напротив,, положительный перепад с инверсного выхода аналогового компаратора 3 проходит через первый элемент 12 задержки, через второй эле больший половины периода сигнала, напряжение с выхода генератора 1 превысит напряжение второго входа аналогового компаратора 3 (момент 3, фиг, 2 а и состояние аналогового компаратора 3

изменится на единичное. Как и при. первом, нечетном преобразовании в мо- 10 мент 1, после перехода аналогового

компаратора 3 в состояние 1 вьфаба- тывается импульс запуска АЦП 31 и импульс разрешения записи результата преобразования в регистр 8. При от--

tS сутствии у АЦП 31 погрешности в регистр 8 запишется нулевой код.

Через время, равное задержке во втором элементе 13 задержки, разряд знака группы выходов 6 принимает уро20 вень 1 и на выходе ЦАП 4 устанавливается отрицательное напряжение, равное 2 части кванта А1Щ 31. Далее в момент 4 (аналогично, как в четный момент 2) АЦП 31 преобразует отрица2Slтельное напряжение в код, который не записьшается в регистр 8.

Таким образом, из выходных сигналов аналогового компаратора 3 вырабатываются импульсы запуска контролируемого АЦП 31 как при положительных, так и при отрицательных значениях сигналов, и с поступлением каждого импульса запуска АЦП 31 преобразует . в код напряжение с мгновенным значе-- нием и полярностью, существовавшими в момент запуска. Однако пока код на выходе реверсивного счетчика 22 увеличивается от нулевого до единичного и затем уменьшается от единичного до нулевого, в регистр 8 записывается результат только нечетных преобразований, т.е. преобразований положитель ных значений сигнала.

При монотонном увеличении кода на

30

35

40

л 1 I ft 1,Ч- л ж л л %-А.с ж- и л . v«-« J- «- .-f, -

мент И 17 на вход суммирования ревер- 5 выходе реверсивного счетчика 22 от сивного счетчика 22 и изменяет его со нулевого до единичного состояния D- держимое на единицу. Задержка второго элемента 12 задержки составляет часть времени преобразования А1Ш 31, зависящую от быстродействия ЦАП 4. Через 50 счетчика 22 на выходе третьего эле- время, равное задержке второго элемен- мента И 18 и, следовательно, на С- та 13 задержки, нулевой уровень прямого выхода аналогового компаратора 3 устанавливается на разряде знака груп-

триггера 20 и RS-триггера 21 остаются нулевыми, так как при наличии 1 хотя бы в одном разряде реверсивного

- ---. ,,

входе D-триггера 20 установлен нулевой уровень, а на R-входе и S-входе RS-триггера 21 действуют уровни 1,

пы выходов 6 и на выходе ЦАП 4 уста- 55-В этом случае при нормальной работе

навливается положительное напряжение, АЦП 31 мантисса его кода монотонно

составляющее 2 часть кванта контроли-увеличивается и выходному коду регируемого АЦП 31 (см, ступенчатая кри-стра 8 соответствует аналоговое на-: вая, фиг. 2 а),

пряжение (фиг. 2 в).

5897

Через интервал времени, несколько

больший половины периода сигнала, напряжение с выхода генератора 1 превысит напряжение второго входа аналого вого компаратора 3 (момент 3, фиг, 2 а) и состояние аналогового компаратора 3

изменится на единичное. Как и при. первом, нечетном преобразовании в мо- 10 мент 1, после перехода аналогового

компаратора 3 в состояние 1 вьфаба- тывается импульс запуска АЦП 31 и импульс разрешения записи результата преобразования в регистр 8. При от--

tS сутствии у АЦП 31 погрешности в регистр 8 запишется нулевой код.

Через время, равное задержке во втором элементе 13 задержки, разряд знака группы выходов 6 принимает уро20 вень 1 и на выходе ЦАП 4 устанавливается отрицательное напряжение, равное 2 части кванта А1Щ 31. Далее в момент 4 (аналогично, как в четный момент 2) АЦП 31 преобразует отрица2Slтельное напряжение в код, который не записьшается в регистр 8.

Таким образом, из выходных сигналов аналогового компаратора 3 вырабатываются импульсы запуска контролируемого АЦП 31 как при положительных, так и при отрицательных значениях сигналов, и с поступлением каждого импульса запуска АЦП 31 преобразует . в код напряжение с мгновенным значе-- нием и полярностью, существовавшими в момент запуска. Однако пока код на выходе реверсивного счетчика 22 увеличивается от нулевого до единичного и затем уменьшается от единичного до нулевого, в регистр 8 записывается результат только нечетных преобразований, т.е. преобразований положитель ных значений сигнала.

При монотонном увеличении кода на

30

35

40

А.с ж- и л . v«-« J- «- .-f, -

5 выходе реверсивного счетчика 22 от нулевого до единичного состояния D- 50 счетчика 22 на выходе третьего эле- мента И 18 и, следовательно, на С-

выходе реверсивного счетчика 22 от нулевого до единичного состояния D- счетчика 22 на выходе третьего эле- мента И 18 и, следовательно, на С-

триггера 20 и RS-триггера 21 остаются нулевыми, так как при наличии 1 хотя бы в одном разряде реверсивного

выходе реверсивного счетчика 22 от нулевого до единичного состояния D- счетчика 22 на выходе третьего эле- мента И 18 и, следовательно, на С-

- ---. ,,

входе D-триггера 20 установлен нулевой уровень, а на R-входе и S-входе RS-триггера 21 действуют уровни 1,

стра 8 соответствует

пряжение (фиг. 2 в).

При достижении единичного кода на выходах реверсивного счетчика 22 состояние D-триггера 20 не изменяется, а RS-триггер 21 перейдет в состояние 1, так как с вьрсода элемента 19 И- НЕ на S-вход поступит уровень О, С переходом RS-триггера 21 в состоя- ние 1 создаются условия для прохождения сигнала с выхода первого зле- |мента 12 задержки через первый эле- |мент И 16 на вход вычитания реверсивного счетчика 22,

В связи с этим в дальнейшем код на выходах реверсивного счетчика 22 убьгаает от единичного до нулевого,а на выходе ЦАП 4 вырабатывается сту- ;пенчатое знакопеременное напряжение с убывающим модулем. При этом D-триг-- гер 20 и RS-триггер 21 сохраняют свои состояния, а импульсы запуска АЦП 31 и записи в регистр 8 формируются аналогично: два преобразования АЦП 31 за период сигнала и запись в регистр 8 результата преобразования только положительных значений сигнала.

При достижении кодом реверсивного счетчика 22 нулевого значения выходной уровень третьего элемента И 18 . изменится с нулевого на единичный, а D-триггер 20 перейдет в состояние 1, RS-триггер, наоборот. Из единичного состояния перейдет в нулевое, так как на его R-вход с выхода инвертора 24 поступит нулевой уровень, Реверсивный счетчик 22 переходит в режим суммирования. При переходе D- триггера 20 в состояние 1 создаются условия для прохождения на вход 28 записи регистра 8 импульса с выхода первого 9 формирователя импульсов, созданного из положительного перепада инверсного выхода аналогового компаратора 3, переходящего в нулевое состояние под действием сигнала отригда- тельной полярности.

Далее работа устройства для контроля протекает аналогично: код на выход реверсивного счетчика 22 монотонно увеличивается от нулевого до единич- ного, затем реверсивный счетчик 22 переводится в режим вычитания, и код убывает до нулевого. Отличие и состои в том, что в регистр 8 записывается результат преобразования сигнала от- рицательной полярности (четных преобразований).

Обработка и индикация результатов контроля АЦП 31 определяется составом

5

5 0

0 5 О 5

Q

блока 7 обработки и индикации. При гщфровой обработке в блоке 7 обработки и индикации проводится подсчет .повторяющихся кодов с выхода контролируемого АЦП 31,

При работе АЦП 31, близкой к идеальной, т,е, дифференциальная нелинейность не хуже 2 части кванта, код с выхода А1Щ 31 повторяется 2 раз при нарастании и убывании кода . реверсивного счетчика 22, При худшей нелинейности повторяется меньше раз, чем 2 раз. Задание допуска в блоке 7 обработки и индикации и сравнение с ним числа повторений .кодовых комбинаций позволяет принять и индицировать решение в соответствии контролируемого АЦП техническим условиям,

В варианте блока 7 обработки и индикации, использующим п-разрядньш цифроаналоговый преобразователь, входы которого соединяются с выходами регистра 8, а выход подключается к вертикальному входу осциллографа, цифровая информация с выхода регистра 8 преобразуется в аналоговую форму и индицируется на экране рсхщлло- графа в виде ступенчатой функции, огибающей которая близка к синусоидальной кривой (диаграмма фиг, 3, по строенная для случая п 4 и m 1).

Запуск осциллографа проводится сигналом с прямого выхода D-триггера 20, а первым управляющим входом 29 блока 7 обработки и индикации является канал Z осциллографа. Количество повторяющихся кодов (фиг, 3),.определяется по яркостным отметкам.

Устройство для контроля аналого- цифрового преобразователя повышает достоверность контроля, обеспечивая измерение дифференциальной нелинейности с погрешностью, составляющей часть кванта контролируемого АЦП. При этом АЦП проверяется в биполярном режиме высокочастотным синусоидальным сигналом, к коэффициенту гармоник и к качеству калибровки амплитуды которого не предъявляется особых требований,

Формула изобретения

Устройство для контроля аналого-, цифрового преобразователя, содержащее генератор сигнала, выход которого является первой выходной шиной и подключен к первому входу аналогового

компаратора, второй вход которого соединен зьжодом цифроаналогового преобразователя, входы которого соединены с соответствующими выходами . группы выходов блока управления, блок обработки и индикации, отличающееся тем, что, с целью повышения достоверности контроля и расширения области применения за счет контроля биполярных преобразователей, введен регистр, а блок управления выполнен на двух формирователях импуль сов, элементе ИЛИ, трех элементах задержки, блоке элементов НЕ, трех элементах И, элементе И-НЕ, D-триг- гере, RS-.триггере, реверсивном счетчике, элементе 2И-ИЛИ, инверторе, выход которого соединен с Н-входом R-триггера, S-вход которого соединен с выходом элемента И-НЕ, а прямой и инверсный выходы соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых соединены с выходом первого элемента задержки, вход которого объединен с входом первого формировате- .ля импульсов и соединен с инверсным выходом аналогового компаратора, прямой выход которого соединен с входами второго формирователя импульсов и второго элемента задержки, выход которого и выходы реверсивного счетчика являются соответствующими выхода-ми группы выходов блока управления, входы суммирования и вычитания реверсивного счетчика соединены с выхода

ми второго и первого элементов И соответственно, вход установки в О, объединен с входами установки в О D-триггера, блока обработки и индикации, регистра и является шиной Сброс, С-вход D-триггера объединен с входом инвертора и соединен с выходом третьего элемента И, входы которого соединены с соответствующими выходами блока элементов НЕ, входы которого объединены с соответствующими входами элемента И-НЕ и подключены к соответствующим выходам реверсивного счетчика, выходы первого и второго формирователей импульсов соединены с первым и вторым входами эле- , мента 2И-ИЛИ соответственно и подключены к первому и второму входам элемента ИЛИ, выход которого является второй выходной шиной устройства, входной шиной которого являются информационные входы регистра, выходы которого соединены с соответствующими информационными входами блока обработки и индикации, первый управляющий вход которого объединен с входом занесения регистра и подключен к выходу третьего элемента задержки, вход которого соединен с выходом элемента 2И-ИЛИ, третий вход которого объединен с D-входом D-триггера и подключен к инверсному выходу D-триггера, а «;,. четвертый вход объединен с вторым управляющим входом блока обработки и индикации .и подключен к прямому выходу D-триггера,

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2020751C1 |

| Устройство для измерения амплитуды синусоидального напряжения низкой частоты | 1982 |

|

SU1170364A1 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1985 |

|

SU1356233A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1499495A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

| Устройство для контроля динамических параметров аналого-цифровых преобразователей | 1987 |

|

SU1474839A1 |

| Устройство для централизованного контроля параметров | 1984 |

|

SU1238040A1 |

| Система экстремального регулирования квадрупольного масс-спектрометра | 1989 |

|

SU1795419A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С САМОКОНТРОЛЕМ | 2010 |

|

RU2431233C1 |

| Устройство для задержки прямоугольных импульсов переменной амплитуды | 1986 |

|

SU1370749A1 |

Изобретение относится к вычислительной технике и предназначено для контроля быстродействующих аналого-цифровых преобразователей (АЦП) и обеспечивает достовериность контроля за счет получения информации о точности АЦП с погрешностью, не превышающей части кванта характеристики прибора. Изобретение позволяет повысить достоверность контроля биполярных преобразователей за счет того, что в устройство, содержащее генератор сигнала, цифроаналоговый преобразователь, блок управления, блок обработки и индикации, аналоговый компаратор, введен регистр, а блок управления выполнен на двух формирователях импульсов, элементе ИЛИ, трех элементах задержки, блоке элементов НЕ, трех элементах И, элементе И-НЕ, D-триггере, RS-триггере, реверсивном счетчике, элементе 2И-ИЛИ, инверторе. Такое выполнение блока управления позволяет осуществлять поверку приборов как при возрастающем, так и при убывающем входном испытательном сигнале, а также возможность поверять биполярные АЦП. 3 ил.

Н

Г ИI II J i

и U

QM-n.....

Ф//гГ

| Устройство для автоматическогоизМЕРЕНия МЕТРОлОгичЕСКиХ XAPAK-ТЕРиСТиК цифРОВыХ изМЕРиТЕльНыХпРибОРОВ | 1979 |

|

SU824428A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-08-15—Публикация

1986-01-14—Подача