Изобретение относится к электросвязи, в частности к цифровым системам передачи (ЦСП), использующим кабельные линии или линии других типов, оборудованные регенераторами кв зитроичного сигнала с самохронированием. В таких системах исходный двоичны сигнал (ИДС) для передачи по линии преобразуется (кодируется) в сбалансированньй квазитройчный сигнал, который возможно передавать без искаже ний через разделительные цепи (например, трансформаторы), которые неизбежно имеются в линии передачи, а после передачи производится обратное преобразование квазитроичного сигнала (декодирование) в двоичный сигнал Сбалансированный квазитроичный сигнал представляет собой последовательность различным образом чередующихся положительных, отрицательных и нулевых посылок, причем положитель ные и отрицательные пасылки предс,тавляют собой прямоугольные импульсы одинаковой амплитуды. Закон чередования положительных и отрицательных посылок в сбалансированном квазитроичном сигнале обеспечивает равенство нулю всех составляющих энергетического спектра на нулевой частоте (т.е. отсутствие постоянной составляющей и подавление нижних частот спектра), что и позволяет передавать его без искажений через разделительные цепи. Кроме того, энергетический спектр балансного квазитроичного сигнала обращается в нуль также и на частотах, кратных тактовой частоте этого сигнала. Известен преобразователь двоичного сигналив квазитроичный сигнал, содержащий два элемента задержки, формирователь квазитроичного кода и счетчик, а также синхронный коммутатор, входы которого соединены с выходами элементов задержки, а выход синхронного коммутатора подключен к первым входам формирователя квазитроичного кода и счетчика, второй вход которого соединен с входом первого элемента задержки, при этом выход счетчика подключен к второму входу формирователя квазитроичного кода и входу второго элемента задерж ки til . Недостатком преобразователя является то, что энергетический спектр

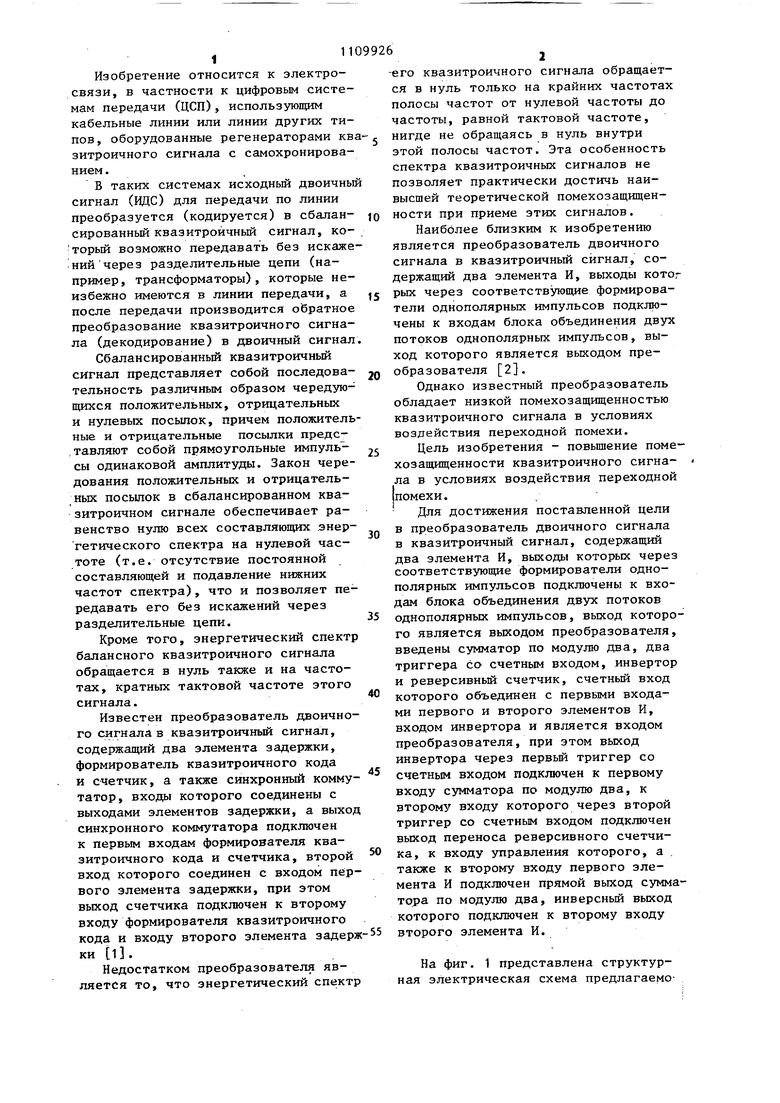

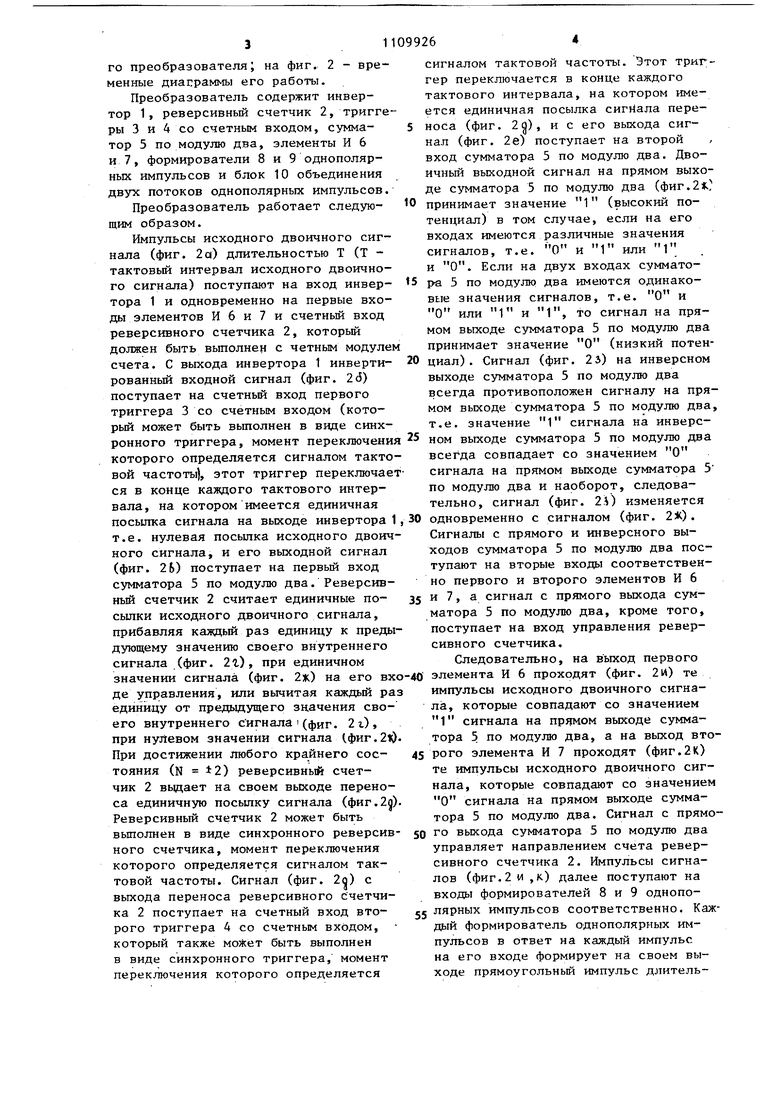

его квазитроичного сигнала обращается в нуль только на крайних частотах полосы частот от нулевой частоты до частоты, равной тактовой частоте. нигде не обращаясь в нуль внутри этой полосы частот. Эта особенность спектра квазитроичных сигналов не позволяет практически достичь наивысшей теоретической помехозащищенности при приеме этих сигналов. Наиболее близким к изобретению является преобразователь двоичного сигнала в квазитроичный сигнал, содержащий два элемента И, выходы котог рых через соответствующие формирователи однополярных импульсов подключены к входам блока объединения двух потоков однополярных импульсов, выход которого является выходом преобразователя 2. Однако известный преобразователь обладает низкой помехозащищенностью квазитроичного сигнала в условиях воздействия переходной помехи. Цель изобретения - повышение помехозащищенности квазитроичного сигнала в условиях воздействия переходной помехи. Для достижения поставленной цели в преобразователь двоичного сигнала в квазитроичный сигнал, содержащий два элемента И, выходы которых через соответствующие формирователи однополярных импульсов подключены к входам блока объединения двух потоков однополярных импульсов, выход которого является выходом преобразователя, введены сумматор по модулю два, два триггера со счетным входом, инвертор и реверсивньй счетчик, счетный вход которого объединен с первыми входами первого и второго элементов И, входом инвертора и является входом преобразователя, при этом выход инвертора через первьй триггер со счетным входом подключен к первому входу сумматора по модулю два, к второму входу которого через второй триггер со счетным входом подключен выход переноса реверсивного счетчика, к входу управления которого, а также к второму входу первого элемента И подключен прямой выход сумматора по модулю два, инверсный выход которого подключен к второму входу второго элемента И. На фиг. 1 представлена структурная электрическая схема предлагаемого преобразователя на фиг. 2 - временные диаграммы его работы. Преобразователь содержит инвертор 1, реверсивный счетчик 2, тригге ры 3 и 4 со счетным входом, сумматор 5 по модулю два, элементы И 6 и 7, формирователи 8 и 9 однополярных импульсов и блок 10 объединения двух потоков однополярных импульсов. Преобразователь работает следующим образом. Импульсы исходного двоичного сигнала (фиг. 2а) длительностью Т (Т тактовый интервал исходного двоичного сигнала) поступают на вход инвертора 1 и одновременно на первые входы элементов И 6 и 7 и счетный вход реверсивного счетчика 2, который должен быть вьшолнен с четным модуле счета. С выхода инвертора 1 инвертированный входной сигнал (фиг. 26) поступает на счетный вход первого триггера 3 со счетным входом (который может быть выполнен в виде синхронного триггера, момент переключени которого определяется сигналом такто вой частоты), этот триггер переключае ся в конце каждого тактового интервала, на котором имеется единичная посылка сигнала на выходе инвертора т.е. нулевая посылка исходного двоичного сигнала, и его выходной сигнал (фиг. 26) поступает на первый вход сумматора 5 по модулю два. Реверсивньй счетчик 2 считает единичные посылки исходного двоичного сигнала, прибавляя каждый раз единицу к предыдующему значению своего внутреннего сигнала (фиг. 2г), при единичном значении сигнала (фиг. 2ж) на его вхо де управления, или вьиитая каждый раз

единицу от предьщущего значения своего внутреннего сигнала i (фиг. 20, при нулевом значении сигнала (.фиг.2ldПри достижении любого крайнего состояния (N 2) реверсивный счетчик 2 выдает на своем выходе переноса единичную посылку сигнала (фиг.2о). Реверсивный счетчик 2 может быть вьшолнен в виде синхронного реверсивного счетчика, момент переключения которого определяется сигналом тактовой частоты. Сигнал (фиг. 2о) с выхода переноса реверсивного счетчика 2 поступает на счетный вход второго триггера 4 со счетным входом, который также может быть выполнен в виде синхронного триггера, момент переключения которого определяется

ла, которые совпадают со значением 1 сигнала на прямом выходе сумматора 5 по модулю два, а на выход вто45 рого элемента И 7 проходят (фиг.2К) те импульсы исходного двоичного сигнала, которые совпадают со значением О сигнала на прямом выходе сумматора 5 по модулю два. Сигнал с прямо50 го выхода сумматора 5 по модулю два управляет направлением счета реверсивного счетчика 2. Импульсы сигналов (фиг.2 м ,к) далее поступают на входы формирователей 8 и 9 однопо55 лярных импульсов соответственно. Каждый формирователь однополярных импульсов в ответ на каждый импульс на его входе формирует на своем выходе прямоугольный импульс длительсигналом тактовой частоты. Этот трит;гер переключается в конце каждого тактового интервала, на котором имеется единичная посылка сигйала переноса (фиг. 2), и с его выхода сигнал (фиг. 2е) поступает на второй вход сумматора 5 по модулю два. Двоичный выходной сигнал на прямом выходе сумматора 5 по модулю два (фиг.2.} принимает значение 1 (высокий потенциал) в том случае, если на его входах имеются различные значения сигналов, т.е. О и 1 или 1 и О. Если на двух входах сумматора 5 по модулю два имеются одинаковые значения сигналов, т.е. О и О или 1 и 1, то сигнал на прямом выходе сумматора 5 по модулю два принимает значение О (низкий потенциал). Сигнал (фиг. 2з) на инверсном выходе сумматора 5 по модулю два всегда противоположен сигналу на прямом выходе сумматора 5 по модулю два, т.е. значение 1 сигнала на инверсном выходе сумматора 5 по модулю два всегда совпадает со значением О сигнала на прямом выходе сумматора 5 по модулю два и наоборот, следовательно, сигнал (фиг. 2i) изменяется одновременно с сигналом (фиг. ). Сигналы с прямого и инверсного выходов сумматора 5 по модулю два поступают на вторые входы соответственно первого и второго элементов И 6 и 7, а сигнал с прямого выхода сумматора 5 по модулю два, кроме того, поступает на вход управления реверсивного счетчика. Следовательно, на выход первого элемента И 6 проходят (фиг. 2И) те импульсы исходного двоичного сигнаностью 0,5 Т, жестко привязанный по своему временному положению к определенному месту в пределах тактового интервала (например, расположенный строго в его первой половине). С целью обеспечения необходимых параметров импульсов формирователя в нем обычно используется сигнал тактовой частоты (т.ч.), который поступает от синхрогенератора, общего с источником исходного двоичного сигнала, и имеет вид меандра с длительностью полупериодов 0,5 Т. Однополярные сигналы (фиг. 2/1 и фиг. 2л), образующиеся на выходах формирователей 8 и 9, однополярных (положительных) импульсов, объединяются в блоке 10 объе динения двух потоков однополярных импульсов в один квазитроичный сигнал (фиг. 2к). Блок 10 может быть пассивньм устройством, например, он может представлять собой двухтактовый трансформатор, в этом случае формирователи 8 и 9 однополярных импульсов должны обеспечивать на выходах необходимые амплитуды (мощности) импульсов, которые проходят на выход блока 10 объединения двух потоков однополярных импульсов. Однако в общем случае блок 10 может содержать и усилители мощности сигналов, причем эти усилители могут работать как в линейном, так и в ключевом режимах.

Очевидно, когда импульсы входного исходного двоичного сигнала проходят на выход первого элемента И 6, тогда в сигнале на выходе блока 10 объединения двух потоков однополярных импульсов появляются положительные импульсы, а когда импульсы исходного дискретного сигнала проходят на выход второго элемента И 7, тогда в выходном сигнале появляются отрицательные импульсы, причем одновременно с изменением полярности импульсов выходного сигнала изменяется и направление счета реверсивного счетчика 2. Управление полярностью импульсов выходного сигнала и направлением счета реверсивного счетчика 2 происходит с помощью выходного сигнала сумматора 5 по модулю два. Изменение этого сигнала (фиг. 2ж) происходит в одном из следующих двух случаев. Во-первых, реверсивный счетчик 2 достигает одного из крайних состояний, а на его выходе появляется нечетное число импульсов сигнала переноса (тактовые ин-тервалы 4, 8, 17, 22, 28 на фиг.2),

вследствие чего изменяется значение сигнала (фиг. 26) на втором входе сумматора 5 по модулю два (А). Вовторых, в исходном двоичном сигнале (фиг. 2а) появляется нечетное число нулевьЕх посылок подряд (тактовые интервалы 13 и 20 (фиг. 2), вследствие чего изменяется значение сигнала (фиг. 2Ь) на Первом входе сумматора 5 по модулю два (Б).

Очевидно, что изменение направления счета реверсивного счетчика 2 по причине (А) приводит к тому, что цифровая сумма, выходной сигнал, определяемая выражением

t

(l

N (i,

Ь 1

где dL +1 , если на i -м тактовом интервале имеется положительный импульс (выходного сигнала), Оi -1, если на « -м тактовом интервале имеется отрицательный импульс; (3 О, если на -t -м тактовом интервале нет импульса (нулевая посылка выходного сигнала), оказывается ограниченной, причем,в отличие от известного устpoйctвa,поскольку диапазон счета реверсивного счетчика NO 4, INItJ l. (2)

Таким образом, в выходном сигнале не может накапливаться преобладание положительных или отрицательных импульсов, т.е. выходной сигнал преобразователя является сбалансированным и, следовательно, его энергетический спектр должен быть равен нулю на нулевой частоте (отсутствие постоянной составляющей) и на частотах, краных тактовой частоте этого сигнала, что и подтверждается расчетом спектр

Изменение направления счета реверсивного счетчика 2 по причине (Б) приводит к тому, что импульсы выходного сигнала, разделенные нечетным числом нулевых посылок, имеют различные знаки. Такая закономерность чередования знаков посылок ведет к тому, что,кроме описанных особенностей, энергетический спектр выходного сигнала преобразователя имеет нулевые значения на частотах

.(2к + 1)-, К 0,1,2,...

причем в полосе частот энергия выходного сигнала -сосредоточена в нижней части этой полосы.

711099268

Таким образом .предложенный преобра- нала в условиях воздействия переходной эователь двоичного сигнала в квазитро- помехи на ближнем конце в симметричном ичныи сигнал обеспечивает повышение кабеле путем концентрации энергии этопомехозащищенности квазитроичного сиг- го сигнала в нижней части полосы частот

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного сигнала в квазитроичный | 1982 |

|

SU1095430A1 |

| Способ тактовой синхронизации приемника двоичного частотно-модулированного сигнала и устройство для его осуществления | 1980 |

|

SU1361727A1 |

| Устройство для преобразования двоичного кода в квазитроичный | 1977 |

|

SU640435A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА ВО МНОГОЗНАЧНЫЙ КОД (ВАРИАНТЫ) | 1997 |

|

RU2109400C1 |

| Цифровой фильтр | 1988 |

|

SU1569957A1 |

| Преобразователь двоичного сигнала в балансный пятиуровневый сигнал | 1981 |

|

SU987832A1 |

| ПРЕОБРАЗОВАТЕЛЬ СТЫКОВ ДЛЯ ПЕРЕДАЧИ ЦИФРОВЫХ СИГНАЛОВ (ВАРИАНТЫ) | 1994 |

|

RU2105413C1 |

| Устройство формирования много-СТупЕНчАТОгО КВАзиСиНуСОидАльНОгОТРЕХфАзНОгО НАпРяжЕНия | 1978 |

|

SU809437A1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| Цифровой приемник дельта-модулированных сигналов | 1989 |

|

SU1732499A1 |

ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО СИГНАЛА В КВАЗИТРОИЧНЫЙ СИГНАЛ, содержащий два элемента И, выходы которых через соответствующие формирователи однополярньк импульсов подключены к входам блока объединения двух потоков однополярньк импульсов, выход которого является выходом преобразователя, отличающийся тем, что, с целью повьппения помехозащищенности квазитроичного сигнала в условиях воздействия переходной помехи, в него введены сумматор по модулю два, два триггера со счетным входом, инвертор и реверсивный счетчик, счетный вход которого объединен с первыми входами первого и второго элементов И, входом инвертора и является входом преобразователя, при этом выход инвертора через первый триггер со счетным входом подключен к первому входу сумматора по моду-пю два, к второму входу которого через второй триггер со счетным входом подключен выход переноса реверсивного счетчика, к входу управления которого, а также i к второму входу первого элемента И подключен прямой выход сумматора по (Л модулю два, инверсный выход которого подключен к второму входу второго .элемента И. ю

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для преобразования двоичного кода в квазитроичный | 1977 |

|

SU640435A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

Авторы

Даты

1984-08-23—Публикация

1983-03-04—Подача