13

Изобретение относится к радиотех- ргмке и може.т быть использовано для фильтрации шумоподобных сигналов (ШПС).

Цель изобретения - повьшение быстродействия .

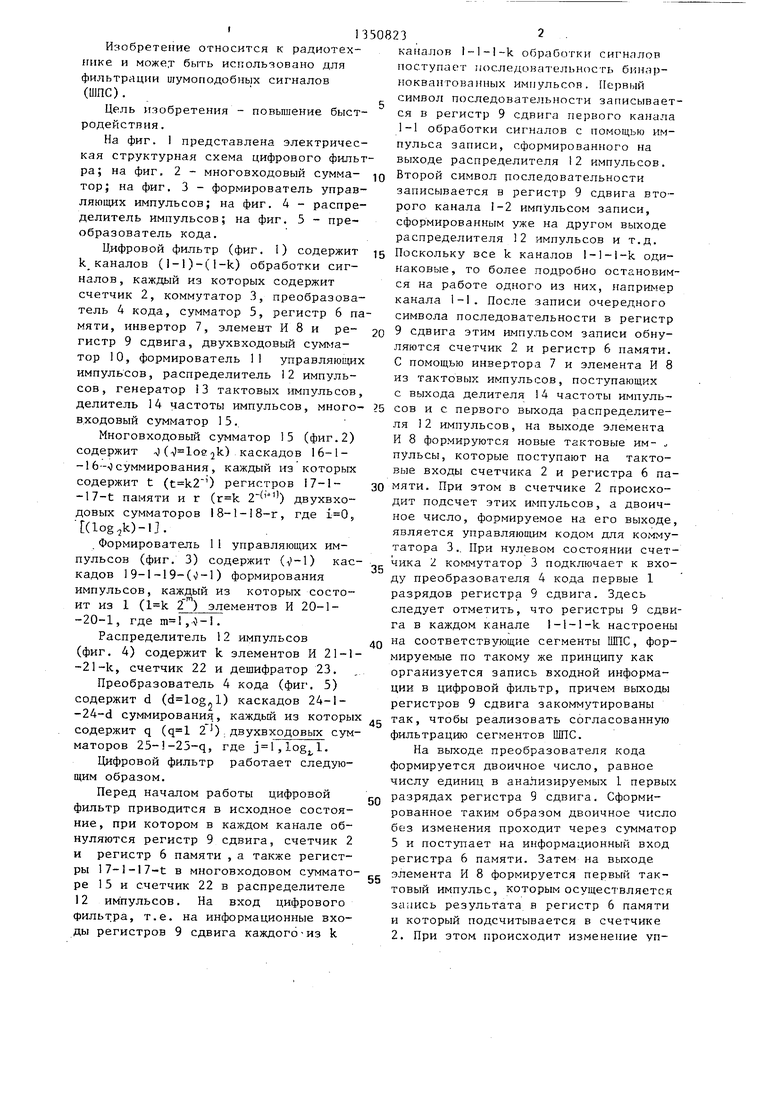

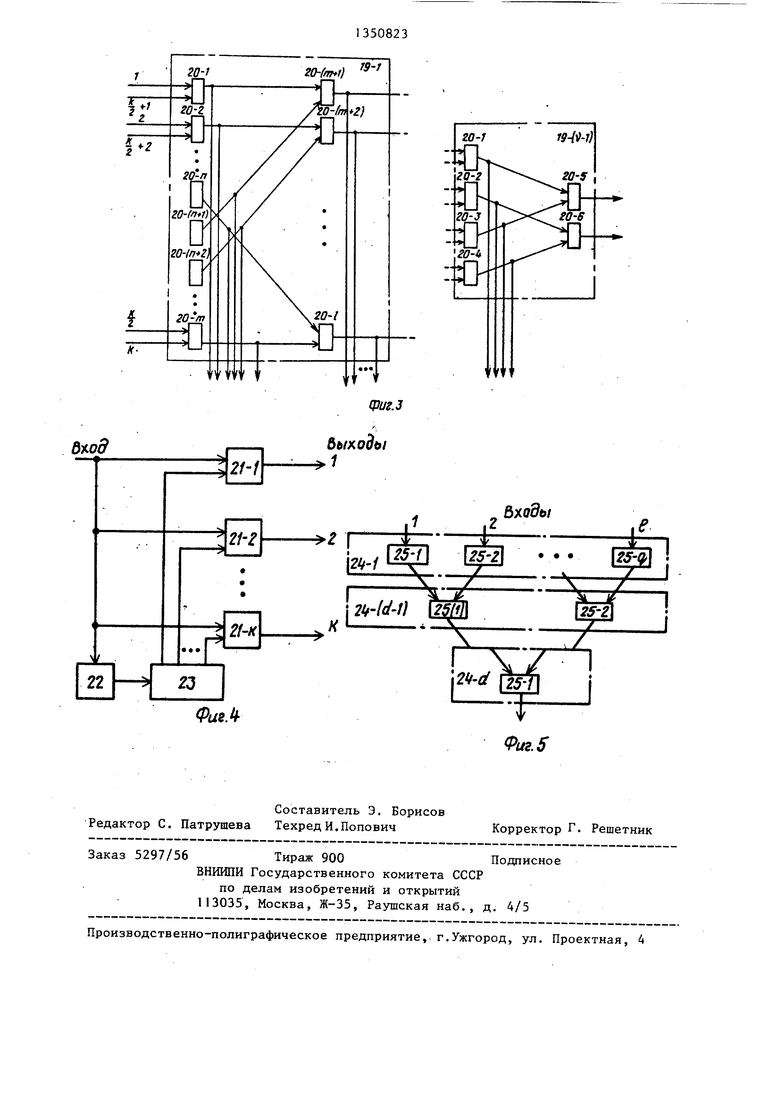

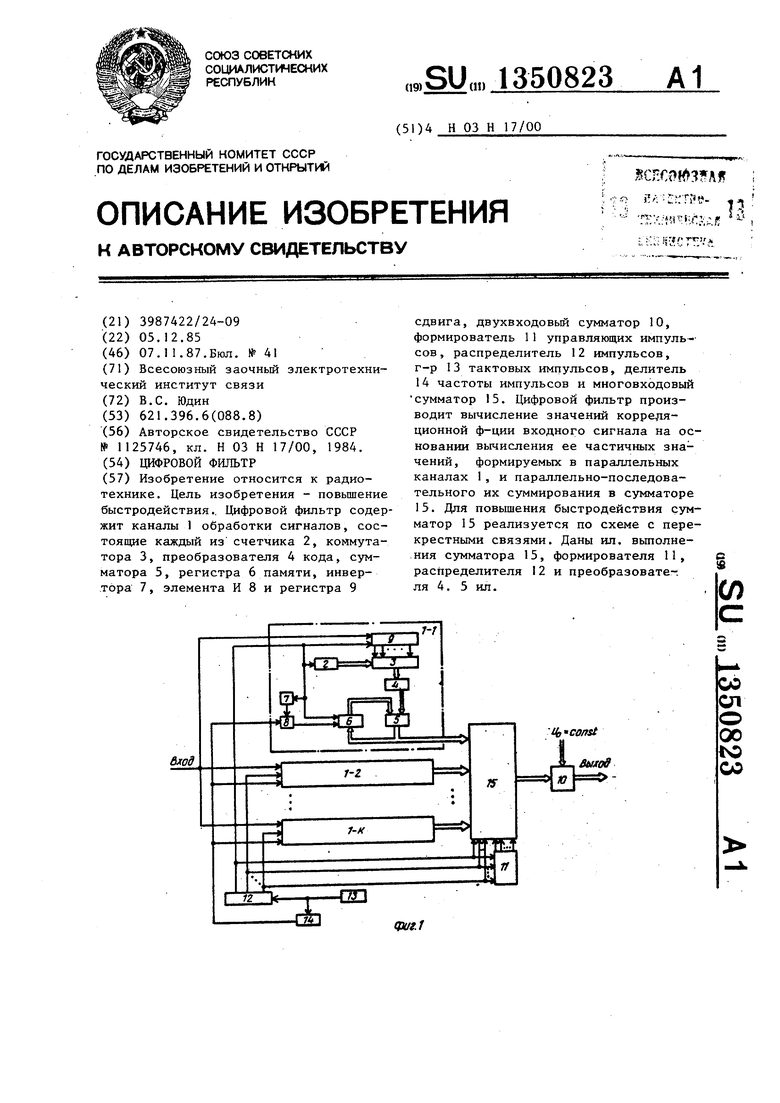

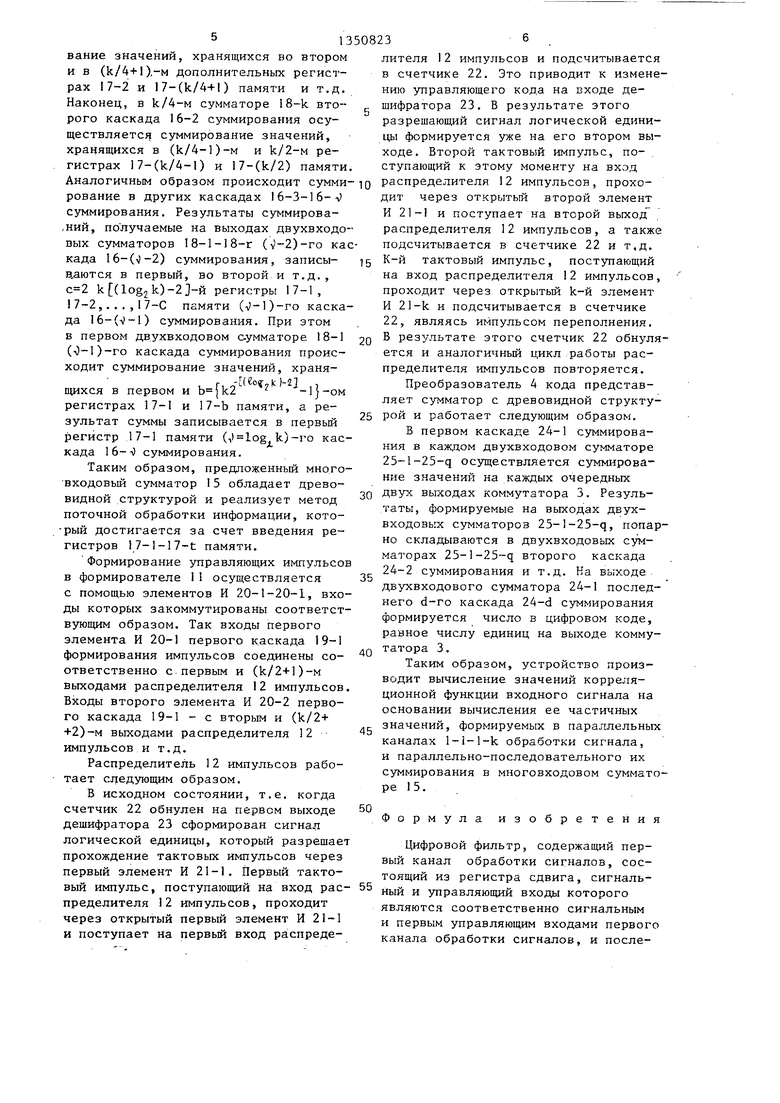

На фиг. 1 представлена электрическая структурная схема цифрового фильт ра; на фиг. 2 - многовходовый сумматор; на фиг, 3 - формирователь управляющих импульсов; на фиг. 4 - распределитель импульсов; на фиг. 5 - преобразователь кода.

Цифровой фильтр (фиг. I) содержит k каналов (i-l)-(l-k) обработки сигналов , каждый из которых содержит счетчик 2, коммутатор 3, преобразователь 4 кода, сумматор 5, регистр 6 па мяти, инвертор 7, элемент И 8 и регистр 9 сдвига, двухвходовый сумматор 10, формирователь 11 управляющих импульсов, распределитель 12 импульсов, генератор 3 тактовых импульсов, делитель 14 частоты импульсов, многовходовый сумматор 15.

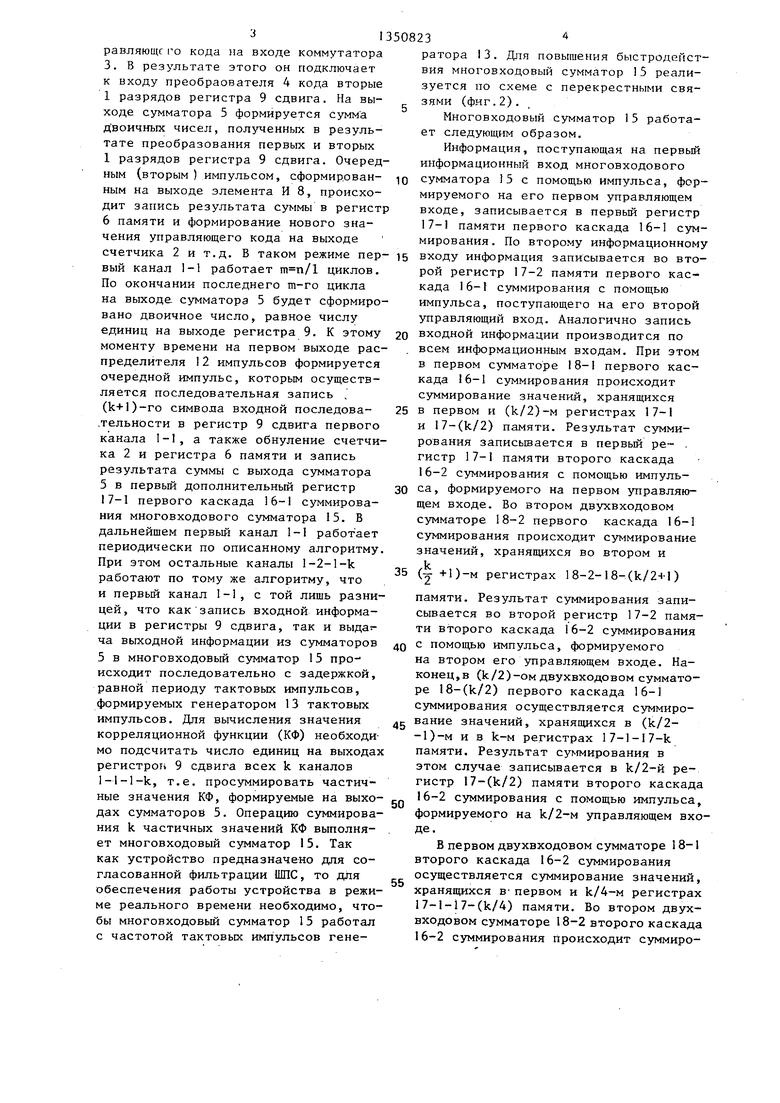

Многовходовый сумматор 15 (фиг.2) содержит л) ( jk) каскадов 16-1- -1 б-л}суммирования, каждый из которых содержит t () регистров 17-1- -17-t памяти и г ( ) двухвхо- довых сумматоров 18-1-18-г, где , (log,k)-lj.

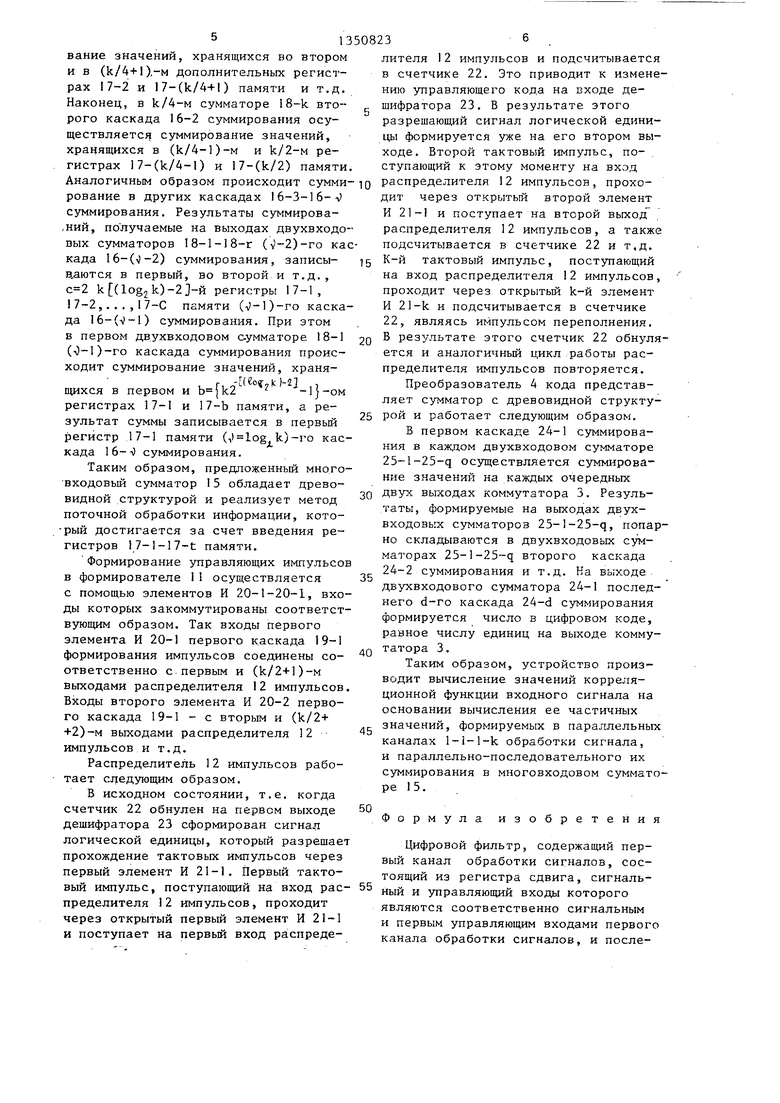

Формирователь 11 управляющих импульсов (фиг. 3) содержит (i)l) каскадов 1 9-1-19-(iJ-l) формирования импульсов, каждый из которых состоит из 1 ( 2 ) элементов И 20-1- -20-1, где т,}-.

Распределитель 12 импульсов (фиг. 4) содержит k элементов И 21-1- -21-k, счетчик 22 и дешифратор 23.

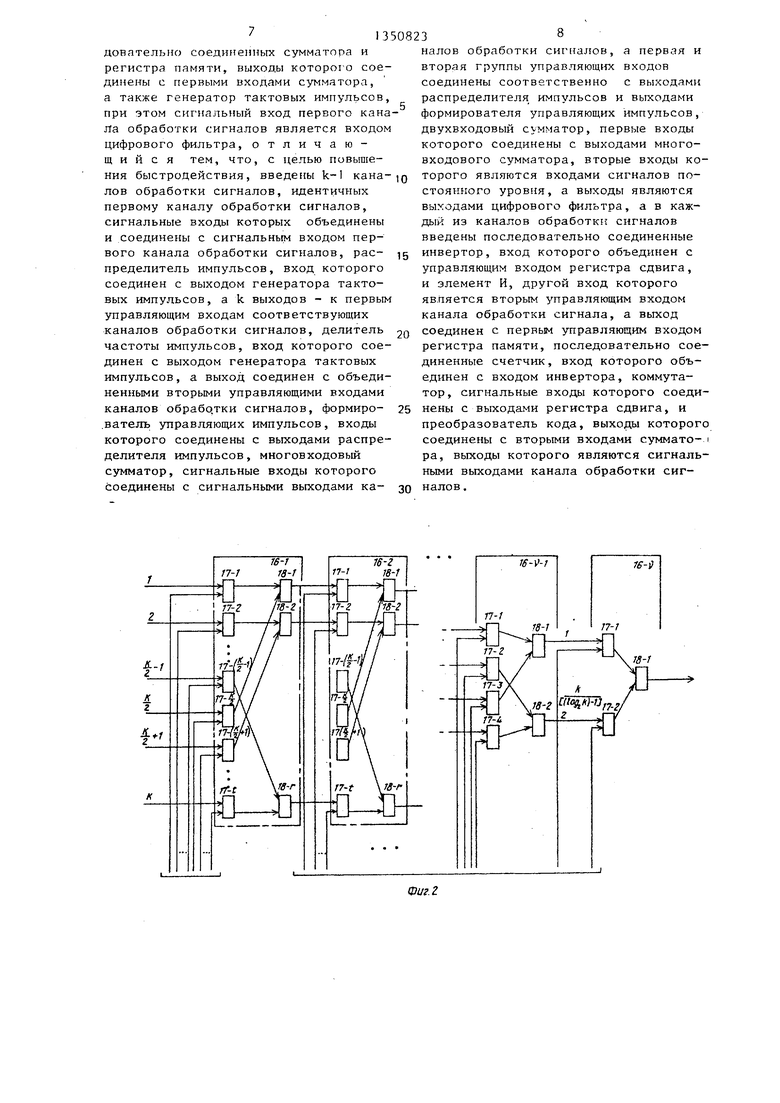

Преобразователь 4 кода (фиг . 5) содержит d (.l) каскадов 24-1- -24-d суммирования, каждый из которых содержит q ( 2) - двухвходовых сумматоров 25- -25-q, где j l,log.l.

Цифровой фильтр работает следующим образом.

Перед началом работы цифровой фильтр приводится в исходное состояние, при котором в каждом канале обнуляются регистр 9 сдвига, счетчик 2 и регистр 6 памяти , а также регистры 17-1-17-t в многовходовом сумматоре 1 5 и счетчик 22 в распределителе 12 импульсов. На вход цифрового фильтра, т.е. на информационные входы регистров 9 сдвига каждого-из k

08232

каналов 1-1-1-k обработки сигналов поступает последовательность бинар- ноквантоваиных импульсов. Первый символ последовательности записывает ся в регистр 9 сдвига первого ка)1ала 1-1 обработки сигналов с помощью импульса записи, сформированного на выходе распределителя 12 импульсов.

Q Второй символ последовательности

записывается в регистр 9 сдвига второго канала 1-2 импульсом записи, сформированным уже на другом выходе распределителя 12 импульсов и т.д.

5 Поскольку все k каналов l-1-i-k одинаковые, то более подробно остановимся на работе одного из них, например канала 1-1. После записи очередного символа последовательности в регистр

0 9 сдвига этим импульсом записи обнуляются счетчик 2 и регистр 6 памяти. С помощью инвертора 7 и элемента И 8 из тактовых импульсов, поступающих с выхода делителя 14 частоты импуль25 сов и с первого выхода распределителя 12 импульсов, на выходе элемента И 8 формируются новые тактовые им- пульсы, которые поступают на тактовые входы счетчика 2 и регистра 6 па0 мяти. При этом в счетчике 2 происходит подсчет этих импульсов, а двоичное число, формируемое на его выходе, является управляюп1им кодом для коммутатора 3.. При нулевом состоянии счетчика 2 коммутатор 3 подключает к входу преобразователя 4 кода первые 1 разрядов регистра 9 сдвига. Здесь следует отметить, что регистры 9 сдвига в каждом канале 1-1-1-k настроены

Q на соответствующие сегменты ШС, формируемые по такому же принципу как организуется запись входной информации в цифровой фильтр, причем вькоды регистров 9 сдвига закоммутированы

с так, чтобы реализовать согласованную фильтрацию сегментов ШПС.

На выходе преобразователя кода формируется двоичное число, равное числу единиц в анализируемых 1 первых

П разрядах регистра 9 сдвига. Сформированное таким образом двоичное число без изменения проходит через сумматор 5 и поступает на информационный вход регистра 6 памяти. Затем на выходе элемента И 8 формируется первый тактовый импульс, которым осуществляется запись результата, в регистр 6 памяти и который подсчитывается в счетчике 2. При этом происходит изменение уп35

55

равляющг го кода на входе коммутатора 3. В результате этого он подключает к входу преобраователя 4 кода вторые 1 разрядов регистра 9 сдвига. На выходе сумматора 5 формируется сумма Двоичных чисел, полученных в результате преобразования первых и вторых 1 разрядов регистра 9 сдвига. Очередным (вторым ) импульсом, сформирован-

ным на выходе элемента И 8, происходит запись результата суммы в регистр 6 памяти и формирование нового значения управляющего кода на выходе счетчика 2 и т.д. В таком режиме пер- вый канал 1-1 работает циклов. По окончании последнего т-го цикла на выходе, сумматора 5 будет сформировано двоичное число, равное числу единиц на выходе регистра 9, К этому моменту времени на первом выходе распределителя 12 импульсов формируется очередной импульс, которым осуществляется последовательная запись , (k+l)-ro символа входной последова- .тельности в регистр 9 сдвига первого канала 1-1, а также обнуление счетчика 2 и регистра 6 памяти и запись результата суммы с выхода сумматора 5 в первьй дополнительный регистр 17-1 первого каскада 16-1 суммирования многовходового сумматора 15. В дальнейшем первый канал 1-1 работ ает периодически по описанному алгоритму При этом остальные каналы l-2-l-k работают по тому же алгоритму, что и первьш канал 1-1, с той лишь разницей, что как запись входной информации в регистры 9 сдвига, так и выдача выходной информации из сумматоров 5 в многовходовый сумматор 13 происходит последовательно с задержкой, равной периоду тактовых импульсов, формируемых генератором 13 тактовых импульсов. Для вычисления значения корреляционной функции (КФ) необходимо подсчитать число единиц на выходах регистрон 9 сдвига всех k каналов 1-1-1-k, т.е. просуммировать частичные значения КФ, формируемые на выхо- дах сумматоров 5. Операцию суммирования k частичных значений КФ выполня- ет многовходовый сумматор 15. Так как устройство предназначено для согласованной фильтрации ШПС, то для обеспечения работы устройства в режиме реального времени необходимо, чтобы многовходовый сумматор 15 работал с частотой тактовых импульсов гене

0 5 О о g g

5

ратора 13. Для повышения быстродействия многовходовый сумматор 15 реализуется по схеме с перекрестными связями (фиг.2).

Многовходовый сумматор 15 работает следующим образом.

Информация, поступающая на первый информационный вход многовходового сумматора 15 с помощью импульса, формируемого на его первом управляющем входе, записывается в первый регистр 17-1 памяти первого каскада 16-1 суммирования. По второму информационному входу информация записывается во второй регистр 17-2 памяти первого каскада 16-1 суммирования с помощью импульса, поступающего на его второй управляющий вход. Аналогично запись входной информации производится по всем информационным входам. При этом в первом сумматоре 18-1 первого каскада 16-1 суммирования происходит суммирование значений, хранящихся в первом и (k/2)-M регистрах 17-1 и 17-(k/2) памяти. Результат суммирования записьшается в первьш ре- . гистр 17-1 памяти второго каскада 16-2 суммирования с помощью импульса, формируемого на первом управляющем входе. Во втором двухвходовом сумматоре 18-2 первого каскада 16-1 суммирования происходит суммирование значений, хранящихся во втором и

( +1)-м регистрах 1 8-2-1 8-(k/24-l )

памяти. Результат суммирования записывается во второй регистр 17-2 памяти второго каскада 16-2 суммирования с помощью импульса, формируемого на втором его управляющем входе. Наконец, в (k/2)-ом двухвходовом сумматоре 18-(k/2) первого каскада 16-1 суммирования осуществляется суммирование значений, хранящихся в (k/2- -1)-м и в k-M регистрах 17-1-17-k памяти. Результат суммирования в этом случае записывается в k/2-й регистр 17-(k/2) памяти второго каскада 16-2 суммирования с помощью импульса, формируемого на k/2-м управляющем входе.

В первом двухвходовом сумматоре 18-1 второго каскада 16-2 суммирования осуществляется суммирование значений, хранящихся в- первом и k/4-м регистрах 17-1-17-(k/4) памяти. Во втором двухвходовом сумматоре 18-2 второго каскада 16-2 суммирования происходит суммирование значений, хранящихся во втором и в (k/4+l),-M дополнительных регистрах 17-2 и 17-(k/4+l) памяти и т.д. Наконец, в k/4-м сумматоре 18-k второго каскада 16-2 суммирования осуществляется суммирование значений, хранящихся в (k/4-l)-M и k/2-м регистрах 17-(k/4-l) и 17-(k/2) памяти.

13508236

лителя I2 импульсов и подсчитывается в счетчике 22. Это приводит к изменению управляющего кода на входе дешифратора 23. В результате этого разрешающий сигнал логической единицы формируется уже на его втором выходе. Второй тактовый импульс, поступающий к этому моменту на вход

20

25

30

Аналогичным образом происходит сумми-io распределителя 12 импульсов, прохо- рование в других каскадах 16-3-16-V суммирования. Результаты суммирова- ,ний, получаемые на выходах двухвходо- вых сумматоров 18-1-18-г (V-2)-ro каскада 16-(-2) суммирования, записы- 15 в,аются в первый, во второй и т.д., k {log2k) регистры 17-1, 7-2,. . . , 1 7-С памяти (V-O-ro каскада 16-() суммирования. При этом в первом двухвходовом сумматоре 18-1 (0-1)-го каскада суммирования происходит суммирование значений, храня, г, ., , щихся в первом и -1)-ом

регистрах 17-1 и 17-Ь памяти, а результат суммы записывается в первый регистр 17-1 памяти (i)log k)ro каскада 1 6--О суммирования.

Таким образом, предложенный много- входовьй сумматор 15 обладает древовидной структурой и реализует метод поточной обработки информации, кото- рый достигается за счет введения регистров 17-1-17-t памяти.

Формирование управляющих импульсов в формирователе 1I осуществляется 35 с помощью элементов И 20-1-20-1, входы которых закоммутированы соответствующим образом. Так входы первого элемента И 20-1 первого каскада 19-1 формирования импульсов соединены соответственно с первым и (k/2+l)-M выходами распределителя 12 импульсов. Входы второго элемента И 20-2 первого каскада 19-1 - с вторым и (k/2+ +2)-м выходами распределителя 12 45 импульсов и т.д.

Распределитель 12 импульсов работает следующим образом.

В исходном состоянии, т.е. когда счетчик 22 обнулен на первом выходе 50 дешифратора 23 сформирован сигнал логической единицы, который разрешает прохождение тактовых импульсов через первый элемент И 21-1. Первый тактовый импульс, поступающий на вход рас- 55 пределителя 12 импульсов, проходит через открытый первый элемент И 21-1 и поступает на первый вход распреде40

дит через открытый второй элемент И 21-1 и поступает на второй выход распределителя 12 импульсов, а также подсчитывается в счетчике 22 и т,д. К-й тактовый импульс, поступающий на вход распределителя 12 импульсов проходит через открытьш k-й элемент И 21-k и подсчитывается в счетчике 22, являясь импульсом переполнения. Б результате этого счетчик 22 обнуля ется и аналогичный цикл работы распределителя импульсов повторяется.

Преобразователь 4 кода представляет сумматор с древовидной структурой и работает следующим образом.

В первом каскаде 24-1 суммирования в каждом двухвходовом сумматоре 25-1-25-q осуществляется суммирование значений на каждых очередных двух выходах коммутатора 3. Результаты, формируемые на выходах двух- входовых сумматоров 25-1-25-q, попа но складываются в двухвходовых сумматорах 25-1-25-q второго каскада 24-2 суммирования и т.д. На выходе двухвходового сумматора 24-1 послед него d-ro каскада 24-d суммирования формируется число в цифровом коде, равное числу единиц на выходе комму татора 3.

Таким образом, устройство производит вычисление значений корреляционной функции входного сигнала на основании вычисления ее частичных значений, формируемых в параллельны каналах l-1-l-k обработки сигнала, и параллельно-последовательного их суммирования в многовходовом суммат ре 15.

Формула изобретени

Цифровой фильтр, содержащий первый канал обработки сигналов, состоящий из регистра сдвига, сигнальный и управляющий входы которого являются соответственно сигнальным и первым управляющим входами первог канала обработки сигналов, и после

распределителя 12 импульсов, прохо-

дит через открытый второй элемент И 21-1 и поступает на второй выход распределителя 12 импульсов, а также подсчитывается в счетчике 22 и т,д. К-й тактовый импульс, поступающий на вход распределителя 12 импульсов, проходит через открытьш k-й элемент И 21-k и подсчитывается в счетчике 22, являясь импульсом переполнения. Б результате этого счетчик 22 обнуляется и аналогичный цикл работы распределителя импульсов повторяется.

Преобразователь 4 кода представляет сумматор с древовидной структурой и работает следующим образом.

В первом каскаде 24-1 суммирования в каждом двухвходовом сумматоре 25-1-25-q осуществляется суммирование значений на каждых очередных двух выходах коммутатора 3. Результаты, формируемые на выходах двух- входовых сумматоров 25-1-25-q, попарно складываются в двухвходовых сумматорах 25-1-25-q второго каскада 24-2 суммирования и т.д. На выходе двухвходового сумматора 24-1 последнего d-ro каскада 24-d суммирования формируется число в цифровом коде, равное числу единиц на выходе коммутатора 3.

Таким образом, устройство производит вычисление значений корреляционной функции входного сигнала на основании вычисления ее частичных значений, формируемых в параллельных каналах l-1-l-k обработки сигнала, и параллельно-последовательного их суммирования в многовходовом сумматоре 15.

Формула изобретения

Цифровой фильтр, содержащий первый канал обработки сигналов, состоящий из регистра сдвига, сигнальный и управляющий входы которого являются соответственно сигнальным и первым управляющим входами первого канала обработки сигналов, и последовательно соединенных сумматора и регистра памяти, выходы которого соединены с нервыми входами сумматора, а также генератор тактовых имнульсов, при этом сигнальный вход первого канала обработки сигналов является входом цифрового фильтра, отличающийся тем, что, с целью повышения быстродействия, введе 1ы k-I каналов обработки сигналов, идентичных первому каналу обработки сигналов, сигнальные входы которых объединены и соединены с сигнальньгм входом первого канала обработки сигналов, рас- пределитель импульсов, вход которого соединен с выходом генератора тактовых импульсов, а k выходов - к первым управляющим входам соответствующих каналов обработки сигналов, делитель частоты импульсов, вход которого соединен с выходом генератора тактовых импульсов, а выход соединен с объединенными вторыми управляющими входами каналов обработки сигналов, формиро- .вателъ управляю цих импульсов, входы которого соединены с выходами распределителя импульсов, многовходовый сумматор, сигнальные входы которого соединены с сигнальными выходами ка-

налов обработки сигналов, а первая и вторая группы управляющих входов соединены соответственно с выходами распределителя импульсов и выходами формирователя управляющих импульсов, двухвходовый сумматор, первые входы которого соединены с выходами много- входового сумматора, вторые входы которого являются входами сигналов постоянного уровня, а выходы являются выходами цифрового фильтра, а в каждый из каналов обработки сигналов введены последовательно соединенные инвертор, вход которого объединен с управляющим входом регистра сдвига, и элемент И, другой вход которого является вторым управляющим входом канала обработки сигнала, а выход соединен с первьм управляющим входом регистра памяти, последовательно соединенные счетчик, вход которого объединен с входом инвертора, коммутатор, сигнальные входы которого соединены с выходами регистра сдвига, и преобразователь кода, выходы которого соединены с вторыми входами суммато- pa, выходы которого являются сигнальными выходами канала обработки сигналов ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой рекурсивный фильтр | 1985 |

|

SU1328925A1 |

| УСТРОЙСТВО АНАЛИЗА ПЕРЕКРЫТИЙ КАНАЛОВ ПРИ РАЗМЕЩЕНИИ ПАРАЛЛЕЛЬНЫХ ПОДПРОГРАММ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ | 2011 |

|

RU2460126C1 |

| Генератор псевдослучайных последовательностей | 1981 |

|

SU1023325A1 |

| Радиозотопный уровнемер | 1986 |

|

SU1384957A1 |

| Генератор псевдослучайных последовательностей импульсов | 1981 |

|

SU978147A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 2018 |

|

RU2670389C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Генератор систем базисных функций Аристова | 1988 |

|

SU1599850A1 |

| Устройство поиска степени оптимальности размещения в кластерных многопроцессорных системах при направленной передаче информации | 2022 |

|

RU2798392C1 |

| Декодирующее устройство | 1990 |

|

SU1783626A1 |

Изобретение относится к радиотехнике. Цель изобретения - повьшение быстродействия.. Цифровой фильтр содержит каналы 1 обработки сигналов, состоящие каждый из счетчика 2, коммутатора 3, преобразователя 4 кода, сумматора 5, регистра 6 памяти, инвертора 7, элемента И 8 и регистра 9 сдвига, двухвходовый сумматор 10, формирователь 11 управляющих импуль-- сов, распределитель 12 импульсов, г-р 13 тактовых импульсов, делитель 14 частоты импульсов и многовходовый сумматор 15. Цифровой фильтр производит вычисление значений корреляционной ф-ции входного сигнала на основании вычисления ее частичных значений, формируемых в параллельных каналах 1, и параллельно-последовательного их суммирования в сумматоре 15. Для повышения быстродействия сумматор 15 реализуется по схеме с перекрестными связями. Даны ил. вьтолне- ния сумматора 15, формирователя 11, распределителя 12 и преобразовате-. ля 4. 5 ил. i СЛ С со СЛ о 00 to со ./

бмд

(риг.з быкодй

2

Г

2t-K

2if-ld-i} Щ

23

ФигЛ

блоды

Составитель Э. Борисов Редактор С. Патрушева Техред И.Попович

Заказ 5297/56 Тираж 900Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

Фиг.$

Корректор f. Решетник

| Цифровой фильтр | 1982 |

|

SU1125746A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-11-07—Публикация

1985-12-05—Подача