Изобретение относится к областям радиотехники, измерительной и вычислительной техники и может быть использовано в устройствах интегрирования в системах цифровой обработки сигналов, системах управления и специализированных вычислительных устройствах.

Известно устройство цифрового интегрирования [1] на базе реверсивного счетчика, в котором отсчеты сигнала преобразуются в последовательность импульсов, что снижает точность и скорость вычисления интеграла.

Известны цифровые интеграторы [2-4] на базе накапливающих сумматоров со сбросом, в которых отсутствует возможность непрерывного (текущего) интегрирования по выборке заданного объема, что снижает их быстродействие.

Известны цифровые интеграторы на базе цифровых усредняющих фильтров, например, с окном Дирихле [5] или с конечной импульсной характеристикой [6]. Их недостатком является сложность аппаратной реализации при большой выборке отсчетов сигнала.

Наиболее близким по технической сущности к предлагаемому устройству является цифровой интегратор [7], содержащий аналого-цифровой преобразователь (АЦП), генератор тактовых импульсов, элементы памяти с реверсивными счетчиками и многовходовой многоразрядный сумматор. Его недостатками являются сложность реализации многовходового сумматора и накопление отдельных разрядов отсчетов в реверсивных счетчиках, в которых при наличии ложного срабатывания ошибочный результат будет сохраняться неограниченно долго, что приведет к неустранимому сбою работы интегратора.

Основной операцией, определяющей эффективность цифрового интегрирования, является накопление (последовательное суммирование) отсчетов из выборки заданного объема, увеличение которого повышает точность результата, но усложняет аппаратную реализацию устройства.

Задачей предлагаемого технического решения является обеспечение непрерывного цифрового интегрирования сигнала по выборке отсчетов заданного объема с высокой точностью при минимальных аппаратных затратах.

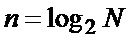

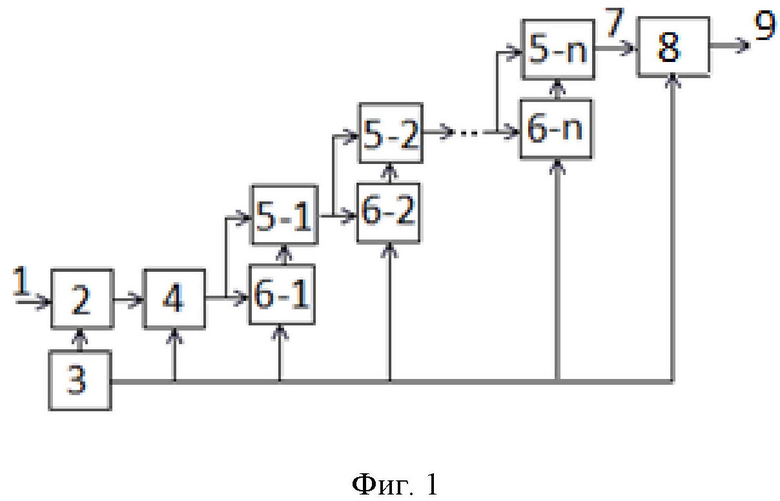

Поставленная задача решается тем, что цифровой интегратор, содержащий АЦП, последовательно соединенный с ним элемент памяти и генератор тактовых импульсов (ГТИ), дополнительно содержит n каскадно соединенных двухвходовых сумматоров (СУМ) (

Предлагаемое техническое решение поясняется чертежами.

На фиг. 1 представлена структурная схема предлагаемого устройства, на фиг. 2 – результаты моделирования работы интегратора при гармоническом входном сигнале, на фиг. 3 – результаты моделирования для импульсного сигнала, а на фиг. 4 – оценка относительной погрешности интегрирования.

Интегрируемый сигнал 1 поступает на вход АЦП 2, который по тактовым импульсам ГТИ 3, выход которого соединен с тактовым входом АЦП 2, формирует отсчеты, которые записываются в ячейку памяти (регистр) 4. Выход ячейки памяти 4 подключен к соединенным между собой первому входу первого сумматора

Устройство работает следующим образом.

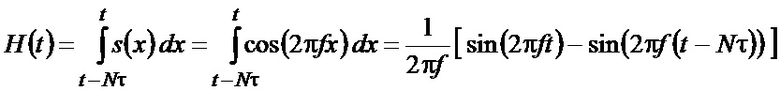

Входной сигнал

с абсолютной погрешностью R, равной [8]

где

Как видно, при заданном интервале интегрирования

Отсчеты

которая складывается в нем с суммой

ранее записанной в регистре сдвига 6-n на

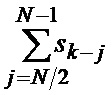

представляющая собой нормированное значение 7 интеграла (1):

Эта величина записывается в регистр результата 8 и на его выходе появляется результат интегрирования 9. После записи суммы отсчетов в регистр результата по импульсам ГТИ содержимое регистров сдвига 6-k (

Нетрудно видеть, что для вычисления полной суммы (3) требуется

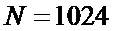

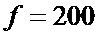

В случае гармонического входного сигнала

Результат имитационного моделирования работы интегратора вида

На фиг. 3а показана временная диаграмма входного импульсного сигнала с периодом, равным

При ограниченной разрядности АЦП погрешность интегрирования значительно увеличивается. На фиг. 4 приведена полученная в результате моделирования зависимость относительной максимальной погрешности

от числа m разрядов АЦП для гармонического сигнала вида фиг. 2а при

С уменьшением амплитуды сигнала погрешность повышается, то есть целесообразно проводить масштабирование преобразования сигнала в последовательность отсчетов. При увеличении объема выборки до

Частота квантования АЦП от ГТИ должна выбираться не менее чем в 30-50 раз выше граничной частоты спектра входного сигнала.

Источники информации

1. Трохин В.М., Перельмутер В.М., Энтина В.И. Цифроаналоговые системы автоматического управления. – К.: Технiка, 1979. – 160 с.

2. Новиков Ю.В. Введение в цифровую схемотехнику. – М.: Интенет-Университет Информационных Технологий; БИНОМ. Лаборатория знаний, 2007. – 343 с.

3. Дрозд А.В., Полин Е.Л., Нестеренко С.А., Николенко А.А., Ногина Е.Н. Устройство цифрового интегрирования // Авторское свидетельство SU 1532922А1, МПК G06F7/64 от 30.12.89 (Бюлл. № 48).

4. Полян Л.Е., Угер В.Г. Цифровой интегратор // Патент № 2029357, МПК G06F7/64 от 20.02.1995; заявка № 5043408/24 от 26.05.1992.

5. Гутников В.С. Фильтрация измерительных сигналов. – Л.: Энергоатомиздат, 1990. – 122 с.

6. Солонина А.И., Улахович Д.А., Арбузов С.М., Соловьева Е.Б. Основы цифровой обработки сигналов. – СПб.: БХВ Петербург, 2005. – 768 с.

7. Ледовских В.И., Бухтияров С.А. Цифровой интегратор // Авторское свидетельство SU 1478214А1, МПК G06F7/64 от 07.05.89 (Бюлл. № 17).

8. Гусак А.А., Гусак Г.М., Бричикова Е.А. Справочник по высшей математике. – Мн.: ТетраСистеис, 1999. – 640 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ИНТЕГРАТОР | 2019 |

|

RU2710990C1 |

| Цифровой измеритель действующего значения сигнала | 2018 |

|

RU2685062C1 |

| Цифровой коррелятор | 2020 |

|

RU2735488C1 |

| Цифровой измеритель параметров случайных процессов с распределением Накагами | 2020 |

|

RU2742695C1 |

| Цифровой измеритель коэффициента корреляции случайного сигнала | 2020 |

|

RU2747725C1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ СТАТИСТИЧЕСКИХ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ СИГНАЛОВ | 2017 |

|

RU2662412C1 |

| ЦИФРОВОЙ ДЕМОДУЛЯТОР СИГНАЛОВ С АМПЛИТУДНО-ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2022 |

|

RU2786159C1 |

| Цифровой когерентный демодулятор сигналов с двоичной относительной фазовой манипуляцией | 2020 |

|

RU2748858C1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ СДВИГА ФАЗ ГАРМОНИЧЕСКИХ СИГНАЛОВ | 2020 |

|

RU2751020C1 |

| Цифровой демодулятор сигналов с амплитудной - относительной фазовой манипуляцией | 2022 |

|

RU2790205C1 |

Изобретение относится к областям радиотехники, измерительной и вычислительной техники и может быть использовано в устройствах интегрирования в системах цифровой обработки сигналов, системах управления и специализированных вычислительных устройствах. Технический результат заключается в обеспечении непрерывного цифрового интегрирования сигнала по выборке отсчетов заданного объема с высокой точностью при минимальных аппаратных затратах. Цифровой интегратор содержит аналого-цифровой преобразователь, элемент памяти, генератор тактовых импульсов, n двухвходовых сумматоров, n регистров сдвига многоразрядных кодов и регистр результата. 4 ил.

Цифровой интегратор, содержащий аналого-цифровой преобразователь, последовательно соединенный с ним элемент памяти и генератор тактовых импульсов (ГТИ), отличающийся тем, что он дополнительно содержит n каскадно соединенных двухвходовых сумматоров (СУМ), n регистров сдвига многоразрядных кодов (МР) и регистр результата (РР), первый вход k-го сумматора (

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1991 |

|

RU2030092C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2007 |

|

RU2344541C1 |

| Цифровой интегратор | 1987 |

|

SU1478214A1 |

| US 4701871, 20.10.1987. | |||

Авторы

Даты

2018-10-22—Публикация

2018-03-26—Подача