Изобретение относится к в.ьгчисли- тельной технике и может использоваться в системах тестового диагности- рования дискретных объектов в качестве источника входных воздействий и анализатора выходных реакций объекта контроля.

Целью изобретения является повышение быстродействия устройства.

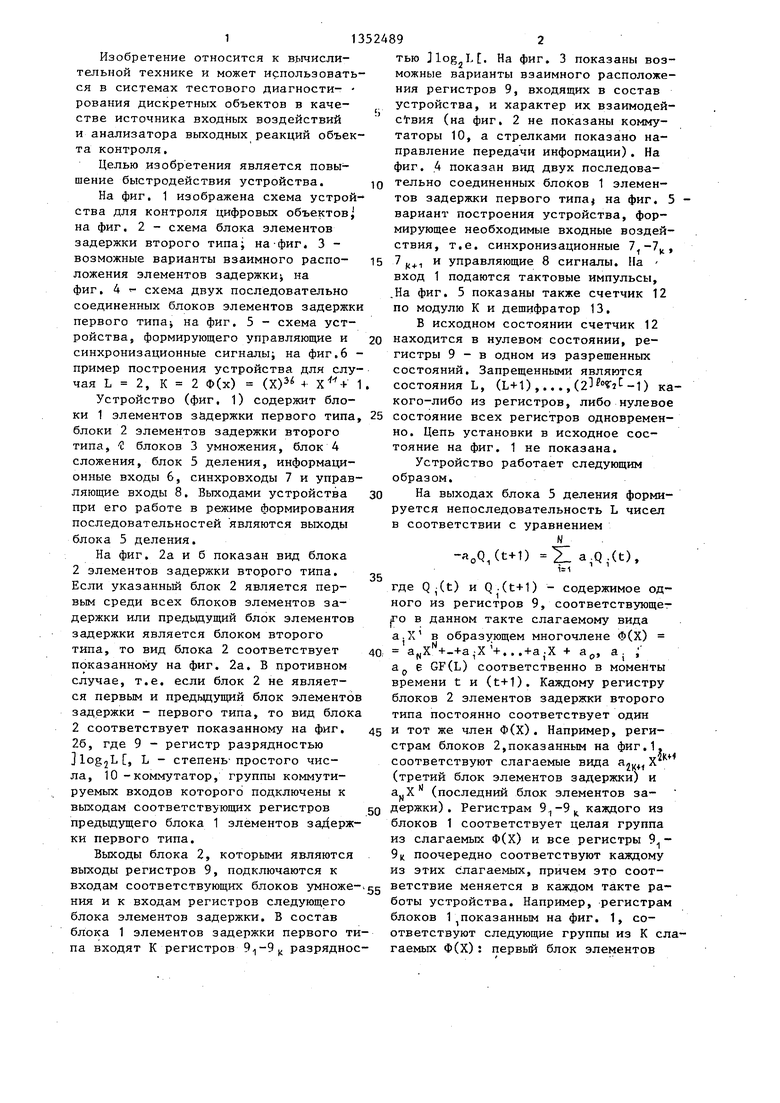

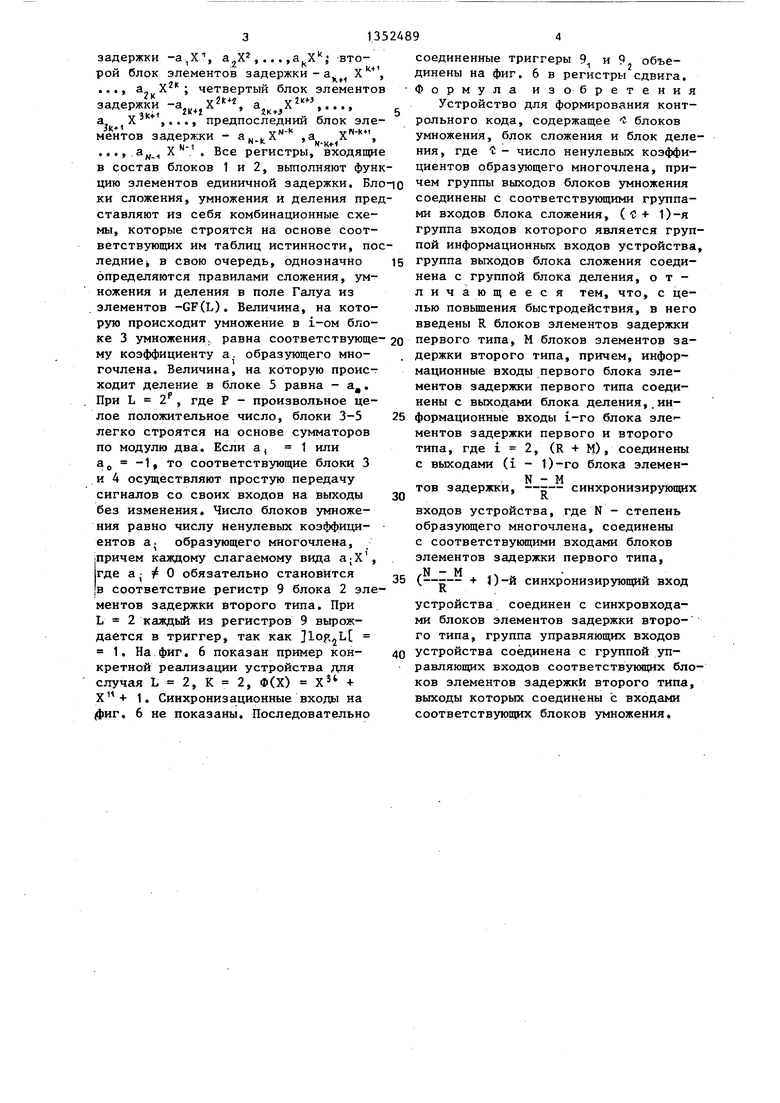

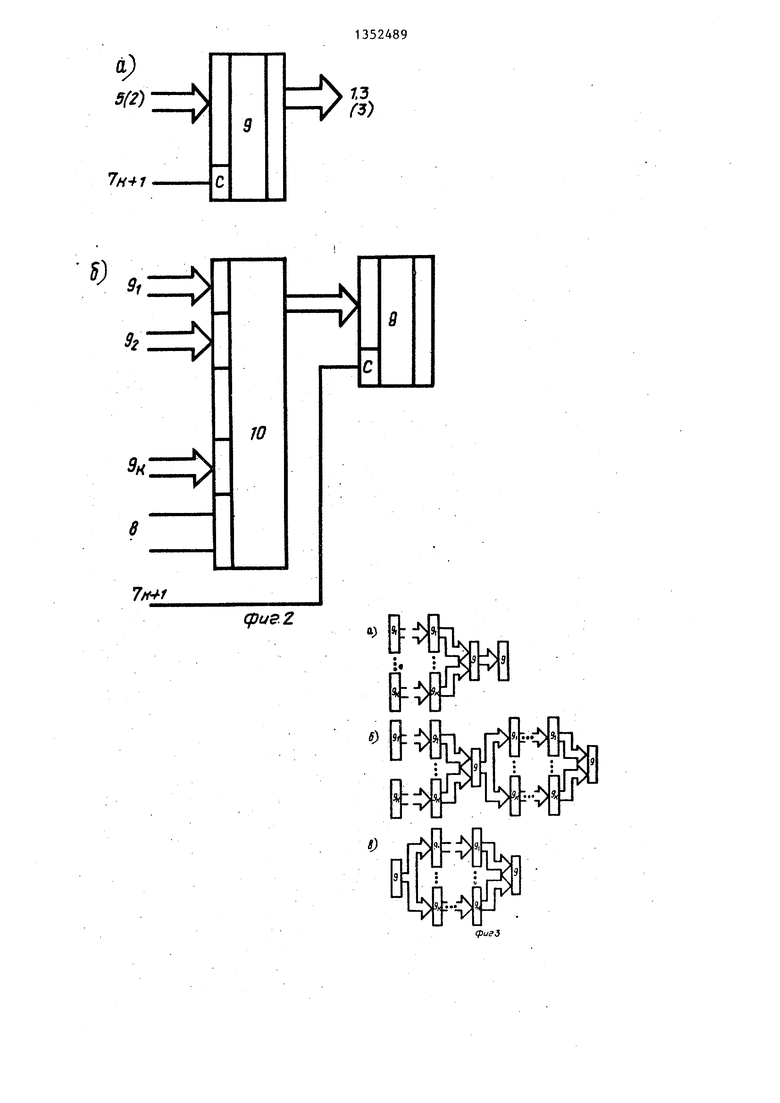

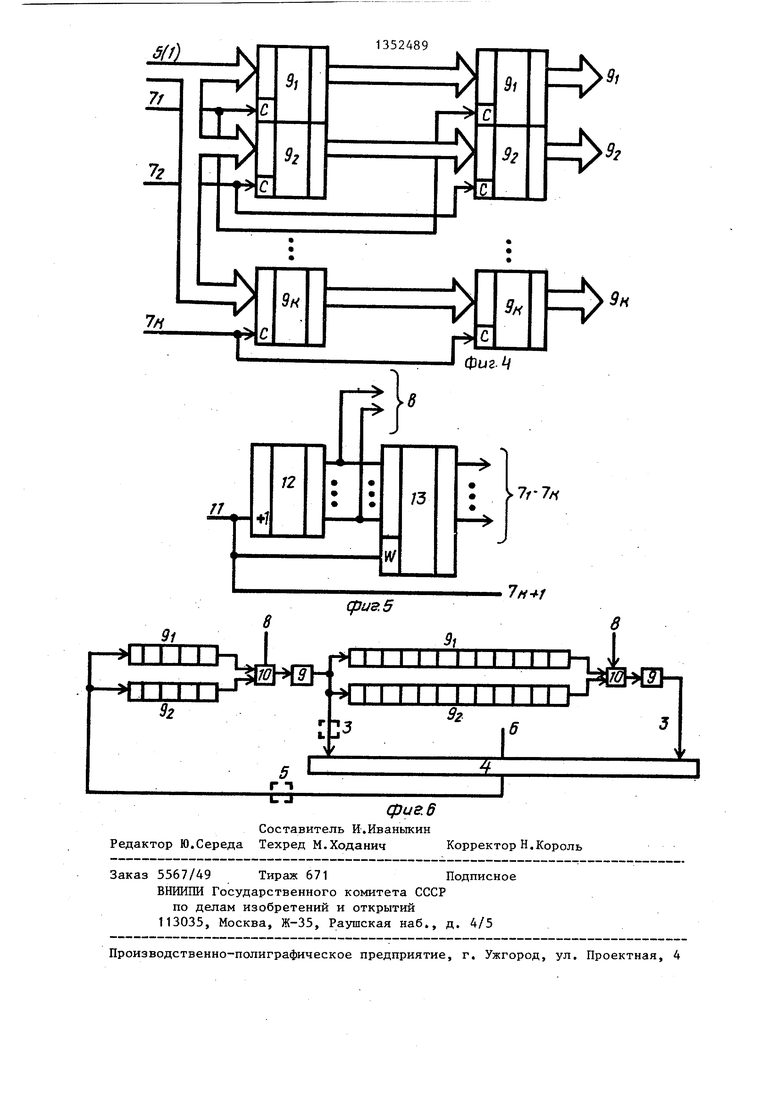

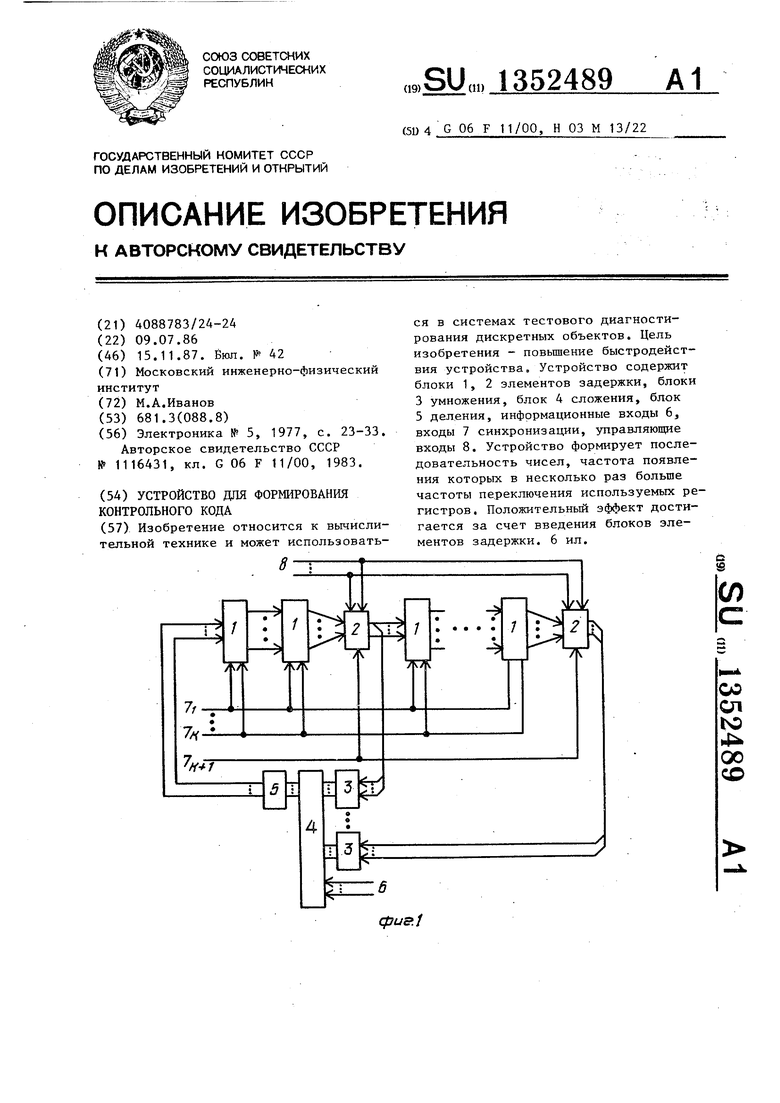

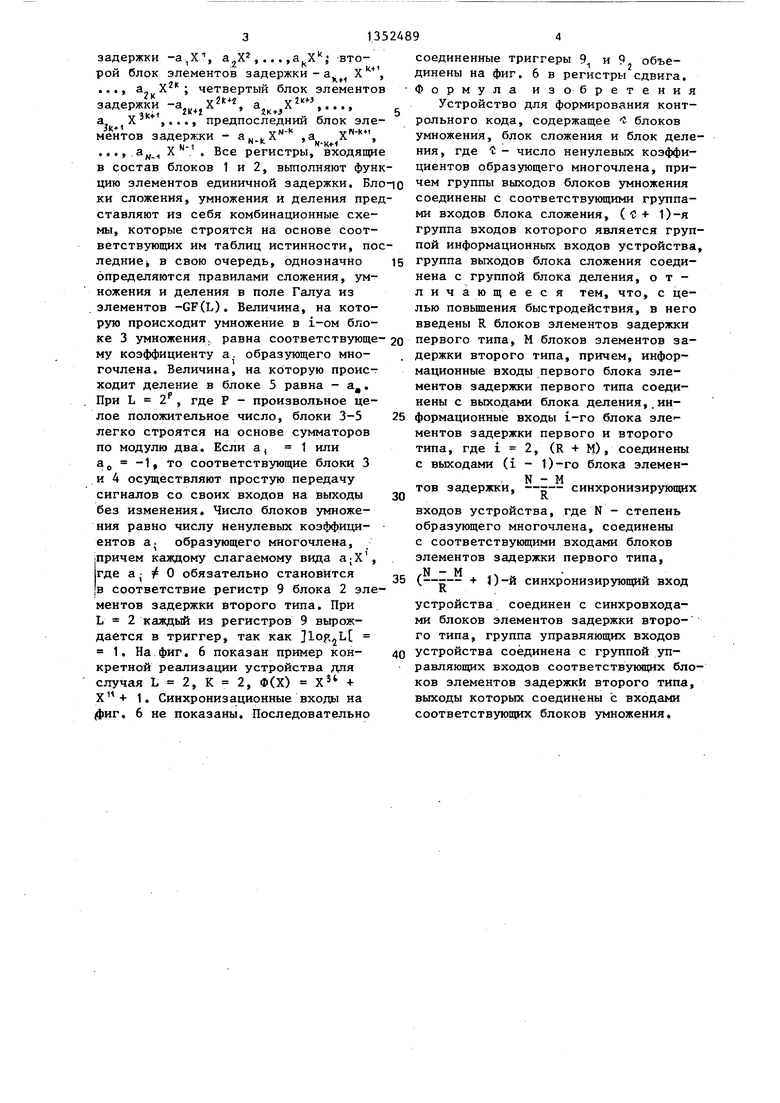

На фиг. 1 изображена схема устройства для контроля цифровых объектов на фиг. 2 - схема блока элементов задержки второго типа; на-фиг. 3 - возможные варианты взаимного распо- ложения элементов задержки на фиг, 4 схема двух последовательно соединенных блоков элементов задержки первого типа на фиг. 5 - схема устройства, формирующего управляющие и синхронизационные сигналы; на фиг.6 - пример построения устройства для случая L 2, К 2 Ф(х) (Х)З 4 Х + 1

Устройство (фиг. 1) содержит блоки 1 элементов задержки первого типа, блоки 2 элементов задержки второго типа, С блоков 3 умножения, блок 4 сложения, блок 5 деления, информационные входы 6, синхровходы 7 и управляющие входы 8. Выходами устройства при его работе в режиме формирования последовательностей являются выходы блока 5 деления.

На фиг. 2а и б показан вид блока 2 элементов задержки второго типа. Если указанный блок 2 является первым среди всех блоков элементов задержки или предьвдущий блок элементов задержки является блоком второго типа, то вид блока 2 соответствует показанному на фиг. 2а. В противном случае, т.е. если блок 2 не является первым и предыдущий блок элементов задержки - первого типа, то вид блика 2 соответствует показанному на фиг. 26, где 9 - регистр разрядностью JlogjLT, L - степень-простого числа, 10 -коммутатор, группы коммутируемых входов которого подключены к выходам соответствующих регистров предыдущего блока 1 элементов зa iepж- ки первого типа.

Выходы блока 2, которыми являются выходы регистров 9, подключаются к входам соответствующих блоков умножения и к входам регистров следующего блока элементов задержки. В состав блока 1 элементов задержки первого типа входят К регистров 9;,-9 JJ разрядностью Jlog L. На фиг. 3 показаны возможные варианты взаимного расположения регистров 9, входящих в состав устройства, и характер их взаимодействия (на фиг. 2 не показаны коммутаторы 10, а стрелками показано направление передачи информации). На фиг. 4 показан вид двух последовательно соединенных блоков 1 элементов задержки первого типа на фиг. 5 вариант построения устройства, формирующее необходимые входные воздействия, т.е. синхронизационные , 7 и управляющие 8 сигналы. На - вход 1 подаются тактовые импульсы, .На фиг. 5 показаны также счетчик 12 по модулю К и дешифратор 13.

Б исходном состоянии счетчик 12 находится в нулевом состоянии, регистры 9 - в одном из разрешенных состояний. Запрещенными являются состояния L, (Ы-1),...,() какого-либо из регистров, либо нулевое состояние всех регистров одновременно. Цепь установки в исходное состояние на фиг. 1 не показана.

Устройство работает следующим образом.

На выходах блока 5 деления формируется непоследовательность L чисел в соответствии с уравнением

N -a,Q(t+1) Х a.Q,.(t),

где Q-(t) и Q.(t+1) - содержимое одного из регистров 9, соответствующего в данном такте слагаемому вида а.Х в образующем многочлене Ф(Х) .Х +...+а;Х + а, а ; а е GF(L) соответственно в моменты времени t и (t+1). Каждому регистру блоков 2 элементов задержки второго типа постоянно соответствует один и тот же член Ф(Х). Например, регистрам блоков 2,показанным на фиг.1 соответствуют слагаемые вида а, X (третий блок элементов задержки) и (последний блок элементов задержки). Регистрам каждого из блоков 1 соответствует целая группа из слагаемых Ф(Х) и все регистры 9 к поочередно соответствуют каждому из этих слагаемых, причем это соответствие меняется в каждом такте работы устройства. Например, регистрам блоков 1 показанным на фиг. 1, соответствуют следующие группы из К слгаемых Ф(Х): первый блок элементов

к

задержки

-а,Х

а,Х ,...а X j

втоk+

2 Ц-

рой блок элементов задержки - а X

Х ; четвертый блок элементов

2К+1

X

2(2

...

iKtJ

2к

задержки -а

,..., предпоследний блок элеМ-К „

«

ц.1 ментов

задержки

К-1

я У N-K,а.

W-1

Все регистры, входящие

соединенные триггеры 9 и 9 объединены на фиг. 6 в регистры сдвига. Формула изобретения Устройство для формирования контрольного кода, содержащее блоков умножения, блок сложения и блок деления, где 1 - число ненулевых коэффив состав блоков 1 и 2, вьтолняют функ- циентов образующего многочлена, при- цию элементов единичной задержки. Бло-ю группы выходов блоков умножения

ки сложения, умножения и деления представляют из себя комбинационные схемы, которые строятсй на основе соответствующих им таблиц истинности, пос- ледние в свою очередь, однозначно определяются правилами сложения, умножения и деления в поле Галуа из элементов -GF(L). Величина, на которую происходит умножение в i-ом блоке 3 умножения, равна соответствующе- 2о первого типа, М блоков элементов задержки второго типа, причем, информационные входы первого блока элементов задержки первого типа соединены с выходами блока деления,,ин- 25 формационные входы i-ro блока эле|- ментов задержки первого и второго типа, где i 2, (R + М), соединены с выходами (i - 1)-го блока элемен. N - М тон задержки, --- синхронизирующих

му коэффициенту а. образующего многочлена. Величина, иа которую происходит деление в блоке 5 равна - а. При L 2 , где Р - произвольное целое положительное число, блоки 3-5 легко строятся на основе сумматоров по модулю два. Если а, 1 или а о -1, то соответствующие блоки 3 и 4 осуществляют простую передачу сигналов со своих входов на выходы без изменения. Число блоков умножения равно числу ненулевых коэффициентов а. образующего многочлена, причем каждому слагаемому вида а;Х , где а О обязательно становится в соответствие регистр 9 блока 2 элементов задержки второго типа. При L 2 каждый из регистров 9 вьфож- дается в триггер, так как 1. На фиг, 6 показан пример конкретной реализации устройства для случая L 2, К 2, Ф(Х) Х + 1. Синхронизационные входы на иг. 6 не показаны. Последовательно

30

35

входов устройства, где N - степень образующего многочлена, соединены с соответствующими входами блоков элементов задержки первого типа,

1)-й синхронизирующий вход

(4-S .

40

устройства соединен с синхровхода- ми блоков элементов задержки второго типа, группа управляющих входов устройства соединена с группой управляющих входов соответствующих блоков элементов задержки второго типа, выходы которых соединены с входами соответствующих блоков умножения.

соединенные триггеры 9 и 9 объединены на фиг. 6 в регистры сдвига. Формула изобретения Устройство для формирования контрольного кода, содержащее блоков умножения, блок сложения и блок деления, где 1 - число ненулевых коэффисоединены с соответствующими группами входов блока сложения, ( С + 1)-я группа входов которого является группой информационных входов устройства, группа выходов блока сложения соединена с группой блока деления, отличающееся тем, что, с целью повьшения быстродействия, в него введены R блоков элементов задержки

входов устройства, где N - степень образующего многочлена, соединены с соответствующими входами блоков элементов задержки первого типа,

1)-й синхронизирующий вход

(4-S .

устройства соединен с синхровхода- ми блоков элементов задержки второго типа, группа управляющих входов устройства соединена с группой управляющих входов соответствующих блоков элементов задержки второго типа, выходы которых соединены с входами соответствующих блоков умножения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля двоичных последовательностей | 1983 |

|

SU1116431A1 |

| Счетчик | 1986 |

|

SU1422403A1 |

| Генератор цифровых последовательностей | 1987 |

|

SU1513449A1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1995 |

|

RU2087030C1 |

| Запоминающее устройство с контролем информации | 1984 |

|

SU1288758A1 |

| Цифровое устройство для воспроизведения функций | 1988 |

|

SU1532945A1 |

| Генератор М-последовательности | 1985 |

|

SU1256162A1 |

| Генератор псевдослучайных последовательностей | 1986 |

|

SU1465885A1 |

| Устройство для деления многочленов | 1986 |

|

SU1483461A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

Изобретение относится к вычислительной технике и может использоваться в системах тестового диагностирования дискретных объектов. Цель изобретения - повышение быстродействия устройства. Устройство содержит блоки 1, 2 элементов задержки, блоки 3 умножения, блок 4 сложения, блок 5 деления, информационные входы 6, входы 7 синхронизации, управляющие входы 8. Устройство формирует последовательность чисел, частота появления которых в несколько раз больше частоты переключения используемых регистров. Положительньш эффект достигается за счет введения блоков элементов задержки. 6 ил. оо СП ю 4 00 со cfjuff.j

CpLff.Z

a.) ft

12

/7

+

/3

7г7/

8

I i I Н

2

qsuaS

3i

L J

i I I г I 1 I I

M I M M

2

5 t

Г т

qsuaS

3i

i I I г I 1 I I

O i/g

Составитель И.Иваньпсин Редактор Ю.Середа Техред М.Ходанич Корректор Н.Король

Заказ 5567/49 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Устройство для контроля двоичных последовательностей | 1983 |

|

SU1116431A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-11-15—Публикация

1986-07-09—Подача