О1

со

4 QD

3151

Изобретение относится к цифровой вычислительной технике и может использоваться в системах тестового иагностирования дискретных объектов.

Цель изобретения - расширение функциональных возможностей генератора за счет формирования последовательностей любой длины М, где 1 М

L

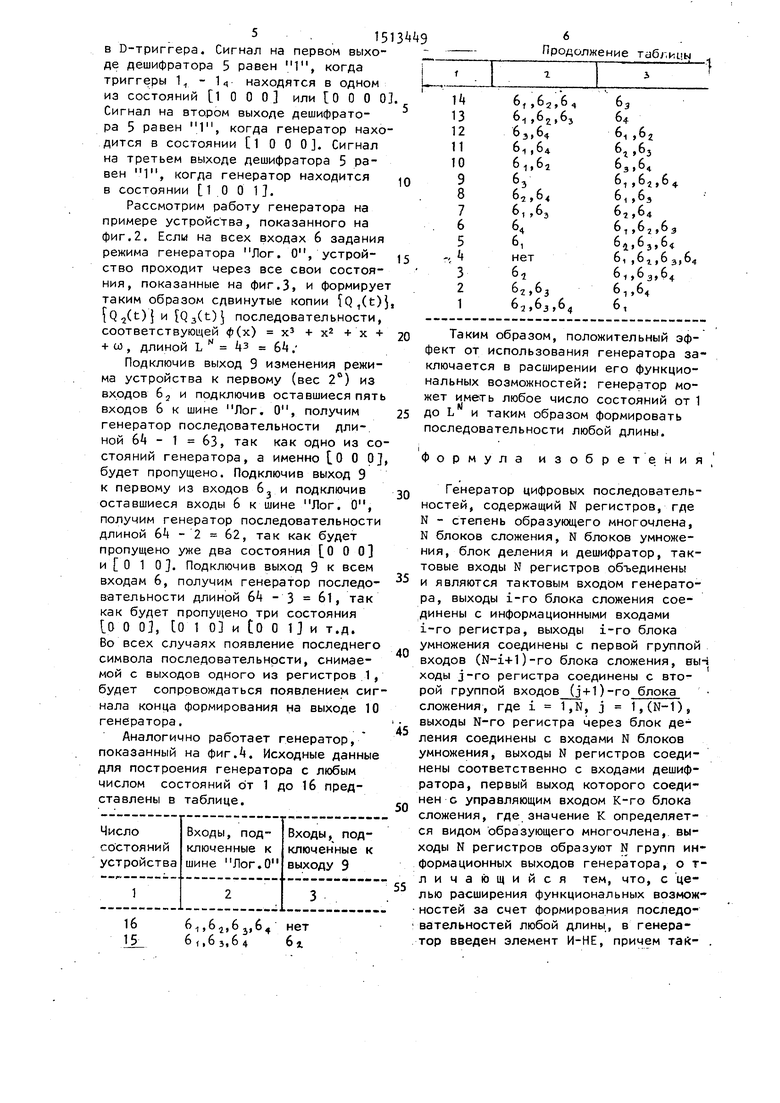

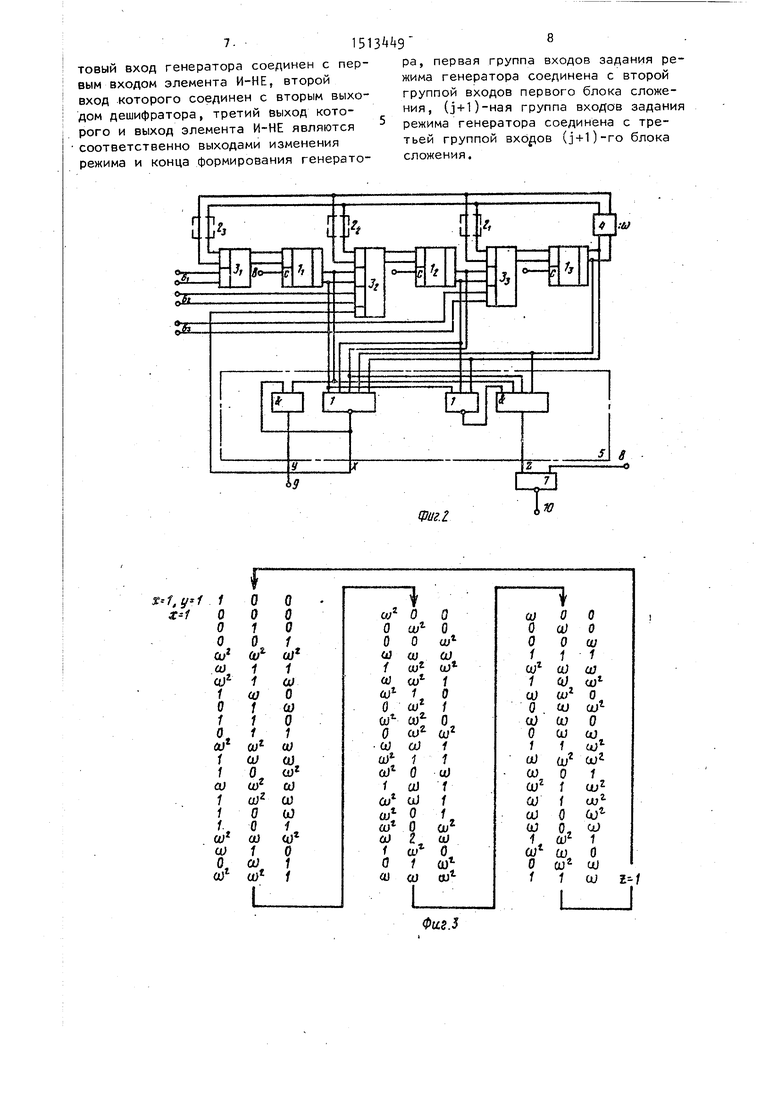

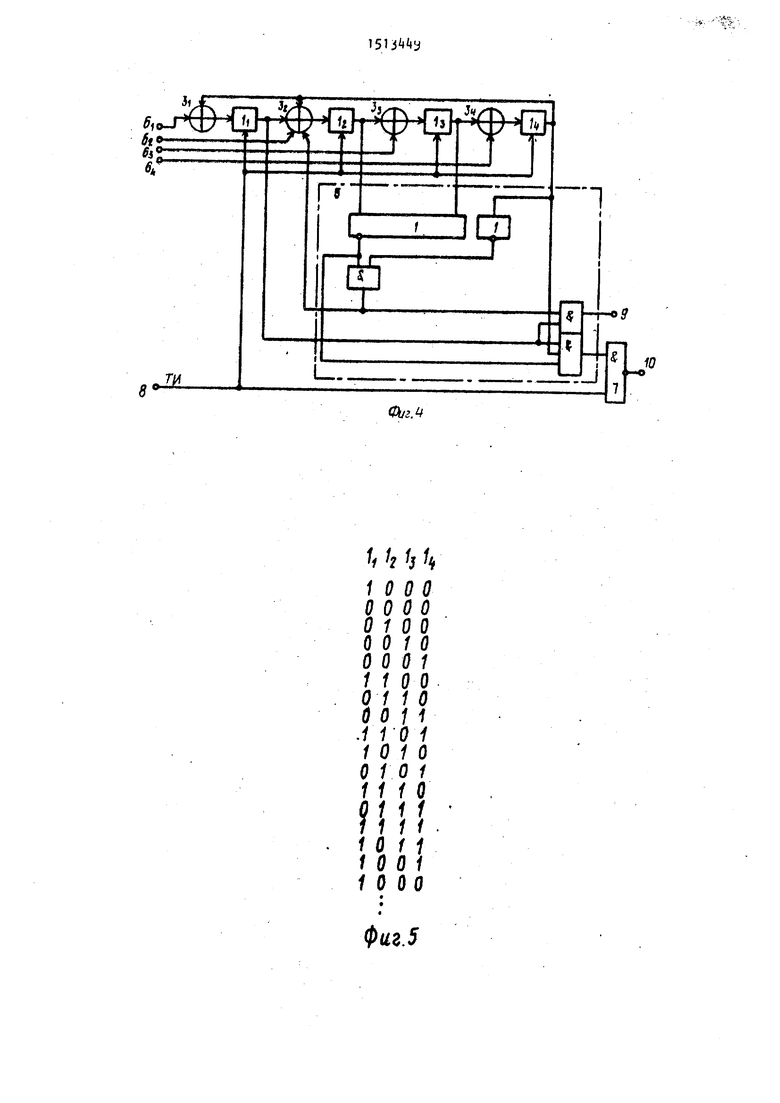

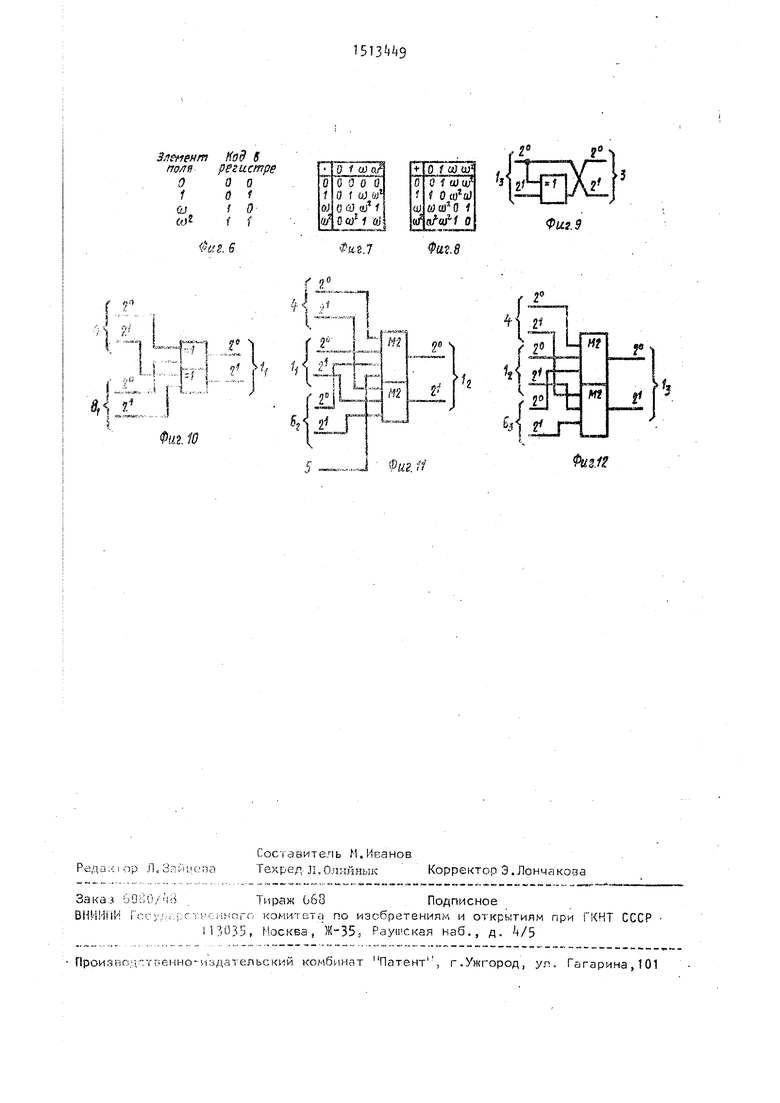

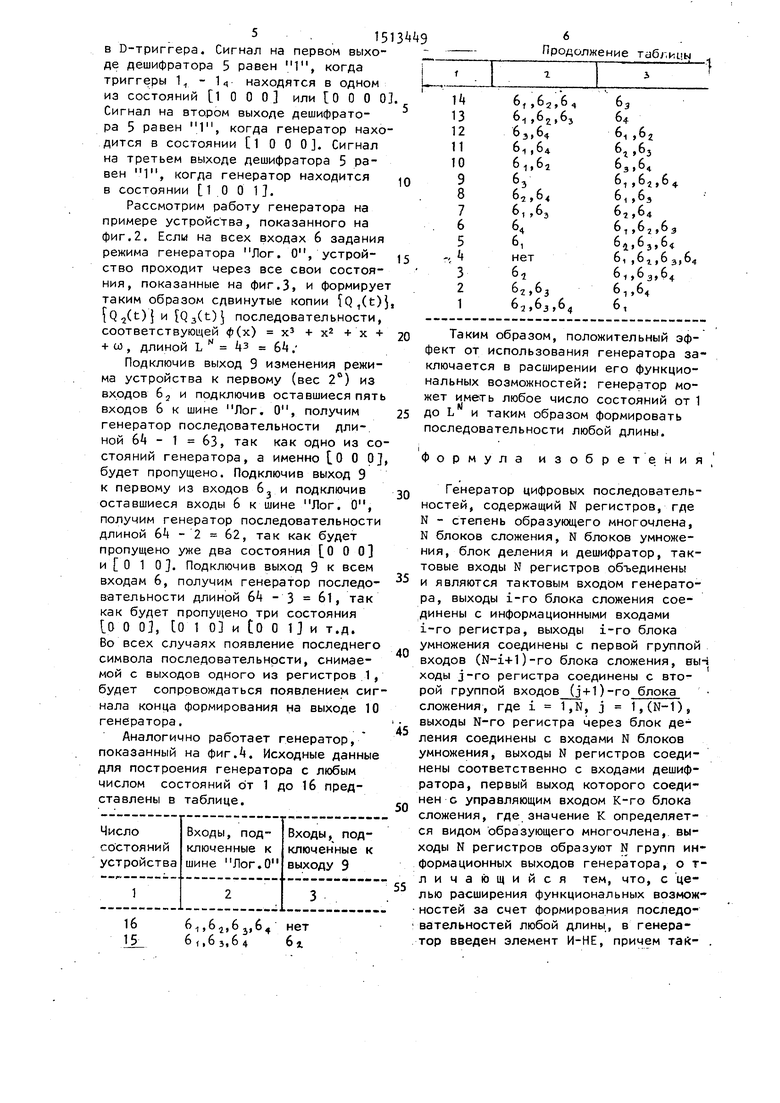

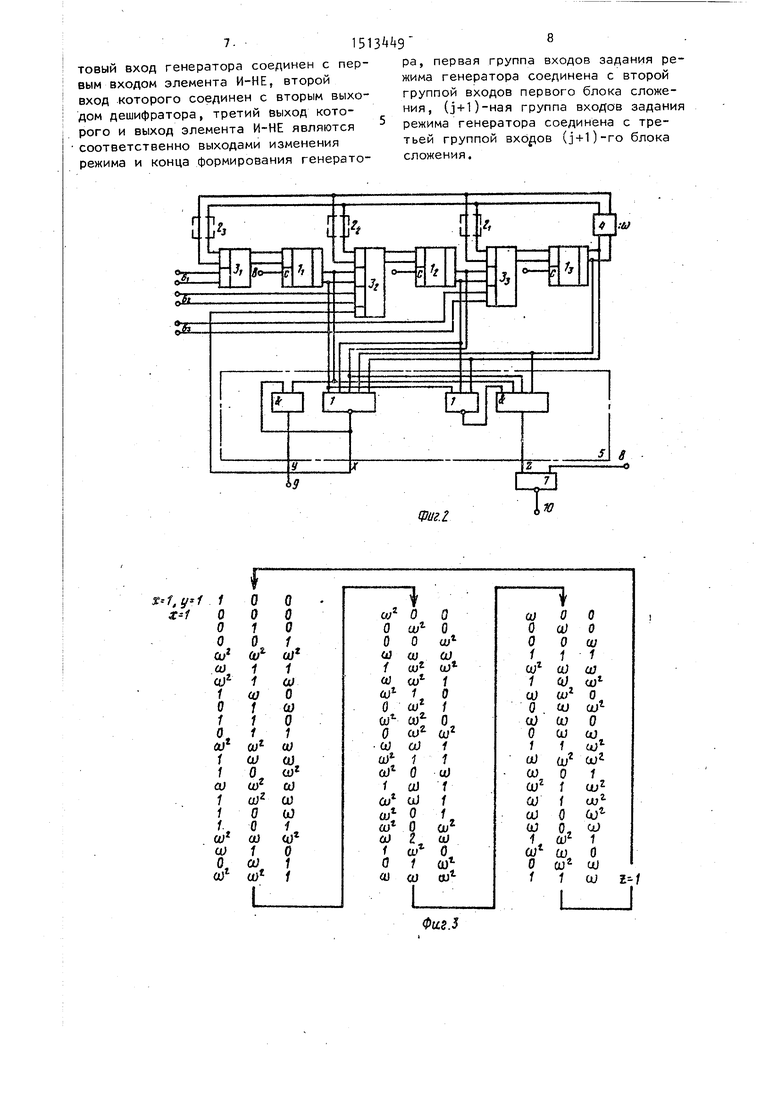

На фиг.1 приведена структурная схема генератора; на фиг,2 - пример конкретной реализации генератора чет- веричных последовательностей при L в 22, N 3| Ф (х) хз + х +х + W ; на фиг.З - последовательность переключения регистров генератора , на фиг. - пример конкретной реализации генератора для случая L 2, N 4, ф(х) 5J + х + 1; на фиг. 5 - последовательные состояния генератора при Лог. О на всех входах; на фиг.6 - соответствие между элементами поля GF (22) и кодом в регистрах генератора; на фиг.7 правила умножения на to (деления на со); на фиг.8 - правила сложения в по- ле GF (22)J на фиг.9 - блок деления на О); на фиг. 10-12 - соответственно блоки сложения генератора.

Генератор цифровых последовательностей (фиг.1) содержит N регистров 1, где N - степень образующего многочлена р(х) а,,х «, ... + а;Х +. + ... + + ад - примитивного над полем Галуа из L элементов, N блоков 2 умножения в поле GF(L), причем величина, на которую происходит умножение в i-M блоке, равна i-му коэффициенту РСх), N блоков 3 сложения в поле GF(L), блок деления в поле GF(L), причем величина, на которую происходит деление, равна а,,, дешифратор 5, входы 6 задания режима и элемент И-НЕ 7, а также входы 8 и 9 и выход 10.

Если все коэффициенты а, отличны от нуля, то номер блока сложения, к упрашлйщему sxofly которого подключается першый шыход дешифратора 5, безразличен, Если же некоторые коэффициенты а; равны нулю, то первый выход дешифратора 5 должен быть обя эательно подключен к одному и§ тех i-x блоков сложения, для которых справедливо а ,jt 0.

Перед началом работы все регистры 1, кроме того, выходы которого соединены с группой входов блока 3

9 4

сложения с управляющим входом, устанавливаются в нулевое состояние. Регистр 1, выходы которого- соединены с группой входов блока 3 сложения с управляющим входом, перед началом работы должен быть установлен в состояние, отличное от нулевого, Это условие является обязательным для нормального функционирования генератора. Далее будем считать, что указанный регистр будет устанавливаться в состояние 1 (код 00,.,001) - на фиг.1 это регистр 1 ,

Регистры 1 выполняют функции элементов задержки на один такт, их разрядность равна R log,Lt (при L 2, R 1). Блоки 2- представляют из себя комбинационные схемы,

которые строятся на основе соответствующих им таблиц истинности. Последние однозначно определяются правилами умножения, сложения и деления в поле GF(L). Если L это - степень

2, указанные блоки легко реализуются на сумматорах по модулю два.

В примере, рассмотренном на фиг,2, блоки 2 осуществляют умножение на 1, что эквивалентно простой передаче

сигналов с входов блоков на выходы без изменения. По указанной причине блоки 2 на фиг.2 показаны пунктирной линией. Блок k осуществляет деление на -ад -и ы (умножение на со), где Чо-. примитивный элемент поля GF(22) 0,1 ,u3,u;2. Разрядность каждого из регистров 1 на фиг.2 равна R 2. Сигнал х на первом выходе дешифратора 5 принимает единичное значение, когда регистры 1 находятся в одном из состояний Q (t) QV4t)(t)(t)l 1 О 0 или (t) (t) X X Q7(t)QT(t)l СО О 0, где

Q;(t) - содержимое i-ro регистра в момент времени t. Сигнал у на втором выходе дешифратора 5 равен 1, когда регистры 1 генератора находятся в состоянии ) 1 О 0, Сигнал г на третьем выходе дешифратора ра

вен 1, когда регистры 1 находятся а состоянии, предшествующем состоя- нию Q, (t), для елучая, раебмотрен- ного на фиг,2 это состояние 1 1w.

S случае, рассмотренном на фиг., все коэффициенты в; равны либо , либо 1, поэтому все блоки 2 и вырождаются. Блоки 3 превращаются в сумматоры по модулю два, регистры 1 5 . 15 в D-триггера. Сигнал на первом выходе дешифратора 5 равен 1, когда триггеры 1 - 1 находятся в одном из состояний 1 000 или 0000 Сигнал на втором выходе дешифратора 5 равен 1, когда генератор находится в состоянии 1 О О 0. Сигнал на третьем выходе дешифратора 5 равен 1, когда генератор находится в состоянии 1 .0 О 1.

Рассмотрим работу генератора на примере устройства, показанного на фиг.2. Если на всех входах 6 задания режима генератора Лог. О, устройство проходит через все свои состояния, показанные на фиг.З, и формирует

таким образом сдвинутые копии tQ,(t)J ,j(t)} и QaCt) последовательности.

соответствующей ф(х) х + х + х + + со , длиной L k 6k .

Подключив выход 9 изменения режи(вес 2°)

ма устройства к первому

из

входов 6, и подключив оставшиеся пять входов 6 к шине Лог. О, получим генератор последовательности дли-, ной 6 - 1 63, так как одно из состояний генератора, а именно О О 0, будет пропущено. Подключив выход 9 к первому из входов 6 и подключив оставшиеся входы 6 к шине Лог. О, получим генератор последовательности длиной 6 - 2 62, так как будет пропущено уже два состояния 000 и о 1 0. Подключив выход 9 к всем входам 6, получим генератор последовательности длиной 64 - 3 б1, так как будет пропуи;ено три состояния О О 03, 01 0 и to О и т.д. Во всех случаях появление последнего символа последовательности, снимаемой с выходов одного из регистров 1, будет сопровождаться появлением сигнала конца формирования на выходе 10 генератора.

Аналогично работает генератор, показанный на фиг.А. Исходные данные для построения генератора с любым числом состояний бт 1 до 1б представлены в таблице.

10

15

20

25

Таким образом, положительный эффект от использования генератора заключается в расширении его функциональных возможностей: генератор может иметь любое число состояний от 1 до L и таким образом формировать последовательности любой длины.

0

5

0

5

0

5

Формула изобретения,

Генератор цифровых последовательностей, содержащий N регистров, где N - степень образующего многочлена, N блоков сложения, N блоков умножения, блок деления и дешифратор, тактовые входы N регистров объединены и являются тактовым входом генератора, выходы i-ro блока сложения соединены с информационными входами i-ro регистра, выходы i-ro блока умножения соединены с первой группой входов (N-i+1)-ro блока сложения, вы- ходы j-ro регистра соединены с второй группой входов(л+1)-го блока сложения, где i 1,N, j 1,(N-1), выходы N-го регистра через блок деления соединены с входами N блоков умножения, выходы N регистров соединены соответственно с входами дешифратора, первый выход которого соединен с управляющим входом К-го блока сложения, где значение К определяется видом образующего многочлена, выходы N регистров образуют N групп информационных выходов генератора, о т- личайэщийся тем, что, с целью расширения функциональных возмож- ностей за счет формирования последо- вательностей любой длины, в генератор введен элемент И-НЕ, причем тай- .

товый вход генератора соединен с первым входом элемента И-НЕ, второй вход .которого соединен с вторым выходом дешифратора, третий выход кото- I рого и выход элемента И-НЕ являются соответственно выходами изменения режима и конца формирования генератора, первая группа входов задания режима генератора соединена с второй группой входов первого блока сложения, (з+1)-ная группа входов задания режима генератора соединена с третьей группой (j + l)-ro блока сложения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетчик | 1986 |

|

SU1422403A1 |

| Генератор тестовых последовательностей | 1986 |

|

SU1388999A1 |

| Генератор псевдослучайных последовательностей | 1986 |

|

SU1465885A1 |

| Генератор L-ичных последовательностей | 1986 |

|

SU1406586A1 |

| Счетчик | 1985 |

|

SU1298900A1 |

| Генератор псевдослучайных последовательностей | 1984 |

|

SU1251303A1 |

| Генератор М-последовательности | 1986 |

|

SU1411724A1 |

| Генератор М-последовательности | 1985 |

|

SU1256162A1 |

| Устройство для деления многочленов | 1986 |

|

SU1483461A1 |

| Запоминающее устройство с контролем информации | 1984 |

|

SU1288758A1 |

Изобретение относится к цифровой вычислительной технике и может использоваться для генерации тестовых воздействий при контроле дискретных объектов, для построения синхронных счетчиков и делителей частоты. Цель изобретения - расширение функциональных возможностей генератора за счет формирования последовательностей любой длины. Генератор цифровых последовательностей содержит N регистров 1, N блоков 2 умножения, N блоков 3 сложения, блок 4 деления, дешифратор 5 и элемент И-НЕ 7, где N - степень образующего многочлена. Подключая выход изменения режима генератора к соответствующим входам задания режима, оставшиеся из которых подключаются к шине лог. "О", можно изменять число состояний последовательных элементов генератора, что приводит к желаемому изменению длины формируемой последовательности. 12 ил., 1 табл.

1риг2

ю

10

Г, /, fj /4

1000 0000 0100 0010 0001 1100 01 1 о

и о 11 .1 1 о i

1010 0101 1110 0111

1111 nil

1001 1000

фиг.5

НоВ S froff регистре

0О а

1о

OJf о

м f f

Фиг. 6

Фа2.10

5 -.™„ J Фиг //

Фиг. 9

Фа ,. 8

JL tt

25

м

f

i

И 1

4:

M.fj

w

Puti2

| Устройство для контроля двоичных последовательностей | 1983 |

|

SU1116431A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Иваной М.А., Кларин А.П | |||

| Генераторы псевдослучайных последовательностей.- М.: Изд-во МИФИ, 1987, с | |||

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

Авторы

Даты

1989-10-07—Публикация

1987-07-24—Подача