катор 10. Сигнатурный анализатор 4 содержит блок 14 деления по модулю с , N блоков 15 умножения по модулю „L i К блоков 16 сложения по моду1288758

лю пр GF ра

1

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам (ЗУ) с контролем правильности хранения информации, и может быть использовано для построения буферных ЗУ или устройств отображения информации.

Цель изобретения - расширение функциональных возможностей за счет обеспечения контроля ЗУ при его работе в реальном масштабе времени.

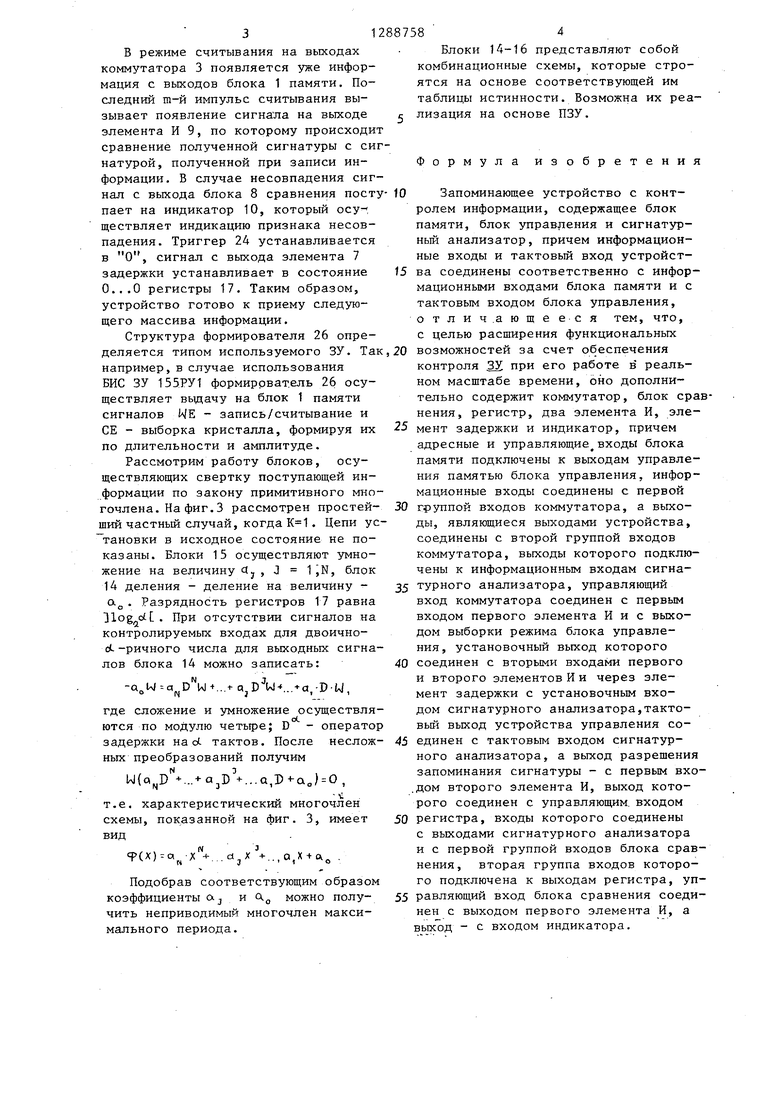

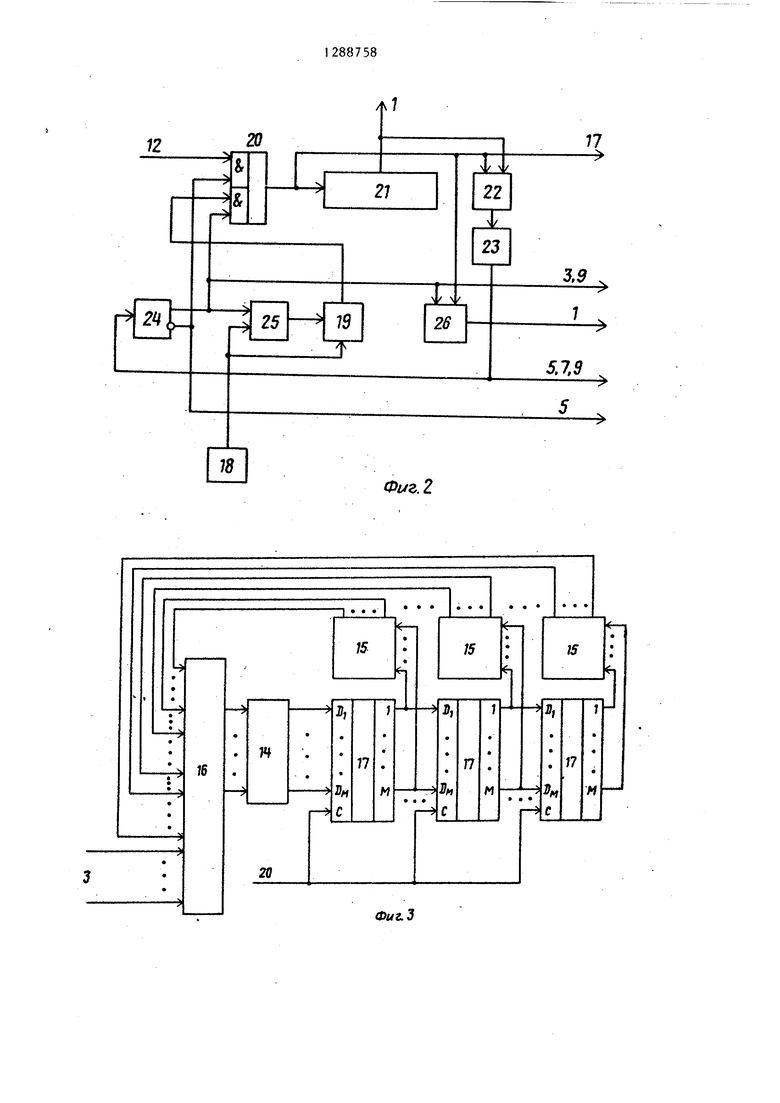

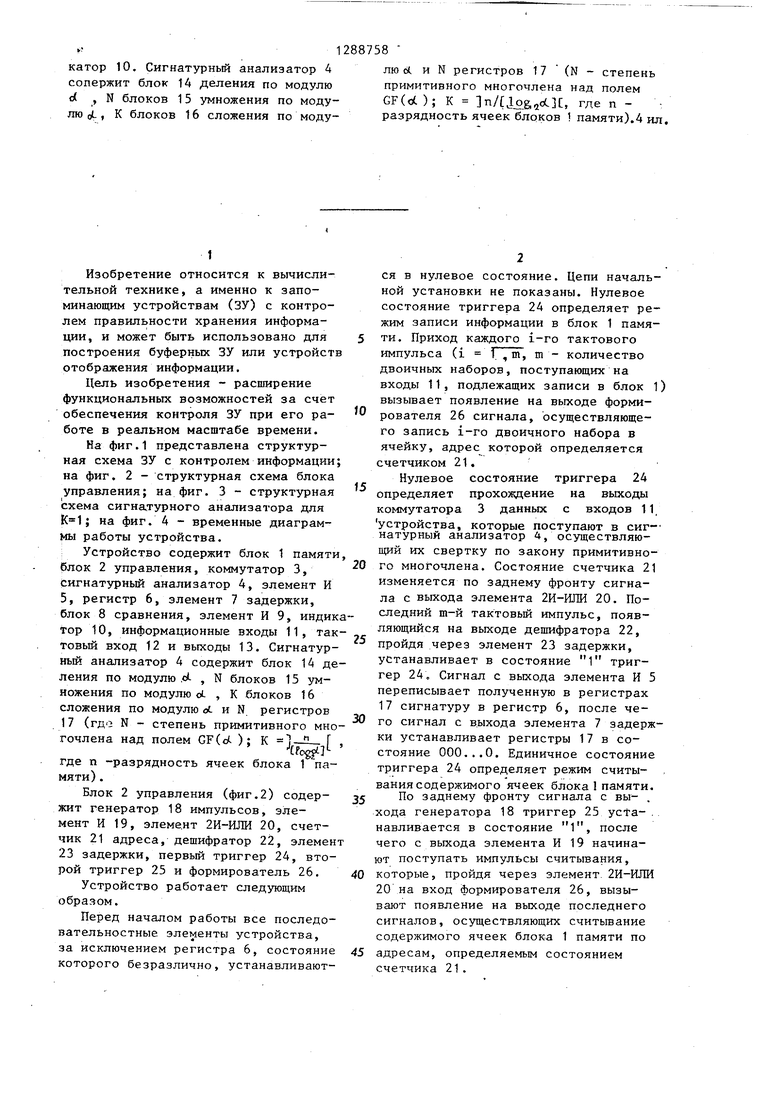

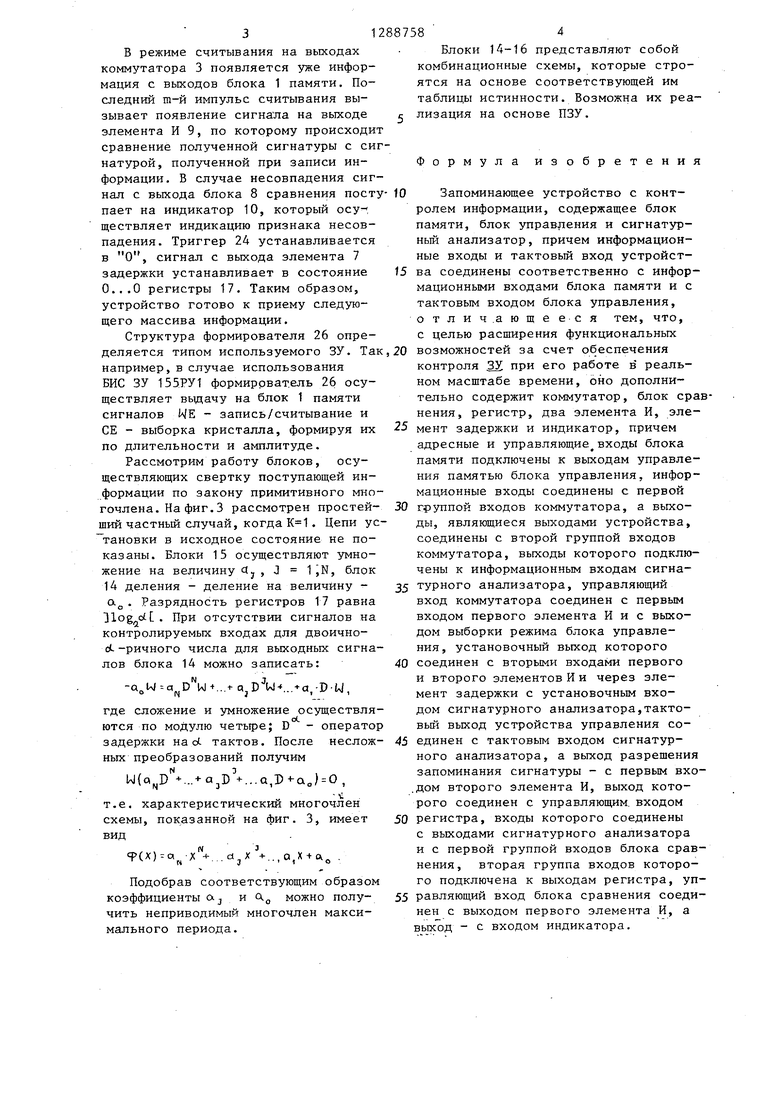

На фиг.1 представлена структурная схема ЗУ с контролем информации; на фиг. 2 - структурная схема блока управления; на фиг. 3 - структурная схема сигнатурного анализатора для на фиг. 4 - временные диаграммы работы устройства.

Устройство содержит блок 1 памяти блок 2 управления, коммутатор 3, сигнатурный анализатор 4, элемент И 5, регистр 6, элемент 7 задержки, блок 8 сравнения, элемент И 9, индиктор 10, информационные входы 11, тактовый вход 12 и выходы 13. Сигнатурный анализатор 4 содержит блок 14 деления по модулю . , N блоков 15 умножения по модулю oL , к блоков 16 сложения по модулю ot и N регистров 17 (гд 2 N - степень примитивного многочлена над полем GF(dt. ); К -... Г

Cfogfi

где п -разрядность ячеек блока 1 памяти) .

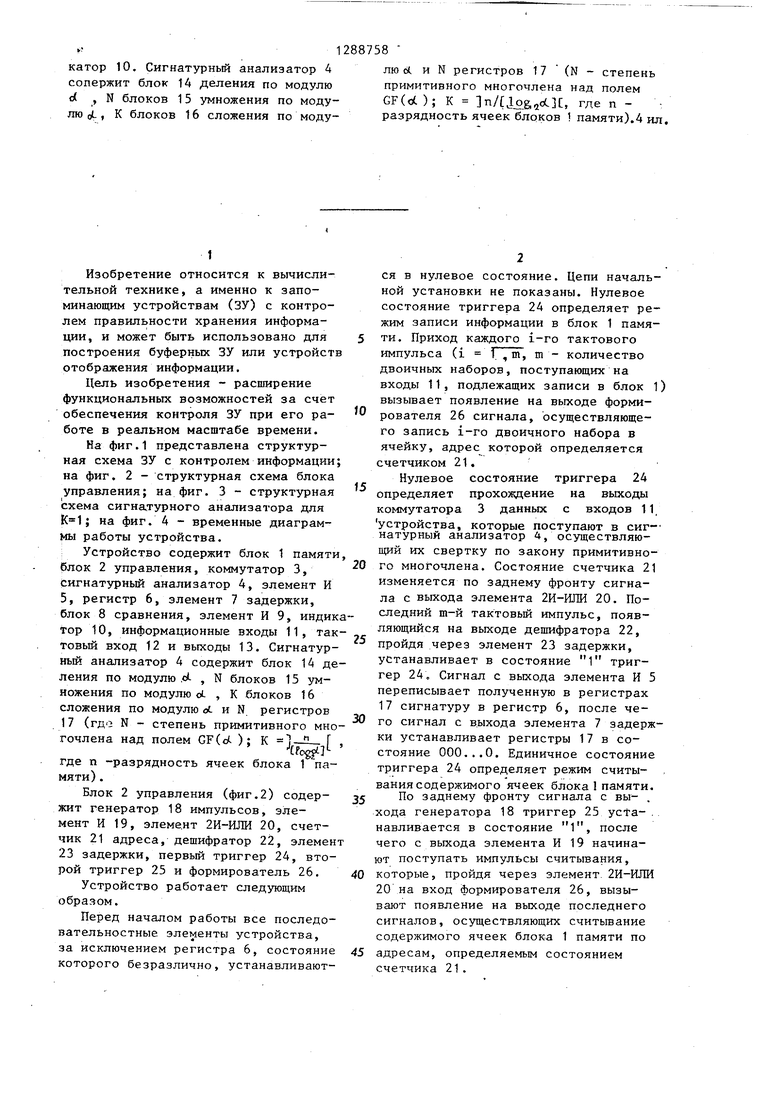

Блок 2 управления (фиг.2) содержит генератор 18 импульсов, элемент И 19, элемент 2И-ИЛИ 20, счетчик 21 адреса, дешифратор 22, элемен 23 задержки, первый триггер 24, второй триггер 25 и формирователь 26,

Устройство работает следующим образом.

Перед началом работы все последо- вательностные элементы устройства, за исключением регистра 6, состояние которого безразлично, устанавливаютлю б(. и N регистров 17 (N - степень примитивного многочлена над полем GF(oC ); К ,oL, гле п - разрядность ячеек блоков 1 памяти).4 ил.

5

0

5

0

5

0

5

ся в нулевое состояние. Цепи начальной установки не показаны. Нулевое состояние триггера 24 определяет режим записи информации в блок 1 памяти. Приход каждого i-ro тактового импульса (i 1 , m, m - количество двоичных наборов, поступающих на входы 11, подлежащих записи в блок 1) вызывает появление на выходе формирователя 26 сигнала, осуществляющего запись i-ro двоичного набора в ячейку, адрес которой определяется счетчиком 21.

Нулевое состояние триггера 24 определяет прохолдение на выходы коммутатора 3 данных с входов 11,

устройства, которые поступают в сиг- натурный анализатор 4, осуществляющий их свертку по закону примитивного многочлена. Состояние счетчика 21 изменяется по заднему фронту сигнала с выхода элемента 2И-ИЛИ 20. Последний т-й тактовый импульс, появляющийся на выходе дещифратора 22, пройдя через элемент 23 задержки, устанавливает в состояние 1 триггер 24. Сигнал с выхода элемента И 5 переписывает полученную в регистрах 17 сигнатуру в регистр 6, после чего сигнал с выхода элемента 7 задержки устанавливает регистры 17 в состояние 000...О. Единичное состояние триггера 24 определяет режим считывания содержимого ячеек блока 1 памяти. По заднему фронту сигнала с вы ,

хода генератора 18 триггер 25 усТа- . навливается в состояние 1, после чего с выхода элемента И 19 начинают поступать импульсы считывания, которые, пройдя через элемент. 2И-ИЛИ 20 на вход формирователя 26, вызывают появление на выходе последнего сигналов, осуществляющих считьшание содержимого ячеек блока 1 памяти по адресам, определяемым состоянием счетчика 21.

В режиме считывания на выходах коммутатора 3 появляется уже информация с выходов блока 1 памяти. Последний т-й импульс считывания вызывает появление сигнала на выходе элемента И 9, по которому происходит сравнение полученной сигнатуры с сигнатурой, полученной при записи информации, В случае несовпадения сигнал с выхода блока 8 сравнения поступает на индикатор 10, который осуп ществляет индикацию признака несовпадения. Триггер 24 устанавливается в О, сигнал с выхода элемента 7 задержки устанавливает в состояние 0...0 регистры 17. Таким образом, устройство готово к приему следующего массива информации.

Структура формирователя 26 определяется типом используемого ЗУ. Так,20 возможностей за счет обеспечения

например, в случае использования БИС ЗУ 155РУ1 формиррватель 26 осуществляет выдачу на блок 1 памяти сигналов WE - запись/считывание и СЕ - выборка кристалла, формируя их по длительности и амплитуде.

Рассмотрим работу блоков, осуществляющих свертку поступающей информации по закону примитивного многочлена. На фиг. 3 рассмотрен простейший частный случай, когда . Цепи установки в исходное состояние не показаны. Блоки 15 осуществляют умножение на величину с( , j 1 JN, блок 14 деления - деление на величину а. Разрядность регистров 17 равна Hog ot . При отсутствии сигналов на контролируемых входах для двоичнос --ричного числа для выходных сигналов блока 14 можно записать:

...t- .

а.

-P-W,

где сложение и умножение осуществляются по модулю четьфе; D - оператор задержки наЫ тактов. После неслож- ных преобразований получим

...4-a.|D -t-.-.Q,) -&„) О ,

т.е. характеристический многочлен схемы, показанной на фиг. 3, имеет вид

м

Т(Х)-а ;( V.

Q,X + a

Подобрав соответствующим образом коэффициенты а-, и Q.(, можно получить неприводимый многочлен макси- Мсшьного периода.

Блоки 14-16 представляют собой комбинационные схемы, которые строятся на основе соответствующей им таблицы истинности. Возможна их реализация на основе ПЗУ.

Формула изобретения

Запоминающее устройство с контролем информации, содержащее блок памяти, блок управления и сигнатурный анализатор, причем информационные входы и тактовьм вход устройства соединены соответственно с информационными входами блока памяти и с тактовым входом блока управления, отлич.ающееся тем, что, с целью расширения функциональных

5

0

5

контроля ЗУ. при его работе в реальном масштабе времени, оно дополнительно содержит коммутатор, блок сравнения, регистр, два элемента И, элемент задержки и индикатор, причем адресные и управляющие входы блока памяти подключены к выходам управления памятью блока управления, информационные входы соединены с первой группой входов коммутатора, а выходы, являющиеся выходами устройства, соединены с второй группой входов коммутатора, выходы которого подключены к информационным входам сигна5 турного анализатора, управляющий вход коммутатора соединен с первым входом первого элемента И и с выходом выборки режима блока управления , установочный выход которого соединен с вторыми входами первого и второго элементов И и через элемент задержки с установочным входом сигнатурного анализатора,тактовый выход устройства управления соединен с тактовым входом сигнатурного анализатора, а выход разрешения запоминания сигнатуры - с первым входом второго элемента И, выход которого соединен с управляющим, входом регистра, входы которого соединены с выходами сигнатурного анализатора и с первой группой входов блока сравнения, вторая группа входов которого подключена к выходам регистра, уп5 равляющий вход блока сравнения соединен с выходом первого элемента И, а вьтхЪд - с входом индикатора.

0

0

« S «

CM CM еч

I I I I I I

nj §

S

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1998 |

|

RU2133057C1 |

| Многовходовой сигнатурный анализатор | 1987 |

|

SU1478219A1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1995 |

|

RU2087030C1 |

| Устройство для диагностирования цифровых объектов | 1989 |

|

SU1705829A1 |

| Сигнатурный анализатор | 1983 |

|

SU1223230A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1185338A1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1996 |

|

RU2120136C1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1254489A1 |

Изобретение относится к области вычислительной техники, может быть использовано для построения буферных запоминающих устоойств (ЗУ) или устройств отображения информации и обеспечивает расширение функциональных возможностей за счет обеспечения контроля ЗУ при его работе в реальном масштабе времени. Устройство содержит блок 1 памяти, блок 2 управления, коммутатор 3 сигнатурный анализатор 4, элемент И 5, регистр 6, элемент 7 задержки, блок 8 сравнения, элемент И 9, инди- g ю 00 00 -vj ел оо фиг}

Редактор В. Петраш

Составитель С. Сушко

Техред В.Кадар Корректор А. Тяско

Заказ 7813/50Тираж 611Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Иванов М.А., Кларин А.П., Тышкевич В.Г | |||

| Методика оперативного анализа информации искровых камер гамма-телескопа | |||

| - Методологические аспекты применения ЭВМ в ядерной физике и технике | |||

| - М.: Атомиздат, 1981, с | |||

| Пишущая машина | 1922 |

|

SU37A1 |

| Устройство для контроля полупроводниковой памяти | 1982 |

|

SU1032481A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| да | |||

Авторы

Даты

1987-02-07—Публикация

1984-01-23—Подача