- конечные разности 1-го порядка ,

И{ - 1-е коэффициенты. Вычисление значения интеграла от воспроизводимой функции производится по формуле

к

j f(x)dx - j f(x)dx + f(x)dx;(2),

ё. «

X-X

2

f(xK)+f(Xi (3)

f(x)di

XK

Таким образом общий принцип работу устройства сводится к следующему:

1.Выбирается опорный узел интер- п{эляции.

2.Производится вычисление значе- ния воспроизводимой функции, для чего

- по значению Х-ХК и адресу опор

ного узла интерполяции выбирают из памяти все величины, входящие в формулу (1)}

-перемножают коэффициенты слагаемых интерполяционного многочлена на соответствующие конечные разности по формуле (1);

-вычисляют значение воспроизводимой функции сложением членов интерполяционного многочлена по формуле (1).

3. Производится вычисление значения интеграла от воспроизводимой функции, для чего

-по значению адреса, соответствующего номеру опорного узла интерполяции, выбирают из памяти значение первой составляющей, входящей в формулу (2);

-вычисляют значение второй составляющей, входящей в формулу (2);

-производят сложение обеих составляющих формулы (2).

Устройство работает следующим образом.

С входа 1 аргумента заданное зна- чение аргумента поступает на вход регистра 7 аргумента и фиксируется в момент прихода импульса с входа 2 запуска. Импульс с входа 2 запуска одновременно поступает на вход счетчика 6, обнуляя его, на первый вход накапливающего сумматора 11, устанавливая его в исходное состояние (на выходе первого накапливающего сумматора появляется значение аргумента а последнем узле интерполяции Xft), на первый вход накапливающего сумматора 12, устанавливая его в исходное

5

5

0

5

5

0

0

5

состояние, на выходе второго накапливающего сумматора появляется значение функции в последнем узле интерполяции f(X).

Далее производится поиск опорного узла интерполяции.

На первый вход элемента И А поступают импульсы с тактового входа 3. Заданное значение аргумента с выхода регистра 7 аргумента поступает на вход схемы 8 сравнения; на вход сумматора 10.

В блоке 27 задания шага устанавливается необходимое значение шага интерполяции h, которое поступает на вход накапливающего сумматора И и на вход схемы 9 сравнения.

Значение аргумента в узлах интерполяции с выхода накапливающего сумматора 11 поступает на вход схемы 8 сравнения и на вход сумматора 10.

Сумматор 10 вычисляет разность между заданным значением аргумента и значением аргумента в текущем узле интерполяции.

Схема 8 сравнения работает следующим образом.

Если заданное значение аргумента больше или равно значению аргумента текущего узла интерполяции, т.е. Х ХК на выходе формируется сигнал запрещения (1), при Х Хц - формируется сигнал разрешения (О).

Схема 9 сравнения работает следующим образом.

Если значение шага интерполяции больше или равно разности между за- данным значением аргумента и значением аргумента в текущем узле интерпо- , (ляции, которая поступает с выхода сумматора 10, т.е. , на выходе формируется сигнал запрещения (1), при - сигнал разрешения (О).

Выходы схем 8 и 9 сравнения соединены соответственно с первым и вторым входами элемента И-НЕ 5, который запрещает прохождение тактовых импульсов через элемент И Ц в случае появления на обоих входах сигналов запрещения (,так как выход элемента И-НЕ 5 соединен с вторым входом элемента И k.

Поиск опорного узла осуществляется следующим образом.

При приходе импульса запроса схема 8 сравнения сравнивает заданное значение аргумента X со значением аргумента в последнем узле интерполяции Хп,. так как Х« ЈХП, на ее выходе по5

является сигнал разрешения. Схема 9 сравнения сравнивает значение шага интерполяции h со значением Х-Х на выходе сумматора 10, так как h Х-ХК, на ее выходе появляется сигнал разрешения. Элемент И-НЕ 5 формирует сигнал разрешения на втором входе элемента И J. Таким образом импульсы пропускаются с тактового входа 3 через элемент И k.

Счетчик 6 формирует адрес следующего узла интерполяции.

Накапливающий сумматор 11 осуществляет вычитание шага интерполяции из значения аргумента предыдущего узла интерполяции. Накапливающий сумматор 12 вычитает конечную разность первого порядка, поступающую с выхода первого блока 13 памяти, выбранную по адресу, сформированному счетчиком 6, из значения функции в предыдущем узле интерполяции. Процесс повторяется до тех пор, пока на выходах обеих схем 8 и 9 сравнения не сформируется CHI- нал запрещения, т.е. не будут выполнены условия и . В этом случае на выходе элемента И-НЕ 5 формируется сигнал запрещения (О), который, поступая на второй вход элемента И +, запрещает прохождение импульсов с тактового входа 3. Процесс нахождения опорного узла завершен. При этом на выходе счетчика 6 присутствует адрес, соответствующий номеру опорного узла интерполяции, на выходе накапливающего сумматора 11 присутствует значение аргумента в опорном узле интерполяции, на выходе накапливающего сумматора 12 - значение функции в опорном узле интерполяции , на выходе сумматора 10 - разность между заданным значением аргумента и значением аргумента в опорном узле интерполяции Х-ХК.

При приходе сигнала запрещения (О) на вход элемента 22 задержки с выхода элемента И-НЕ 5 она формирует на выходе 28 готовности результата сигнал разрешения с временной задержкой, достаточной для вычисления значения воспроизводимой функции и значения интервала Jf(x)dx. Далее

«0

производится вычисление значения воспроизводимой функции. По адресу, соответствующему номеру опорного узла интерполяции, из блока памяти 13 выбираются значения конечных разнос15

тей вплоть до пятого порядка,,которые передаются с первого, второго, третьего, четвертого и пятого выходов бло- . ка памяти 13 на входы соответствующих блоков 15-19 умножения.

По значению разности Х-ХК, поступающий на вход блока И памяти, выбираются значения коэффициентов слагае- Ю мых интерполяционного многочлена, которые передаются схвыходов второго блока И памяти на входы соответствующих блоков умножения. Блоки умножения перемножают коэффици- 15 енты слагаемых интерполяционного многочлена на соответствующие конечные разности и передают их с выходов на входы сумматора 20.

Значение функции в опорном узле 20 интерполяции поступает на вход сумматора 20 с выхода накапливающего сумматора 12. Сумматор 20 вычисляет значения воспроизводимой функции суммированием членов интерполяционного 25 многочлена по формуле {1).

Значение воспроизводимой функции с выхода сумматора 20 поступает на выход 23 значения функции.

Далее производится вычисление зна- 30 чения интеграла от воспроизводимой функции.

По адресу, соответствующему номеру опорного узла интерполяции, из блока 13 памяти выбирается значение

35

f(x)dx, которое передается на вход

сумматора 25. Сумматор 21 вычисляет f(XK) + f(X), причем f(XK) поступает

на его вход с выхода накапливающего сумматора 12, a f(X) - с выхода сумматора 20, и передает это значение на вход блока умножения. Значение Х-ХК поступает с выхода сумматора 10

на вход блока 2 умножения, операция деления на два осуществляется разовым сдвигом вправо значения Х-Х,, , который осуществляется соответствующей коммутацией.

Блок 2k умножения вычисляет значение второй составляющей формулы (2) . по формуле (3) и выдает это значение на вход сумматора 25, который осуществляет сложение обоих составляющих формулы (2) и выдает это значение на выход 26 значения интеграла.

При появлении сигнала разрешения на выходе готовности результата 28 внешнее устройство считывает данные

с выхода 23 функции и выхода 26 знамения интеграла. Формула изобретения

Цифровое устройство для воспроиз- ведения функций, содержащее регистр аргумента, счетчик, элемент И, первую схему сравнения, блок памяти конечных разностей, первый накапливающий сумматор, первый блок умножения и первый комбинационный сумматор, причем тактовый вход устройства соединен с первым входом элемента И, ,выход которого соединен со счетным входом счетчика, вход аргумента уст- ройства соединен с информационным входом регистра аргумента, выход которого соединен с первым входом пер- | вой схемы сравнения, выходы первого i блока умножения и первого накапливаю J щего сумматора соединены соответственно с входами первого и второго слагаемых первого комбинационного сумматора, отличающееся тем, что, с целью повышения точности в него введены блок задания шага, второй накапливающий сумматор, с второго по четвертый комбинационные сумматоры, вторая.схема сравнения, элемент И-НЕ, элемент задержки, блок памяти коэффициентов, с второго по шестой блоки умножения, причем выход элемента И соединен с тактовыми входами первого и второго накапливающих сумматоров, входы установки которых соединены с входом запуска устройства, входом разрешения записи регистра аргумента и входом установки в О счетчика, выход которого соединен с адресным входом блока памяти конеч ных разностей, выходы с первого по пятый значений конечных разностей и выход значения интеграла которого соединены соответственно с входами множимого с первого по пятый блоков умножения и входом первого слагаемог второго комбинационного сумматора,

выход которого соединен с выходом значения интеграла устройства, первый выход значения конечной разности блока памяти конечных разностей соединен с информационным входом первого накапливающего сумматора, выход которого соединен с входом первого слагаемого третьего комбинационного сумматора, вход второго слагаемого которого соединен с выходом первого комбинационного сумматора и выходом функции устройства, выход блока задания шага соединен с первым входом второй схемы сравнения и информационным входом второго накапливающего сумматора, выход которого соединен с вторым входом первой схемы сравнения и входом первого слагаемого четвертого комбинационного сумматора, вход второго слагаемого которого соединен с выходом регистра аргумента, выход четвертого комбинационного сумматора соединен с вторым входом второй схемы сравнения, входом множителя шестого блока умножения и адресным входом блока памяти коэффициентов, выходы с первого по пятый коэффициентов которого соединены с входами множителя соответственно с первого по пятый блоков умножения, выходы блоков умножения с второго по пятый соединены с входами соответственно с третьего по шестой слагаемых первого комбинационного сумматора, выход третьего комбинационного сумматора соединен с входом множимого шестого блока умножения, выход которого соединен с входом второго слагаемого второго комбинационного сумматора, выходы первой и второй схем сравнения соединены с соответствующими входами элемента И-НЕ, выход которого соединен с вторым входом элемента И и входом элемента задержки, выход которого соединен с выходом готовности устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой генератор функций | 1988 |

|

SU1541581A1 |

| Цифровое устройство для воспроизведения функций | 1989 |

|

SU1635168A1 |

| Устройство для воспроизведения функций | 1981 |

|

SU991435A1 |

| Цифровое устройство для вычисления синусно-косинусных зависимостей | 1983 |

|

SU1104510A1 |

| Устройство для воспроизведения функций | 1987 |

|

SU1458876A1 |

| Интерполятор третьей степени | 1988 |

|

SU1566369A1 |

| Функциональный преобразователь | 1979 |

|

SU769548A1 |

| Функциональный преобразователь | 1984 |

|

SU1171774A1 |

| Линейный интерполятор | 1986 |

|

SU1413603A1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

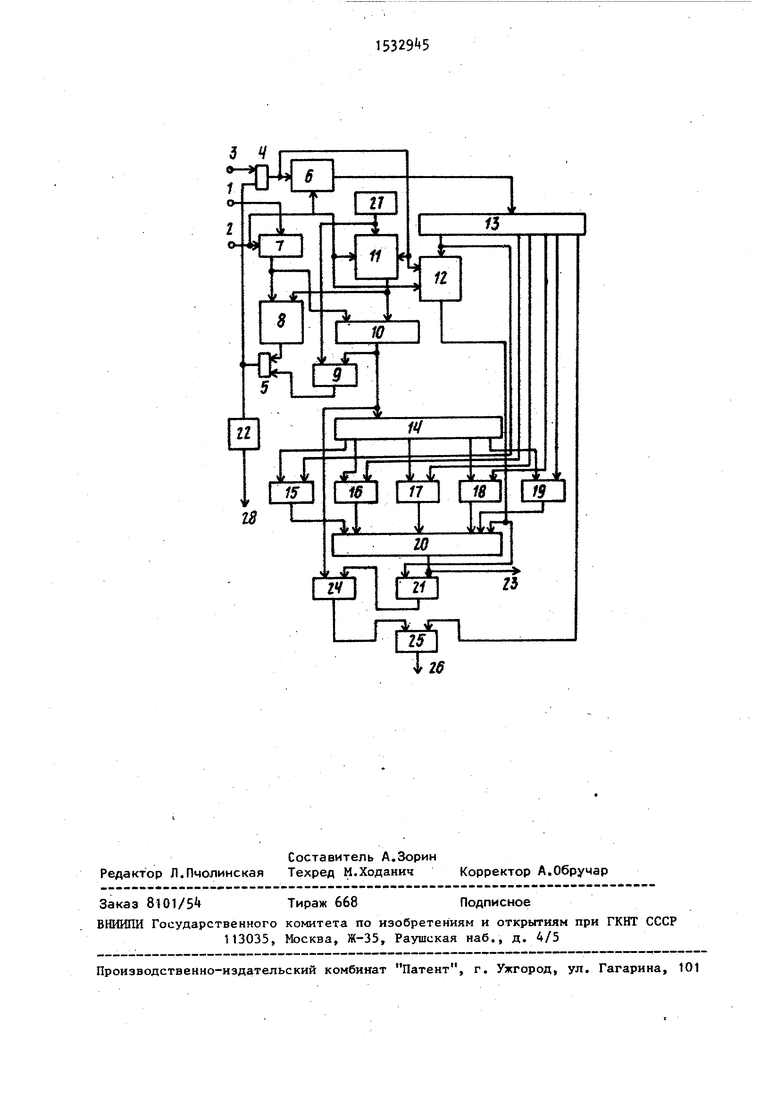

Изобретение относится к автоматике и вычислительной технике. Целью изобретения является увеличение точности. Устройство содержит элементы И и И-НЕ, счетчик, регистр аргумента, две схемы сравнения, два накапливающих сумматора, два блока памяти, элемент задержки, шесть блоков умножения, четыре комбинационных сумматора и блок задания шага. Цель достигается за счет вычисления значения функции методом конечных разностей до пятого порядка. Кроме того, устройство позволяет получить значение интеграла функции. 1 ил.

| Крайзмер Л.П | |||

| Устройства хранения дискретной информации | |||

| Энергия, 1969, с | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой генератор функций | 1980 |

|

SU894692A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ( ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ВОСПРОИЗВЕДЕНИЯ ФУНКЦИЙ Изобретение относится к автоматике и вычислительной технике и может быть использовано в специальных вычислительных устройствах для воспроизведения функциональных зависимостей, а также в измерительных системах для функционального преобразования информации | |||

| Цель изобретения - повышение точности | |||

| На чертеже представлена блок-схема устройства | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-12-30—Публикация

1988-05-03—Подача