Изобретение относится к вычислительной технике и электросвязи и может быть использовано при построении цифровых систем связи,

Целью изобретения является повьпне- ние эффективности подавления шумов свободного канала.

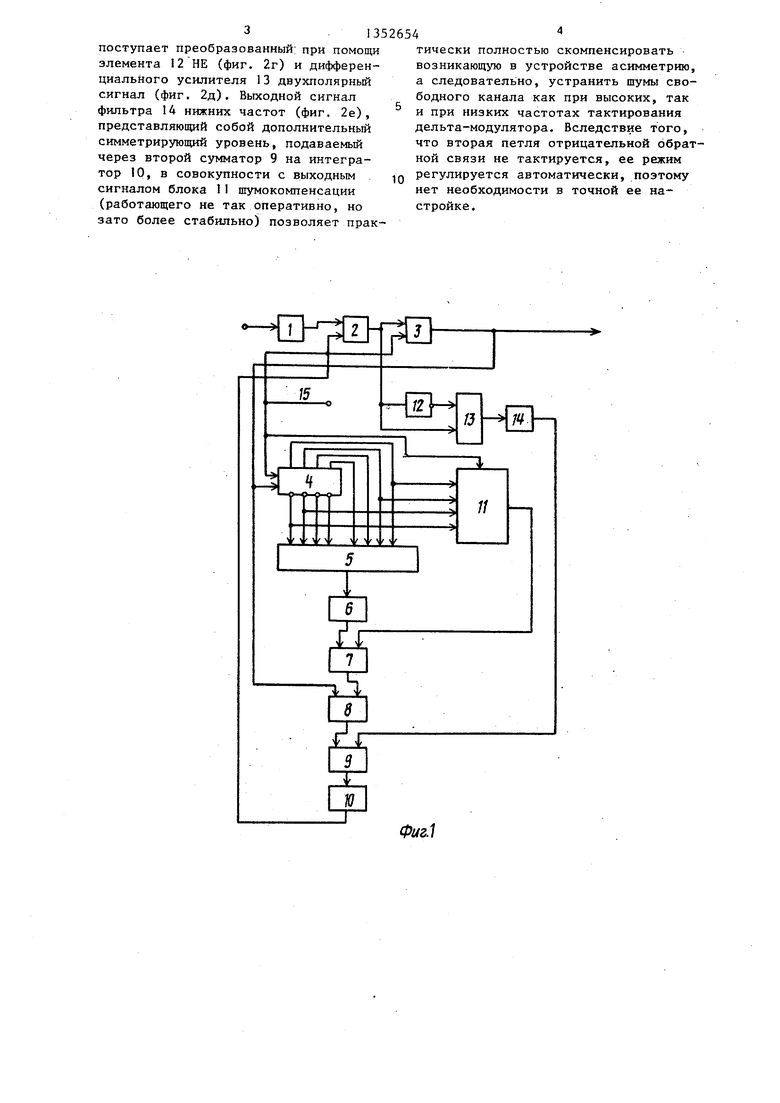

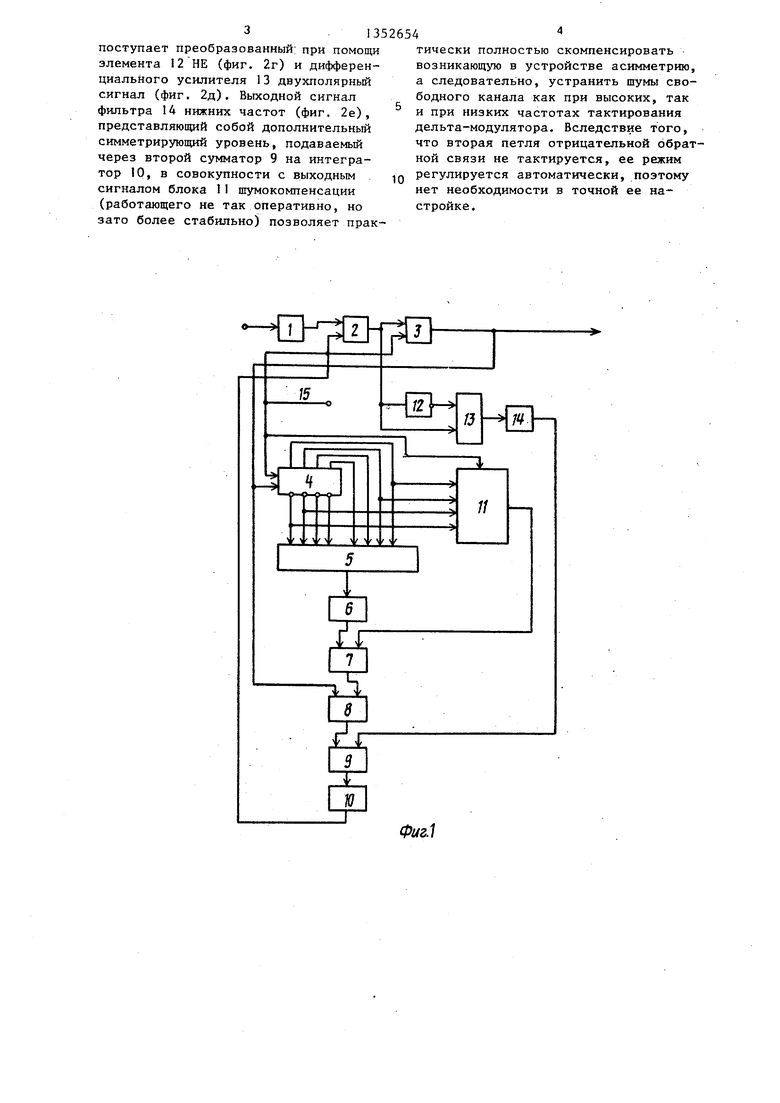

На фиг. 1 приведена структурная схема дельта-модулятора; на фиг.2 - временные диаграммы, поясняющие его работу.

На фиг. 1 входной фильтр 1 соединен с первым входом компаратора 2, выход которого подключен к информационному входу триггера 3. Выход триггера 3 соединен с информационным входом регистра 4 сдвига и одновре- :менно является выходом устройства. Прямые и инверсные выходы регистра 4 сдвига через элемент 5 эквивалентности и слоговый фильтр 6 соединены ;с первым входом первого сумматора 7, :выход которого подключен к информа ционному входу амплитудно-импульсного 25 двухполярные импульсы с выхода ампли- .;модулято:ра 8, управляющий вход кото- тудно-импульсного модулятора 8 через

рого соединен с информационным входом регистра сдвига 4. Выход амплитудно- импульсного модулятора 8 соединен с одним из входов второго сумматора 9, выход которого через интегратор 10 подключен к вторбму входу компаратора 2. Информационные входы блока I1 шумокомпенсации подключены к первым двум прямым и инверсным выходам регисТтра 4 сдвига, а выход блока 1 1 шумокомпенсации соединен с вторым входом первого сумматора 7. Вход элемента 12 НЕ подключен к выходу компаратора 2, а выход соединен с первым входом дифференциаль ого усилителя 13,. второй вход которого подключен к входу элемента 12 НЕ, а выход через фильтр 14 нижних.частот соединен с другим входом второго суммато

ра 9, Тактовые входы триггера 3, регистра 4 сдвига и блока 1 шумокомпенсации соединены между собой и заведены на тактовую шину 15.

Дельта-модулятор работает щим образом.

Входной аналоговый сигнал, ограниченный по полосе входным фильтром

I, поступает на первый вход компаратора 2 и сравнивается с сигналом, присутствующим на втором его входе (фиг, 2а), Б зависимости от соотношения амплитуд сигналов на входах компарато.ра 2 на его выходе появлярегистров и других подобных задерживающих элементов, а информация на ее вход поступает не с выходов триггера 3 или регистра 4 сдвига, а непо- следую- gQ средственно с выхода компаратора 2. Как видно из фиг. 2, структура сигнала на выходе триггера 3 (фиг, 2в) отлича.ется от сигнала на выходе компаратора 2 (фиг. 26),, более оперативно и без задержек отражает возник-- шую в схеме асимметрию. Формирование дополнительного симметрирующего уровня производится при помощи фильтра 14 нижних частот, на вход которого

55

ется либо нулевой, либо единичньй логический уровень (фиг, 2б), который записывается в триггер 3 через

его информационный вход, по приходу на тактовый вход триггера 3 очередного тактового импульса. Сигнал с выхода триггера 3 является выходным сигналом дельта-модулятора (фиг.2в),

а также используется в цепи обратной связи для формирования напряжения аппроксимации выходного сигнала, поступающего на второй вход компаратора 2. С выхода триггера 3 цифровой

сигнал переписывается в регистр 4 сдвига, анализируется элементом 5 эквивалетности и усредняется слоговым фильтром 6 и через первьй вход сумматора 7 поступает на информационный вход амплитудно-импульсного модулятора 8 в виде напряжения, управляющего величиной шага квантования сигнала аппроксимации дельта-модулятора. Модулированные по амплитуде

второй сумматор 9 поступают на интегратор 10, где происходит восстановление входного сигнала кодека (фиг. 2а). Блок II шумокомпенсации предназначен для подавления шумов свободного канала, возникающих вследствие неравенства зарядных и разрядных токов основного интегратора 10, возможной несимметричности компаратора 2 и амплитудно-импульсного модулятора 8 и из-за гистерезиса компаратора 2. Вьпсодные сигналы блока 1 1 подаются через первый сумматор 7 на амплитудно-импульсный модулятор 8, корректируя возникающие искажения.

Вторая петля отрицательной обратной связи включает в себя элемент 12 НЕ, дифференциальный усилитель 13 и

фильтр 14 нижних частот и не содержит

поступает преобразованный: при помощи элемента 12 НЕ (фиг. 2г) и дифференциального усилителя 13 двухполярный сигнал (фиг. 2д). Выходной сигнал фильтра 14 нижних частот (фиг. 2е), представляюпщй собой дополнительный симметрирующий уровень, подаваемый через второй сумматор 9 на интегратор 10, в совокупности с выходным сигналом блока 1I шумокомпенсации (работающего не так оперативно, но зато более стабильно) позволяет прак

тически полностью скомпенсировать возникающ то в устройстве асимметрию, а следовательно, устранить шумы свободного канала как при высоких, так и при низких частотах тактирования дельта-модулятора. Вследствие того, что вторая петля отрицательной обратной связи не тактируется, ее режим регулируется автоматически, поэтому нет необходимости в точной ее настройке.

Ф«г.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-кодер | 1987 |

|

SU1441482A1 |

| Дельта-модулятор | 1984 |

|

SU1203707A1 |

| Дельта-модулятор | 1980 |

|

SU917339A1 |

| Низкоскоростной дельта-модулятор | 1983 |

|

SU1138950A1 |

| Дельта-модулятор | 1984 |

|

SU1241478A1 |

| УСТРОЙСТВО СВЯЗИ С ДЕЛЬТА-МОДУЛЯЦИЕЙ | 1994 |

|

RU2104614C1 |

| УСТРОЙСТВО СВЯЗИ С ДЕЛЬТА-МОДУЛЯЦИЕЙ | 1994 |

|

RU2104613C1 |

| Устройство для преобразования цифровых сигналов | 1991 |

|

SU1803982A1 |

| Дельта-модулятор | 1978 |

|

SU752799A1 |

| Дельта-модулятор | 1983 |

|

SU1121777A2 |

| Авторское свидетельство СССР № 756633, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Дельта-модулятор | 1983 |

|

SU1121777A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-11-15—Публикация

1984-05-30—Подача