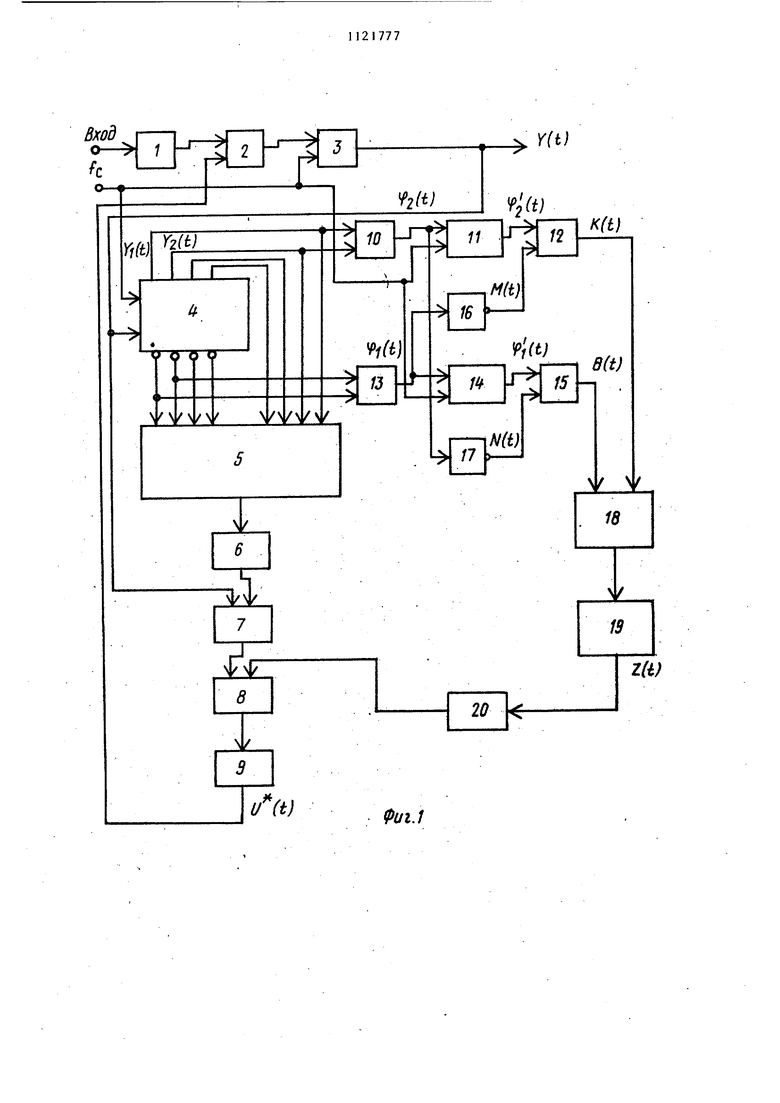

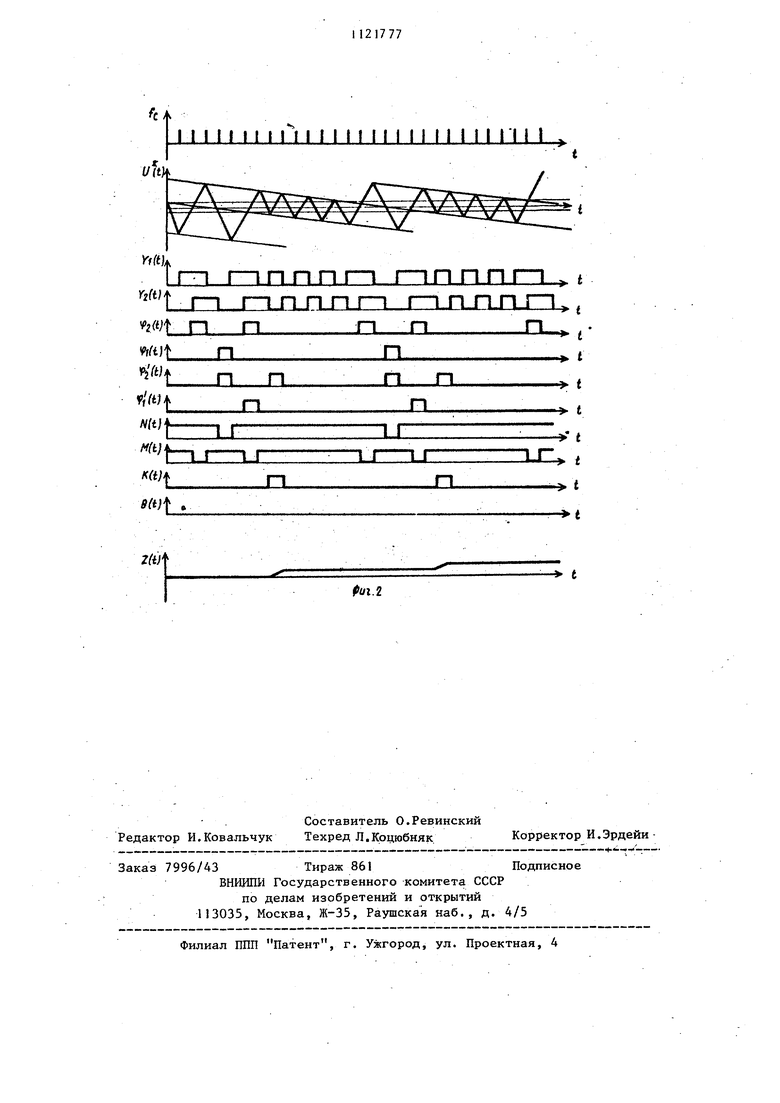

ч 1 Изобретение относится к импульсной технике и предназначено для пре образования речевых сигналов в цифровую форму для дальнейшей коммута ции и уплотнения. По основному авт.ев, 752799 известен дельта-модулятор, содержащий соединенные последовательно входной фильтр, компаратор, триггер и четырехразрядный регистр сдвига, соединенные последовательно элемент эквивалентности, слоговый интегратор, амплитудно-импульсный модулятор, первый преобразователь полярно ти и основной интегратор, два элеме та совпадения и соединенные последовательно второй преобразователь полярности, дополнительный интегратор и усилитель, причем тактируемые входы триггера и четырехразрядного регистра сдвига соединены с тактовой шиной, прямые и инверсные выход разрядов четырехразрядного регистра сдвига подключены к входам элемента эквивалентности, второй вход компар тора подключен к выходу основного и тегратора, второй вход амплитудноимпульсного модулятора соединен с .выходом триггера, второй вход перво го преобразователя полярности соеди нен с выходом усилителя, входы второго преобразователя полярности сое динены с выходами элементов совпадения, входы которых подключены соответственно к прямым и,инверсным выходам первых двух разрядов четыре разрядного регистра сдвига С ID. Недостаток этого устройства - не высокая степень подавления шумов св бодного канала, что снижает качество преобразования сигналов. Цель изобретения - улучшение качества преобразования сигналов путем уменьшения мощности шумов свободного канала. Поставленная цель достигается тем, что в дельта-модулятор введены два инвертора и две цепочки из соединенных последовательно двухразряд ного регистра сдвига и дополнительного элемента совпадения, включенные между выходами соответствующих элементов совпадения и соответствую щими входами второго преобразователя полярности, при этом выходы инверторов соединены с другими входами соответствующих дополнительных элементов совпадения, входы первого и второго инверторов подключены к 72 выходам соответственно второго и первого элементов совпадения, а тактируемые входы двухразрядных регистров сдвига соединены с тактовой шиной. На фиг. приведена блок-схема дельта-модулятора; на фиг.2 - временные диаграммы, поясняющие принцип его работы. Дельта-модулятор содержит входной фильтр I, соединенный с первым входом компаратора 2, выход которого подключен к первому входу триггера 3. Выход триггера 3 соединен с первым входом четырехразрядного регистра 4 сдвига и одновременно является выходом устройства. Прямые и инверсные выходы четырехразрядного регистра 4 сдвига через элемент 5 эквивалентности соединены со слоговым интегратором 6; выход которого подключен к первому входу амплитудно-импульсного модулятора 7, второй вход которого соединен с выходом триггера 3. Выход а(тлитудно-импульсного модулятора 7 подключен к первому входу первого преобразователя 8 полярности, выход которого через основ.ной интегратор 9 соединен с вторым входом компаратрра 2. Входы первого элемента 10 совпадения подключены к прямым выходам первого и второго разряда четырехразрядного регистра 4 сдвига, а выход элемента 10 совпадения соединен с первым входом первого двухразрядного регистра I1 сдвига. выход которого соединен с первым входой первого дополнительного элемента 12 совпадения. Входы второго элемента 13 совпадения подключены к инверсным выходам первого и второго разряда четырехразрядного регистра 4 сдвига, а выход элемента 13 совпадения через первый вход второго двухразрядного регистра 14 сдвига соединен с первым входом второго дополнительного элемента 15 совпадения. Вход первого инвертора 16 подключен к выходу первого элемента 13 совпадения, выход его - к второму входу первого дополнительного элемента 12 совпадения, кроме того, вход второго инвертора 17 соединен с выходом.первого элемента 10 совпадения , а выход его - с вторым входом BTopofo дрполнительногр элемента 15 совпадения . Выходы элементов I2 и 15 соединены с первым и вторым входами второго преобразователя 18 полярности. 31 выход которого через дополнительный интегратор 19 и усилитель 20 соединей с вторым входом первого преобра зователя 8 полярности. Дельта-модулятор работ&ет следующим образом. При отсутствии сигнала на входе устройства выходной сигнал X, (t)должен представлять собой последовательность чередующихся импульсов ...1010..., причем период этрй последовательности определяется как Q , где -Ер - частота следования тактовых импульсов. Однако на практике характеристика компаратора 2 вйегда обладает некоторым гистерезисом, т.е. пороги переброса ко в Г О всегда различны. Это вызывает появление в выходной последовательности периодически повторяющихся пачек из сдвоенных единичных и нулевых импульсов. Meханизм появления таких пачек из сдвоенных единичных и нулевых импульсов иллюстрируется временными диаграммами на фиг.2 где fJ. - последовательность импул сов , стробирующих дельта кодер; - напряжение на выходе основного интегратора; (t)X(t|- сигналы на первом и втором выходах четырёхразряд ного регистра сдвига соот ветственно; i/{t),V.(-t)- сигналы на выходах элемен тов совпадения; (t),/2(tl- сигналы на выходах двухра рядных регистров сдвига; M(-fcl,W(t) - сигналы на выходах инвер/ торов, (Clt),6(i) - сигналы на выходах дополн тельных элементов совпаде ния ; Z(t) - медленно меняющееся напря жение, на выходе дополнительного интегратора, уро вень которого пропорциона лен степени асимметрии устройства. Очевидно, что в сигнале Y(-t), а значит и в сигнале Y2(t) содержатся пачки двойных единичных и нулевых импульсов. В данном устройстве выходная последовательность по мере поступления стр1обирующих импульсов записьшается в четырехразрядный регистр 4 сдвига анализируется элементом 5 эквива7лентности и усредняется слоговым интегратором 6. На выходе слогового интегратора 6 появляется сигнал, представляющий собой постоянную составляющую, величина которой изменяется в зависимости от амплитуды и частоты входного сигнала. Эта постоянная составляющая используется для управления величиной импульсов, воздействующих на основной интегратор 9, при помощи амплитудно-импульсного модулятора 7 и первого преобразователя 8 полярности. При отсутствии в выходной последовательности Y (Ч:) пачек единичных или нулевых импульсов на выходах элементов 10 и 13 совпадения импульсы не появляются и соответственно блоки 10-20 никакого влияния на работу устройства не оказывают. При появлении в выходной последовательности сдвоенной пачки единичных импульсов на выходе элемента О совпадения появляется единичный импульс. В случае появления; пачки, состоящей из двух нулевых импульсов, единичный импульс появляется на выходе элемента 13 совпадения. Причем из-за гистерезиса компаратора 2 двойная нулевая пачка следует всегда сразу же за двойной единичной пачкой (фиг.2 ). Кроме того, преобладание единичных либо нулевых пачек импульсов в выходном сигнале кодера является прйзнаком существования асимметрии в устройстве. При преобладании в выходной последовательности единичных пачек им-г пульсов (фиг.2) выходная последовательность (-Ь) записывается в четырехразрядный регистр 4 сдвига и с приходом каждого стробирующего импульса продвигается по регистру 4 на один разряд. Каждая двойная пачка единичных импульсов, записанная в два первых разряда четырехразрядного регистра 4 сдвига, вызьшает появление на выходе элемента 10 совпадения, подключенного к первым выходам регистра 4, единичного импульса, в то время как на выходе .элемента iJcoBnaдения сигнал отсутствует, так как данный элемент подключен к инверсным выходам регистра 4. В течение действия следующих двух стробирующих импульсов единичный импульс с выхода элемента 10 совпадения переписывается на выход двухразрядного регистра 11 сдвига и поступает на первый вход дополнительного элемента 12 совпадения. Теми же стробирующими импульсами двойная единичная пачка переписывается в последующие разряды четырехразрядного регистра 4 сдвига и на ее место записывается двойная пачка нулевых импульсов, которая следует за единичной-, вследствие гистерезиса компаратора 2. Записанная в два первых разряда регистра 4 нулевая пачка вызьшает появление на выходе элемента 13 совпадения единичного импульса, который инвертируется инвертором 16 и поступает на второй вход дополнительного элемента 12 совпадения. Таким образом, на первом входе дополнительного элемента 12 совпадения появляется единичный импульс, а на втором его входе - нулевой импульс, что не вызывает изменений сигнала на вы.ходе данного элемента. Если за двойной единичной пачкой не следует двойная нулевая пачка (а следует, например, комбинация 10, либо 01, то на выходе элемента 13 совпадения остается нулевой сигнал и соответственно на втором входе дополнительного элемента 12 совпадения присутствует единичный потенциал, которьй является разрешающим для прохождения импульсов с выхода двухразрядного регистра 11 сдвига на. выход дополнительного элемента 12 совпадения. Таким образом, лишь при преобладании в выходной последовательности единичных двухэлементных пачек на выходе дополнительного элемента 12 совпадения будут появляться единичные импульсы. Нетрудно убедиться в том, что при преобладании в выходной последовательности двухэлементных нулевых пачек, единичные импульсы будут появляться на выходе дополнительного элемента 15 совпадения. Импульсы, появляющиеся на выходах дополнительных элементов 12 и 15 совпадения являются информацией о Наличии асимметрии того или иного знака. Эти импульсы поступают на второй преобразователь 18 полярности, затем усредняются дополнительным интегратором 19 и после усиления усилителем 20 подаются на второй вход, первого преобразователя 8 полярности в качестве сигнала, компенсирующего асимметрию.

Как видно из алгоритма работы устройства, импульсы, управляющие вторым преобразователем 18 полярности, поступают только на один из его входов в зависимости от знака асимметрии.

Таким образом, в предлагаемом уст5 ройстве за счет введения новых элементов 15 и 12, регистров 14 и 11, Инверторов 16 и 17 на дополнительный интегратор 19 воздействует не каждая двойная пачка единичных и ну0 левых импульсов. Симметричные комбинации импульсов вида 11001100, не несущие информации об асимметрии в дельта-модуляторе, устраняются введенными элементами I5 и 12 регист5 ров 14 и II, инверторов 16 и 17, и дополнительный интегратор 19 во второй цепи обратной связи реагирует только на последнюю группу сдвоенных символов паузной последовательности, в которой и заключена вся информация об асимметрии. Этим устраняется нежелательньй перезаряд емкости дополнительного интегратора 19 в течение воздействия на вход четырехразрядного регистра 4 сдвига симметричных последовательностей вида 11001100. При этом в постоянной составляющей, вьщеляемой на дополнительном интеграторе 19, не содержится пульсаций напряжений.

За счет уменьшения пульсаций на дополнительном интеграторе 19 существенно снижаются нелинейные искажения сигнала,- восстанавливаемого на основном интеграторе 9. Кроме

того, все блоки предлагаемого устройства построены на базе цифровых интегральных микросхем, что позволяет значительно уменьшить его габариты, повысить надежность и открывает

возможность для реализации всего устройства в виде единой интегральной микросхемы.

I И I t И i t I I И M I I I I I I I I I I I 111

-/ Irn Г ТППП1-I I-1ПППГП ., t

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-модулятор | 1983 |

|

SU1129732A1 |

| Дельта-модулятор | 1978 |

|

SU752799A1 |

| Преобразователь дельта-модулированного сигнала в импульсно-кодомодулированный сигнал | 1985 |

|

SU1282336A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Дельта-декодер | 1983 |

|

SU1181152A1 |

| СПОСОБ КОДИРОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2168270C2 |

| Устройство конференц-связи | 1979 |

|

SU886311A1 |

| Дельта-кодер | 1987 |

|

SU1441482A1 |

| Дельта-кодер | 1988 |

|

SU1646056A1 |

| Устройство для регистрации сейсмических сигналов | 1989 |

|

SU1681288A1 |

ДЕЛЬТА-МОДУЛЯТОР по авт. св. № 752799, отлйчающийс я тем, что, с целью улучшения качества преобразования сигналов путем уменьшения мощности шумов свободного канала, в него введены два инвертора и две цепочки из соединенных последовательно двухразрядного регистра сдвига и дополнительного элемента совпадения, включенные между выходами соответствукщих элементов совпадения и соответствующими входами второго преобразователя полярности, при этом выходы инверторов соединены с другими входами соответствующих дополнительных элементов совпадения, входы первого и второго инверторов подключены к выходам соответственно второго и первого элементов совпадения, а тактируемые входы двухразрядных регистров сдвига соединены с тактовой , (Л шиной..

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Дельта-модулятор | 1978 |

|

SU752799A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-10-30—Публикация

1983-07-19—Подача