1//1

00 ьг

1

Изобретение относится к вьписли- тельиой технике и технике связи и мжет использоваться в систеь ах передчи сигналов.

Цель изобретения - повышение достоверности преобразования за счет снижения шумов свободного канала и расширени51 динамического диапазона преобразуемых сигналов.

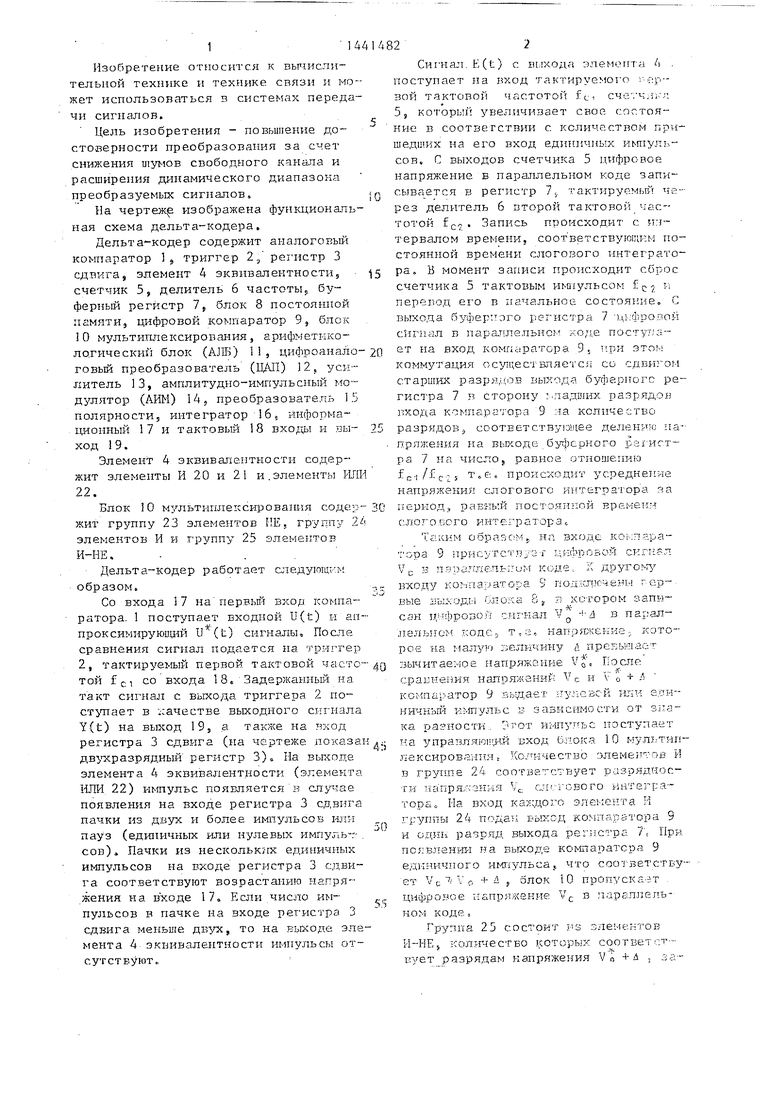

На чертежу изображена функ1;ионап иая схема дельта-кодера.

Дельта -кодер содержит аналоговьш компаратор 1, триггер 2,, рех истр 3 сдвига, элемент 4 эквивалентности.

счетчик 5j делитель 6 частоты., буферный регистр 7j блок 8 постоянной памяти, цифровой компаратор 9, блок 0 мультиплексирования, арифметккоСигнал. E(t) с выхода злемеггта 4 поступает на вход тактируемот о ; гг:рзой тактовой частотой fc сче ; ч.;ь.5, которь й увеличивает СВОЕ состояние в соответствии с количеством пр шедших на его вход единичных им1уль 00в. С выходов счетчика 5 цифровое напряжение в параплельном коде запи сывается в регистр 7;, тактируемый ч рез делитель 6 второй тактовой частотой f ;7 Запись происходит с интервалом времени, соот ветствуюьчкм п стоянной времени слогового интеграт ра. В момент записи происходргг сбро счетчика 5 тактовым иьиульсом iпере1 од его в начальное состоян ае выхода буфер;тэго регистра 7 1и ;-фрово с{1гпал в паратшельнон коде поступа25

логический блок (AJIB) 1, цифроанало-20 вход компаратора 9. 1;ри этоы говьш преобразователь (ЦДП) 12, уск- литель 13, амплитудно-импульсный модулятор (ЛИМ) lA. преобразователь 15 ПОЛЯРНОСТИ;, интегратор 6s информационный 17 и тактовьй 18 входф и зы- ход 19.

Элемент 4 эквивалентности содержит элементы И 20 и 21 и.элементы РШИ 22.

Блок 10 мультипле ссирован15я содер-30 жит группу 23 элементов ПЕ группу 24 элементов И и группу 25 элементов И-НЕ, . . .

Дельта-кодер работает следующим образом,...

Со входа 7 на первьшг вход компаратора. 1 поступает входной U(t) и ап- прокснмируюБщй и (t) сигналы. После сравнения сигнал подается на триггер 2, тактируемый первой тактовой часто-40 той f (-. 1 со входа 18, Задержанный на такт сигнал с выхода триггера .2 по- в сачестве выходного сигнала Y(t) на выход 19, а таклсе на вход регистра 3 сдвига (на чертеже показан ;- двз осразрядный регистр 3). Ыа вькоде элемента 4 эквивалентности (элемента ИЛИ 22) импульс появляется з появления на входе регистра 3 сдвига пачки из двух и более импульсов иля пауз (единичных или нулевых импуль- сов). Пачки из нескольких единичных импульсов на входе регистра 3 сдвига соответствуют возрастанию напря-- жения на входе 17. Если число импульсов в пачке на входе регистра 3 сдвига меньше двух, то на выходе элемента 4 эквивалентности импульсы от- сутству1от„

5П

55

коммутация осутиествзтяется со сдвиуо старших разрял-оэв выхода буферногс р гистра 7 в сторону :.ладш1-1Х разрядов лхода компаратора 9 на количество разрядов.; соответствующее делениьз н пряжения на выходе б уг})ерного рег игт ра 7 на числоJ равное отношению fe-1/fc/s т„е происходят усреднение напряжения слогового интегратора за период, постоянной времени с логового интегратораS

Таким образс м,, на входе ког-:пара- тора 9 присутстпуэт цифровой сигнал VP 3 пэрагшепьпим коде. К другот входу ко1-1паратора 9 подкл счены -ср- вые ж ккоды блока и, л котором записан ц -Афрозой сиг кап V в параллельном коде, T,s, напр скекие, кото рое на г-шлую величину д преЕЬиает вычитаемое напряжение VJ. сра.цнеиия напряжений с и v o + компаратор 9 вьтцает nyjiCECu i-ши е.пи ничньй кмпульс в зависимоCTVJ от зна ка разности. гот 1П--шу.г ьс поступает на управляюп ий вход блока 10 лекснрова:-П1Я г Ко..-.-1чество элементов в группе 24 соответствует разряднос ти напря; зння V cjirroBoro интегратора,, Ыа вход ка ::дого элемента И гругты 24 подан ЕЬПСОД компаратора 9 и одт Ь разр.яд выхода регистра 7, Пр появлени:н на выходе компаратсра 9 единичного игшульса, что соответств е т V г цифровое ном коде.

Группа 25 состоит РЗ злементов И-НЕ, : ол -иество которых соответст- Е ует разрядам налряжения о +& , 3i

i + 4 J блок 10 пропуск H JT

напряжение V. в араплель2

Сигнал. E(t) с выхода злемеггта 4 . поступает на вход тактируемот о ; гг:р- зой тактовой частотой fc сче ; ч.;ь.; 5, которь й увеличивает СВОЕ состояние в соответствии с количеством пришедших на его вход единичных им1уль- 00в. С выходов счетчика 5 цифровое напряжение в параплельном коде записывается в регистр 7;, тактируемый через делитель 6 второй тактовой частотой f ;7 Запись происходит с интервалом времени, соот ветствуюьчкм постоянной времени слогового интегратора. В момент записи происходргг сброс счетчика 5 тактовым иьиульсом ii пере1 од его в начальное состоян ае С выхода буфер;тэго регистра 7 1и ;-фровой с{1гпал в паратшельнон коде поступа5

0 вход компаратора 9. 1;ри этоы

0

..

0 ;-

П

5

коммутация осутиествзтяется со сдвиуом старших разрял-оэв выхода буферногс регистра 7 в сторону :.ладш1-1Х разрядов лхода компаратора 9 на количество разрядов.; соответствующее делениьз напряжения на выходе б уг})ерного рег игт- ра 7 на числоJ равное отношению fe-1/fc/s т„е происходят усреднение напряжения слогового интегратора за период, постоянной времени с логового интегратораS

Таким образс м,, на входе ког-:пара- тора 9 присутстпуэт цифровой сигнал VP 3 пэрагшепьпим коде. К другот входу ко1-1паратора 9 подкл счены -ср- вые ж ккоды блока и, л котором записан ц -Афрозой сиг кап V в параллельном коде, T,s, напр скекие, которое на г-шлую величину д преЕЬиает вычитаемое напряжение VJ. сра.цнеиия напряжений с и v o + компаратор 9 вьтцает nyjiCECu i-ши е.пи- ничньй кмпульс в зависимоCTVJ от знака разности. гот 1П--шу.г ьс поступает на управляюп ий вход блока 10 лекснрова:-П1Я г Ко..-.-1чество элементов И в группе 24 соответствует разрядности напря; зння V cjirroBoro интегратора,, Ыа вход ка ::дого элемента И гругты 24 подан ЕЬПСОД компаратора 9 и одт Ь разр.яд выхода регистра 7, При появлени:н на выходе компаратсра 9 единичного игшульса, что соответству- е т V г цифровое ном коде.

Группа 25 состоит РЗ злементов И-НЕ, : ол -иество которых соответст- Е ует разрядам налряжения о +& , 3i

i + 4 J блок 10 пропуск H JT

напряжение V. в араплельпнса миог О в Олоко 8. la один из входов каждого элемента И-ИЕ заведен выход компаратора 9, а на второй вход - разряд цифровог о напряжения V + Л , проинвертнрованного элементом НЕ группы 23. При поступлении с выхода компаратора 9 нулевого импульса, что соответствует V. - V + 4 , на вькоде группы 25 элементов И-НЕ появляется двоичное напряжение V +d в параллельном коде, что делается с целью задания минимального напряжения X J + i-J , ниже которого не может быть напряжения Vt слогового интегратора, - при этом (при дальнейшем вычитании Vc - Vp) разность V с - V всегда положительная. Такая опера1щя устраняет пульсадии на выходе слогового, интегратора (т.е счетчика 5, делителя 6 и регистра 7),

С выходов блока 10 на первьй вход АЛБ поступает цифровой сигнал Vc V -г л На вторые входы АЛБ 1 i заведены вторые выходы блока 8, где в параллельном коде записано вычитываемое напряжение V. Это напряжение вычитается с целью повьшения степени сжагия AroiaNiH4ecKoro диапазона.

Разность Vf. V с выходов /ШБ 11

3 параллельном коде подается на входы ЦАП 12, где преобразуется в аналоговое напряжение V с- V и, пройдя через усилитель 13, умножается на коэффициент Kg усилчения. Полученное напряжение KC-(VC- V) посту17ает на первьй вход АИМ IA, на второй вход которого подается вьгходной сигнал Y(t), С выхода АШ 4 сигнал V(t) с амплитудой, измененной в соответствии с уровнем KC-(VC - V), поступает на вход преобразователя 15 полярности, С его выхода двухполярное напряжение V(t) поступает на вход интегратора

0

5

0

5

Я1етяется информационным входом дельта-кодера, выход соединен с информационным входом триггера, выход которого подключен к информационному входу регистра сдвига и является выходом дельта-кодера 5 тактовьй вход регистра сдвига объединен с тактовым входом триггера и входом делителя частоты и является тактовым входом дельта-кодера, прямые и инверсные выходы разря-, дов регистра сдвига соединены с пер- -выми и вторыми входами элемента эквивалентности, выход которого подключен к счетному входу счетчика, буферный регистр, блок постоянной памяти, первые выходы которого соединены с первыми входа ш цифрового компаратора, блок мультиплексирования ариф- метико-логическш1 блок и цифроанало- говый преобразователь, отличающийся тем, что, с целью повьцпения достоверности преобразования за счет снижения шумов свободного 5 канала и расширения динамического диапазона преобразуемых сигналов, в дельта кодер введены усилитель и последовательно соединенные амплитудно- импульсный модулятор, преобразователь полярности и интегратор, выход которого подключен к второму входу аналогового компаратора, выход делителя частоты соединен с тактовым входом буферного регистра и входом обнуления счетчика, тактовый вход которого подклкг ен к тактовому входу дельта- кодера , выходы счетчика г зединены с информационными входами буферного регистра, выходы которого подключены к первым информационным входак блока, мультиплексирования и соответствующим вторым входам цифрового компаратора, выход которого соединен с управляющим входом блока мультиплекси0

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Преобразователь сигналов с импульсно-кодовой модуляцией в сигналы с адаптивной дельта-модуляцией со слоговым компандированием | 1990 |

|

SU1709537A1 |

| Дельта-кодер | 1988 |

|

SU1646056A1 |

| Дельта-кодек | 1987 |

|

SU1427572A1 |

| Дельта-кодер | 1987 |

|

SU1429321A1 |

| Адаптивный дельта-модулятор | 1990 |

|

SU1815801A1 |

| Преобразователь сигналов с адаптивной дельта-модуляцией со слоговым компандированием в сигналы с нелинейной импульсно-кодовой модуляцией | 1990 |

|

SU1762411A1 |

| Дельта-кодер | 1989 |

|

SU1612375A1 |

| Дельта-кодер | 1984 |

|

SU1197088A1 |

| УСТРОЙСТВО СВЯЗИ С ДЕЛЬТА-МОДУЛЯЦИЕЙ | 1994 |

|

RU2104614C1 |

Изобретение относится к вычислительной технике и технике связи. Его использование в системах передачи сигналов позволяет повысить достовер-, ность преобразования за счет снижения шумов свободного канала и расширения динамического диапазона преобразуемых сигналов. Дельта-кодер содержит аналоговый компаратор 1, триггер 2, регистр 3 сдвига, элемент 4 эквивалентности, счетчик 5, делитель 6 частоты, буферный регистр 7, блок .8 постоянной памяти, цифровой компаратор 9, блок 10 мультиплексирования, арифметико-логический блок II и циф- роаналоговый преобразователь 12. Благодаря введению усилителя I3, амплитудно-импульсного модулятора 14, преобразователя 15 полярности и интегра-J2 тора 16, а также соответствующей S ганизации соединений в дельта-кодере обеспечивается более высокая достоверность преобразования. 1 кл. (Л

б5формирующего ступеньку аппроксими- , рования, вторые информационные входы рующего напряжения U (t), поступаюкоторого подключены к первым выходам блока постоянной памяти, выходы блока мультиплексирования и вторые выходы блока постоянной памяти сое- . динены с первыми и вторы ш входами арифметико-логического блока, выходы которого подключены к входам цифро- аналогового преобразователя, выход которого через усилитель соединен с первым входом а тлитудно-импульсного модулятора, второй вход которого подключен к выходу триггера.

щего на второй вход компаратора 1, Таким образом, в дельта-кодере обеспечивается сжатие динамического диапазона и уменьшение шумов свободного канала в режиме холостого хода, благодаря чему повышается достоверность преобразования.

Формула изобретения Дельта-кодер, содержащий анапого- ULM компаратор, первый вход которого BffifflllH Заказ 6296/57

, рования, вторые информационные входы

50

которого подключены к первым выходам блока постоянной памяти, выходы блока мультиплексирования и вторые выходы блока постоянной памяти сое- . динены с первыми и вторы ш входами арифметико-логического блока, выходы которого подключены к входам цифро- аналогового преобразователя, выход которого через усилитель соединен с первым входом а тлитудно-импульсного модулятора, второй вход которого подключен к выходу триггера.

ираж 929 Подписное

55

| Котович Г.Н., Ламекин В.Ф; Проектирование дельта-преобразователей речевых сигналов | |||

| М.: Радио и связь, 1986, с, | |||

| Способ изготовления звездочек для французской бороны-катка | 1922 |

|

SU46A1 |

| Дельта-модулятор | 1983 |

|

SU1121777A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Дельта-кодер | 1984 |

|

SU1197088A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-11-30—Публикация

1987-06-17—Подача