ел

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-демодулятор | 1991 |

|

SU1803981A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Адаптивный дельта-модулятор со слоговым компандированием | 1991 |

|

SU1785078A1 |

| УСТРОЙСТВО СВЯЗИ С ДЕЛЬТА-МОДУЛЯЦИЕЙ | 1994 |

|

RU2104614C1 |

| УСТРОЙСТВО СВЯЗИ С ДЕЛЬТА-МОДУЛЯЦИЕЙ | 1994 |

|

RU2104613C1 |

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| Устройство конференц-связи для систем с дельта-модуляцией | 1986 |

|

SU1418926A1 |

| Дельта-кодер | 1988 |

|

SU1646056A1 |

| Устройство для цифровой записи воспроизведения речевой информации | 1988 |

|

SU1573470A1 |

| Дельта-демодулятор | 1984 |

|

SU1269270A1 |

| Изобретение относится к электросвязи и может быть использовано в системах теле- фонрой связи с дельта-модуляцией с цифровым инерционным компандированием. Цель изобретения - повышение помехоустойчивости. Дельта-п-разрядный двоичный регистр сдвига 1, n-разрядного буферного регистр-сдвига 2, ключ 4, счетчик 5, дешифратор б, триггер 7, блок синхронизации 8 и управляемый генератор 9, шину тактовых импульсов 3, слоговый фильтр 10, амплитудно-импульсный модулятор 11, интегратор 12, выходной фильтр нижних частот 13 и обеспечивает сведение к нулю воздействие случайных ошибок с вероятностью менее 3,3 на работу блока компандирования. 2 ил., 1 табл.

Фм1

00

о со ю

00

Изобретение относится к электросвязи и может быть использовано в системах телефонной связи с дельта-демодуляцией (ДМЦИК) и дельта-сигма-модуляцией (ДСМЦИК) с цифровым инерционным ком- пандированием для повышения их помехоустойчивости.

Цель изобретения - повышение помехоустойчивости.

На фиг. 1 представлена структурная электрическая схема предлагаемого устройства; на фиг. 2 - временные диаграммы, иллюстрирующие работу дельта-модулятора, где

а - сигналы дельта-потока на входе демодулятора;

б - сигналы на шине такта с частотой FT;

в - сигналы на шине такта в увеличенном масштабе;

г-сигналы на входе управляемого генератора импульсов;

д - сигналы на выходе управляемого генератора импульсов;

е - сигналы на тактовом входе триггера;

ж - сигналы на управляющем входе счетчика;

з - сигналы на управляющем входе буферного регистра;

и - сигналы на выходе буферного регистра;

к - сигналы на счетном входе счетчика;

л - сигналы на выходе дешифратора;

м - сигналы на выходе триггера.

Дельта-модулятор содержит первый п- разрядный регистра сдвига 1, информационный вх од которого является входной шиной 2, а тактовый соединен с шиной такта 3, выходы всех разрядов соединены со входами блока управления компандиро- ванием 4, а выход k-ro разряда - с информационным входом амплитудно-импульсного модулятора 5, управляющий вход которого подключен к выходу блока управления компандированием, тактовый вход которого соединен с шиной такта, выход амплитудно-импульсного модулятора соединен со входом интегратора б, выход которого подключен к входу выходного фильтра 7, выход которого является выходной шиной, причем блок управления компандированием выполнен на блоке синхронизации 8, управляемом генераторе импульсов 9 и последовательно соединенных п-разрядном буферном регистре сдвига 10, входы разрядов которого являются соответственно входами блока управления, ключе 11, счетчике 12, дешифраторе 13, триггере 14 и слоговом фильтре 15, выход которого является выходом блока управления компаидированием, причем управляющие входы счетчика, триггера и управляемого генератора импульсов соединены с соответствующими выходами блока синхронизации, вход которого объединен с управляющим входом буферного

регистра сдвига и является тактовым входом блока управления компандированием, а выход управляемого генератора импульсов соединен с тактовым входом буферного регистра и управляющим входом ключа.

Демодулятор работает следующим образом.

Сигналы дельта-потока, задержанные на k тактов в регистре сдвига 1, поступают на вход амплитудно-импульсного модулятора (АИМ) 5, с выхода которого после интегрирования и низкочастотной фильтрации снимается восстановленный речевой сигнал. Сигнал, управляющий величиной ступеньки квантования подается на второй

вход АИМ с выхода блока управления компандированием 4. Известно, что наилучшее качество речи обеспечивается при постоянной слогового компандирования г 4... 10 мс, что соответствует ...160 или

п 128-320 тактам частоты дискретизации для скоростей 16 кбит/с и 32 кбит/с соответственно. Учитывая, что средняя длительность слогов составляет около 250-260 мс, на интервале времени т возможна обработка сигнала управления компандированием по алгоритму, обеспечивающему наибольшую помехоустойчивость. С этой целью импульсы входного дельта-потока с выходов регистра 1 на каждом такте переписываются в буферный регистр 10, который за время каждого такта осуществляет параллельную запись информации, а затем ее последовательный вывод с частотой F2, вырабатываемый узлом 9, Частота F2 выбирается из

соотношения п FT. С выхода буферного регистра информационная последовательность стробируется ключом 11 и подается на счетный вход счетчика 12, на вход сброс которого подаются сигналы начальной установки. Емкость счетчика равна п двоичных единиц. В дешифраторе 13 информация, поступающая с выхода счетчика преобразуется по следующему правилу:

50

F

1, при 2/3 n N 1/3 п О, при 1/3 п п

где N - число единиц, подсчитанных счетчиком за один такт.

В этом случае алгоритм функционирования предлагаемого устройства полностью совместим с алгоритмом ДМЦИК (ДСМЦИК). Так как на каждом такте счетчик

последовательно подсчитывает импульсы от нуля до максимально возможного значения п, то на выходе дешифратора это приводит к периодическому изменению управляющего сигнала. Для устранения этого введен триг- ге р 14, осуществляющий хранение записанной информации в течение всего такта. Сиена информации происходит в момент действия импульса перезаписи, вырабатываемого узлом синхронизации 8. Этим же углом вырабатываются сигналы начальной установки счетчика и сигнал разрешения работы генератора 9.

; Покажем, что предложенное устройство ксмпандирования нечувствительно к ка- Hi льным ошибкам, при вероятности последv1

х не более 3,3 10 . Действительно, при боте модулятора в режиме перегрузки по

м

№

крутизне, на вход демодулятора будут поступать последовательности нулей (при отрицательной перегрузке), или единиц (при положительной перегрузке), искаженные ошибками. При ,3 10 на вход счетчика будет приходить п единиц или N 2/3 п единиц, следовательно, на выходе дешифратора в конце каждого такта бу- де|г единица, то есть команда управления на увеличение шага квантования.

; Изменение амплитуды передаваемого сигнала приводит и к изменению структуры дельта-сигнала на входе демодулятора. В этом случае максимальная задержка сигнала компандирования может составлять 1/IS п тактов, которая может быть скомпенсирована переключением входа АИМ с выхода первого разряда регистра 1 на k-й, причем установлено, что лучшее качество речи обеспечивается при опережении сиг- на|а компандирования по сравнению с сигналом дельта-потока на 8... 10 тактов. Исходя из этого, k выбирают в пределах 1/4; n k 1/3 п.

Таким образом, ошибки на входе демодулятора не приводят к нарушению работоспособности схемы управления KON пандированием, тем самым достигается поЕышение помехоустойчивости предлага- емс го дельта-демодулятора.

i При практической реализации демоду- лятЬра использованы известные техниче- решения: в качестве регистров 1, 10, счетчика, дешифратора и триггера используется серийные микросхемы широкого применения, генератор 9 выполнен по известной схеме, узел синхронизации может быт|ь выполнен на основе генераторов с внеЬним запуском или импульсного распределителя. Изготовленный в организации макет дельта-кодека, содержащий

модулятор, аналогичный прототипу и предлагаемый демодулятор с 60-ти разрядной схемой анализа, выполнен на 78 ИМС серии 564, 140 и 521. Потребляемая мощность 400

мВт, масса 350 г, обьем 1,5 дм3.

Эффективность предлагаемого дельта-демодулятора оценивалась путем проведения сравнительных артикуляционных испытаний совместно с дельта-демодулятором,

0 используемым в настоящее время в серийно выпускаемой аппаратуре связи и полностью соответствующем прототипу. Оценка проводилась на скоростях 16 и 32 кбит/с. Результаты исследований представлены в таблице.

5 Проведенные испытания показали, что при предлагаемый демодулятор обеспечивает лучшую на 10-25% слоговую разборчивость речи, чем используемый, что позволяет повысить дальность прямой УКВ

0 радиосвязи на 10...30% и улучшить натуральность речи без увеличения мощности радиопередающих устройств.

Формула изобретения Дельта-демодулятор, содержащий пер5 вый n-разрядный регистр сдвига, информационный вход которого является входной шиной, а тактовый вход соединен с шиной такта, выходы всех разрядов соединены с входами блока управления компандирова0 нием, а выход К-ro разряда - с информационным входом амплитудно-импульсного модулятора, управляющий вход которого подключен к выходу блока управления компандированием, тактовый вход которо5 гс соединен с шиной такта, выход амплитудно-импульсного модулятора соединен с входом интегратора, выход которого подключен к входу выходного фильтра, выход которого является выходной шиной, о т л и0 чающийся тем, что, с целью повышения помехоустойчивости, блок управления компандированием выполнен на блоке синхронизации, управляемом генераторе импульсов и последовательно соединенных

5 разрядном буферном регистре сдвига, входы разрядов которого являются соответственно входами блока управления, счетчике, ключе, дешифраторе, триггере и слоговом фильтре, выход которого является выходом

0 блока управления командированием, причем управляющие входы счетчика, триггера и управляемого генератора импульсов соединены с соответствующими выходами блока синхронизации,вход которого объединен

5 с управляющим входом буферного регистра сдвига и является тактовым входом блока управления компандированием, а выход управляемого генератора импульсов соединен с тактовым входом буферного регистра и управляющим входом ключа.

I И

JTJTJTJlJTJTJT JTJTjnJTJTj

такт

Редактор С.Иванова

IT

Фиг.1

Составитель А.Косарев

Техред.М.МоргенталКорректор С.Пекарь

Заказ 1061Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при I кн I ссек 113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул.Гагарина, 101

-//

I JL JL I

(211)4912381/24

(2)2)20.02.91

(4р) 23.03.93. Бюл. № 11

(7fl) Грузинский технический университет

(7J2) Н.Г.Харатишвили, В.В.Нанобашвил

Р.|Г.Сванидзе и Г.Ш.Джавахишвили

(50) Патент Великобритании № 2004165,

кл1 Н 03 К 19/30, опублик. 1979.

Авторское свидетельство СССР №j 1109925, кл. Н 04 L 3/02, 1982.

(5

)

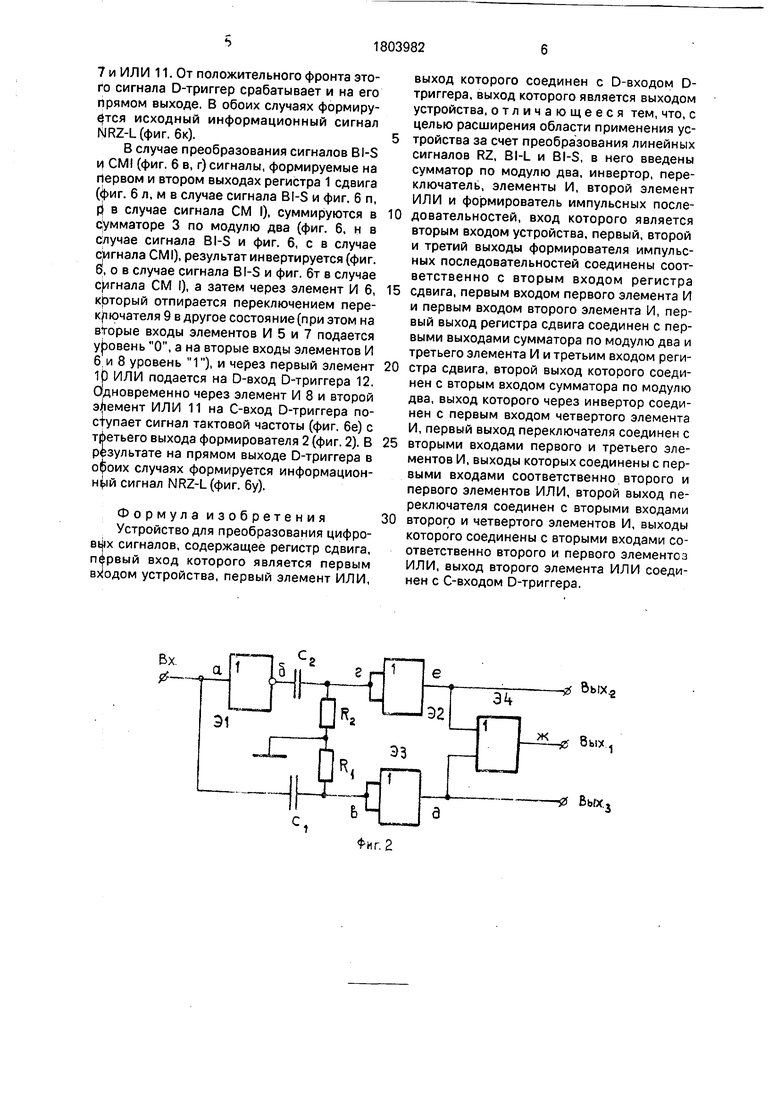

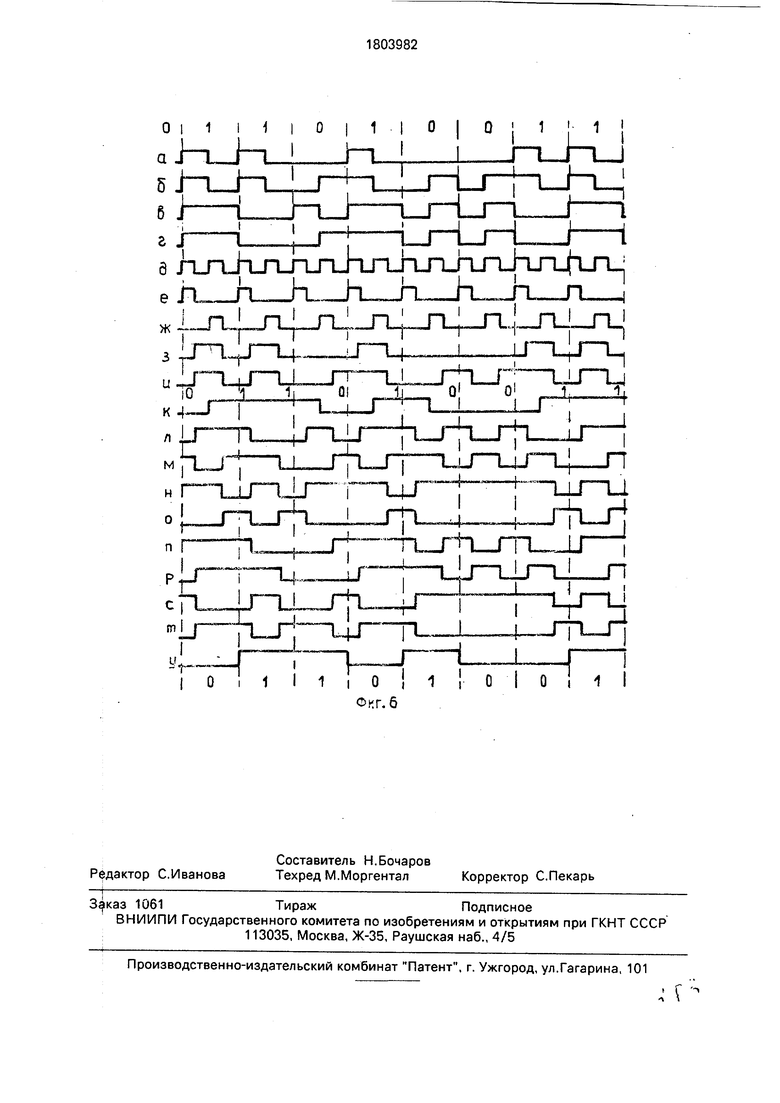

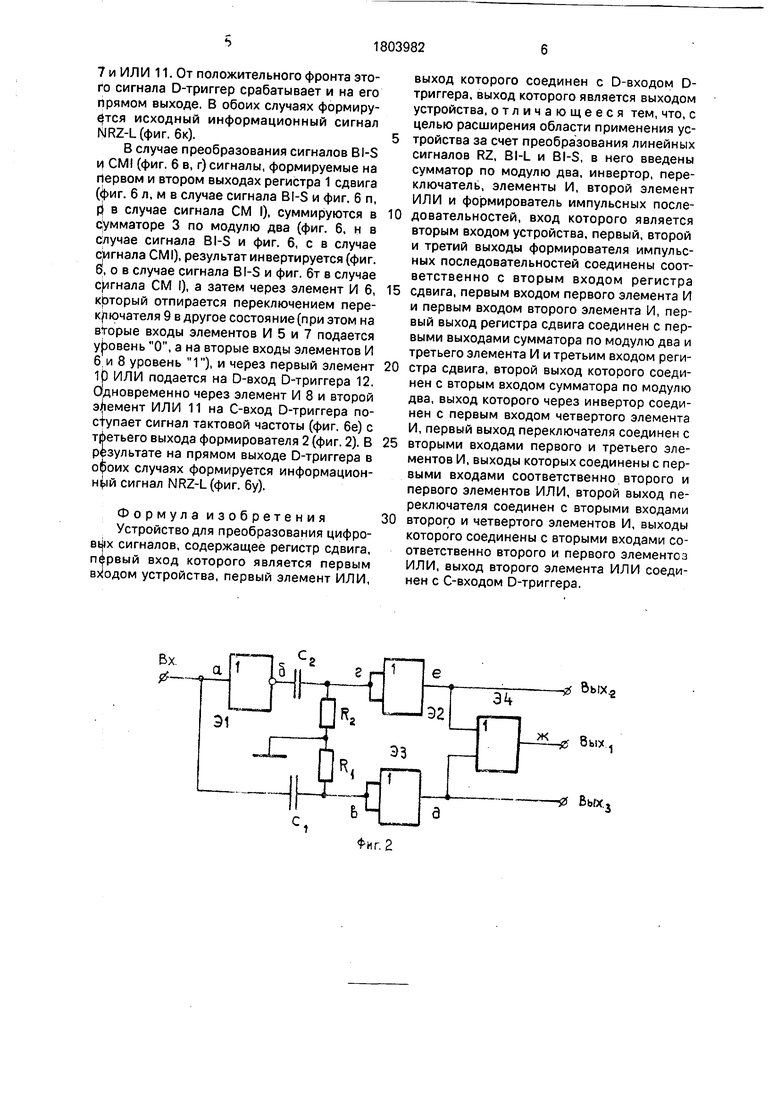

УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ (57) Изобретение относится к технике электросвязи и может быть использовано для преобразования цифровых сигналов линейного тракта при передаче информации по волоконно-оптическому кабелю в цифровой информационный сигнал. Цель изобретения - расширение области применения устройства за счет преобразования не только сигнала CMI, но и линейных сигналов RZ, BI-L и BI-S. Устройство для преобразования цифровых сигналов содержит регистр 1 сдвига, формирователь 2 импульсных последовательностей, сумматор 3 по модулю два, инвертор 4, элементы И 5-8, переключатель 9, элементы ИЛИ 10, 11, D-триггер 12. бил.

Авторы

Даты

1993-03-23—Публикация

1991-02-20—Подача