00

ф ч

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств для телевизионных систем анализа изображений.

Целью изобретения является устранение потерь информации при записи

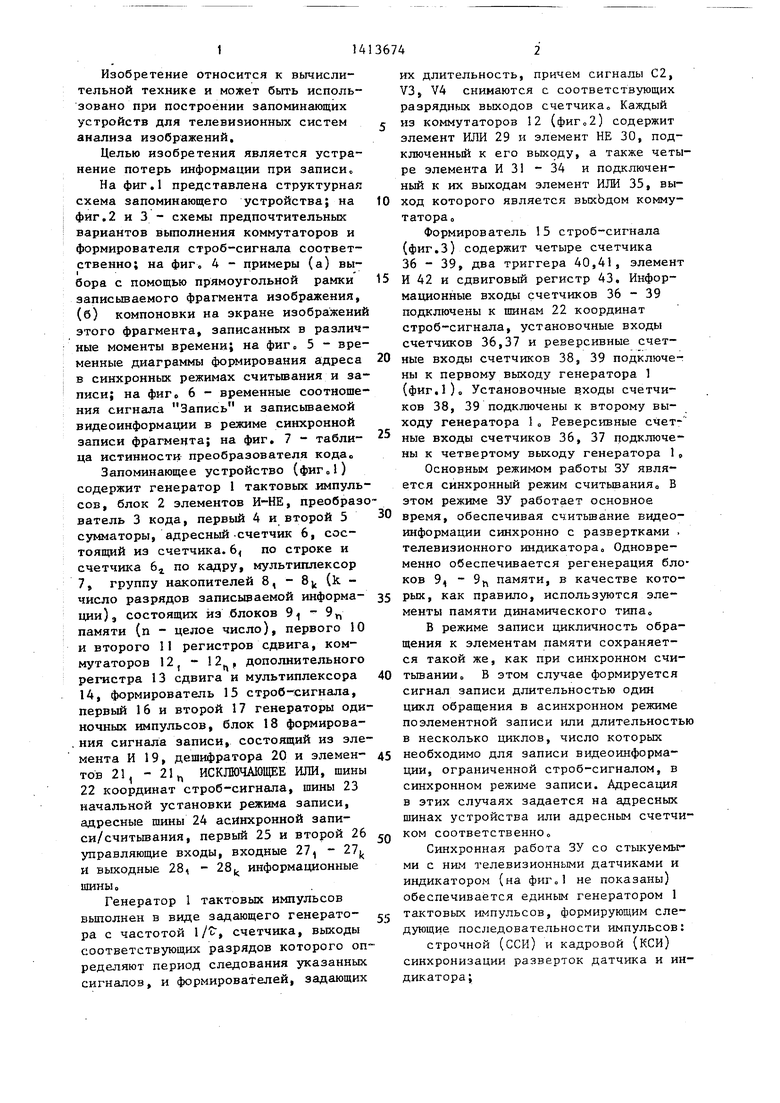

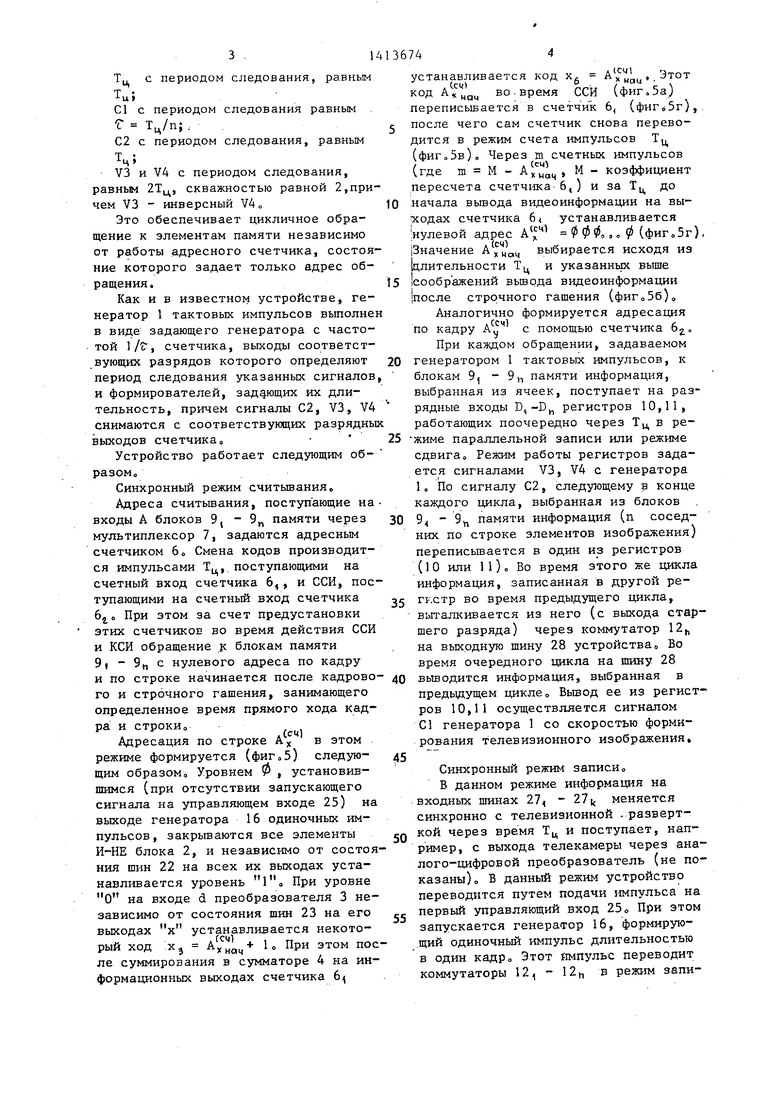

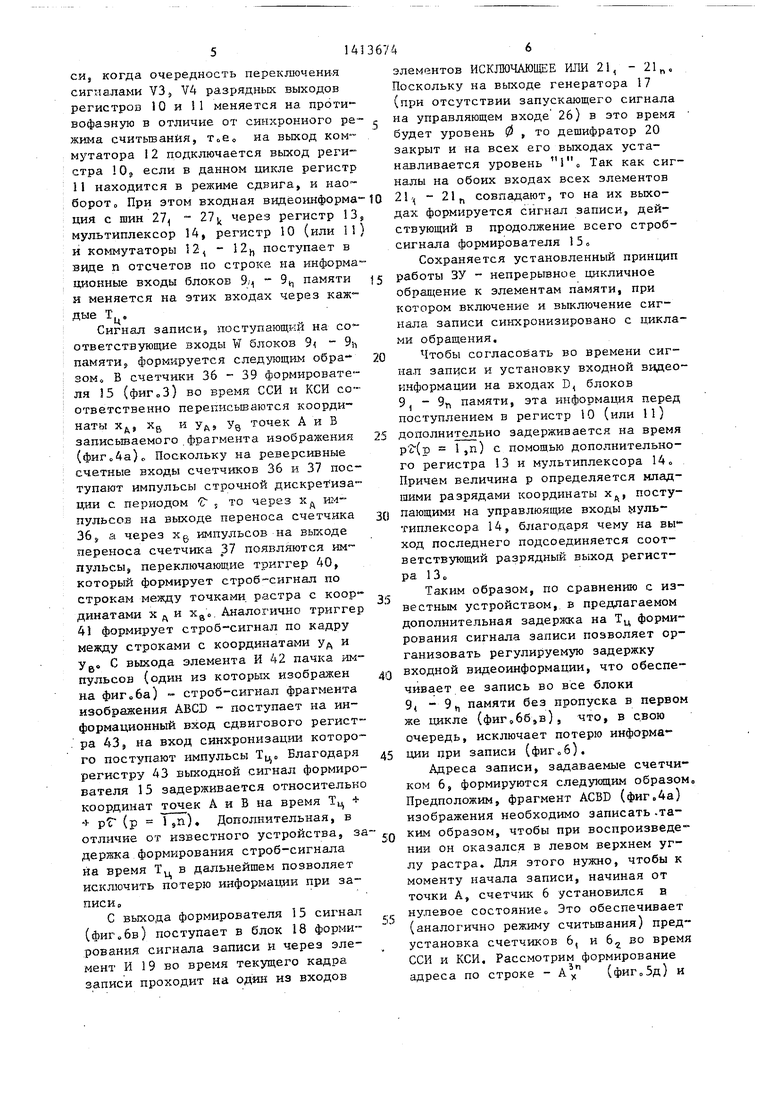

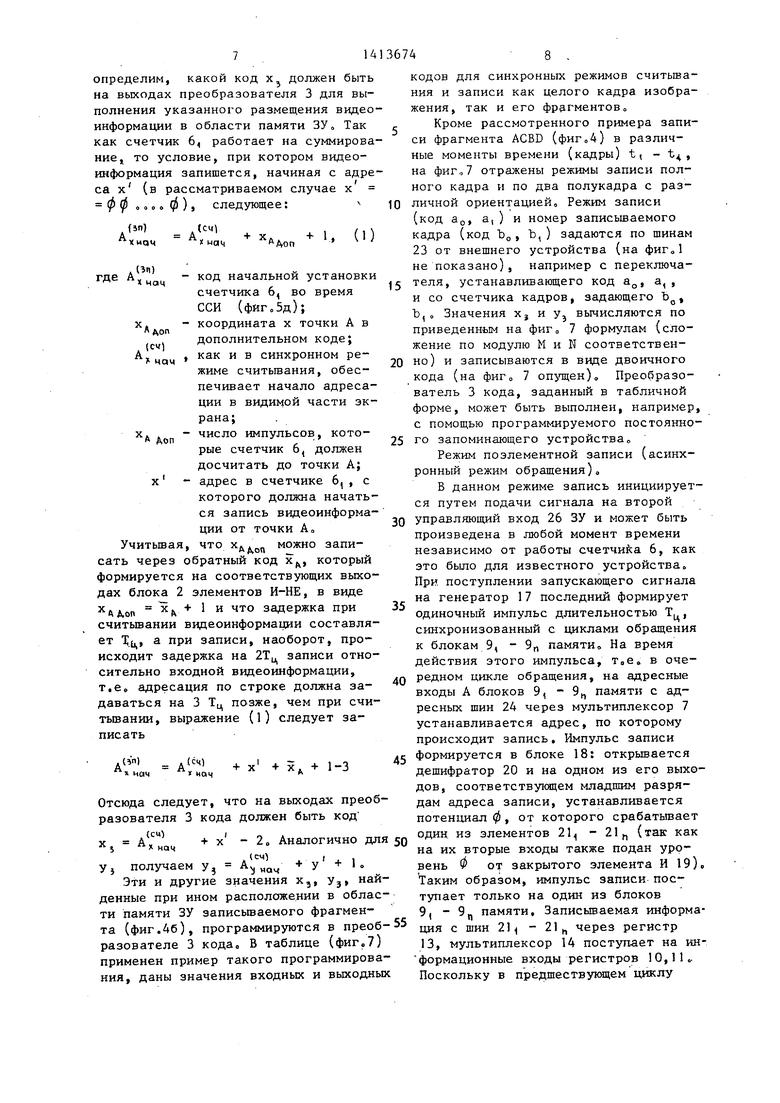

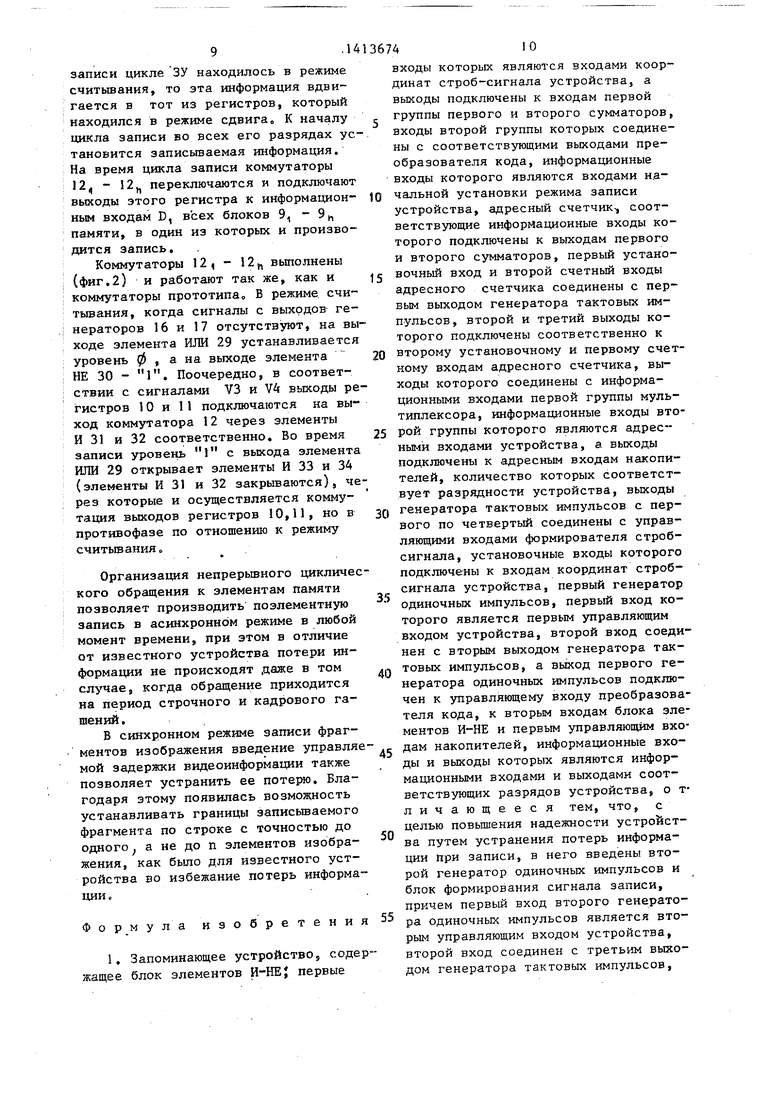

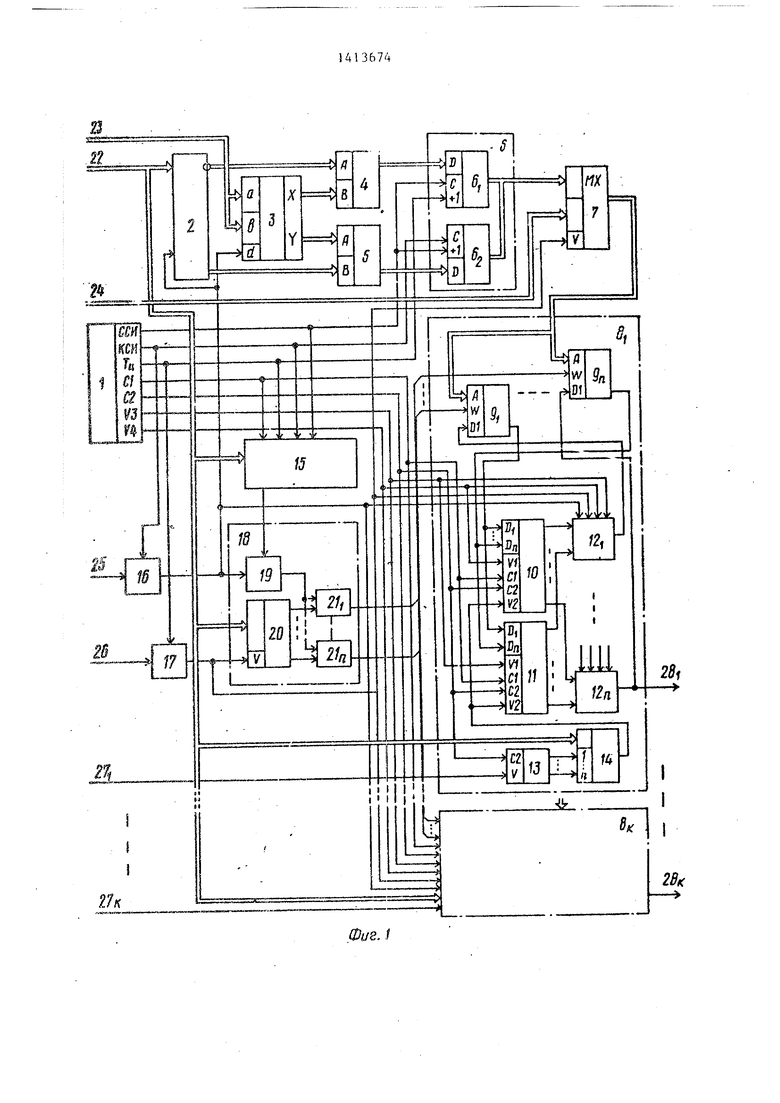

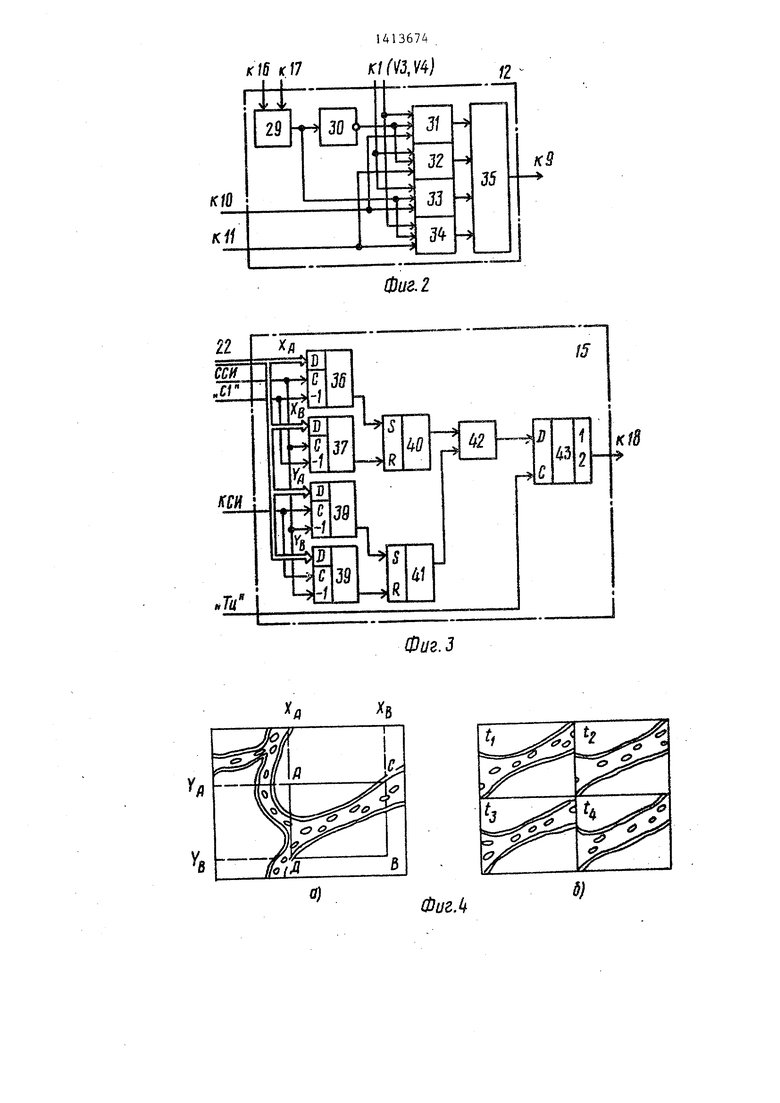

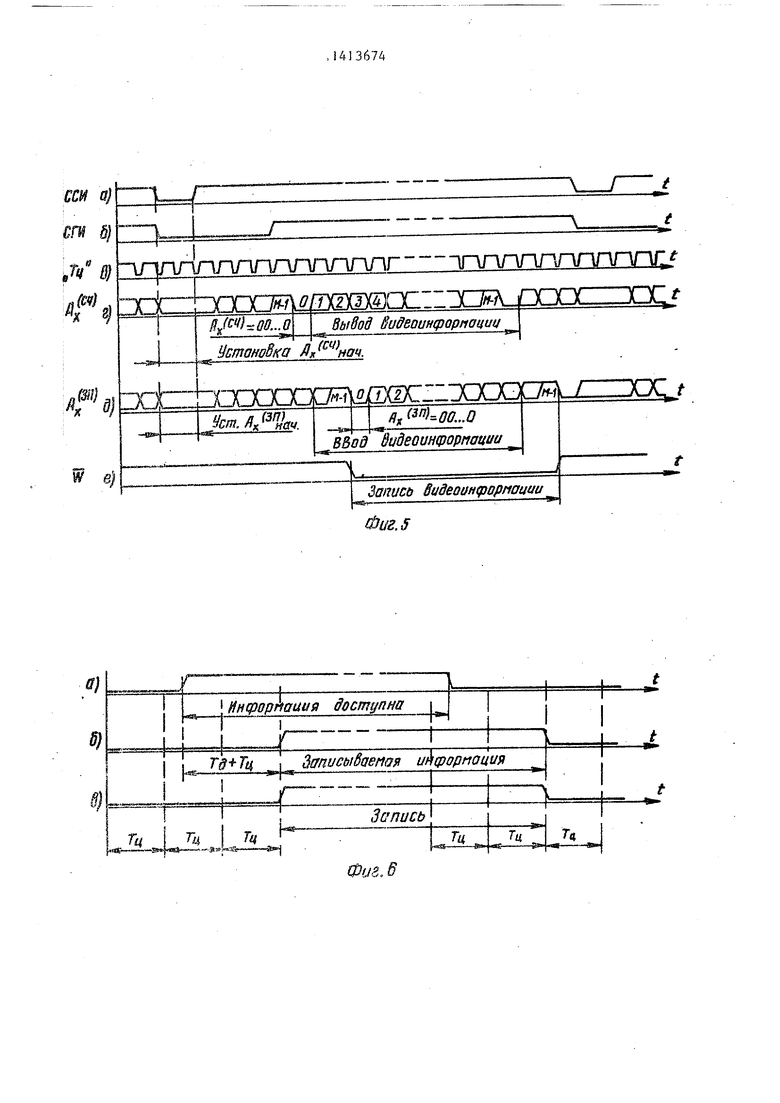

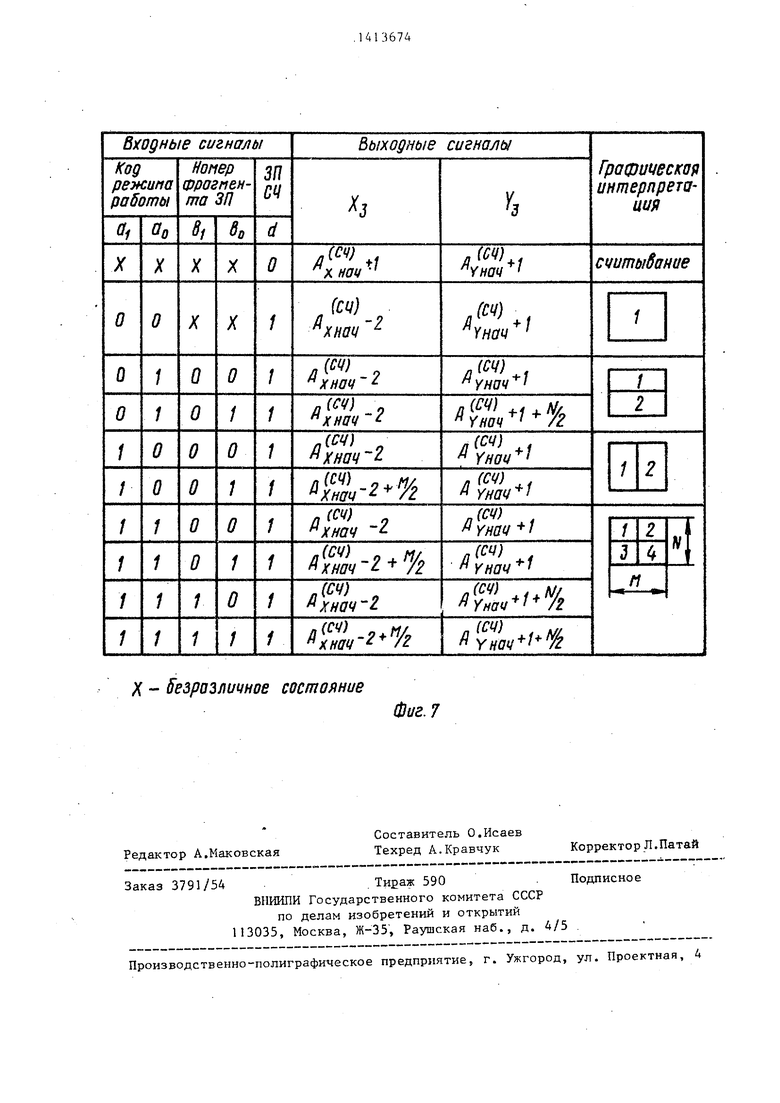

На фиг.1 представлена структурная схема запоминающего устройства; на фиг.2 и 3 - схемы предпочтительных вариантов вьтолиения коммутаторов и формирователя строб-сигнала соответственно; на фиг о 4 - примеры (а) выбора с помощью прямоугольной рамки записьшаемого фрагмента изображения, (б) компоновки на экране изображений этого фрагмента, записанных в различные моменты времени; на фиг 5 - временные диаграммы формирования адреса в синхронных режимах считьшания и записи; на фиг о 6 - временные соотношения сигнала Запись и записьшаемой видеоинформации в режиме синхронной записи фрагмента; на фиг, 7 - таблица истинности преобразователя кодао

Запоминающее устройство (фиго) содержит генератор 1 тактовых импульсов, блок 2 элементов И-НЕ, преобразо ватель 3 кода, первый 4 и второй 5 сумматоры, адресный-счетчик 6, состоящий из счетчика.6 по строке и счетчика 6 по кадру, мультиплексор 7, группу накопителей 8, - 8jj (k - число разрядов записываемой информации)., состоящих из блоков 9 - 9„ памяти (п - целое число), первого 10 и второго 11 регистров сдвига, коммутаторов 12, - 12, дополнительного регистра 13 сдвига и мультиплексора 14, формирователь 15 строб-сигнала, первый 16 и второй 17 генераторы одиночных импульсов, блок 18 формирования сигнала записи, состоящий из элемента И 19, дешифратора 20 и элементов 21, - 21 ИСКЛЮЧАЮЩЕЕ ИЛИ, шины 22 координат строб-сигнала, шины 23 начальной установки режима записи, адресные шины 24 асинхронной запи- си/считьшания, первый 25 и второй 26 управляющие входы, входные 27 - 27, и выходные 28, - 28 информационные ишны о

Генератор 1 тактовых импульсов выполнен в виде задающего генератора с частотой 1/, счетчика, выходы соответствующих разрядов которого определяют период следования указанных сигналов, и формирователей, задающих

их длительность, причем сигналы С2, УЗ, V4 снимаются с соответствующих разрядных выходов счетчика Каждый 5 из коммутаторов 12 () содержит элемент ИЛИ 29 и элемент НЕ 30, подключенный к его выходу, а также четыре элемента И 31 - 34 и подключенный к их выходам элемент ИЛИ 35, вы0 ход которого является выхЬдом коммутатора

Формирователь 15 строб-сигнала (фиг,З) содержит четыре счетчика 36 - 39, два триггера 40,41, элемент

5 И 42 и сдвиговый регистр 43, Информационные входы счетчиков 36-39 подключены к шинам 22 координат строб-сигнала, установочные входы счетчиков 36,37 и реверсивные счет0 ные входы счетчиков 38, 39 подключены к первому выходу генератора 1 (фиг,1)„ Установочные в.ходы счетчиков 38, 39 подключены к второму выходу генератора 1„ Реверсивные счет ные входы счетчиков 36, 37 подключены к четвертому выходу генератора 1, Основным режимом работы ЗУ является синхронный режим считьшанияо В этом режиме ЗУ работает основное

0 время, обеспечивая считьюание видеоинформации синхронно с развертками , телевизионного индикатора. Одновременно обеспечивается регенерация бло- ков 9 - 9f памяти, в качестве кото5 рых, как правило, используются элементы памяти динамического типа

В режиме записи цикличность обращения к элементам памяти сохраняется такой же, как при синхронном счи0 тьшаниио В этом случае формируется сигнал записи длительностью один цикл обращения в асинхронном режиме поэлементной записи или длительностью в несколько циклов, число которых

5 необходимо для записи видеоинформации, ограниченной строб-сигналом, в синхронном режиме записи. Адресация в этих случаях задается на адресных шинах устройства или адресным счетчи

ком соответственно.

Синхронная работа ЗУ со стыкуемыми с ним телевизионными датчиками и индикатором {на фиг,1 не показаны) обеспечивается единыьг генератором 1 тактовых импульсов, формирующим следующие последовательности импульсов:

строчной (ССИ) и кадровой (КСИ) синхронизации разверток датчика и индикатора;

Тц с периодом следования, равным

ц

С1

Т,

с периодом следования равным

ц/п; ..

С2 с периодом следования, равным

Тц;

V3 и V4 с периодом следования, равным 2Тц, скважностью равной 2,причем V3 инверсный V4о

Это обеспечивает цикличное обращение к элементам памяти независимо от работы адресного счетчика, состояние которого задает только адрес обращения.

Как и в известном устройстве, генератор 1 тактовых импульсов выполне в виде задающего генератора с частотой Izt счетчика, выходы соответствующих разрядов которого определяют период следования указанных сигналов и формирователей, задающих их длительность, причем сигналы С2, V3, V4 снимаются с соответствующих разрядны выходов счетчика о

Устройство работает следующим об- разом

Синхронный режим считывания

Адреса считьшания, поступающие на входы А блоков 9, 9 памяти через мультиплексор 7, задаются адресным счетчиком 6о Смена кодов производится импульсами Тц, поступающими на счетный вход счетчика 6,, и ССИ, поступающими на счетный вход счетчика 6jt, При этом за счет предустановки этих счетчиков во время действия ССИ и КСИ обращение JK блокам памяти 9t - 9„ с нулевого адреса по кадру и по строке начинается после кадрового и строчного гашения, занимающего определенное время прямого хода кадра и строкио

Адресация по строке А в этом режиме формируется () следующим образом. Уровнем 0 , установившимся (при отсутствии запускающего сигнала на управляющем входе 25) на выходе генератора 16 одиночных импульсов , закрываются все элементы И-НЕ блока 2, и независимо от состояния шин 22 на всех их выходах устанавливается уровень При уровне о на входе d преобразователя 3 независимо от состояния шин 23 на его выходах х устанавливается некоторый ход Xj lo При этом после суммирования в сумматоре А на информационных выходах счетчика 6

0

0

устанавливается код Xg

X наи

Этот

код во. время ССИ (фиг«5а) переписьшается в счетчик 6, (фиГоЗг), после чего сам счетчик снова переводится в режим счета импульсов Тц (фиГоЗв), Через m счетных импульсов (где m М - , М - коэффициент пересчета счетчика 6,) и за Тц до начала вывода видеоинформации на выходах счетчика 6 устанавливается нулевой адрес 0 0 0,,« (фиг,5г),

(Значение А

Сеч)

,X Нач

длительности Т

выбирается исходя иэ

5

0

и указанньрс выше соображений вывода видеоинформации |после строчного гашения (фиго5б)о

Аналогично формируется адресап я по кадру Р с помощью счетчика Sg.

При каждом обращении, задаваемом генератором 1 тактовых импульсов, к блокам 9, - 9,т памяти информация, выбранная из ячеек, поступает на разрядные входы регистров 10,11, работающих поочередно через Тц в ре5 жиме параллельной записи или режиме сдвига Режим работы регистров задается сигналами V3, V4 с генератора 1. По сигналу С2, следующему в конце каждого цикла, выбранная из блоков 9 9 памяти информация (п соседних по строке элементов изображения) переписьшается в один из регистров (10 или П)о Во время этого же цикла информация, записанная в другой ре- гкстр во время предыдущего цикла, выталкивается из него (с выхода старшего разряда) через коммутатор 12,, на выходную шину 28 устройства Во время очередного цикла на шину 28 вьшодится информация, выбранная в предыдущем цикле Вывод ее из регистров 10,11 осзпдествляется сигналом С1 генератора 1 со скоростью формирования телевизионного изображения.

Синхронный режим записи В данном режиме информация на входных шинах 27, - 21 меняется синхронно с телевизионной -разверткой через время Тц и поступает, например, с выхода телекамеры через аналого-цифровой преобразователь (не показаны) В данный режим устройство переводится путем подачи импульса на первый управляющий вход 25 При этом запускается генератор 16, формирую- .щий одиночный импульс длительностью в один кадр Этот импульс переводит коммутаторы 12, - 12 в режим записи, когда очередность переключения сигналами V3j V4 разрядных выходов регистров 10 и И меняется на противофазную в отличие от синхронного режима считьюанйя, Tt,e, на выход коммутатора 12 подключается выход регистра lOj если в данном цикле регистр 11 находится в режиме сдвига, и нао- борот о При этом входная видео1шформа ция с шин 27 - 27jj через регистр 13, мультиплексор 14, регистр 10 (или 11) и коммутаторы 12 - 12, поступает в виде п отсчетов по строке на информационные входы блоков

9м памяти

и меняется на этих входах через каж дые Т,

Сигнал записи5 поступающий на со ответствующие входы блоков 9i - 9-п памяти5 формируется следующим образом, В счетчики 36 - 39 формирователя 15 (фиГоЗ) во время ССИ и КСЙ соответственно переписьшаются координаты X

А

И Уд, Уд точек А и В

записьюаемого фрагмента изображения (фиГо4а)о Поскольку на реверсивные счетные входы счетчиков 36 и 37 поступают импульсы строчной дискретизации с. периодом с 5 то через Хд и2-1- пульсов на выходе переноса счетчика 36, а через Xg импульсов на выходе переноса счетчика 37 появляются импульсы, переключающие триггер 40, который формирует строб-сигнал по строкам между точками, растра с координатами X и Xgo. Аналогично триггер 41 формирует строб сигнал по кадру между строками с координатами Уд и Уцо С выхода элемента И 42 пачка импульсов (один из которых изображен на фиг оба) - строб-сигнал фрагмента изображения ABCD поступает на информационный вход сдвигового регистра 43, на вход синхронизации которого поступают импульсы Тц Благодаря регистру 43 выходной сигнал формирователя 15 задерживается относительно координат точек А и В на время Тц (р - 59), Дополнительная, в отличие от известного устройства, задержка ,формирования строб-сигнала на время Тц в дальнейшем позволяет искл очить потерю информации при записи

С выхода формирователя 15 сигнал (фиг.бв) поступает в блок 18 формирования сигнала записи и через элемент И 19 во время текущего кадра записи проходит на одян из входов

элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 21, - 21„, Поскольку на выходе генератора 17 (при отсутствии запускающего сигнала на управляющем входе 26) в это время будет уровень 0 , то дешифратор 20 закрыт и на всех его выходах устанавливается уровень Так как сигналы на обоих входах всех элементов

5

5

0

П

O

21 - 2If, совпадают, то на их выходах формируется сигнал записи, действующий в продолжение всего строб- сигнала формирователя 15

Сохраняется установленный принцип

работы ЗУ - непрерывное цикличное обращение к элементам памяти, при котором включение и выключение сигнала записи сиьгхронизировано с циклами обращения,

0 Чтобы согласовать во времени сигнал записи и установку входной видеоинформации на входах D, блоков 9, - 9г, памяти, эта информация перед поступлением в регистр 10 (или П) дополнительно задерживается на время р ь (р 1 jn) с помощью дополнительного регистра 13 и мультиплексора 14 Причем величина р определяется младшими разрядами координаты х, поступающими на управлюящие входы мультиплексора 14, благодаря чему на выход последнего подсоединяется соответствующий разрядный выход регистра 13„

Таким образом, по сравнению с известным устройством, в предлагаемом дополнительная задержка на Тц формирования сигнала записи позволяет организовать регулируемую задержку входной видеоинформации, что обеспечивает ее запись во все блоки 9( 9 памяти без пропуска в первом же цикле (), что, в свою очередь, исключает потерю информа5 ции при записи (фиГоб).

Адреса записи, задаваемые счетчиком 6, формируются следуюцим образом Предположим, фрагмент ACBD (фиг,4а) изображения необходимо записать .таким образом, чтобы при воспроизведении он оказался в левом верхнем углу растра. Для этого нужно, чтобы к моменту начала записи, начиная от точки А, счетчик 6 установился в нулевое состояние Это обеспечивает (аналогично режиму считывания) пред™ установка счетчиков 6, и 6 во время ССИ и КСИ, Рассмотрим формирование адреса по строке - А () и

определим, какой код х должен быть на выходах преобразователя 3 для выполнения указанного размещения видеоинформации в области памяти ЗУ„ Так как счетчик 6, работает на суммирование, то условие, при котором видеоинформация запишется, начиная с адреса х (в рассматриваемом случае х

, о о о (5), следующее:

(C4V

X нач

+ X

I, (1)

(ЗП)

А доп (сч)

где - код начальной установки

счетчика 6, во время ССИ (фиг,5д); - координата х точки А в

дополнительном коде; , как и в синхронном режиме считьшания, обеспечивает начало адресации в видимой части экрана;

Хд - число импульсов, которые счетчик 6, должен досчитать до точки А; X - адрес в счетчике 6, , с которого должна начаться запись видеоинформации от точки АО Учитьшая, что Хд. можно записать через обратный код х,, который формируется на соответствующих выходах блока 2 элементов И-НЕ, в виде

ft Aon ° задержка при считьюании видеоинформации составляет Тц, а при записи, наоборот, происходит задержка на 2Тц записи относительно входной видеоинформации, т,е адресация по строке должна за даваться на 3 Тц позже, чем при считьюании, выражение (1) следует записать

.

) иач X мач

+ X + Х + 1-3

Отсюда следует, что на выходах преобразователя 3 кода должен быть код

Xj Аналогично для 50

у, получаем у, А. „„ + у -i- К

Эти и другие значения х,, УЗ, найденные при ином расположении в области памяти ЗУ записьшаемого фрагмента (фиг.Аб), программируются в преоб-55 разователе 3 кода В таблице (фиг«7) применен пример такого программирования, даны значения входных и вькодных

ю

20

3530

40

45

50

-55х

кодов для синхронных режимов считьшания и записи как целого кадра изображения, так и его фрагментов

Кроме рассмотренного примера записи фрагмента ACBD (фиго4) в различные моменты времени (кадры) t, - t, на фиго 7 отражены режимы записи полного кадра и по два полукадра с различной ориентацией. Режим записи (код ао, а,) и номер записьшаемого кадра (код Ъ, Ъ,) задаются по шинам 23 от внешнего устройства (на фиг не показано), например с переключателя, устанавливающего код а, а,, и со счетчика кадров, задающего Ъ, Ъ,, Значения Xj и у вычисляются по приведенным на фиг„ 7 формулам (сложение по модулю М и N соответственно) и записываются в виде двоичного кода (на фиг 7 ). Преобразователь 3 кода, заданный в табличной форме, может быть выполнен, например, с помощью программируемого постоянного запоминающего устройства

Режим поэлементной записи (асинхронный режим обращения)

Б данном режиме запись инициируется путем подачи сигнала на второй управляющий вход 26 ЗУ и может быть произведена в любой момент времени независимо от работы счетчийа 6, как это было для известного устройства При. поступлении запускающего сигнала на генератор 17 последний формирует одиночный импульс длительностью Т|, синхронизованный с циклами обращения к блокам 9, - 9 памяти. На время действия этого импульса, Тое. в очередном цикле обращения, на адресные входы А блоков 9, 9 памяти с адресных шин 24 через мультиплексор 7 устанавливается адрес, по которому происходит запись, Импульс записи формируется в блоке 18: открывается дешифратор 20 и на одном из его выходов, соответствукяцем младшее разрядам адреса записи, устанавливается потенциал 0, от которого срабатывает один из элементов 21 21,, (так как на их вторые входы также подан уровень Ф о у закрытого элемента И 19) аким образом, импульс записи поступает только на один из блоков 9, 9 памяти, Записьгоаемая информация с шин 21 21 , через регистр 13, мультиплексор 14 поступает на ин- формационные входы регистров 10,1 К Поскольку в предшествующем циклу

9,1

записи цикле ЗУ находилось в режиме считьшания, то эта информация вдвигается в тот из регистров, который находился в режиме сдвигао К началу цикла записи во всех его разрядах установится эаписьшаемая информация. На время цикла записи коммутаторы 12 - 12 переключаются и подключают выходы этого регистра к информационным входам D, всех блоков 9, 9, памяти, в один из которых и производится запись,

Коммутаторы 12, - 12 выполнены (фиг.2) и работают так же, как и коммутаторы прототипа, В режиме счи тывания, когда сигналы с выходов генераторов 16 и 17 отсутствуют, на выходе элемента ИЛИ 29 устанавливается уровень 0 , а на выходе элемента НЕ 30 - 1. Поочередно, в соответствии с сигналами V3 и V4 выходы регистров 10 и 11 подключаются на выход коммутатора 12 через элементы И 31 и 32 соответственно. Во время записи уровень 1 с выхода элемента ИЛИ 29 открывает элементы И 33 и 34 (элементы И 31 и 32 закрываются), через которые и осуществляется коммутация выходов регистров 10,11, но в противофазе по отношению к режиму считывания о

Организация непрерывного циклического обращения к элементам памяти позволяет производить поэлементную запись в асинхронном режиме в любой момент времени, при этом в отличие от известного устройства потери информации не происходят даже в том случае, когда обращение приходится на период строчного и кадрового гашений .

В синхронном режиме записи фрагментов изображения введение управляемой задержки видеоинформации также позволяет устранить ее потеряо. Благодаря этому появилась возможность устанавливать границы записьгоаемого фрагмента по строке с точностью до одного а не до п элементов изображения, как было для известного устройства во избежание потерь информации

Формула изобретения

1. Запоминающее устройство, содержащее блок элементов И-HEJ первые

13674

10

0

5

0

5

0

5

0

5

0

5

входы которых являются входами координат строб-сигнала устройства, а выходы подключены к входам первой группы первого и второго сумматоров, входы второй группы которых соединены с соответствующими выходами преобразователя кода, информационные входы которого являются входами начальной установки режима записи устройства, адресный счетчик-, соответствующие информационные входы которого подключены к выходам первого и второго сумматоров, первый установочный вход и второй счетный входы адресного счетчика соединены с первым выходом генератора тактовых импульсов, второй и третий выходы которого подключены соответственно к второму установочному и первому счетному входам адресного счетчика, выходы которого соединены с информационными входами первой группы мультиплексора, информационные входы второй группы которого являются адресными входами устройства, а выходы подключены к адресным входам наикопи- телей, количество которых соответствует разрядности устройства, выходы генератора тактовых импульсов с первого по четвертый соединены с управляющими входами формирователя строб- сигнала, установочные входы которого подключены к входам координат строб- сигнала устройства, первый генератор одиночньк импульсов, первый вход которого является первым управляющим входом устройства, второй вход соеди ней с вторым выходом генератора тактовых импульсов, а выход первого генератора одиночных импульсов подключен к управляющему входу преобразователя кода, к вторым входам блока элементов И-НЕ и первым управляющим входам накопителей, информационные входы и выходы которых являются информационными входами и выходами соответствующих разрядов устройства, о т- личающееся тем, что, с целью повышения надежности устройства путем устранения потерь информации при записи, в него введены второй генератор одиночных импульсов и блок формирования сигнала записи, причем первый вход второго генератора одиночных импульсов является вторым управляющим входом устройства, второй вход соединен с третьим выходом генератора тактовьк импульсов,

а выход второго генератора одиночных импульсов подключен к вторым управляющим входам накопителей и к первому входу блока формирования сигнала записи, второй и третий входы которого соединены соответственно с выходами первого генератора одиночных импульсов и формирователя строб-сигнала, выходы блока формирования сиг- капа записи подключены к входам записи накопителей, управляющие входы с третьего по шестой которых соединены с выходами с четвертого по седьмой генератора тактовых импульсов соответственно, установочные входы накопителей подключены к входам координат строб-сигнала устройства, управляющий вход мультиплексора соединен с выходом второго генератора оди ночных импульсов, входы группы блока формирования сигнала записи подключены к входам координат строб-сигнала устройствао I ., .

2, Устройство по п.1, отличающееся тем, что каждый из накопителей содержит группу блоков памяти, первый, второй и третий регистры сдвига, группу коммутаторов и мультиплексор, причем адресные входы и входы записи блоков памяти подключены к одноименным входам накопителя, выходы блоков памяти - к соответствую- щим информационным вход1ам первого и второго регистров сдвига, одноименные выходы которых соединены с первым и вторым информационными входами соответствующих коммутаторов, выходы которых подключены к информационным входам соответствующих блоков памяти первые синхррвходы первого и вторрго регистров сдвига соединены с шестым

управляющим входом накопителя, вторые синхровходы первого и второго регистров сдвига и синхровход третьего регистра сдвига подключены к пятому управляющему входу накопителя, первые управляющие входы первого и второго регистров сдвига соединены с третьим и четвертым управляющими входами накопителя соответственно, вторые управляющие входы первого и второго регистров сдвига подключены к выходу мультиплексора, управляющие входы которого соединены с установочными входами накопителя, а информационные входы подключены к выходам третьего регистра сдвига, управляющий вход которого соединен с информационным входом накопителя,управляющие входы коммутаторов подключены к управляющим входам накопителя с первого по четвертьш, выход одного из коммутаторов подключен к выходу накопителя,

Зо Устройство ПОП,1, о ТЛИ

чающееся тем, что блок формирования сигнала записи содержит элемент И, дешифратор и группу элементов ИСКЛЮЧАЮЩЕЕ ИЖ, причем первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к выходу элемента И, входы которого соединены с вторым и третьим входами блока формирования сигнала записи, вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к соответствующим выходам дешифратора, информационные входы и управляющий вход которого . соединены с входами группы и первым управляющим входом блока формирования сигнала записи соответственно, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к выходам блока формирования сигнала записи.

Фи. ,f

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1259336A2 |

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| Телевизионный пеленгатор | 1989 |

|

SU1670805A1 |

| Контурная система программного управления | 1989 |

|

SU1681298A1 |

| Имитатор для тестирования компонентов моноканальной локальной вычислительной сети | 1987 |

|

SU1446621A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

| Тренажер для выработки координарно-моторного рефлекса | 1983 |

|

SU1168199A1 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

| Устройство для ввода измерительной информации | 1986 |

|

SU1354179A1 |

| Устройство для вывода графической информации | 1990 |

|

SU1833858A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств для телевизионных систем анализа изображений. Целью изобретения является устранение потерь информации при записи. Устройство содержит генератор тактовых импульсов. блок элементов И-НЕ, преобразователь кода, первый и второй сумматоры, адресный счетчик, адресный блок, группу накопителей по числу разрядов записьшаемой информации, формирователь строб-сигнала, первый и второй генераторы одиночных импульсов, блок формирования сигнала записи. В устройстве обращение к элементам памяти происходит непрерывно в течение всего кадра от генератора тактовых импульсов и не зависит от режима работы счетчика адреса считывания, что исключает потери информации при записи в асинхронном режиме, даже если обращение приходится на момент строчного гашения, когда указанный счетчик не считает. Благодаря управляемой задержке записываемой видеоинформации эта информация начинает поступать в буфер строго с началом цикла обращения, что исключает ее потерю в синхронном режиме записи фрагмента изображения. 2 в,п. ф-лы, 7. ил. о S (Л

Уп УВ -ФигЛ

Ннфорпааий доступна

I j аписыб1зе 1ая иг форпация 1

.

Запись

т Гц

Э1)«. яь -;-ан

Фиг. 5

Запись

Ти.

Тц

га,

Физ,6

X - безразличное состояние

Фиг. 7

| Запоминающее устройство | 1983 |

|

SU1116458A1 |

| Запоминающее устройство | 1985 |

|

SU1259336A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-07-30—Публикация

1987-01-07—Подача