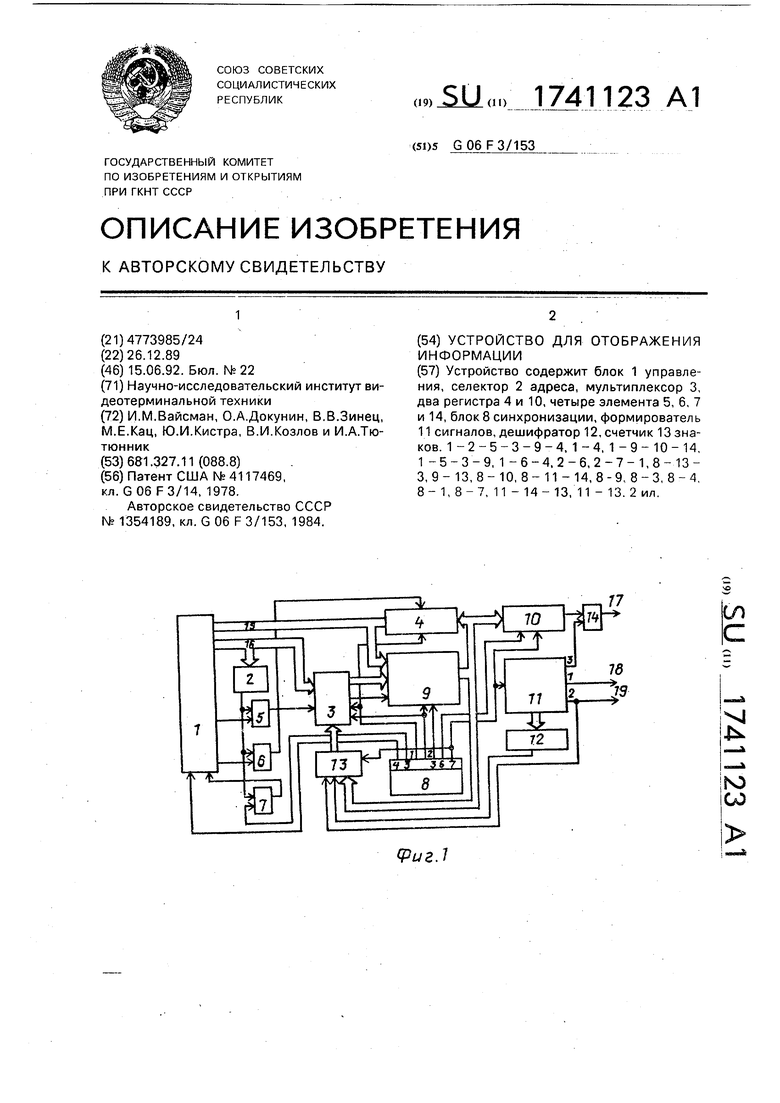

Фиг.1

Изобретение относится к автоматике и вычислительной технике и может быть использовано доя отображения информации на экране электронно-лучевой трубки (ЭЛТ) в системах обработки данных, управляемых микропроцессором, в частности в видеотерминалах, дисплеях, персональных ЭВМ.

Цель изобретения - повышение быстродействия устройства.

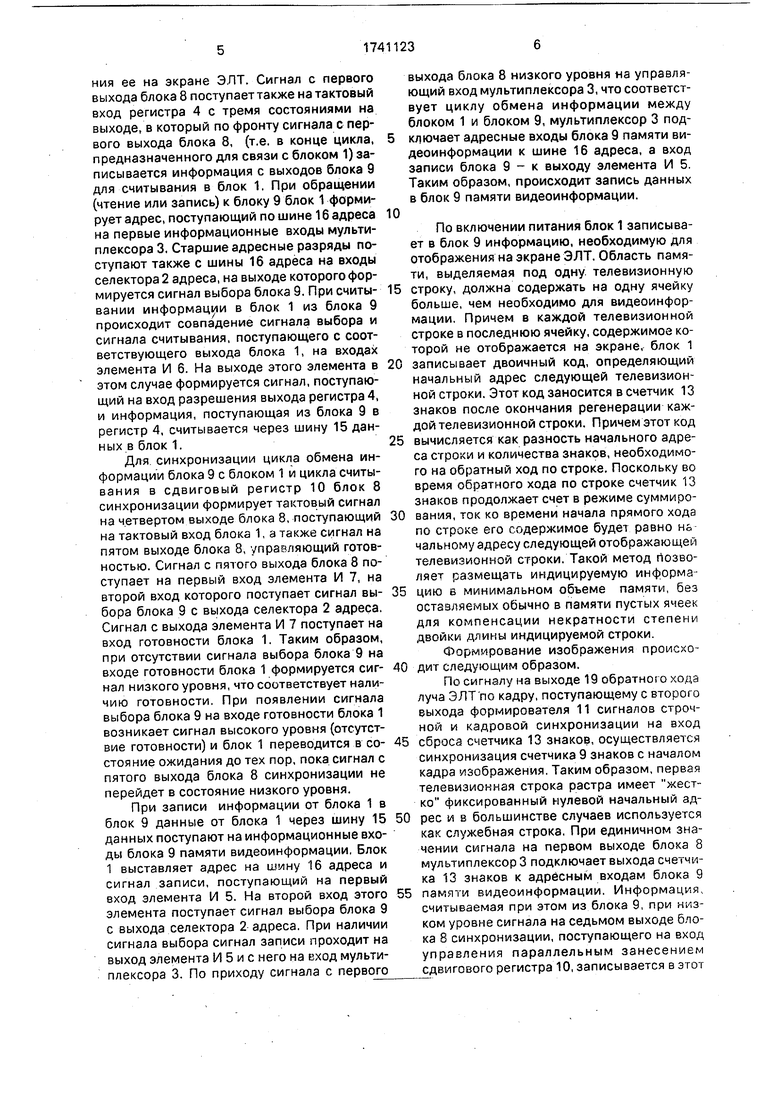

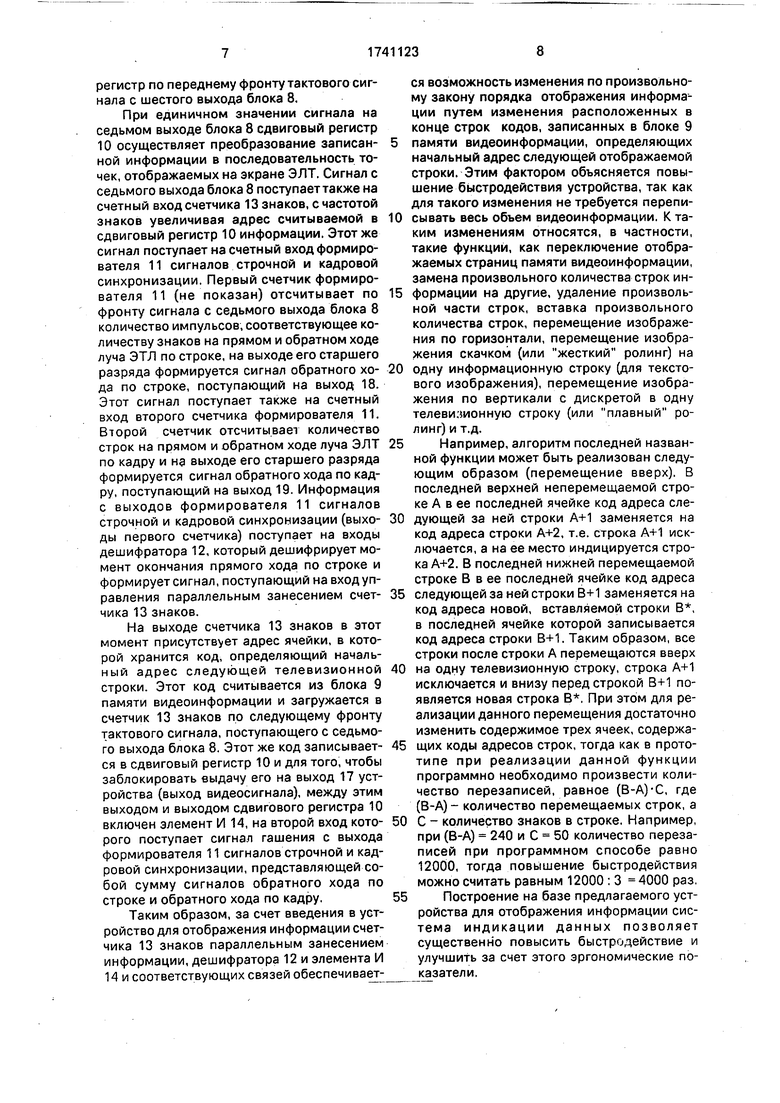

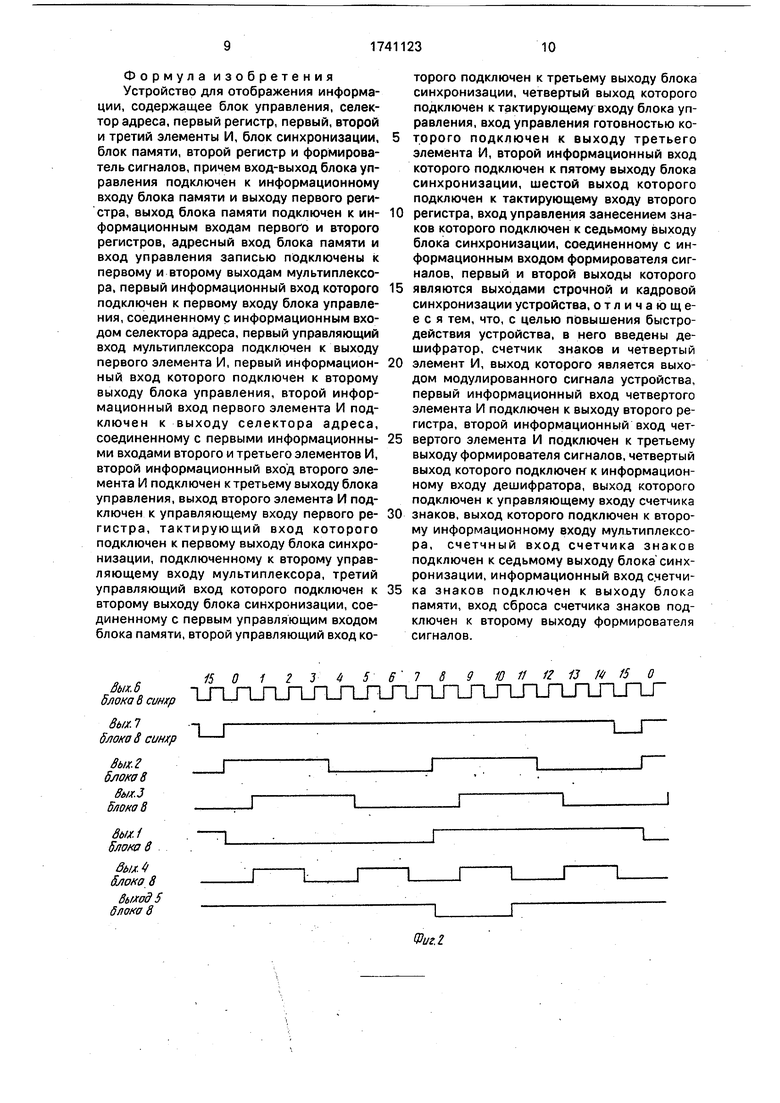

Нафиг.1 представлена структурная схе- ма устройства для отображения информации; на фиг.2 - временные диаграммы его работы.

Устройство содержит блок 1 управления, селектор 2 адреса, мультиплексор 3/ первый регистр 4, первый элемент И 5, второй элемент И 6, третий элемент И 7, блок 8 синхронизации, блок 9 памяти, второй регистр 10, формирователь 11 сигналов, дешифратор 12, счетчик 13 знаков, четвертый элемент И 14. Нафиг.1 изображены шина 15 данных блока 1, шина 16 адреса блока 1, выход 17 устройства, выход 18 строчной развертки, выход 19 кадровой развертки.

Одним из примеров реализации устрой- ства может быть следующее решение.

Первый 5, второй 6, третий 7 и четвертый 14 элементы И - К555ЛИ1; блок 1 - микропроцессор КР1810ВМ86, ПЗУ - К573РФЧА, ОЗУ- КР537РУ8А; мультиплек- сор 3 - КР531КП7; счетчик 13 знаков с параллельным занесением - К555ИЕ10; блок 8 синхронизации - интегральные микросхемы серий КР531; КМ 1556; блок 9 памяти видеоинформации - КР565РУ5В; первый регистр 4 с тремя состояниями на выходе - К555ИР23, второй регистр 10 сдвиговый - К555ИР10; формирователь 11 сигналов строчной и кадровой синхронизации - интегральные микросхемы серий К555, КМ 1556; дешифратор 12 и селектор 2 адреса - К555ИД4.

Блок 8 сихронизации в простейшем случае может быть выполнен в виде генератора, двоичного счетчика-делителя и программируемой логической матрицы. Генератор формирует импульсы с частотой точек, поступающие на вход счетчика-делителя. Выходы счетчика-делителя подключены к программируемой логической матрице, в которой прошиты логические функции всех выходов блока 8 синхронизации (кроме шестого выхода блока 8 синхронизации, который является выходом тактового генератора) в соответствии с фиг.2.

Формирователь 11 сигналов строчной и кадровой синхронизации может быть выполнен на двух счетчиках со сбросом (не показаны). На первый счетчик поступает сигнал с частотой знаков с седьмого выхода

блока 8 синхронизации. Этот счетчик отсчитывает количество знаков, соответствующее прямому и обратному ходу луча ЭТЛ по строке, а на выходе его старшего разряда (первый выход 18 формирователя 11) формируется сигнал обратного хода по строке. Второй счетчик отсчитывает количество строк, соответствующее прямому и обратному ходу луча ЭЛТ по кадру, на выходе его старшего разряда (второй выход 19 формирователя 11) формируется сигнал обратного хода по кадру. Сигнал гашения на третьем выходе формирователя 11 сигналов строчной и кадровой синхронизации, поступающий на первый вход элемента 14 И, представляет собой сумму сигналов обратного хода по строке и сигнала обратного хода по кадру.

Устройство работает следующим образом.

Блок 8 синхронизации формирует на втором и третьем выходах сигналы выбора строк (РА) и выбора столбцов (СА) динамической памяти, соответственно поступающие на соответствующие входы блока 9 памяти видеоинформации, с частотой в два раза выше, чем необходимо для поддержания процесса регенерации изображения, Таким образом, цикл обращения к блоку 9 состоит из двух циклов: цикл считывания информации в сдвиговый регистр 10 и цикл передачи или приема информации из (или в) блока 1.

Такое повышение частоты несколько повышает требование к быстродействию блока 9 памяти видеоинформации, но в то же время гарантирует высокое качество изображения, так как процесс обмена информацией с блока 1 не влияет на процесс отображения информации.

Сигнал с второго выхода блока 8 синхронизации поступает также на один из управляющих входов мультиплексора 3. Таким образом, осуществляется мультиплексная передача разрядов адреса для динамической памяти блока 9, при единичном значении сигнала на втором выходе блока 8 передаются разряды выбора строк, при нулевом значении - разряды выбора столбцов. На другой управляющий вход мультиплексора 3 поступает сигнал с первого выхода блока 8 синхронизации. При нулевом значении этого сигнала мультиплексор 3 подключает к адресным входам блока 9 памяти видеоинформации шину 15 адреса от блока 1. При единичном значении сигнала на первом выходе блока 8 мультиплексор 3 подключает к адресным входам блс. э 9 выходы счетчика 13 знаков для считывания информации в сдвиговый регистр 10 и отображения ее на экране Э.ПТ. Сигнал с первого выхода блока 8 посту лает также на тактовый вход регистра 4 с тремя состояниями на выходе, в который по фронту сигнала с первого выхода блока 8, (т.е. в конце цикла, предназначенного для связи с блоком 1) записывается информация с выходов блока 9 для считывания в блок 1. При обращении (чтение или запись) к блоку 9 блок 1 формирует адрес, поступающий по шине 16 адреса на первые информационные входы мультиплексора 3. Старшие адресные разряды поступают также с шины 16 адреса на входы селектора 2 адреса, на выходе которого формируется сигнал выбора блока 9. При считывании информации в блок 1 из блока 9 происходит совпадение сигнала выбора и сигнала считывания, поступающего с соответствующего выхода блока 1, на входах элемента И 6. На выходе этого элемента в этом случае формируется сигнал, поступающий на вход разрешения выхода регистра 4, и информация, поступающая из блока 9 в регистр 4, считывается через шину 15 данных в блок 1.

Для синхронизации цикла обмена информации блока 9 с блоком 1 и цикла считывания в сдвиговый регистр 10 блок 8 синхронизации формирует тактовый сигнал на четвертом выходе блока 8, поступающий на тактовый вход блока 1, а также сигнал на пятом выходе блока 8, управляющий готовностью. Сигнал с пятого выхода блока 8 поступает на первый вход элемента И 7, на второй вход которого поступает сигнал выбора блока 9 с выхода селектора 2 адреса. Сигнал с выхода элемента И 7 поступает на вход готовности блока 1. Таким образом, при отсутствии сигнала выбора блока 9 на входе готовности блока 1 формируется сигнал низкого уровня, что соответствует наличию готовности. При появлении сигнала выбора блока 9 на входе готовности блока 1 возникает сигнал высокого уровня (отсутствие готовности) и блок 1 переводится в состояние ожидания до тех пор, пока сигнал с пятого выхода блока 8 синхронизации не перейдет в состояние низкого уровня.

При записи информации от блока 1 в блок 9 данные от блока 1 через шину 15 данных поступают на информационные входы блока 9 памяти видеоинформации. Блок 1 выставляет адрес на шину 16 адреса и сигнал записи, поступающий на первый вход элемента И 5. На второй вход этого элемента поступает сигнал выбора блока 9 с выхода селектора 2 адреса. При наличии сигнала выбора сигнал записи проходит на выход элемента Ибис него на вход мультиплексора 3. По приходу сигнала с первого

выхода блока 8 низкого уровня на управляющий вход мультиплексора 3, что соответствует циклу обмена информации между блоком 1 и блоком 9, мультиплексор 3 подключает адресные входы блока 9 памяти видеоинформации к шине 16 адреса, а вход записи блока 9 - к выходу элемента И 5. Таким образом, происходит запись данных в блок 9 памяти видеоинформации.

0

По включении питания блок 1 записывает в блок 9 информацию, необходимую для отображения на экране ЭЛТ, Область памяти, выделяемая под одну телевизионную

5 строку, должна содержать на одну ячейку больше, чем необходимо для видеоинформации. Причем в каждой телевизионной строке в последнюю ячейку, содержимое которой не отображается на экране, блок 1

0 записывает двоичный код, определяющий начальный адрес следующей телевизионной строки. Этот код заносится в счетчик 13 знаков после окончания регенерации каждой телевизионной строки. Причем этот код

5 вычисляется как разность начального адреса строки и количества знаков, необходимого на обратный ход по строке. Поскольку во время обратного хода по строке счетчик 13 знаков продолжает счет в режиме суммиро0 вания, ток ко времени начала прямого хода по строке его содержимое будет равно нь чальному адресу следующей отображающей телевизионной строки. Такой метод позволяет размещать индицируемую информз5 цию Б минимальном объеме памяти, без оставляемых обычно в памяти пустых ячеек для компенсации некратности степени двойки длины индицируемой строки.

Формирование изображения происхо0 дит следующим образом.

По сигналу на выходе 19 обратного хода луча ЭЛТ по кадру, поступающему с второго выхода формирователя 11 сигналов строчной и кадровой синхронизации на вход

5 сброса счетчика 13 знаков, осуществляется синхронизация счетчика 9 знаков с началом кадра изображения. Таким образом, первая телевизионная строка растра имеет жестко фиксированный нулевой начальный ад0 рее и в большинстве случаев используется как служебная строка, При единичном значении сигнала на первом выходе блока 8 мультиплексор 3 подключает выхода счетчика 13 знаков к адрбсным входам блока 9

5 памяти видеоинформации. Информация, считываемая при этом из блока 9, при низком уровне сигнала на седьмом выходе блока 8 синхронизации, поступающего на вход управления параллельным занесением сдвигового регистра 10, записывается в этот

регистр по переднему фронту тактового сигнала с шестого выхода блока 8.

При единичном значении сигнала на седьмом выходе блока 8 сдвиговый регистр 10 осуществляет преобразование записанной информации в последовательность точек, отображаемых на экране ЭЛТ. Сигнал с седьмого выхода блока 8 поступает также на счетный вход счетчика 13 знаков, с частотой знаков увеличивая адрес считываемой в сдвиговый регистр 10 информации. Этот же сигнал поступает на счетный вход формирователя 11 сигналов строчной и кадровой синхронизации. Первый счетчик формирователя 11 (не показан) отсчитывает по фронту сигнала с седьмого выхода блока 8 количество импульсов, соответствующее количеству знаков на прямом и обратном ходе луча ЭТЛ по строке, на выходе его старшего разряда формируется сигнал обратного хода по строке, поступающий на выход 18. Этот сигнал поступает также на счетный вход второго счетчика формирователя 11. Второй счетчик отсчитывает количество строк на прямом и обратном ходе луча ЭЛТ по кадру и на выходе его старшего разряда формируется сигнал обратного хода по кадру, поступающий на выход 19. Информация с выходов формирователя 11 сигналов строчной и кадровой синхронизации (выходы первого счетчика) поступает на входы дешифратора 12, который дешифрирует момент окончания прямого хода по строке и формирует сигнал, поступающий на вход управления параллельным занесением счетчика 13 знаков.

На выходе счетчика 13 знаков в этот момент присутствует адрес ячейки, в которой хранится код, определяющий начальный адрес следующей телевизионной строки. Этот код считывается из блока 9 памяти видеоинформации и загружается в счетчик 13 знаков по следующему фронту тактового сигнала, поступающего с седьмого выхода блока 8. Этот же код записывается в сдвиговый регистр 10 и для того, чтобы заблокировать выдачу его на выход 17 устройства (выход видеосигнала), между этим выходом и выходом сдвигового регистра 10 включен элемент И 14, на второй вход которого поступает сигнал гашения с выхода формирователя 11 сигналов строчной и кадровой синхронизации, представляющей собой сумму сигналов обратного хода по строке и обратного хода по кадру.

Таким образом, за счет введения в устройство для отображения информации счетчика 13 знаков параллельным занесением информации, дешифратора 12 и элемента И 14 и соответствующих связей обеспечивается возможность изменения по произвольному закону порядка отображения информации путем изменения расположенных в конце строк кодов, записанных в блоке 9

памяти видеоинформации, определяющих начальный адрес следующей отображаемой строки. Этим фактором объясняется повышение быстродействия устройства, так как для такого изменения не требуется перепи0 сывать весь объем видеоинформации. К таким изменениям относятся, в частности, такие функции, как переключение отображаемых страниц памяти видеоинформации, замена произвольного количества строк ин5 формации на другие, удаление произвольной части строк, вставка произвольного количества строк, перемещение изображения по горизонтали, перемещение изображения скачком (или жесткий ролинг) на

0 одну информационную строку (для текстового изображения), перемещение изображения по вертикали с дискретой в одну телевизионную строку (или плавный ролинг) и т.д.

5 Например, алгоритм последней названной функции может быть реализован следующим образом (перемещение вверх). В последней верхней неперемещаемой строке А в ее последней ячейке код адреса сле0 дующей за ней строки А+1 заменяется на код адреса строки А+2, т.е. строка А+1 исключается, а на ее место индицируется строка А+2. В последней нижней перемещаемой строке В в ее последней ячейке код адреса

5 следующей за ней строки В+1 заменяется на код адреса новой, вставляемой строки В, в последней ячейке которой записывается код адреса строки В+1. Таким образом, все строки после строки А перемещаются вверх

0 на одну телевизионную строку, строка А+1 исключается и внизу перед строкой В+1 появляется новая строка В. При этом для реализации данного перемещения достаточно изменить содержимое трех ячеек, содержа5 щих коды адресов строк, тогда как в прототипе при реализации данной функции программно необходимо произвести количество перезаписей, равное (В-А)-С, где (В-А)- количество перемещаемых строк, а

0 С - количество знаков в строке. Например, при (В-А) 240 и С 50 количество перезаписей при программном способе равно 12000, тогда повышение быстродействия можно считать равным 12000 : 3 4000 раз.

5 Построение на базе предлагаемого устройства для отображения информации система индикации данных позволяет существенно повысить быстродействие и улучшить за счет этого эргономические показатели.

Формула изобретения Устройство для отображения информации, содержащее блок управления, селектор адреса, первый регистр, первый, второй и третий элементы И, блок синхронизации, блок памяти, второй регистр и формирователь сигналов, причем вход-выход блока управления подключен к информационному входу блока памяти и выходу первого регистра, выход блока памяти подключен к ин- формационным входам первого и второго регистров, адресный вход блока памяти и вход управления записью подключены к первому и второму выходам мультиплексора, первый информационный вход которого подключен к первому входу блока управления, соединенному с информационным входом селектора адреса, первый управляющий вход мультиплексора подключен к выходу первого элемента И, первый информацион- ный вход которого подключен к второму выходу блока управления, второй информационный вход первого элемента И подключен к выходу селектора адреса, соединенному с первыми информационны- ми входами второго и третьего элементов И, второй информационный вход второго элемента И подключен к третьему выходу блока управления, выход второго элемента И подключен к управляющему входу первого ре- гистра, тактирующий вход которого подключен к первому выходу блока синхронизации, подключенному к второму управляющему входу мультиплексора, третий управляющий вход которого подключен к второму выходу блока синхронизации, соединенному с первым управляющим входом блока памяти, второй управляющий вход которого подключен к третьему выходу блока синхронизации, четвертый выход которого подключен к тактирующему входу блока управления, вход управления готовностью которого подключен к выходу третьего элемента И, второй информационный вход которого подключен к пятому выходу блока синхронизации, шестой выход которого подключен к тактирующему входу второго регистра, вход управления занесением знаков которого подключен к седьмому выходу блока синхронизации, соединенному с информационным входом формирователя сигналов, первый и второй выходы которого являются выходами строчной и кадровой синхронизации устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены дешифратор, счетчик знаков и четвертый элемент И, выход которого является выходом модулированного сигнала устройства, первый информационный вход четвертого элемента И подключен к выходу второго регистра, второй информационный вход четвертого элемента И подключен к третьему выходу формирователя сигналов, четвертый выход которого подключен к информационному входу дешифратора, выход которого подключен к управляющему входу счетчика знаков, выход которого подключен к второму информационному входу мультиплексора, счетчный вход счетчика знаков подключен к седьмому выходу блока синхронизации, информационный вход сметчика знаков подключен к выходу блока памяти, вход сброса счетчика знаков подключен к второму выходу формирователя сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

| ДИСПЛЕЙ | 1990 |

|

RU2015536C1 |

| Устройство для отображения информации | 1987 |

|

SU1441451A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| Устройство для отображения информации | 1987 |

|

SU1529279A1 |

| Устройство для запоминания и отображения видеоинформации | 1987 |

|

SU1424029A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Устройство для регистрации динамических процессов | 1988 |

|

SU1624437A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162248C2 |

Устройство содержит блок 1 управления, селектор 2 адреса, мультиплексор 3, два регистра 4 и 10, четыре элемента 5, 6, 7 и 14, блок 8 синхронизации, формирователь 11 сигналов, дешифратор 12, счетчик 13 знаков. 1-2-5-3-9-4, 1-4, 1-9-10-14, 1-5-3-9, 1-6-4. 2-6, 2-7-1,8-13- 3,9- 13, 8- 10, 8- 11 -14, 8-9, 8-3, 8-4, 8- 1, 8-7, 11 - 14- 13, 11 - 13. 2 ил.

Вых. 6 блока В синхр

Вых. блокад синхр

Вых. 2

блоков

Вых.З

5локо 8

Вых.1 блока в

Зш4 блока 8

Выход 5 блока 8

15 О

2 3

5 6

Ю 11 12 13 № 15 О

TJlJl rLJl n nj J JHJ JlJ

5 6

Ю 11 12 13 № 15 О

| Патент США № 4117469, к.л | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор случайных двоичных чисел | 1985 |

|

SU1354189A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-06-15—Публикация

1989-12-26—Подача