ключены к выходам соответствующих логических элементов 2И-НЕ, входы .D-триггеров управления - к плюсовой шине источника питания блока управления, первый вход каждого из N логических элементов 2И-НЕ подключен к выходу первого формирователя стробимпульсов, а второй вход логических элементов 2И-НЕ подключен соответственно к выходу первого, второго,..., N-ro разряда универсального N pasрядного регистра сдвига передних фротов импульсов, выход генератора синхроимпульсов подключен к входу делителя частоты и к входам первого, и второго формирователей тактовых импульсов, выход первого формирователя тактовых импульсов подключен к входу первого формирователя стробимпульсов, отличающийся тем, что, с целью улучшения.качества процесса регулирования при больших возмущающих воздействиях, введены согласующий инвертор и два канала синхронизации передних и задних фронтов импульсов, каждый из которых содержит логический элемент 2И-НЕ,

инвертор и дополнительный формирователь строб-импульсов, при этом выход широтно-импульсного модулятора подключен к общей точке соединения первого входа логического элемента 2И-НЕ канала синхронизации передних фронтов импульсов и входа согласующего -инвертора, выход которого подключен к первому входу логического элемента 2И-НЕ канала синхронизации задних фронтов импульсов, выход инвертора канала синхронизации передних фронтов импульсов цодключен к входу третьего формирователя стробимпульсов, а выход инвертора канала синхронизации задних фронтов импульсов - к.входу второго формирователя строб-импульсов, в каждом из.каналов синхронизации вход дополнительного формирователя стр.об-импульсов подключен к точке соединения выхода делителя частоты и входа формирователя пилообразного напряжения, а выход - к второму входу логического элемента 2И-НЕ, выход элемента 2И-НЕ подключен к входу инвертора .

| название | год | авторы | номер документа |

|---|---|---|---|

| Блок управления многофазным импульсным стабилизатором | 1983 |

|

SU1123085A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265743A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265741A1 |

| Многофазный импульсный стабилизатор напряжения | 1983 |

|

SU1156032A1 |

| Многофазный импульсный стабилизатор напряжения | 1990 |

|

SU1700545A1 |

| Многофазный импульсный стабилизатор | 1982 |

|

SU1019413A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1317415A1 |

| Многофазный импульсный стабилизатор напряжения | 1987 |

|

SU1483438A1 |

| Многофазный импульсный стабилизатор | 1982 |

|

SU1070528A1 |

| Блок управления многофазным импульсным стабилизатором напряжения | 1987 |

|

SU1467704A1 |

.

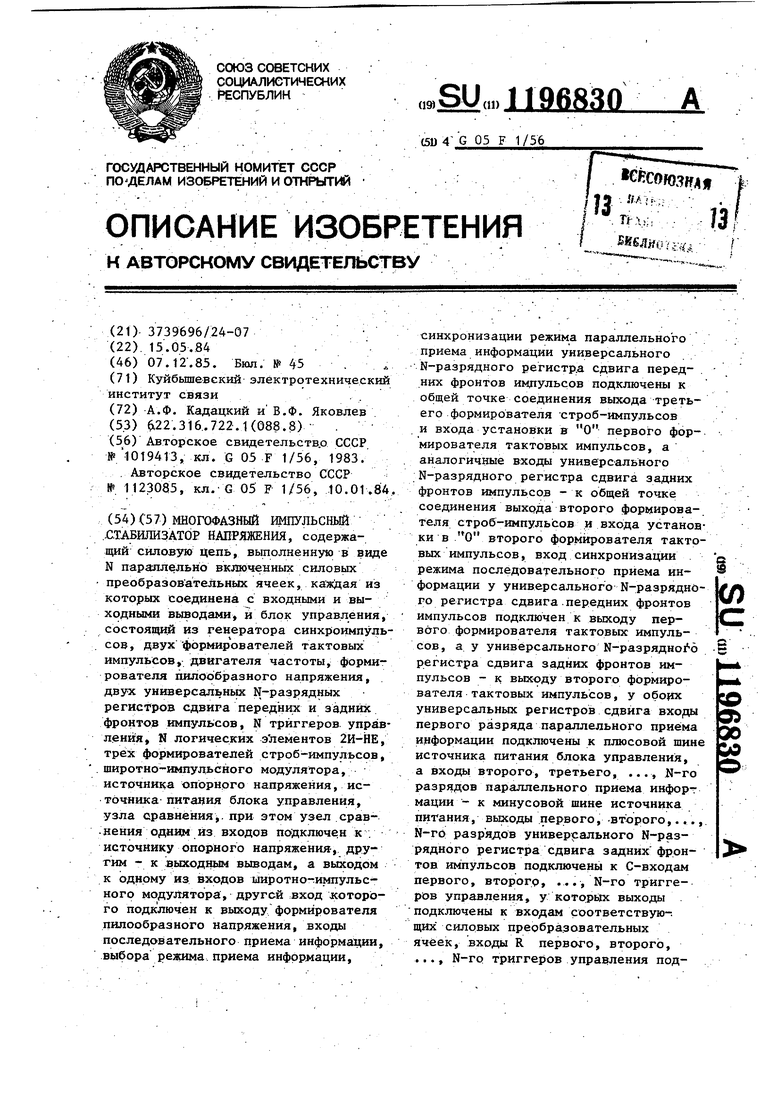

Изобретение относится к электротехнике и может быть использовано в качестве источников электропитания электротехнической и радиоэлектронной аппаратуры различного назначения.

Цель изобретения - улучшение качества процесса регулирования при больших возмущающих воздействиях.

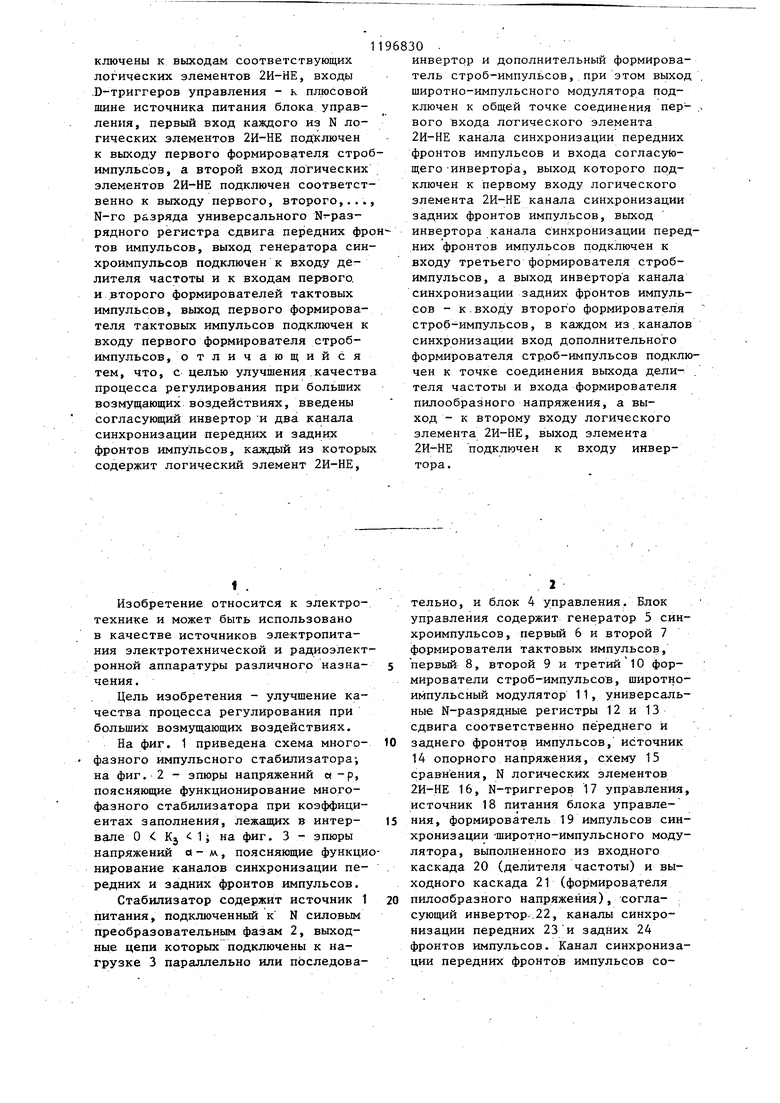

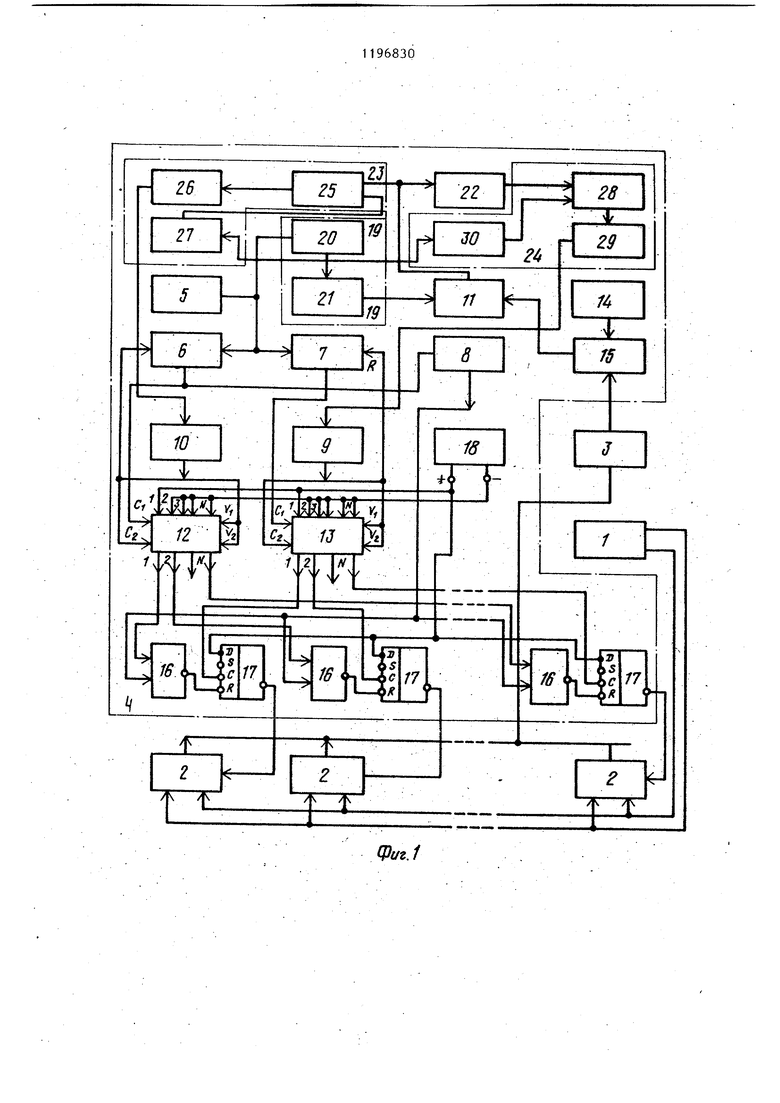

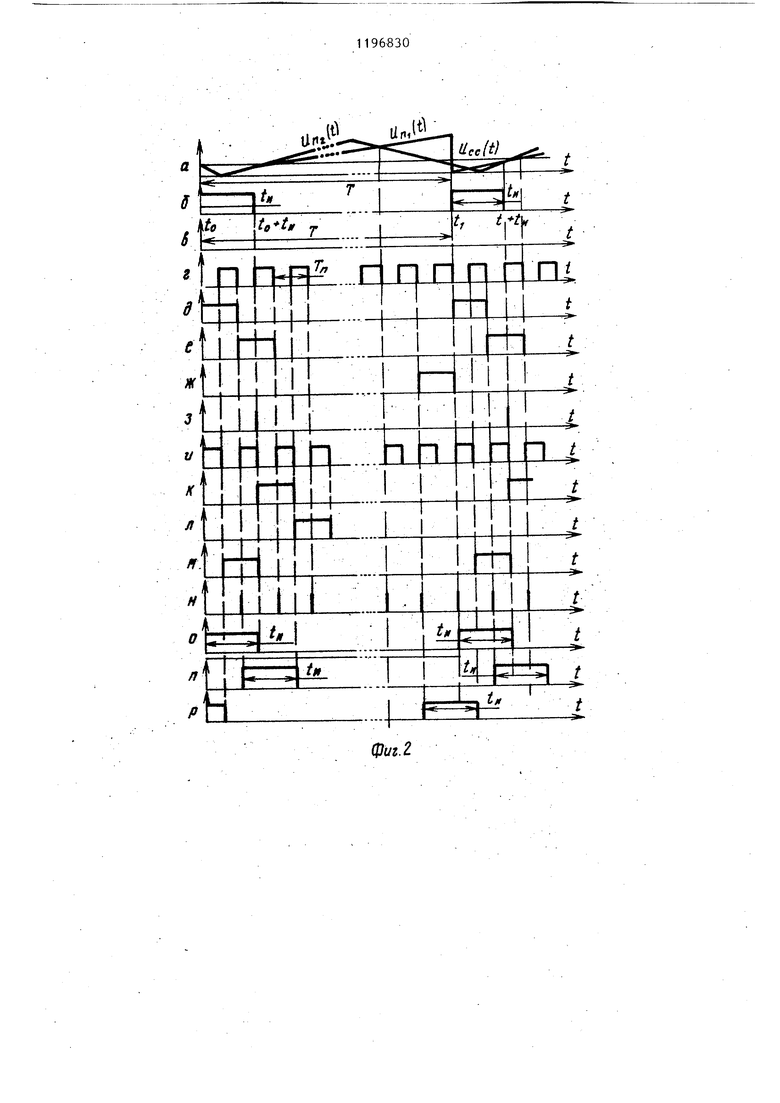

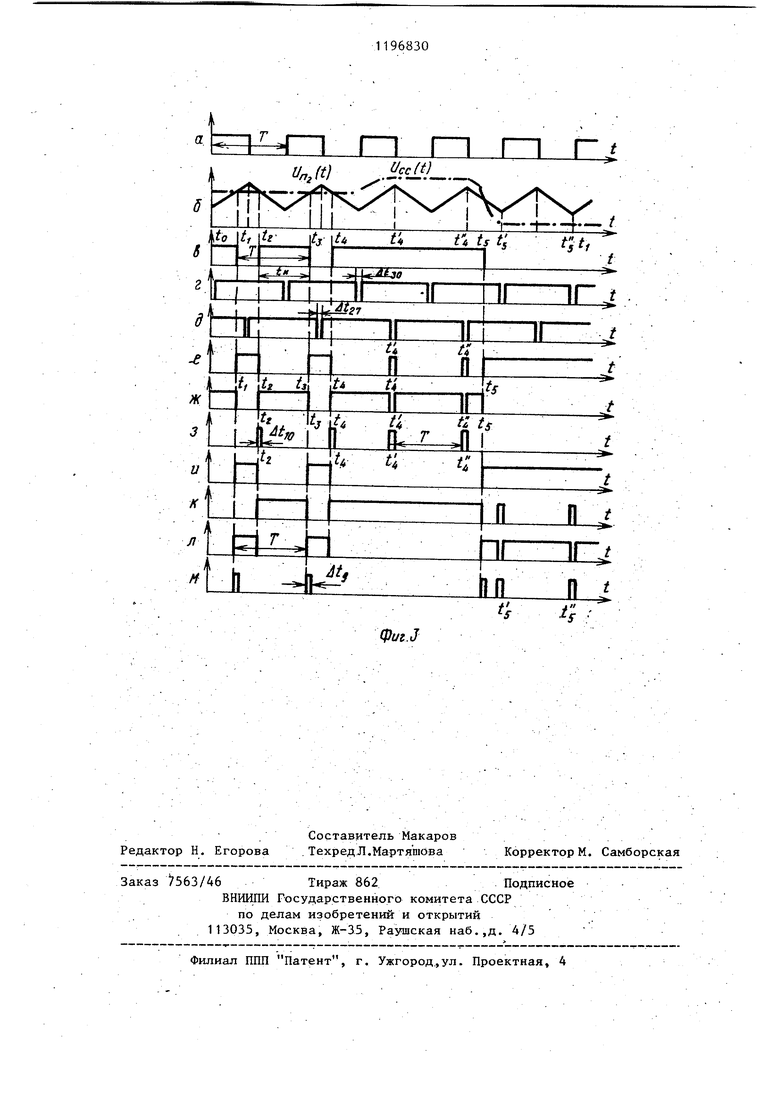

На фиг. 1 приведена схема многофазного импульсного стабилизатора; на фиг. 2 - эпюры напряжений « -р, поясняющие функционирование многофазного стабилизатора при коэффициентах заполнения, лежащих в интервале О Kj 1; на фиг. 3 - эпюры напряжений а - АЛ , поясняющие функцинирование каналов синхронизации передних и задних фронтов импульсов.

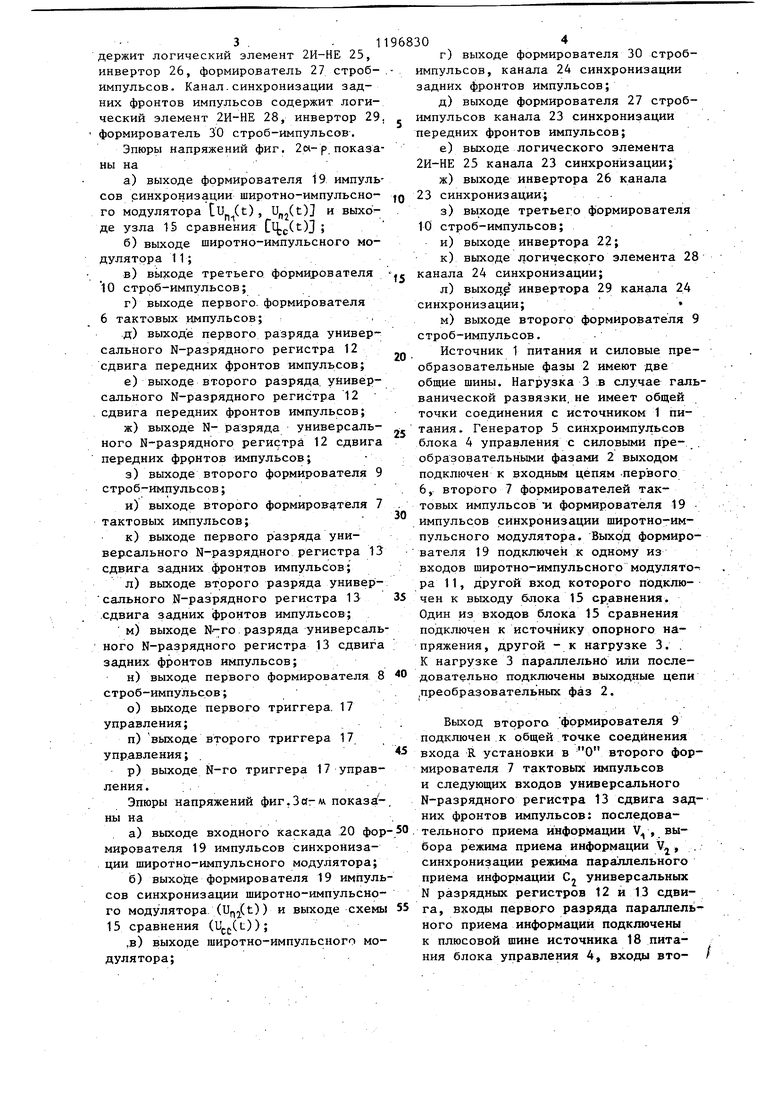

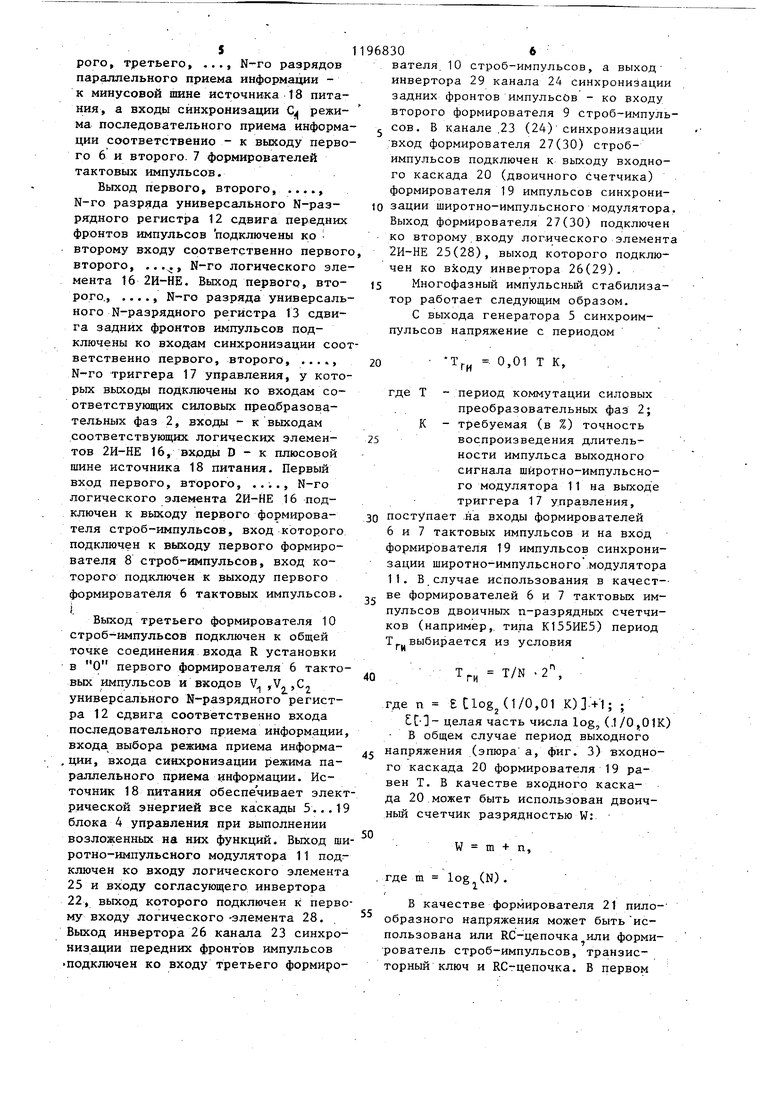

Стабилизатор содержит источник 1 питания, подключенный к N силовым преобразовательным фазам 2, выходные цепи которых подключены к нагрузке 3 параллельно или последовательно, и блок 4 управления. Блок управления содержит генератор 5 синхроимпульсов , первый 6 и второй 7 формирователи тактовых импульсов, первый 8, второй 9 и третий10 формирователи строб-импульсов, широтноимпульсный модулятор 11, универсальные N-разрядные регистры 12 и 13 сдвига соответственно переднего и заднего фронтов импульсов, источник 14 опорного напряжения, схему 15 сравнения, N логических элементов 2И-НЕ 16, N-триггеров 17 управления, источник 18 питания блока управления , формирователь 19 импульсов синхронизации Широтно-импульсного модулятора, выполненного из входного каскада 20 (делителя частоты) и выходного каскада 21 (формирователя пилообразного напряжения), согласующий инвертор-,22, каналы синхронизации передних 23и задних 24 фронтов импульсов. Канал синхронизации передних фронтов импульсов со 3 . -1 держит логический элемент 2И-НЕ 25, инвертор 26, формирователь 27 стробимпульсов. Канал.синхронизации задних фронтов импульсов содержит логический элемент 2И-НЕ 28, инвертор 29 формирователь 30 строб-импульсов. Эпюры напряжений фиг. 2сч-р показа ны на а)выходе формирователя 19 импуль сов синхронизации широтно-импульсного модулятора Cu(t) , (t) и выхо де узла 15 сравнения (t)3 ; б)выходе широтно-импульсного модулятора 11; в)выходе третьего формирователя 10 строб-импульсов; г)выходе первого, формирователя 6 тактовых импульсов;. д)выходке первого разряда универсального N-разрядного регистра 12 сдвига передних фронтов импульсов; е)выходе второго разряда, универсального N-разрядного регистра 12 сдвига передних фронтов импульсов; ж)выходе N- разряда универсального N-разрядного регистра 12 сдвига передних фррнтов импульсов; з)выходе второго формирователя 9 строб-импульсов; и) выходе второго формирователя 7 тактовых импульсов; к) выходе первого разряда универсального N-разрядного регистра 13 сдвига задних фронтов импульсов; л) выходе второго разряда универ(сального N-разрядного регистра 13 .сдвига задних фронтов импульсов; м) выходе N--ro. разряда универсаль кого N-разрядного регистра 13 сдвига задних фронтов импульсов; н) выходе первого формирователя 8 строб-импульсов; о) выходе первого триггера. 17 управления; п) выходе второго триггера 17 управления; р) выходе N-ro триггера 17 управления. ; . Эпюры напряжений фиг.Зйгм показаны на. а)выходе входного каскада 20 фор мирователя 19 импульсов синхронизации широтно-импульсного модулятора; б)выхо;а;е формирователя 19 импуль сов синхронизации широтно-импульсного модулятора. (UpjCt)) и выходе схемы 15 сравнения ()); ,в) выходе широтно-импульсного модулятора;304 г)выходе формирователя 30 стробимпульсов, канала 24 синхронизации задних фронтов импульсов; д)выходе формирователя 27 строб11мпульсов канала 23 синхронизации передних фронтов импульсов; е)выходе логического элемента 2И-НЕ 25 канала 23 синхронизации; ж)выходе инвертора 26 канала 23 синхронизации; . з)выходе третьего формирователя 10 строб-импульсов; и) выходе инвертора 22; к) выходе логического элемента 28 канала 24 синхронизации; л) выход инвертора 29 канала 24 синхронизации; м) выходе второго формирователя 9 строб-импульсов. . Источник 1 питания и силовые преобразовательные фазы 2 имеют две общие шины. Нагрузка 3 .в случае гальванической развязки, не имеет общей точки соединения с источником 1 питания. Генератор 5 синхроимпульсов блока 4 управления с силовыми преобразовательными фазами 2 выходом подключен к входным цепям -первого 6, второго 7 формирователей тактовых импульсов и формирователя 19 импульсов синхронизации широтно-импульсного модулятора. Выхдд формирователя 19 подключен к одному из входов широтно-импульсного модулятора 11, другой вход которого подключен к выходу блока 15 сравнения. Один из входов блока 15 сравнения подключен к источнику опорного напряжения, другой - к нагрузке 3. . К нагрузке 3 параллельно или последовательно подключены выходные цепи .преобразовательных фаз 2. Выход второго формирователя 9 подключен к общей точке соединения входа R установки в О второго формирователя 7 тактовых импульсов и следующих входов универсального N-разрядного регистра 13 сдвига задних фронтов импульсов: последовательного приема информации V , выбора режима приема информации V-, , синхронизации режима параллельного приема информации С универсальных N разрядных регистров 12 и 13 сдвига, входы первого разряда параллельного приема информации подключены к плюсовой шине источника 18 питания блока управления 4, входы вто- / 5 рого, третьего, ..., N-ro разрядов параллельного приема информации к минусовой шине источника 18 питания, а входы синхронизации С режима последовательного приема информа ции соответственно - к выходу перво го 6 и второго. 7 формирователей тактовых импульсов. Выход первого, второго, ...., N-ro разряда универсального N-разрядного регистра 12 сдвига передних фронтов импульсов подключены ко второму входу соответственно первог второго, .. . , N-ro логического эле мента 16 2И-НЕ. Выход первого, второго., ...., N-ro разряда универсаль ного N-разрядного регистра 13 сдвига задних фронтов импульсов подключены ко входам синхронизации соо ветственно первого, второго, ...., N-ro триггера 17 управления, у кото рых выходы подключены ко входам соответствующих силовых прео-бразовательных фаз 2, входы - к выходам соответствующих логических элементов 2И-НЕ 16, вхрды D - к плюсовой шине источника 18 питания. Первый вход первого, второго, ...., N-ro логического элемента 2И-НЕ 16 подключен к выходу первого формирователя строб-импульсов, вход которого подключен к выходу первого формирователя 8 строб-импульсов, вход которого подключен к выходу первого формирователя 6 тактовых импульсов. Выход третьего формирователя 10 строб-Импульсов подключен к общей точке соединения входа R установки в О первого формирователя 6 такто вых импульсов и ВКОДОВ V., универсального N-разрядного регистра 12 сдвига соответственно входа последовательного приема информации входа выбора режима приема информа.ции, входа синхронизации режима параллельного приема информации. Источник 18 питания обеспечивает элек рической энергией все каскады 5...1 блока 4 управления при выполнении возложенных на них функций. Выход ш ротно-импульсного модулятора 11 под ключен ко входу логического элемент 25 и входу согласующего инвертора 22, выход которого подключен к перв му входу логического -элемента 28. Выход инвертора 26 канала 23 синхро низации передних фронтов импульсов подключен ко входу третьего формиро 306 вателя 10 строб-импульсов, а выход инвертора 29 канала 24 синхронизации задних фронтов импульсов - ко входу второго формирователя 9 строб-импульсов. В канале .23 (24)синхронизации ВХОД формирователя 27(30) стробимпульсов подключен к выходу входного каскада 20 (двоичного счетчика) формирователя 19 импульсов синхронизации широтно-импульсного модулятора. Выход формирователя 27(30) подключен ко второму.входу логического элемента 2И-НЕ 25(28), выход которого подключен ко входу инвертора 26(29). Многофазный импульсный стабилизатор работает следующим образом. С выхода генератора 5 синхроимпульсов напряжение с периодом 0,01 Т К, где Т - период коммутации силовых преобразовательных фаз 2; К - требуемая (в %) точность воспроизведения длительности импульса выходного сигнала шйротно-импульсного модулятора 11 на выходе триггера 17 управления, поступает на входы формирователей 6 и 7 тактовых импульсов и на вход формирователя 19 импульсов синхронизации широтно-импульсного.модулятора 11. В.случае использования в качест-ве формирователей 6 и 7 тактовых импульсов двоичных п-разрядных счетчиков (например,, ти.па К155ИЕ5) период Т J. выбирается из условия . ТРИ T/N -2, где п Clog(1/0,01 K).Vl; ; &С-3- целая часть числа log, (.1 /0,01К) В общем случае период выходного напряжения (эпюра а, фиг. 3) входного каскада 20 формирователя 19 равен Т. В качестве входного каскада 20 может быть использован двоичный счетчик разрядностью W: W m + п. где m log (N). В качестве формирователя 21 пилообразного напряжения может быть использована или RC-цепочка или формирователь строб-импульсов, транзисторный ключ и RC-цепочка. В первом

7- . 1

случае формируется симметричное пилообразное напряжение U.(t) (эпюра «, фиг. 2), необходимое для широтноимпульсной модуляции двух фронтов импульсов, Во втором случае формируется пилообразное нап р яжение несимметричной формы и (t) (эпюрд а, фиг. 2), необходимое для модуляции заднего (переднего) фронта импульса. На фиг. 3 (эпюра 5) приведен случай формирования симметричного

пилообразного напряжения U, (tO. 2П

В одном периоде Т следования .пилообразного напряжения UpJ(t)или ) укладывается N периодов Tf, T/N следования напряжений формирователей 6 и 7 тактовых импульсов (эпюры а,г,и на фиг. 2), -В общем случае выходные напряжения формирователей 6 и 7 могут иметь сдвиг,по фазе. Причем выходное напряжение первого формирователя 6 синхрони-зируется в моменты времени, совпадающие с передним фронтом выходного напряжения широтно-импульсного модулятора 11i а выходное напряжение второго формирователя 7 - с задним ;фронтрм модулятора 11. В качестве синхронизируюи(Их сигналов испоЛьзуют ся строб-импуль.сы - выходные сигналы соответственно, формирователей 10 (эпюра В , фиг. .2) и 9 (эпюра з, . фиг. 2). Поскольку формирователи 9 и 10 формируют строб-импульсы лишь на перепад напряжений (соответственно 1/0 и О/1), -поступающих На их входы, то в известном устройст1ве при коэффициентах заполнения, равных нулю или единице -выходного сигнала модулятора 11 .указанные строб-импульсы на выходе формирователей 9 и 10 отсутствуют. Это приводит к неоднозначности сигналов управления преобразовательными фазами 2. Отсутствий в каждом из периодов Т синхронизирующих .строб-импульсов приводит .к критичности и/помехам. - любым возмущающим воздействиям, приводщим к сбою функционирования блока 4 управления. Случайно . возникпшй сбой в . триггерах 17 управления в этой ситуации уже не ликвидируется периодическим возобновлением информации в регистрах 12 и 13. При этом вместо высокого (низкого) уровня напряжения на выходе одного, двух, ...., или BcexN триггеров 17 управления может присутствовать низкий (высо.кий) уровень. Результатом этого мо968308 .

жет явиться потеря устойчивости

электрических процессов в многофазном импульсном стабилизаторе как в замкнутой системе автоматического регулирования.

Б предлагаемом устройстве (фиг.1) указанный недостаток устраняется за счет обеспечения синхронизирующих строб-импульсов при любом выход Q ном напряжении модулятора 11, т.е. при О Kj 1. Осуществляется это . следующим образом.

На воздействие выходного сигнала (эпюра а, фиг. 3) входного каскада

.г 20 формирователя 19 его выхрдной каскад 21 формирует пилообразное напряжение (например, си1 етричной формы - эпюра б, фиг. 3). Указанные пилообразное напряжение (t)

20 с периодом следования Т на выходе формирователя Г9.и напряжение ) (эпюра б, фиг. 3) на выходе схемы 15 сравнения используются для формирования на выходе широтно-импульсного

25 модулятора 11 импульсов с длительностью tj и периодом следования Т (эпюра в,- фиг. 3 - интервал времени tft- t 4) , когда О Kj 1 . При U(-c.(t) 7 ) на выходе модулятора

2Q 11 присутствует высокий уровень на-пряжения (эпюры б, в - интервал времени ty), при Uj.j.(t) ) низкий уровень напряжения (эпюры б, в, фиг. 3 - интервал времени t4- Выходное напряжение модулятора 11 поступает на вход канала 23 синхронизации передних фронтов импульсов и через инвертор 22 - на вход канала -синхронизации задних фронтов .24 импульсов.

40

.1

Канал 23 синхронизации передних фронтов импульсов работает следующим образом.

Формирователь 27 формирует отри5цательные строб-импульсы (эпюра д, фиг. 3) длительностью на перепад 1/0 выходного сигнала (эпюра а, фиг. 3) входного каскада 20 формирователя 19. Указанные строб-импуль0 сы поступают на второй .вход логического элемента 25, на перв.ый вход которого воздействует выходной сигнал широтно-импульсного модулятора 11 (эпюра б, фиг. 2). Одновременному присутствию высоких уровней напряжений на обоих входах (эпюра вид, фиг. 3) логического элемента 2И-НЕ 25 соответствует низкий уровень вы9ходкого напряжения (эпюра е, фиг, 3 интервал времени to- tg , t4-1;, ) - ,(t:i + 4t2i) -ty ... и соответственно высокий уро вень на выходе инвертора 26 (эпюра ж, фиг, 3). На перепад 0/1 выходног напряжения инвертора 26 формирователь 10 формирует положительные стр импульсы длительностью (эпюры 3, фиг. 3) в момент времени 2 t. , t|, . Таким образом, на выходе формирователя 10 присутствуют синхронизирующие строб-импуЛьсы при коэффициентах заполнения широтн модулированного сигнала, лежащих в интервале О К 1 (интервал вре мени tg- t эпюра 3, фиг. 3), и отсутствуют при Кз О (интервал времени t - tp . В отличие от известног в предлагаемом устройстве при Kj 1 (в момент времени 14 t), совпадаю щим с перепадом 0/1 выходного напря жения (эпюра а, фиг. 3) входного каскада 20 формирователя 19 импульсов синхронизации широтно-импульсно го модулятора, н,а вьйсоде третьего формирователя 10 присутствуют в каж дом периоде Т синхронизирующие строб-импульсы. Работа канала 24 синхронизации , задних фронтов импульсов аналогична работе канала 23 синхронизации. Задачей первого является обеспечение подачи в каждом периоде Т работы синхронизирующих импульсов Сна выходе формирователя 9) в моменты времени, совпадакнцие с задним фронтом (перепадом 1/0) выходного сигнала модулятора 11 (эпюра б, фиг.2) когда О Kj 1, и при низком уровне указанного сипГала модулятора 11 когда Kj 0. Это достигается тем, что на входы логического элемента 2И-НЕ 28 воздействуют: на первый вход - инвертированный (эпюра и, фиг. 2) инвертором 22 выходной сигнал модулятора 11 (эпюра в, фиг.З), на второй вход - выходной сигнал формирователя 30, формируккцего отрицательные строб-импульсы (эпюра г, фиг. 3) на перепад 0/1 выходного сигнала (эшора а, фиг. 3) входного каскада 20 фор шрователя 19. Резуль татом этого является получение на выходе логического элемента 28 сиг-. нала, соответствующего эпюре к на фиг. 3, и на выходе инвертора 29 сигнала, соответствующего эпюре л 3010 на фиг. 3. У последнего перепады 0/1 в выходном сигнале (эпюра л, фиг. .3) соответствуют моментам времени t , t.j , совпадающим с задним фронтом выходного сигнала (эпюра в,.фиг. 3) модулятора 11 (при О Кз 1) и моментам времени t.t, совпадающим с перепадом 0/1 выходного сигнала (эпюра а, фиг. 3) входного каскада 20 формирователя 19 (когда Кз 0). В указанные моменты времени-t , t , t ,а также в момент времени tj, соответствующий перепаду 1/0 выходного сигнала модулятора 11 (когда Kj становится равным нулю), формирователь 9 формирует положительные строб-импульсы (эпюра м, фиг. 3). Здесь, в отличие от известного устройства,при Кз О в каждом периоде обеспечиваются синхррнизирующие строб-импульсы, (моменты времени tg., tjl - эпюра м, фиг. 3), Таким образом, введение каналов синхронизации передних 23 и задних 24 фронтов импульсов обеспечивает наличие синхронизирующих сигн.алов на выходе формирователей соответственно 10 и 9 при любых коэффициентах заполнения выходного шир.отно-модулированного сигнала модулятора 11. При О : К 3 1 появляются положительные строб-импульсы на выходе второго формирователя 9 в момент времени t + Ь„; t,+ t, ,..., (эпюра 3, фиг. 3), совпаданицие с задним фронтом сигнала модулятора 11 (эпюра б, фиг. 2), и на выходе третьего формирователя 10 - в момент времени t -. ... {эпюра в, фиг. 2), совпадаю- , - щие с передним фронтом сигнада моду- . лятора 11. Короткий положительный строб-импульс (эпюра в, фиг. 2) на выходе третьего формирователя 10 в указанные моменты времени обеспечивает установку в О формирователя (счетчика) 6 по входу R и перевод универсального К-разрядного регистра 12 по входу Vj в режим параллельного приема информации.. Аналогично положительный строб-импульс (эпюра з,фиг.2) на выходе второго формирователя 9 в моменты времени tjj+ t,.,, t, обеспечивает установку в О второго формирователя (счетчика) 7 по входу R и перевод универсального N-разряд.ного регистра 13. по входу V в режим параллельного приема информации. Так как входы первого разряда у регистров 12 и. 13 подключены к плюсовой шине источника 18 питания, а вх ды разрядов со второго по N-й подключены к минусовой шине источника 18 питания, то обеспечивается запис высокого уровня напряжения в первый разряд и низкого уровня напряжения в разряды .со BTopord по N-й соответ ствейно у регистра 12 в момент времени tp,t ,.,. (эпюры Д)е, ж, фиг, 2) |И у регистра 13 в момент Ц (эпюры к,л. времени to+ tj,, м, фиг. 2). Таким образом, в каждом периоде Т производится установка в О первого формирователя 6 в моменты времени (эпюра в, фиг. 2), совпадающие с передним фронтом второго формирователя 7 в моменты времени ( 3, фиг.2) , которые совпадают с задним фронтом сигнала модулятора 11 (эпюра б, фиг. 2). В ин тервалах времени между воздействиям строб-импульсов формирователи 6 и 7 обеспечивают тактовые импульсы, спе риодом следования Т ц на входах С синхронизации режима последовательного прйема информации соответствен . но регистров 12 и 13, В указанные интерва;лы времени регистры 12 и 13 переводятся в режим последовательного .приема информации (на входах . Vj) присутствуют низкие уровни на-, пряжений -(эпюры в, з, фиг, 2). Поэтому запнсанные в первые разряды сдвига 12 и 13 высокие уровни напря жений сохраняются соответственно на выходе первого разряда регистра . 12 в интервалах времени t-j, t tj+ + . (эпюра д, . фиг.,, 2). В моменты времени tg+Tr,, t + Т|, совпадающие с фронтом 1/0 поступаю 1цих с выхода формирователя 6 на вход синхронизации С регистра 12 тактовых импульсов (эпюра производится запись низких уровней напряженийв первый разряд (эпюра д, фиг, 2) и высоких уровней напряжений BQ втррой разряд (эпюра е, .. фи. 2). Так как период следования тактовьк импульсов на выходе, формирователя 6 равен Т (эпюра г,фиг. 2 то на N-выходах регистра 12 будут .присутствовать высокие уровни напря жений длительностью Т,начиная с мо мента времени: на выходе первого разряда с tp,t (эпюра д, фиг, 2), на в.ыходе второго разряда с tp+ Т ,.., (эпюра е, фиг, 2),,,,, на выходе N-ro разряда с t(j+(N-1) Т t, UN -1) Т эпюра ж сЬиг. 2 ) , Напряжение на выходе второго формирователя тактовых импульсов 7 (эпюра и, фиг, 2). синхронизируется строб-импульсом - (эпюра з, фиг, 2), совпадающим по времени с задним фронтом выходного, сигнала широтноимпульсного модулятора 11 (эпюра б, фиг, 2), .Поэтому появление высоких: уровней напряжений на выходах регистра 13 .сдвинуто по оси. времени на величину tj длительности импульса выходного сигнала модулятора 11 отйосительно выходных сигналов одноименных выходов регистра 12, В результате на N-выходах регистра 13 сдвига задних фроктов импульсов будут присутствовать высокие уровни напряжений длительностью Tf,, начиная со следующих моментов времени: на выходе первого разряда с to+ Tf,, , (эпюра и, фиг, 2), на выходе второго разряда: с , (эпюра л, фиг, 2), на выходе N-ro разряда с. to+tr,+ (N-1) Тр, . , + (N-1) Tf, (эпюра м, фиг. 2), Выходное найряжение первого формирователя 6 тактовых импульсов (эпюра г, фиг, 2) используется дополнительно и для формирования положительных импульсов большей скважности первым формирователем 8 стробимпульсов (эпюра н, фиг,2), Форми- . рователь 8 формирует указанные импульсы на перепад 1/0 выходного напряжения формирователя 6 (эпюры г, н, фиг, 2), В результате на первый вход первого, второго,,,,, N-ro логического элемента 2И-НЕ 16 постоянно воздействует последовательность положите; ьных импульсов большой скважности с периодом следова- ния Тп. На второй вход, первого, второго, ,,,, N-ro логического элемента 2И-НЕ 16 воздействует последовательность положительных импульсов длительностью Tfi и периодом следования Т (эпюры д, е, ж, фиг, 2), поступающая- соответственно с выхода первого, второго, , ,,, разрядов регистра 12 сдвига передних фронтов импульсов, Одновременно присутствие высоких уровней напряжений на входах логических элементов 2И-НЕ 16 обеспечивает на входе R соответствующего триггера 17 управления установку низкого уровня и

131

установку его по выходу Q в низкий, а по выходу Q в высокий напряжения. В результате на выходе Q первого триггера 17 управления появятся высокие уровни напряжения в моменты времени t, Ц ..., (эпюра е, фиг. 2), на выходе второго триггера 17 - , , ..., (эпюра п, фиг. 2), на выходе N-ro триггера 17 - te+T|(N-1), T(N-I) (эпюра р, фиг. 2). Высокие уровни напряжений на вькодах Q триггеров 17 управления будут сохраняться до прихода на вход синхронизации С сигнала управления с соответствующего выхода регистра 13 сдвига задних фронтов импульсов. Фронтом 0/1 сигнала с выхода пер-, вого, второго, ..., N-ro разряда регистра 13 (эпюры к, л,м, фиг. 2) производится переключение по выходу Q с низкого уровня на высокий (по входу D присутствует высокий уровень напряжения) и с высокого уровня на низкий уровень напряжения по выходу Q соответственно первого триггера 17 управления в моменты времени to+ t

t, (эпюра a, фиг. 2),

второго триггера 17 в моменты времени tj+ Т„, Tn,..., (эпюра п, фиг. 2), N-ro триггера 17 в моменты времени tj+tf,+(N-1) (N-1) Тр, (эпюра р, фиг. 2). Формирователи (счетчики) 6 и 7 имеют одинаковую разрядность п. Это обеспечивает формирование ими тактовых импульсов с равным периодом Т,, но со сдвигом по фазе, так как начальное состояние формирователя 6 синхронизируется в моменты времени.

6830 14

совпадающие с передним фронтом импульса на выходе широтно-импульсного модулятора 11, а формирователя 1-е. задним фронтом. В результате на выJ ходе триггеров 17 управления получается широтно-модулированные импульсы (эпюры о, п, р,-фиг. 2), равномерно сдвинутые на время Т, и равные по длительности сигналу на

(О выходе модулятора 11. Указанные.

сигналы используются для управления . соответствующей преобразовательной фазой 2.Сдвиг во времени на величину Tf, данных сигналов управления обеспечивает сдвиг во времени электрических процессов в силовых .преобразовательных: фазах..

Изменение напряжения на нагрузке 3 при воздействии какого-либо возмущающего воздействия приведет к изменению уровня напряжения U-.(t) (эпюра б, фиг. 3) на выходе схемы сравнения и к соответст;вукнцему изменению сигнала (эпюра в, фиг.. 3) на выходе широтно-импульсного модулятора11. Это приведет к сдвигу во. времени сиг-налов на выходах регистров 12 и 13сдвига соответственно переднего н . задних фронтов импульсов, к изменению длительности сигналов на выходе триггеров 17 управления и .к изменению энергии, передаваемой каждой силовой преобразовательной фазой 2 в нагрузку 3. Указанные изменения за счет использования отрицательной обратной связи направлены на компенсацию возмущающих воздействий и лгстановление с заданной точностью напряжения на нагрузке 3.

Сриг.1

Фиг.2

| Авторское свидетельство СССР, №lOt9413, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Блок управления многофазным импульсным стабилизатором | 1983 |

|

SU1123085A1 |

Авторы

Даты

1985-12-07—Публикация

1984-05-15—Подача