Изобретение относится к электротехнике и может быть использовано в качестве источников электропитания электротехнической и радиоэлектронной аппаратуры различного назначения Целью изобретения является расширение функциональных возможностей путем обеспечения возможности работы с различньрм числом силовых преобразовательных ячеек.

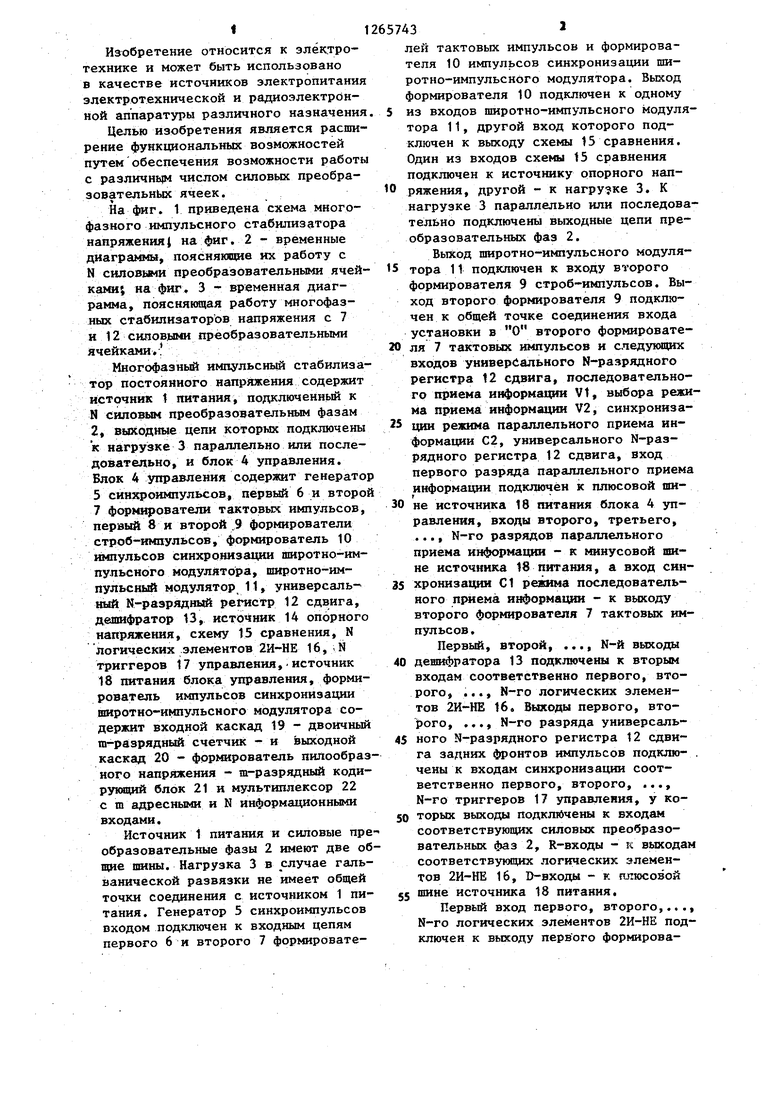

На фиг. 1 приведена схема многофазного импульсного стабилизатора напряжения на фиг.2 - временные диаграммы, поясняющие их работу с N силовьми преобразовательными ячейкa шl на фиг, 3 - временная диаграмма, пояснякйцая работу многофазных стабилизаторов напряжения с 7 и 12 силовыми преобразовательными ячейками.7

Многофазный импульсньй стабилизатор постоянного напряжения содержит источник t питания, подключенный к N силовым преобразовательным фазам 2, выходные цепи которых подключены к наьгрузке 3 параллельно или последовательно, и блок 4 управления. Блок 4 управления содержит генератор 5 синхроимпульсов, первый б и второй 7 формирователи тактовых импульсов, первый 8 и второй 9 формирователи строб-импульсов, формирователь 10 импульсов синхронизахцш широтно-импульсного модулятора, широтно-импульсный модулятор 11, универсальный М-разрядный регистр 12 сдвига, дешифратор 13, источник 14 опорного напряжения, 15 сравнения, N Логических элементов 2И-НЕ 16, -N триггеров 17 управления,источник 18 питания блока управления, формирователь импульсов синхронизации имротно-имнульсного модулятора содержит входной каскад 19 - двоичный 1п-ра:зрядный счетчик - и 1зыходной каскад 20 - формирователь пилообразного напряжения - т-разрядный кодирукиций блок 21 и мультиплексор 22 cm адресными и N информационными входами.

Источник 1 питания и силовые преобразовательные фазы 2 имеют две общие 1Ш1НЫ. Нагрузка 3 в случае гальванической развязки не имеет общей точки соединения с источником 1 питания. Генератор 5 синхроимпульсов входом подключен к входным цепям первого 6 и второго 7 формирователей тактовых импульсов и формирователя 10 импульсов синхронизации широтно-импульсного модулятора. Выход формирователя 10 подключен к одному

из входов широтно-импульсного модулятора 11, другой вход которого подключен к выходу схемы 15 сравнения. Один из входов схемы 15 сравнения подключен к источнику опорного напряжения, другой - к нагрузке 3. К нагрузке 3 параллельно или последовательно подключены выходные цепи преобразовательных фаз 2.

Выход широтно-импульсного модулятора 11 подключен к входу второго формирователя 9 строб-импульсов. Выход второго формирователя 9 подключен к общей точке соединения входа установки в О второго формирователя 7 тактовых импульсов и следукдащх входов универсального N-разрядного регистра 12 сдвига, последовательного приема информащш VI, выбора режима приема информации V2, синхронизацин режима параллельного приема информации С2, универсашьного N-разрядного регистра 12 сдвига, вход первого разряда параллельного приема информации подключён к плюсовой шине источника 18 питания блока 4 управления, входы второго, третьего, ..., N-ro разрядов параллельного приема информации - к минусовой шине источника 18 питания, а вход синхронизащш С1 режима последовательного п{жема И1 ормации - к выходу второго формирователя 7 тактовых импульсов.

Первый, второй, ..., N-й выходы

дев1ифратора 13 подколочены к вторым входам соответственно первого, второго, ..., N-ro логических элементов 2И-НЕ 16. Выходы первого, , ..., N-ro разряда универсального N-разрядного регистра 12 сдвига задних фронтов импульсов подкшо- . чены к входам синхронизации соответственно первого, второго, ..., N-ro триггеров 17 управления, у которых выходы подкл бчены к входам соответствующих силовых преобразовательных фаз 2, R-входы - к вькодам соответствующих логических элементов 2И-НЕ 16, D-входы - к плюсовой

шине источника 18 питания.

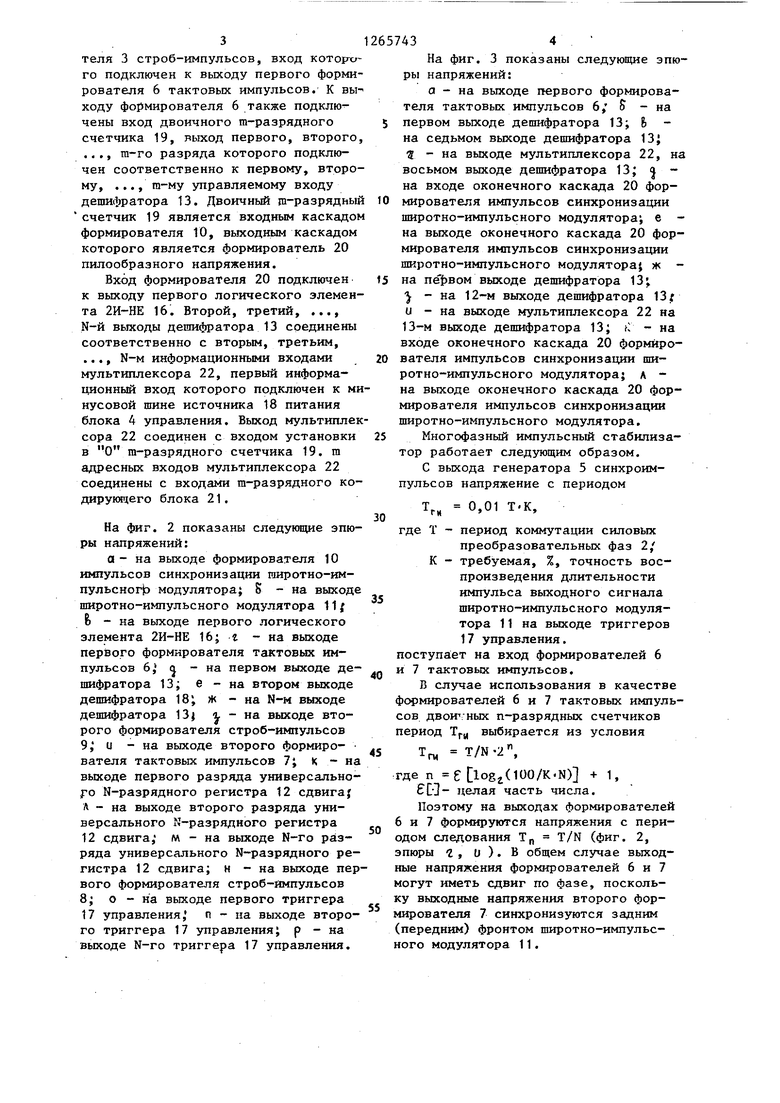

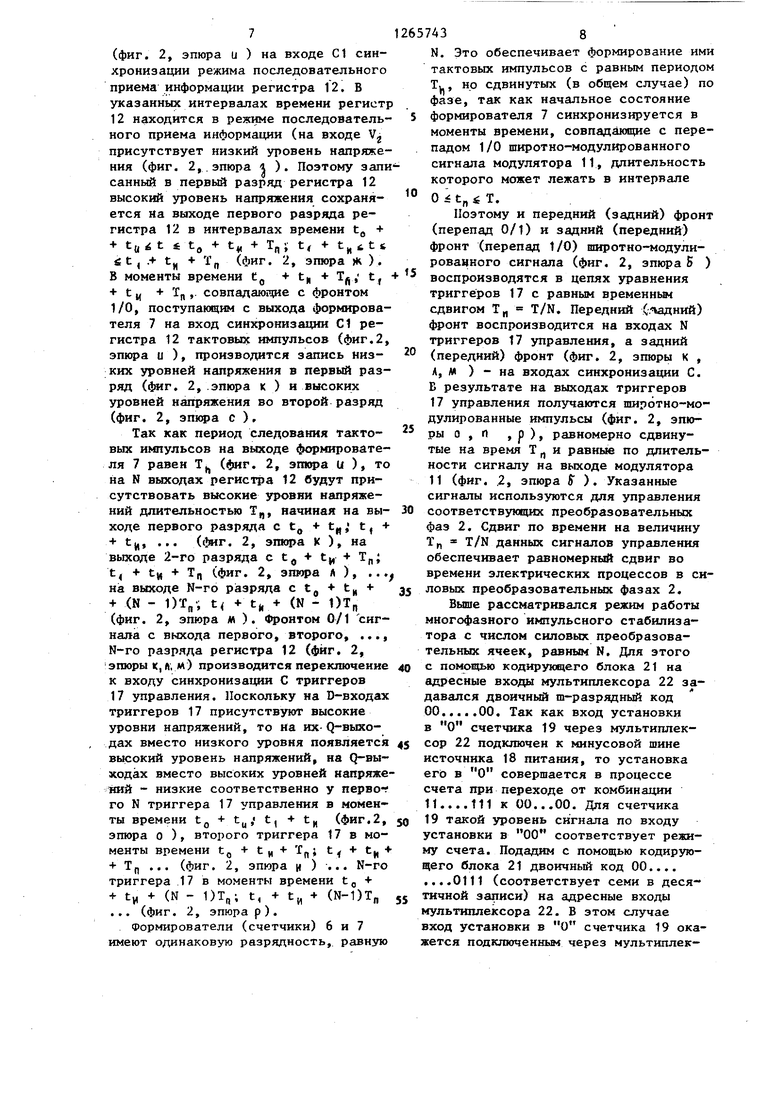

Первый вход первого, второго,.,., N-ro логических элементов 2И-НЕ подключен к выходу первого формирователя 3 строб-импульсов, вход которс/ го подключен к выходу первого форми рователя 6 тактовых импульсов. К вы ходу формирователя 6 также подключены вход двоичного т-разрядного счетчика 19, выход первого, второго ..,, га-го разряда которого подключен соответственно к первому, второ му, ..., т-му управляемому входу дешифратора 13. Двоичный щ-разрядны счетчик 19 является входным каскадо формирователя 10, выходным каскадом которого является формирователь 20 пилообразного напряжения. Вход формирователя 20 подключен к выходу первого логического элемен та 2И-НЕ 16, Второй, третий, ..., N-й выходы дешифратора 13 соединены соответственно с вторым, третьим, ..., N-M информационными входами мультиплексора 22, первый информационный вход которого подключен к м нусовой шине источника 18 питания блока 4 управления. Выход мультипле сора 22 соединен с входом установки в О т-разрядного счетчика 19. m адресных входов мультиплексора 22 соединены с входами т-разрядного ко дирующего блока 21. На фиг. 2 показаны следуннцие эпю ры напряжений: а - на выходе формирователя 10 импульсов синхронизации широтно-импульсног э модулятора; S - на выходе широтно-импульсного модулятора 11/ fe - на выходе первого логического элемента 2И-НЕ 16; t - на выходе первого формирователя тактовых импульсов 6, - на первом выходе дешифратора 13; е на втором выходе дешифратора 18 Ж -на N-M выходе дешифратора 13j г. -на выходе второго формирователя строб-импульсов 9, и - на выходе второго формирователя тактовых импульсов 7; к - на выходе первого разряда универсальноfo N-разрядного регистра 12 сдвигаj Л - на выходе второго разряда универсального N-разрядного регистра 12 сдвига, м - на выходе N-ro разряда универсального N-разрядного регистра 12 сдвига; н - на выходе пер вого формирователя строб-импульсов 8; о - на выходе первого триггера 17 управления, п - на выходе второго триггера 17 управления; р - на выходе N-ro триггера 17 управления. На фиг. 3 показаны следующие эпюры напряжений: а - на выходе первого формирователя тактовых импульсов 6, & - на первом выходе дешифратора 13; 6 на седьмом выходе дешифратора 13; - на выходе мультиплексора 22, на восьмом выходе дешифратора 13; на входе оконечного каскада 20 формирователя импульсов синхронизации широтно-импульсного модулятора; е на выходе оконечного каскада 20 формирователя импульсов синхронизации широтно-импульсного модулятора ж на neijJBом выходе дешифратора 13; - на 12-м выходе дешифратора 13,f и - на выходе мультиплексора 22 на 13-м выходе дешифратора 13; - на входе оконечного каскада 20 формирователя импульсов синхронизации пшротно-импульсного модулятора; А на выходе оконечного каскада 20 формирователя импульсов синхронизации широтно-импульсного модулятора. Многофазный импульсный стабилизатор работает следующим образом. С выхода генератора 5 синхроимпульсов напряжение с периодом Т 0,01 Т.К, где Т период коммутации силовых преобразовательных фаз 2/ К - требуемая, %, точность воспроизведения длительности импульса выходного сигнала широтно-импульсного модулятора 11 на выходе триггеров 17 управления. оступает на вход формирователей 6 7 тактовых импульсов. В случае использования в качестве ормирователей б и 7 тактовых импульов двои-ных п-разрядных счетчиков ериод ТГУ выбирается из условия Тп, T/N де п е logj(100/K.N) + L целая часть числа. Поэтому на выходах формирователей и 7 формируются напряжения с перидом следования Т T/N (фиг. 2, пюры 1 , О ). В общем случае выходые напряжения формирователей 6 и 7 огут иметь сдвиг по фазе, поскольу выходные напряжения второго форирователя 7 синхронизуются задним передним) фронтом широтно-импульсого модулятора 11. Выходное напряжение первого,формирователя 6 тактовых импульсов воздействует на входы формирователей 10 и 8. Входным каскадом формировате ля 10 импульсов синхронизации широтно-импульсного модулятора является двоичный счетчик, разрядность m которого является функцией числа N преобразовательных фаз, чп logjN. Поскольку выходы первого, второго, ..., ш-го разрядов двоичного счетчика 19 подключены к управляющим входам дешифратора 13, то на первом, втором, ..,, N-M выходе девтфратора 13 появляются полояительные импульсы (фиг. 2, эпюры Ч е , ) длитель ностью Т T/N и периодом следования, равным Т. Например, эпюра j (фиг. 2) соответствует состоянию счетчика 19 00...00, эпюра е соответствует состоянию 00...01, эпюра Ж соответствует состоянию 11.... 111 счетчика 19. JB предлагаемом устройстве положи телйше строб-импульсы (фиг. 2, эпю ра Н ) формирователя 6 совпадают с перепадом О/1 выходного сигнала (фиг. 2, эпкфа г ) формирователя 6. Указанные строб-импульсы с периодом следования Т T/N воздействуют на первый вход первого, второго, ..., N-ro логических элементов 2И-НЕ 16. Поскольку на второй вход указанных логических элементов 16 поступают положительные импульсы с выходов (первого, второго, ...t N-ro эпюра , е , Яс г. 2) дешифратора 13 с Периодом следования Т, в N раз боль шем Т, то на выходах логических эл ментов 16 будут появляться (при одновременном присутствии высоких уро ней напряжений) отрицательные импул сы с периодом следованияТ. В результате воздействия этих импульсов по R-входу триггеров 17 управления происходит установка их по выходу Q в низкий, а по выходу Q в высокий уровень напряжений. На выходе Q пер |Вого триггера 17 управления появятс высокие уровни напряжения в моменты I 1. « времени (фиг. 2, эпюра о ), на выходе второ Tj,} t Т„.. го триггера 17 - t (фиг. 2, эпюра п ), на выходе N-ro триггера 17 - to + T(N - 1); t, -I- Trt(N - 1) (фиг. 2, эпюра p ) вие уровни напряжений на выходах Q триггеров 17 управления будут сохраняться до прихода на вход синхронизации С сигнала и управления с соответствующего выхода регистра 12 сдвига. Выходной отрицательный импульс (фиг. 2, эпюра 6 ) первого логическо го элемента 2И-НЕ 15 используется для синхронизации формирователя 20 пилообразного напряжения. Выходной сигнал U(t) (фиг. 2, эпюра а ) формирователя 20 с периодом следования Т воздействует на один из входов ширбтно-импульсного модулятора 11, на второй вход которого воздействует уровень напряжения U (t) с выхода схемы 15 сравнения. Это вызывает появление на выходе модулятора 11 широтно-модулированного сигнала с длительностьюимпульсов t и периодом следования Т (фиг. 2, эпюра S ). Указанный сигнал поступает на вход второго формирователя 9 строб-импульсов. На фронт 1/0 данного сигнала второй формирователь 9 стробимпульсов формирует положительные строб-импульсы в моменты времени (фиг. 2, ЭПЮЧ , pa -v ) . Короткие положительные импульсы формирователя 9 обеспечивают установку в О второго формировате ля (счетчика) 7 по R-входу и перевод универсального регистра 12 по входу Vj в режим параллельного приема информации. Так как вход первого разряда регистра 12 подключен к плюсовой пмне источника 18 питания, а входы разрядов с второго по N-й подключены к минусовой шине источника 18 питания, то обеспечивается запись вы-, сокого уровня напряжения в первый разряд и низкого уровня напряжения в разряды с второго по N-й в моменты (фиг.2, времени .. эпюры к , А им). Таким образом, в каждом периоде Т производится установка в О второго формирователя. 7 тактовых импульсов (фиг. 2, эпюра U ) в моменты времени (фиг. 2, эпюра J ) совпадающие с фронтом 1/О выходного сигнала модулятора 11 (фнг, 2, эпюра 5 ). В интервалах времени между воздействиями строб-импульсов формирователь 7 обеспечивает тактовйе им-: пульсы с периодом следования Т. (фиг. 2, эпюра U ) на входе С1 синхронизации режима последовательного приема информации регистра 12. В указанных интервалах времени регистр 12 находится в режиме последовательного приема информации (на входе V присутствует низкий уровень напряжения (фиг. 2,. эпюра К ). Поэтому запи санный в первый разряд регистра 12 высокий уровень напряжения сохраняется на выходе первого разряда регистра 12 в интервалах времени t + -о + t + Tnv t, t.t.; + tu t « t fi t , . tj, + Tp (фиг. 2, эпюра ж ). В моменты времени t. + t. + Т + Т ,. совпадающие с фронтом 1/0, поступающим с выхода формирователя 7 на вход синхронизации С1 регистра 12 тактовых импульсов (фиг.2, эпюра U ), производится запись низких уровней напряжения в первый разряд (фиг. 2,.эпюра к ) и высоких уровней напряжения во второй разряд (фиг. 2, эпкфа с )г Так как период следования тактовых импульсов на выходе формирователя 7 равен Т (фиг. 2, эпюра U ), то на N выходах регистра 12 будут присутствовать высокие уровни напряжений длительностью Т., начиная на вып t«. t, + ходе первого разряда с t ((иг. 2, эпюра К ), на выходе 2-го разряда с t, + tj, + „, разряда с t, + t,, + t, tt, + Т (фиг. 2, эпюра А ), на выходе N-ro разряда с t, t,, + + (N - 1)Т„-, t + t + (N - 1)Тп (фиг. 2, эпюра м ). Фронтом 0/1 сигнала с вмхода первого, второго, ..., N-ro разряда регистра 12 (фиг. 2, эпюры к, А, м) производится переключение к входу синхронизации С триггеров 17 управления. Поскольку на D-входах триггеров 17 присутствуют высокие уровни напряжений, то На их-Q-выходах вместо низкого уровня появляется высокий уровень напряжений, на Q-выходах вместо высоких уровней напряжений - низкие соответственно у первого N триггера 17 управления в момен- t (фиг.2, ты времени t -i- t ,« t, эпюра о ), второго триггера 17 в моменты времени t + t -ь Т„; 11 + t « + Т ... (фиг. 2, эпюра и ) триггера 17 в моменты времени t + + ty, + (N - 1)Т„; t, + tj, + (N-l)Tn ... (фиг. 2, эпюра р). Формирователи (счетчики) 6 и 7 имеют одинаковую разрядность,, равнзгю tf 7438 N. Это обеспечивает формирование ими тактовых импульсов с равным периодом Ti, но сдвинутых (в общем случае) по фазе, так как начальное состояние формирователя 7 синхронизируется в моменты времени, совпадающие с перепадом 1/0 широтно-модулированного сигнала модулятора 11, длительность которого может лежать в интервале Oitni Т. Поэтому и передний (задний) фронт (перепад 0/1) и задний (передний) фронт (перепад 1/0) широтно-модулированного сигнала (фиг. 2, эпюра Б ) воспроизводятся в цепях уравнения триггеров 17 с равным временн1лч сдвигом Т„ T/N. Передний (. адний) фронт воспроизводится на входах N триггеров 17 управления, а задний (передний) фронт (фиг. 2, эпюры к , Л, м ) - на входах синхронизации С. В результате на выходах триггеров 17 управления получаются широтно-модулированные импульсы (фиг. 2, эпюры о , г , р ), равномерно сдвинутые на время Т и равные по длительности сигналу на выходе модулятора 11 (фиг. .2, эпюра 5 ). Указанные сигналы используются для управления соответствуювцсс преобразовательных фаз 2. Сдвиг по времени на величину Т„ T/N данных сигналов управления обеспечивает равномерный сдвиг во времени электрических процессов в силовых преобразовательных фазах 2. Выше рассматривался режим работы многофазного импульсного стабилизатора с числом силовых преобразовательных ячеек, равным N. Для этого с помощью кодирующего блока 21 на адресные входы мультиплексора 22 задавался двоичный т-разрядный код 0000, Так как вход установки в О счетчика 19 через мультиплексор 22 подключен к минусовой шине источника 18 питания, то установка его в О совершается в процессе счета при переходе от комбинации 11.... 111 к 00...00. Для счетчика 19 такой уровень сигнала по входу установки в 00 соответствует режиму счета. Подадим с помощью кодирующего блока 21 двоичный код 00.... ....0111 (соответствует семи в десятичной записи) на адресные входы мультиплексора 22. В этом случае вход установки в О счетчика 19 окажется подкгооченньм через мультиплек9сор 22 к восьмому выходу дешифратора 13. Блок управления преобразователем работает аналогично ранее описанному при состояниях счетчика 19.00.... 00, 00....01, 00010, 00 ....0110 (фиг. За, В,) ). При состоянии счетчика 19 00....0111 сигнал 1 с выхода деш1 ратора 13 через мультиплексор 22 пройдет на вход установки в О счетчика 19 (фиг.Зг) и установит его в О. За состоянием 00....0110 в счетчике 19 следует состояние 000....00 и производится гашение импульса синхронизации широтно-импульсного модулятора (фиг. 3 , с) . Таким образом, многофазный импульсный стабилизатор начинает работать с семью силовыми преобразовательными ячейками. Если подать посредством кодирующего блока на адрес ные входы мультиплексора код 00.... ....01100 (двенадцать), то к входу установки в О счетчика 19 подключается 13-й выход дешифратора 13. Блок 4 управления в этом случае работает на 12 фаз (фиг, ЗЖ, , К , Таким образом, установка на входе кодирующего блока числа Р позволяет формировать период пилообразно го напряжения Т в Р раз превьапающий период следования тактовых импульсов Т„. Как было ранее показано это позволило сформировать равномер но сдвинутые идентичные сигналы для управления силовыми преобразователь ными ячейками, число которых программно задается от N до 2-х. Изменение напряжения на нагрузке 3 при воздействии какого-либо возмущающего воздействия приведет к из менению зфовня напряжения Vgj (t) на выходе схемы сравнения и-к соответствующему изменению сигнала на выходе широтно-импульсного модулятора 11. Это приведет i к изменению (сдвигу) во времени сигналов на выходах регистра 12 сдвига, воспроизводящего перепад 1/О пшротно-модулированного сигнала и к изменению длительности сигналов на выходе триггеров 17 управления и к изменению энергии

передаваемой каждой силовой преобра- jjка питания блока управления, вход

зовательной фазой 2 в нагрузку 3.второго, третьего, ... N-ro разрядов

Указанные изменения за счет использопараллельного приема информации - к

вания отрицательной обратной связиминусовой шине источника питания. 3 направлены в компенсацию возмущающих воздействий и установлению с заданной точностью напряжения на нагрузке 3. Формула изобретения Многофазньй импульсный стабилизатор напряжения, содержащий силовую цепь, выполненную в виде N параллельно (последовательно) включенных силовых преобразовательных ячеек, и блок управления, включающий в себя генератор синхроимпульсов, формирователь импульсов синхронизации широтноимпульсного модулятора, содержащего входной двоичный т-разрядный счетчик и выходной формирователь пилообразного напряжения, универсальный N-разрядный регистр сдвига, два формирователя тактовыхимпульсов, два формирователя строб-импульсов, источник опорного напряжения, источник питания блока управления, схему сравнеНИН, т-разрядный кодирующий блок и мультиплексор с т-адресными и N- информационными входами, при этом m выходов т-разрядногр кодируикцего блока подключены к т-адресным входам мультиплексора, схема сравнения одним из входов подключена к источнику опорного напряжения, другим - к нагрузке стабилизатора, а выходом к одному из входов широтно-импульсного модулятора, другой вход которого подключен к выходу формирователя импульсов синхронизации широтноимпульсного модулятора, выход широтно-импульсного модулятора через второй формирователь строб-импульсов подключен к общей точке соединения входа установки в О второго форми-ь рователя тактовых импульсов и входов последовательного приема информации, выбора режима приема информации, синхронизации режима параллельного приема информации универсального Н-разряднбго регистра сдвига, у которого вход синхронизации режима последовательного приема информации подключен к выходу второго формирователя тактовых импульсов, вход первого разряда параллельного приема информации к плюсовой шине источнивыходы первого, второго, ... N-ro разрядов - к входам синхронизации соответственно первого, второго,... N-rc триггеров управления, у которых R-выходы подключены к входам соответствукяцих логических элементов 2И-НЕ, D-входы - к плюсовой шине источника питания блока управления, первый вход первого, второго, ..., N-ro логических элементов 2Й-НЕ подключен к выходу первого формирователя строб-импульсов, вход которого подключен к выходу первого формирователя тактовых импульсов и к входу формирователя импульсов синхронизации широтно-импульсного модулятора, выход генератора синхроимпульсов под ключен к входам первого и второго формирователей тактовых импульсов, второй вход первого, второго, ..., N-ro логических элементов 2И-НЕ подключен соответственно к первому, вто рому, .., N-My выходам дешифратора, при этом первый, второй, ... т-й управлянхцие входы дешифратора подключены к выходу первого, второго. 4312 ..., т-го разрядов т-разрядов двоичного счетчике формирователя импульсоа синхронизации шкротно-импульсного модулятора, выход первого логического элемента 2И-НЕ также подключен к входу формирователя пилообразного напряжения формирователя импульсов синхронизации широтно-импульсного модулятора, отличающийся тем, что, с целью расширения функциональных возможностей путем обеспечения возможности работы с различньи числом силозых преобразовательных ячеек, первый информационный }сод мультиплексора соединен с минусовой шиной источника питания блока управления, второй, третий, ..., N-й информационные входы мультиплексора подключены соответственно к второму, третьему, ..., N-му выходам дешифратора, а выход мультиплексора соединен с входом установки в О т-разрядного двоичного счетчика формирователя импульсов синхронизации широтно-импульсного модулятора.

Гп

п

п

п

о.

п пппппппппппппппппппппппг

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный импульсный стабилизатор напряжения | 1983 |

|

SU1156032A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265741A1 |

| Многофазный импульсный стабилизатор | 1982 |

|

SU1070528A1 |

| Многофазный импульсный стабилизатор | 1982 |

|

SU1019413A1 |

| Блок управления многофазным импульсным стабилизатором | 1983 |

|

SU1123085A1 |

| Многофазный импульсный стабилизатор | 1984 |

|

SU1196830A1 |

| Многофазный импульсный стабилизатор напряжения | 1987 |

|

SU1483438A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1317415A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1302255A1 |

| Блок управления многофазным импульсным стабилизатором напряжения | 1987 |

|

SU1467704A1 |

Изобретение относится к,вторичным источникам питания радиоаппаратуры. Целью изобретенияявляется расширение функциональных возможностей многофазного импульсного стабилизатора путем обеспечения возможности работы с различным числом силовых преобразовательных ячеек. Цель достигается тем, что первый информагщонный вход мультиплексора 22 соединен с минусовой шиной источника питания 18 блока 4 управления, а второй, третий, N-й информационные входы подключены соответственно к второму, третьему, ..., N-му выходам дешифратора 13. При этом выход мультиплексора 22 соединен с входом установки. в О т-разрядного двоичного счетчика 19 формирователя 10 импульсов синхронизации широтно-импульсного модулятора 11. 3 ил.

П

П.

п

| Многофазный импульсный стабилизатор напряжения | 1983 |

|

SU1156032A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Авторское свидетельство СССР № 1183949, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-10-23—Публикация

1985-05-23—Подача