Изобретение относится к радиотехнике и.может быть использовано в системах автоматики и связи.

Целью изобретения является повышение точности.

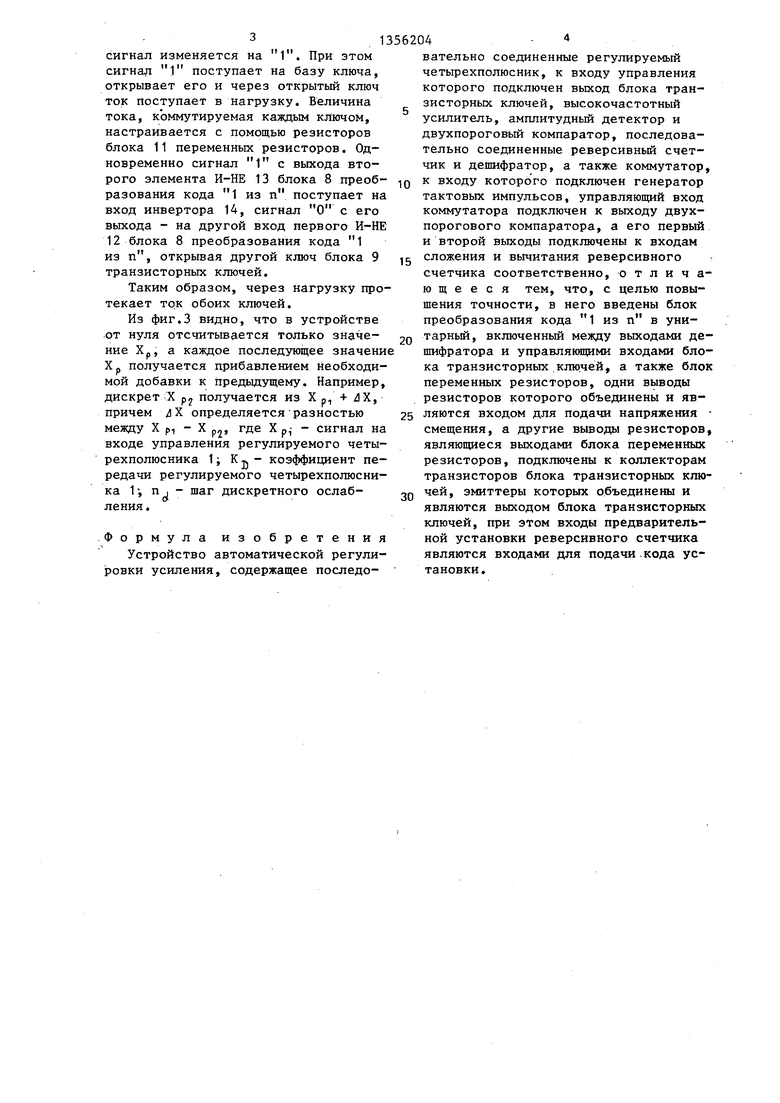

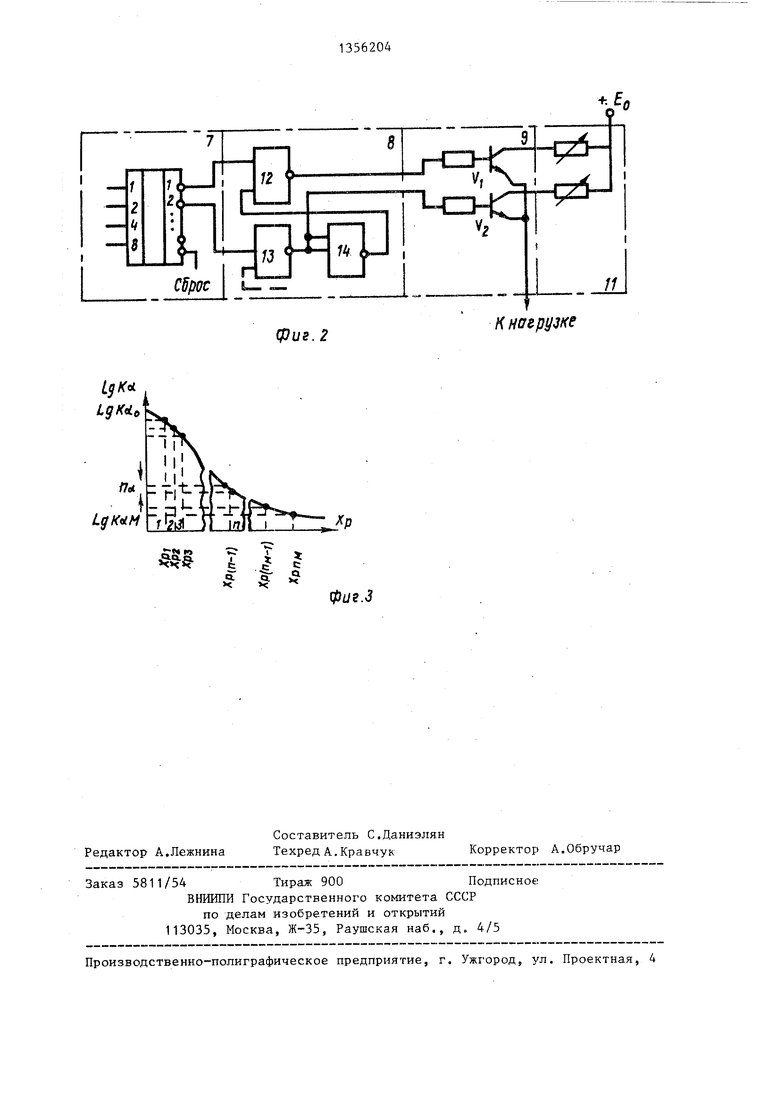

На фкг.1 показана структурная электрическая схема предлагаемого устройства-; на фиг.2 - принципиальная электрическая схема блока преобразования кода 1 из п в унитарный, блока транзисторных ключей и блока переменных резисторов ; на фиг. 3 - графический расчет сопряжения, состоящего из дешифратора, блока преобразо- g фиксированное реверсивным счетчиком

вания кода 1 из п в унитарный, блока транзисторных ключей и блока переменных резисторов, с регулировочной характеристикой регулируемого четырехполюсника .

Устройство автоматической регулировки усиления содержит регулируемый четырехполюсник 1, высокочастотный усилитель 2, амплитудный детектор 3, двухпороговый компаратор 4, коммутатор 5, реверсивный счетчик 6, дешифратор 7, блок 8 преобразования кода 1 из п в унитарный, блок 9 транзисторных ключей, генератор 10 тактовых импульсов и блок 11 переменных резисторов, а также первый и второй элементы И-НЕ 12 и 13 и инвертор 14, входящие в блок 8 преобразования.

Устройство работает следующим образом.

В исходном состоянии сигнал с выхода регулируемого четырехполюсника 1 через высокочастотный усилитель 2 поступает на вход амплитудного детектора 3 и после детектирования в виде постоянного напряжения подается на вход двухпорогового компаратора 4. При значении регулируемого сигнала Uj3 XQ, (X oj и X 0 - опорные напряжения двухпорогового компаратора 4) сигнал / +1 открывает коммутатор 5 и подключает генератор 10 тактовых импульсов к входу сложения реверсивного счетчика 6. В результате реверсивный счетчик 6 заполняется пропорционально времени существования значений ,. Число импульсов, поступающих в реверсивный счетчик 6, в виде двоичного кода на его выходе подается на дешифратор 7 и далее через блок 8 преобразования кода 1 из п на управляющие входы блока транзисторных ключей 9 и включает число транзисторных ключей, соответствую30

35

40

50

55

6, с помощью дешифратора 7, блока 8 преобразования кода из п и блока 9 транзисторных ключей, поддерживает сигнал Хр на стационарном уровне.

2Q При значении Uj, X на выходе двухпорогового компаратора 4 формируется сигнал :/ -1, который через коммутатор 5 подключает генератор 10 тактовых импульсов к выходу вычита25 ния реверсивного счетчика 6. Накопленное в реверсивном счетчике 6 число уменьшается, а следовательно, с помощью дешифратора 7, блок 8 преобразования кода из п и блока транзисторных ключей 9 снижается величина X . В результате коэффициент пере дачи увеличивается и величина U возрастает. Процесс заканчиваете в момент, когда возрастающее Uj входит в зону .

Например, при поступлении от реверсивного счетчика 6 четырехразрядного двоичного кода дешифратор 7 пре образует его в десятичный код и выдает сигнал логического нуля (благодаря наличию инверсных выходов) на вход первого элемента И-НЕ 12 блока 8 преобразования кода 1 из п Если в реверсивный счетчик 6 поступило два импульса, то на вход дешифратора 7 поступает код 0010 и в результате с второго выхода дешифратора 7 на второй элемент И-НЕ 13 блока 8 преобразования кода 1 из п посту пает сигнал О вместо 1 в исходном состоянии.

Поскольку в исходном состоянии на все входы второго элемента И-НЕ 13 блока 8 преобразования кода 1 из п поступают сигналы 1, а при поступлении указанного кода на один вход второго элемента И-НЕ 13 блока 8 преобразования кода 1 из п поступает О, на выходе этого элемента

щее сигналам с выхода блока 8 преобразования кода 1 из п. При этом токи от каждого ключа поступают на вход управления регулируемого четырехполюсника 1. Регулирующий сигнал Хр в данном случае изменяет коэффициент передачи до тех пор, пока регулируемый сигнал и2 не .попадет в зону и XPJ - Хд . При этом сигнал с/ становится равным нулю и коммутатор 5 отключает генератор 10 тактовых импульсов от входа сложения реверсивно- .го счетчика 6. Число импульсов, за0

5

0

0

5

6, с помощью дешифратора 7, блока 8 преобразования кода из п и блока 9 транзисторных ключей, поддерживает сигнал Хр на стационарном уровне.

Q При значении Uj, X на выходе двухпорогового компаратора 4 формируется сигнал :/ -1, который через коммутатор 5 подключает генератор 10 тактовых импульсов к выходу вычита5 ния реверсивного счетчика 6. Накопленное в реверсивном счетчике 6 число уменьшается, а следовательно, с помощью дешифратора 7, блок 8 преобразования кода из п и блока транзисторных ключей 9 снижается величина X . В результате коэффициент передачи увеличивается и величина U возрастает. Процесс заканчиваете в момент, когда возрастающее Uj входит в зону .

Например, при поступлении от реверсивного счетчика 6 четырехразрядного двоичного кода дешифратор 7 преобразует его в десятичный код и выдает сигнал логического нуля (благодаря наличию инверсных выходов) на вход первого элемента И-НЕ 12 блока 8 преобразования кода 1 из п. Если в реверсивный счетчик 6 поступило два импульса, то на вход дешифратора 7 поступает код 0010 и в результате с второго выхода дешифратора 7 на второй элемент И-НЕ 13 блока 8 преобразования кода 1 из п поступает сигнал О вместо 1 в исходном состоянии.

Поскольку в исходном состоянии на все входы второго элемента И-НЕ 13 блока 8 преобразования кода 1 из п поступают сигналы 1, а при поступлении указанного кода на один вход второго элемента И-НЕ 13 блока 8 преобразования кода 1 из п поступает О, на выходе этого элемента

сигнал изменяется на 1. При этом сигнал 1 поступает на базу ключа, открывает его и через открытый ключ ток поступает в нагрузку. Величина тока, коммутируемая каждым ключом, настраивается с помощью резисторов блока 11 переменных резисторов, Одновременно сигнал 1 с выхода второго элемента И-НЕ 13 блока 8 преоб- разования кода 1 из п поступает на вход инвертора 14, сигнал О с его выхода - на другой вход первого И-НЕ 12 блока 8 преобразования кода 1 из п, открьгаая другой ключ блока 9 транзисторных ключей.

Таким образом, через нагрузку протекает TQK обоих ключей.

Из фиг.З видно, что в устройстве от нуля отсчитывается только знача- ние Хр, а каждое последующее значени X р получается прибавлением необходимой добавки к предьщущему. Например, дискрет X р2 получается из X р, + ЗХ, причем дХ определяется разностью между X р1 - X pj, где X р,- - сигнал на входе управления регулируемого четырехполюсника 1; К jj - коэффициент передачи регулируемого четырехполюсника 1-, п , - щаг дискретного ослаб- ления.

Формула изобретения Устройство автоматической регулировки усиления, содержащее последовательно соединенные регулируемый четьфехполюсник, к входу управления которого подключен выход блока транзисторных ключей, высокочастотный усилитель, амплитудный детектор и двухпороговый компаратор, последовательно соединенные реверсивньй счетчик и дешифратор, а также коммутатор, к входу которого подключен генератор тактовых импульсов, управляющий вход коммутатора подключен к выходу двух- порогового компаратора, а его первый и второй выходы подключены к входам сложения и вычитания реверсивного счетчика соответственно, отличающееся тем, что, с целью повышения точности, в него введены блок преобразования кода 1 из п в унитарный, включенный между выходами дешифратора и управляющими входами блока транзисторных ключей, а также блок переменных резисторов, одни выводы резисторов которого объединены и являются входом для подачи напряжения смещения, а другие выводы резисторов, являюпщеся выходами блока переменных резисторов, подключены к коллекторам транзисторов блока транзисторных ключей, эмиттеры которых объединены и являются выходом блока транзисторных ключей, при этом входы предварительной установки реверсивного счетчика являются входами для подачи, кода установки.

С§рос

фиг. 2

К нагрузке

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматической регулировки усиления | 1988 |

|

SU1626329A1 |

| ПОЗИЦИОННЫЙ РЕГУЛЯТОР | 1992 |

|

RU2047210C1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1481887A1 |

| Усилитель мощности | 1987 |

|

SU1532994A1 |

| СИСТЕМА АВТОМАТИЗИРОВАННОГО КОНТРОЛЯ | 1991 |

|

RU2006896C1 |

| СПОСОБ РЕГУЛИРОВАНИЯ МОЩНОСТИ ПЕРЕДАЧИ ЗЕМНЫХ СТАНЦИЙ СЕТИ СПУТНИКОВОЙ СВЯЗИ, УСТРОЙСТВО РЕГУЛИРОВАНИЯ МОЩНОСТИ ПЕРЕДАЧИ ЗЕМНОЙ СТАНЦИИ И ФОРМИРОВАТЕЛЬ УПРАВЛЯЮЩЕГО СИГНАЛА | 2001 |

|

RU2214682C2 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1156258A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛЫ ВРЕМЕНИ | 2014 |

|

RU2552605C1 |

| Устройство измерения времени ограничения тока транзисторными коммутаторами систем зажигания | 1989 |

|

SU1758279A1 |

| Измеритель мощности переменного тока | 1980 |

|

SU883764A1 |

Изобретение может быть использовано в системах автоматики и связи. Цель изобретения - повышение точности. Устройство содержит регулируе- мый четырехполюсник 1, высокочастотный усилитель 2, амплитудный детек- - тор 3, двухпороговый компаратор 4, коммутатор 5, реверсивный счетчик 6, дешифратор 7, блок 9 транзисторных ключей, генератор 10 тактовых импульсов. Вновь введены блок 8 преобразования кода 1 из п в унитарный и блок 11 переменных резисторов. 3 ил. сл со СП а ю

LgKoiH

i

с

5

фие.З

Редактор А.Лежнина

Составитель С.Даниэлян Техред А.Кравчук

Заказ 5811/54 Тираж 900Подписное

ВНРШПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор А.Обручар

| Царенко В.Т | |||

| и др | |||

| Автоматические устройства СВЧ | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Говорящий кинематограф | 1920 |

|

SU111A1 |

Авторы

Даты

1987-11-30—Публикация

1986-07-02—Подача