Изобретение относится к технике связи и может использоваться в приемных устройствах систем передачи информации.

Цель изобретения - повышение помехоустойчивости.

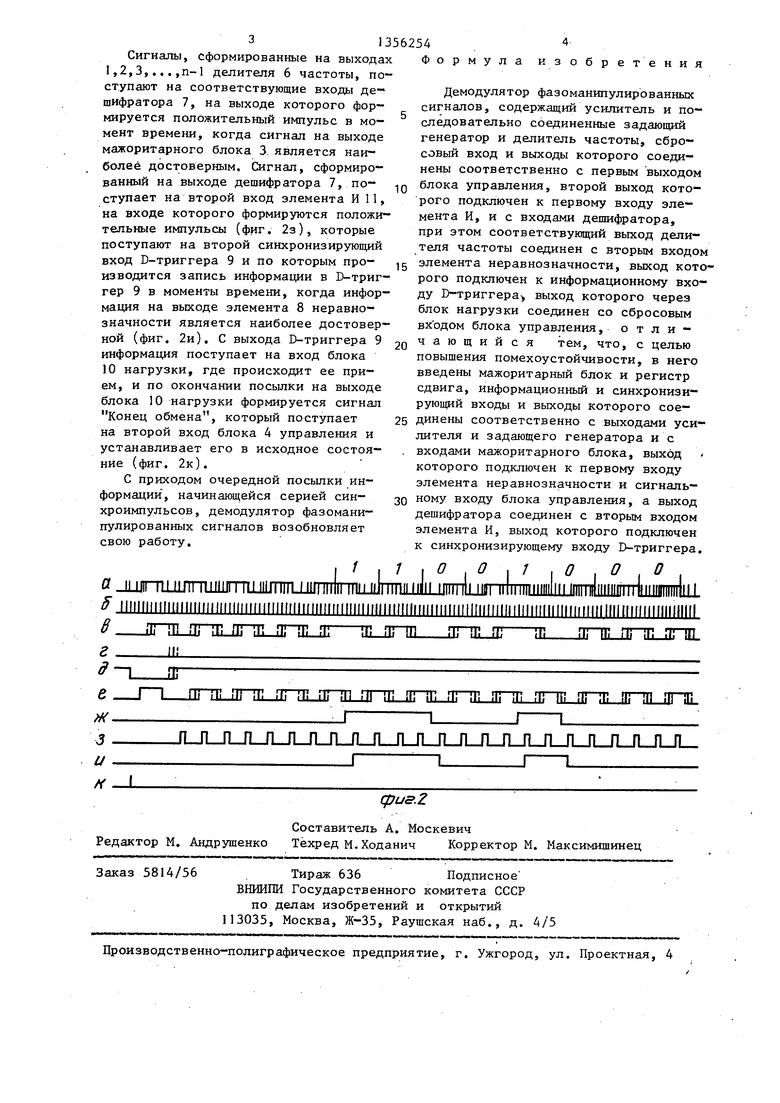

На фиг. 1 представлена структурная электрическая схема предложенного демодулятора; на фиг. 2 - эпюры напряжений, поясняющие его работу.

Демодулятор фазоманипулированных сигналов содержит усилитель 1, регистр 2 сдвига, мажоритарньм блок 3, блок 4 управления, задающий генератор 5, делитель 6 частоты, дешифратор 7, элемент 8 неравнозначности, 1 -триггер 9, блок 10 нагрузки, элемент И 11.

Демодулятор работает следующим об- разом.

Каждая информационная посылка состоит из импульсов синхронизации и определенного числа бит информации. Елок 10 нагрузки представляет собой приемное устройство, которое принимает информацию, определяет конец посылки и формирует сигнал Конец обмена. Задающий генератор 5 выбирается с частотой, близкой к частоте случайной помехи (фиг. 1), присутствующей во входном сигнале, причем тактовая частота должна быть в 2 m раз выше частоты входного сигнала, где m - целое нечетное число, что необходимо для обеспечения правильной работы мажоритарного блока 3, разрядность которого, а также разрядность регистра 2 сдвига равна т.

Блок 4 управления устанавливается в исходное состояние сигналом Конец обмена, .поступающим на его второй вход с выхода блока 10 нагрузки в начале работы и после завершения каж- цой посылки информации, т.е.. на его первом и втором выходе устанавливается состояние О. Информационная посылка в виде фазоманипулированного сигнала несущей частоты с входа устройства поступает на вход усилителя 1, усиливается до уровня 1 и с вы хода усилителя 1 (фиг. 2а) поступает на первый информационньш вход регистра 2 сдвига, на второй синхронизирующий вход которого поступают импульс тактовой частоты с выхода задающего генератора 5 (фиг, 26), по которым в регистр 2 сдвига производится запись очередного значения входного сигнала

5

5

Q

0

5

0

5

0

5

поступающего на- первый информационный вход, и сдвиг на один разряд информации, записанной в предыдущих тактах, С выходов регистра 2 сдвига информация поступает на входы мажоритарного блока 3, на выходе которого формируется сигнал уровня 1, если большинство разрядов регистра 2 сдвига находится в состоянии 1, и уровня о, если большинство разрядов регистра 2 сдвига находится в состоянии О (фиг. 2в), который поступает на первый вход блока 4 управления и на первый вход элемента 8 неравнозначности. При поступлении на первый вход блока 4 управления первого спада первого синхроимпульса данной посылки на первом выходе его формируется положительный импульс сброса (фиг. 2г), который поступает на второй сбросовый вход делителя 6 частоты и устанавливает на его выходах состояние О, на втором выходе блока 4 управления в то же время формируется уровень 1 (фиг. 2д), который поступает на первый вход элемента И 11 и разрешает его работу.

С приходом импульсов тоты с выхода задающего на первый, счетный вход частоты на его выходе п формируется сигнал с периодом, равным периоду сигнала, сфорт-шрованного на выходе мажоритарного блока 3, и с минимальным фазовым сдвигом относительно этого сигнала при кодировании О, С выхода п делителя 6 частоты сигнал поступает на второй вход элемента 8 неравнозначности (фиг. 2е) на выходе которого при поступлении на первый вход кода О формируется уровень О при поступлении кода 1 на выходе формируется уровень. Сигнал, сформированный на выходе элемента 8 не-.; равнозначности (фиг. 2ж), поступает на первый информационный вход D-триг- гера 9,

При наличии случаз ной помехи во входном сигнале возможно появление дополнительного фазового сдвига между сигналом, сформированным на выходе мажоритарного блока 3, и эталонным, формируемым на выходе п делителя частоты 6, что приводит к недостоверности информации на фронтгх сигда-, ла, сформи;рованного на выходе элемен- та 8 неравнозначности.

тактовой час- генератора 5 делителя 6

313

Сигналы, сформированные на выходах 1,2,3,...,п-1 делителя 6 частоты, поступают на соответствующие входы дешифратора 7, на выходе которого формируется положительный импульс в момент времени, когда сигнал на выходе мажоритарного блока 3. является наиболее достоверным. Сигнал, сформированный на выходе дешифратора 7, поступает на второй вход элемента И 11, на входе которого формируются положительные импульсы (фиг. 2з), которые поступают на второй синхронизирующий вход D-триггера 9 и по которым про- изводится запись информации в D-триг- гер 9 в моменты времени, когда информация на выходе элемента 8 неравнозначности является наиболее достоверной (фиг. 2и). С выхода D-триггера 9 информация поступает на вход блока 10 нагрузки, где происходит ее прием, и по окончании посылки на выходе блока 10 нагрузки формируется сигнал

Конец обмена, который поступает на второй вход блока 4 управления и устанавливает его в исходное состояние (фиг. 2к).

С приходом очередной посылки информации, начинающейся серией синхроимпульсов, демодулятор фазоманипулированных сигналов возобновляет свою работу.

О JшпluшпшJJгттlJJiяmJJImrrlI

llllllllllllllllllllillllllllllllllllllllllfllllllllllllllllllllllllllllllllllllllllllllllllllllllllllllllillllllllHIIfllllllllllN

в |ТГТП ГТГ7П ПГТП ПГТП ГТГ

гш

е I 1 ПГТП ПГТП гтгтп {тгтп .тпл ifnri

ж.

3 .

и

/г

JUlJLJlJlJUUlJLJl JUULJLJl n

Т.

I

сриг.2

Редактор М. Андрушенко

Составитель А. Москевич

Техред М.Ходанич Корректор М. Максимишинец

5814/56

Тираж 636 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

изобретения

0

Формула g

0

Демодулятор фазоманипулированных сигналов, содержащий усилитель и последовательно соединенные задающий генератор и делитель частоты, сбросовый вход и выходы которого соединены соответственно с первым выходом блока управления, второй выход которого подключен к первому входу элемента И, и с входами дешифратора, при этом соответствующий выход делителя частоты соединен с вторым входом элемента неравнозначности, выход которого подключен к информационному входу О-триггера выход которого через блок нагрузки соединен со сбросовым вх одом блока управления, отличающийся тем, что, с целью

повышения помехоустойчивости, в него введены мажоритарный блок и регистр сдвига, информационный и синхронизирующий входы и выходы которого сое25 динены соответственно с выходами усилителя и задающего генератора и с . входами мажоритарного блока, выход которого подключен к первому входу элемента неравнозначности и сигналь0 ному входу блока управления, а выход дешифратора соединен с вторым входом элемента И, выход которого подключен к синхронизирующему входу D-триггера.

ТЛ ТПП ГТПГ ЦТ

HL

I l Я iii i; ттт

Т.

сриг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Демодулятор фазоманипулированных сигналов | 1987 |

|

SU1443200A1 |

| Демодулятор фазоманипулированных сигналов | 1980 |

|

SU930645A1 |

| Устройство для сопряжения ЦВМ с магнитофоном | 1985 |

|

SU1317445A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1984 |

|

SU1188745A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном звукозаписи | 1985 |

|

SU1260969A2 |

| Синхронизирующее устройство | 1984 |

|

SU1213528A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1985 |

|

SU1277122A1 |

| Преобразователь серии импульсов в прямоугольный импульс | 1986 |

|

SU1422382A1 |

| Преобразователь серии импульсов в прямоугольный импульс | 1985 |

|

SU1324096A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

Изобретение относится к технике связи и повышает помехоустойчивость. Устройство содержит усилитель I, блок 4 управления, задаю11Ц1Й генератор 5, делитель 6 частоты, дешифратор 7, элемент 8 неравнозначности, D-триг- гер 9, блок 10 нагрузки, элемент И 11. Вновь введены регистр 2 сдвига и мажоритарны блок 3. 2 ил. вх. (Я со О1 О) ю СП 4 fpuz.f

| Демодулятор фазоманипулированных сигналов | 1980 |

|

SU930645A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-11-30—Публикация

1986-05-11—Подача