ходы распределителя импульсов подключены к соответствующим входам блока измерения рассогласования, информационный и тактовый входы которого соединены соответственно с выходами ндкопителя и распределителя импульсов .

2. Устройство по П.1, отличающееся тем, что, с целью повышения помехоустойчивости и быстродействия в условиях помех канала связи, выход блока совпадения подсоединей к объединенным вторым сбросовым входам решающего блока и триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU949832A1 |

| Приемник синхросигнала | 1981 |

|

SU1092745A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU987836A1 |

| Устройство синхронизации | 1980 |

|

SU982205A1 |

| Устройство синхронизации | 1983 |

|

SU1095435A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| Устройство цикловой синхронизации (его варианты) | 1979 |

|

SU864586A1 |

| Устройство синхронизации по циклам | 1980 |

|

SU886289A1 |

1. УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ, содержащее регистр сдвига, выходы которого подключены к объединенным входам решакяцего блока и дешифратора, выход которого подключен к объединенным входам первого и второго анализаторов и блока управления, первый установочный вход которого соединен с выходом первого анализатора, а выход блока управления подключен к объединенным сбросовым входам первого накопителя и делителя частоты, выход которого подключен к объединенным тактовым входам первого анализатора и первого накопителя, выход которого подключен к первому входу блока совпадения, второй вход которого соединен с выходом триггера, а выход блока подключен к установочному входу распределителя импульсов и к объединенным первым сбросовым входам второго и третьего накопителей, выход распределителя импульсов подключен к объединенным тактовым входам решающего блока и второго анализатора, первый выход которого подключен к первому сбросоBONfy входу решающего блока, второму сбросовому входу второго накопителя и к тактовому входу третьего накопителя, а второй выход второго анализатора - к управляющему входу решающего блока, к тактовому входу второго накопителя и к второму сбросовому входу третьего накопителя, выходы второго накопителя подключены к первым входам первого коммутатора, выход которого подключен к первому установочному входу триггера, выход формирователя сигнала Сброс йодключен к объединенным вторым установочным входам блока управления и триггера, при этом информационный вход регистра сдвига и объединенные тактовые входы делителя частоты, распределителя импульсов и регистра сдвига являются соответственно инфор(Л мационным и тактовым входами устройства, а выходы распределителя импульсов являются выходами устройства, о тС личающееся тем, что, с цес лью повьппения помехоустойчивости и быстродействия при сбоях в работе устройства, в него введены последовательно соединенные блок измерения рассогласования и блок умножения и последовательно соединенные блок памяти и второй коммутатор, другие : входы которого соединены с соответствующими выходами третьего накопителя, а выход второго коммутатора подключен к сбросовому входу блока памяти и к первому сбросовому входу триггера, выходы решающего блока подключены к объеднненньм входам блока умножения и блока памяти, управляющий вход которого соединен с выходом первого коммутаора, а установочный вход блока памяти соединен с выходом формирователя сигнала Сброс, а вы

Изобретение относится к электросвязи и может быть использовано для циклового .фазирования систем переда чи дискретных сигналов. Известно устройство для цикловой синхронизации, содержащее регистр сдвига, выходы которого через дешиф ратор подключены к информационным входам первого и второго анализаторов, к тактовому входу первого анализатора подключен соответствующий выход распределителя импульсов, выходы первого анализатора подключены соответственно к тактовым входам первого и второго накопителей, выход второго анализатора соединен через блок управления со сбросовым входом делителя частоты, выход которого соединен с тактовым входом второго анализатора, третьего накопителя и с первым входом блока совпадения, к второму входу которого подключен выход третьего накопителя, а вькод блока совпадения подключен к установочному входу распределителя импульсов, тактовый вход которого объединен с тактовыми входами регистра сдвига и делителя частоты С11. Недостатками устройства являются низкие помехоустойчивость и быстродействие . Наиболее близким к предлагаемому является устройство для цикловой синхронизации, содержащее регистр сдвига, выходы которого подключены к объединенным входам решанщего блока и дешифратора, выход которого подключенным к объединенным входам первого и второго анализаторов и блока управления, первый установоч ный вход которого соединен с выходом первого анализатора, выход блока управления подключен к объединенным входам первого накопителя и делителя частоты, выход которого подключен к объединенным тактовым входам анализатора и первого накопителя, вькод которого подключен к первому входу блока совпадения, второй вход которого соединен с выходом триггера, а вькод блока совпадения подключен к у -тановочному входу распределителя импульсов и объединенным первым сбросовым входам второго и третьего накопителей, выход распределителя импульсов подключен к объединенным тактовым входам решающего блока и второго анализатора, первый выход которого подключен к первому сбросовому входу решающего блока, второму сбросовому входу второго накопителя, и к тактовому входу третьего накопителя, а второй выход второго анализатора подключен к управляющему входу решающего блока, к тактовому входу второго накопителя и к второму сбросовому входу третьего накопителя, выходы второго накопителя подключены к первым входам первого коммутатора, выход которого подключен к первому установочному входу триггера, вьскод формирователя сигнала Сброс подключен к объединенным вторым установочным входам блока управления и триггера, при этом информационный вход регистра сдвига и объединенные тактовые входы делителя частоты, распределителя импульсов и регистра сдвига являются соответственно информационным и тактовы 4 входами устройства, а выходы распределителя импульсов являются выходами устройства 12 Недостатками устройства для цикло-. ой синхронизации являются низкие

помехоустойчивость и быстродействие.

Цель изобретения - повышение помехоустойчивости и быстродействия при сбоях в работе устройства и в условиях помех канала связи.

Для достижения поставленной цели в устройство для цикловой синхронизации, содержащее регистр сдвига, выходы которого подключены к объединенным входам решающего блока и да- шифратора, выход которого подключен к объединенным входам первого и второго анализаторов и блока управления первьй установочный вход которого соединен с выходом первого анализато ра, а вьЕход блока управления подключен к объединенным сбросовым входам первого накопителя и делителя частот выход которого подключен к объединенным входам первого анализатора и первого накопителя, выход которого подключен к первому входу блока совпадения, второй вход которого соединен с выходом триггера, а выход блока совпадения подключен к установочному входу распределителя импульсов и к объединенным первым сбросовым входам второго и третьего накопителей, выход распределителя импульсов подключен к объединенным тактовьт входам решающего блока и второго анализатора, первый выход которого подключен к первому сбросовому входу решающего блока, второму сбросовому входу второго накопителя, и к тактовму входу третьего накопителя, а второй вход второго анализатора - к управляющему входу решающего блока, к тактовому входу второго накопителя и к второму сбросовому входу третьего накопителя, выходы второго накопителя подключены к первым входам первого коммутатора,, выход которого подключен к первому устйновочному входу триггера, выход формирователя сигнала Сброс подключен к объединенным вторым установочным входам блока управления и триггера, при этом информационный вход регистра сдвига и объединенные тактовые входы делителя частоты, распределителя импульсов и регистра сдвига являются соответственно информационным и тактовым входами устройства, а выходы распределителя импульсов являются выходами устройства, введены последовательно соединенные

блок измерения рассогласования и блок умножения-и последовательно соединенные блок памяти и второй коммутатор, другие входы которого соединены с соответствующими выходами третьего накопителя, а выход второго коммутатора подключен к сбросовому входу блока памяти и первому сбросовому входу триггера, выходы решающего блока подключены к объединенным входам блока умножения и блока памяти, управляющий вход которого соединен с выходом первого коммутатора, а установочный вход блока памяти соединен с выходом формирователя сигнала Сброс, а выходы распределителя импульсов подключены к соответствующим входам блока измерения рассогласования, информационный и тактовый входы которого соединены соответственно с выходами накопителя и распределителя импульсов.

Выход блока совпадения может быть подсоединен к объединенным вторым сбросовым входам решающего блока и триггера.

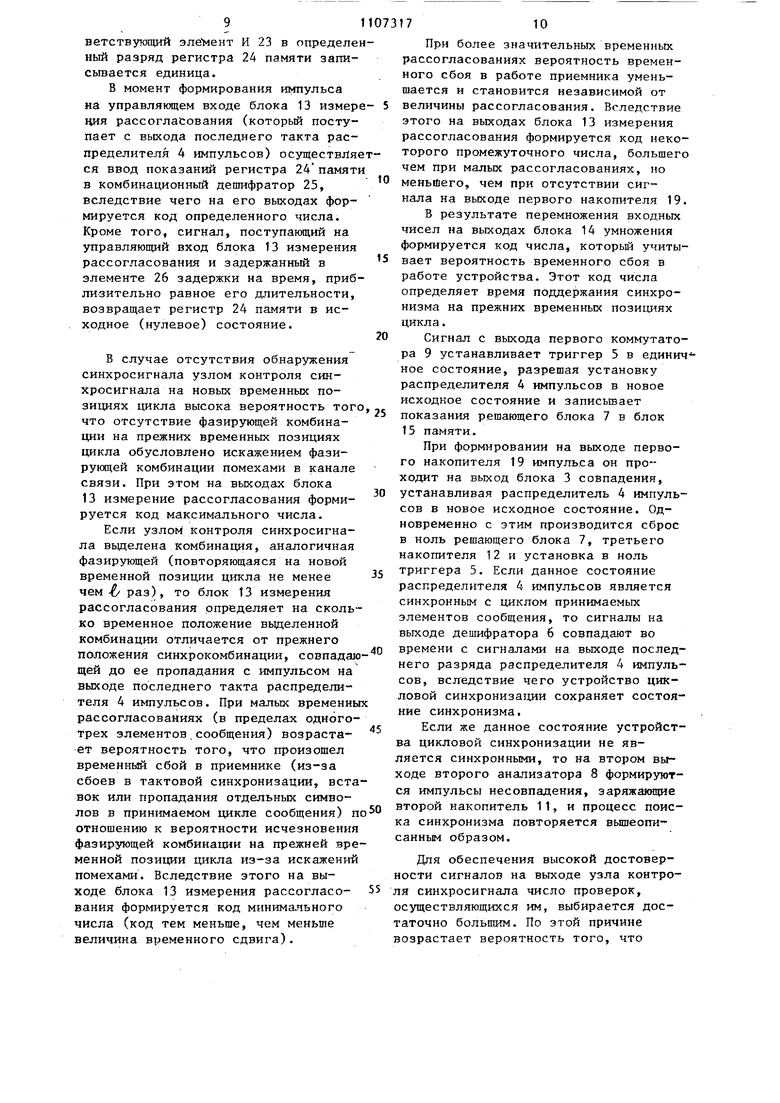

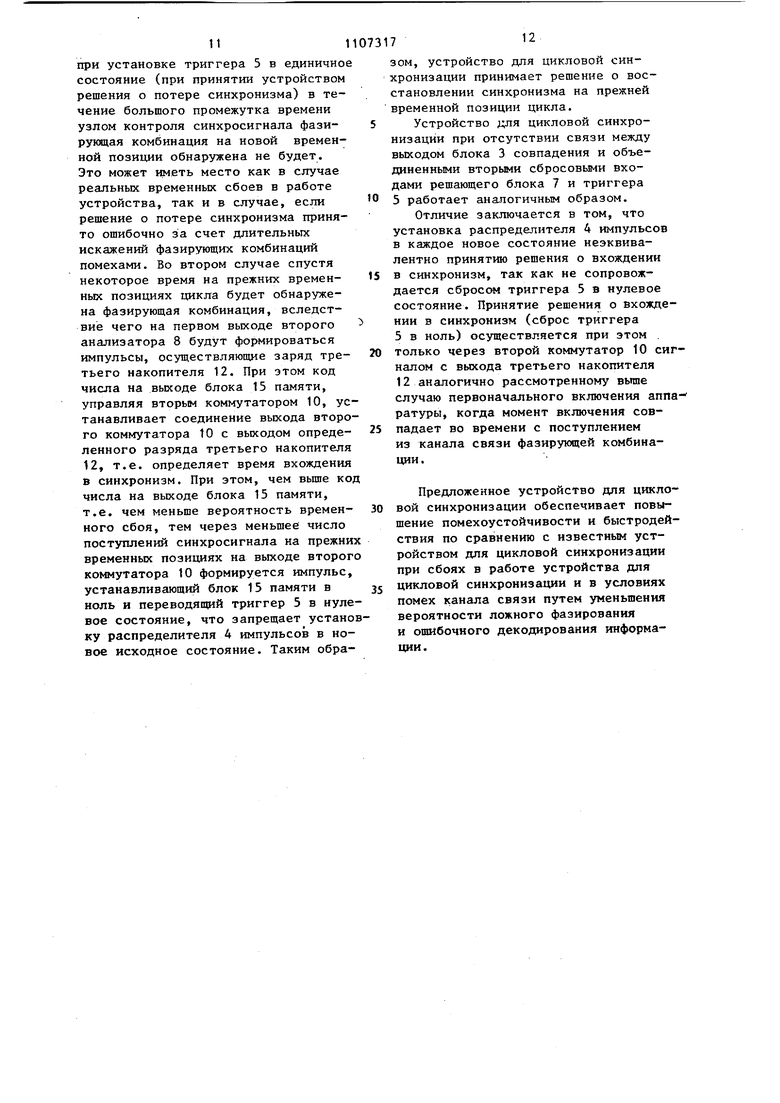

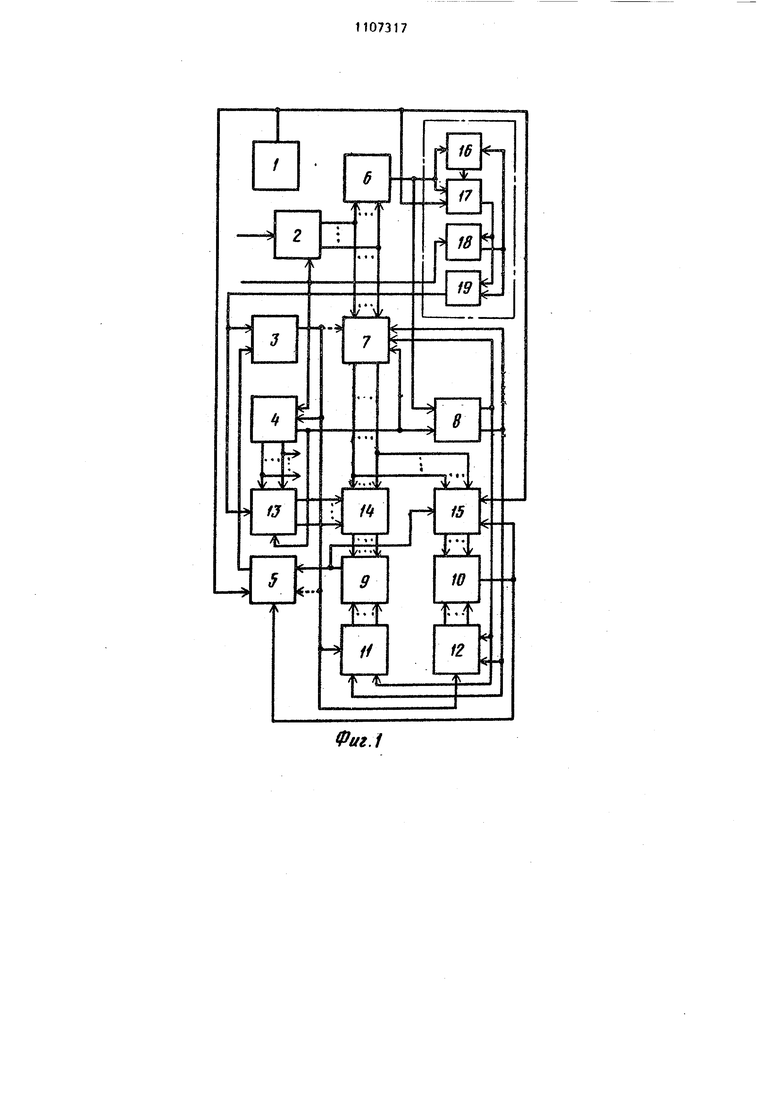

На фиг.1 приведена структурная электрическая схема устройства для цикловой синхронизации на фиг.2 структурная электрическая схема решающего блока; на фиг.З - структурная электрическая схема блока измерения рассогласования.

Устройство для цикловой синхронизации (фиг.1) содержит формирователь 1 сигнала Сброс, регистр 2 сдвига, блок 3 совпадения, распределитель 4 импульсов, триггер 5, деошфратор 6, решающий блок 7, второй анализатор 8, первый и второй коммутаторы 9 и 10, второй и третий накопители 11 и 12, блок 13 измерени рассогласования, блок 1А умножения, блок 15 памяти, первый анализатор 16, блок 17 управления, делитель 18 частоты и первый накопитель 19. Реша щий блок 7 (фиг.2) содержит формирователь 20 эталонной фазирующей комбинации, элемент 21 неравнозначности и усреднитель 22. Блок 13 измерения рассогласования (фиг.З) содержит элементы И 23, регистр 24 памяти, комбинационный.дешифратор 25 и элемент 26 задержки.

Устройство для. цикловой синхронизации работает следующим образом.

В момент включения аппаратуры сигнал с выхода формирователя 1 сиг$11

нала Сброс (фиг.1) устанавливает триггер 5 в единичное состояние, устанавливает на входе блока 15 памяти код минимального числа (уровень логической единицы на последнем выходе) и подготавливает к работе блок

17управления. Одновременно с этим н информационный вход устройства поступает .последовательность принимаемых элементов сообщения, а на его тактовый вход поступает последовательност тактовых импульсов, следующих с часттой принимаемых элементов сообщения.

Если момент включения аппаратуры совпал по времени с поступлением на первый вход устройства фазируклцей комбинации, то сигналы на выходе последнего такта распределителя 4 импульсов (как и на выходе делителя

18частоты) совпадают с сигналом на выходе дешифратора 6 (свидетельствующего об обнаружении в составе принимаемых сообщений комбинации, аналогичной фазирующей), вследствие чего на первом выходе второго анализатора 8 в каждом цикле приема формируются сигналы, заполняющие третий накопитель 12, Минимальный

код числа на выходе блока 15 памяти устанавливает соединение выхода второго коммутатора 10 с вькодом последнего из разрядов третьего накопителя 12 (т.е. устанавливается максимальное число проверок поступления фазирующей комбинации на одной и той же позиции цикла). При заполнении третьего накопителя 12 сигнал с выхода его последнего разряда через второй коммутатор 10 сбрасьгоает в ноль блок 15 памяти и переводит в нулевое состояние триггер 5, сигнал с выхода которого закрывает блок 3 совпадения по первому входу для прохождения сигналов на установку распределителя 4 импульсов в новое исходное состояние, т.е. устройство цикловой синхронизации принимает решение о нахождении в состоянии циклового синхронизма.

Если момент-- включения аппаратуры не совпал во времени с поступлением из канала связи фазирующей комбинации, то узел контроля синхросигнала, содержащий первый анализатор 16, блок 17 управления, делитель 18 частоты и первый накопитель 19, начинает проверку поступления синхросиг176

нала на позиции цикла, соответствующей во времени формированию первого же сигнала на выходе дешифратора 6.

На тактовый вход делителя 18 частоты поступает последовательность тактовых импульсов (их период равен длительности принимаемых элементов сообщения), вследствие чего на выходе делителя .18 частоты формируются тактовые импульсы с периодом следования, равным длительности цикла принимаемых элементов сообщения. На информационные входы первого анализатора 16 и блока 17 управления поступают импульсы, свидетельствующие об обнаружении в составе принимаемых сообщений комбинаций элементов, аналогичных фазирующим (т.е. маркерных комбинаций). При совпадении этих сигналов во времени с каждым из сигналов на выходе делителя 18 частоты сигнал на выходе первого анализатора 16 не формируется, вследствие чего блок 17 управления продолжает находиться в сброшенном состоянии и сигналы на его выходе не формируются. Поэтому при поступлении с выхода делителя 18 частоты подряд более чем сигналов (где -. коэффициент пересчета счетчика первого накопителя 19), сигналы с выхода делителя 18 проходят в дальнейшем через первый накопитель 19 на выход уэла контроля синхросигнала, В случа если в момент формирования сигнала на выходе делителя 18 частоты на информационные входы первого анализатора 16 и блока 17 управления сигнал не поступает, на выходе первого анализатора 16 формируется импульс, устанавливающий блок 17 управления в состояние готовности. Вследствие этого, первый же импульс, поступивший на информационные входы первого анализатора 16 и блока 17 управления, проходит на выход блока 17 управления, сбрасьгаая первый накопител 19 и делитель 18 частоты в нулевое

состояние и возвращая блок 17 управления в исходное (нулевое) состояние В. результате сброса в ноль первого накопителя 19 прекращается формирование сигнала на выходе узла контроля синхросигнала, а в результате сброса в ноль делителя 19 частоты первый анализатор 16 начинает проверять поступление сигнала на его информационный вход в другой момент рремени (на другой временной позиции цикла принимаемых сообщений). Далее работа узла контроля синхросигнала аналогична вьнпеописанной. Установка блока 17 управления в состояние готовности может быть произведена не только формированием импульса на выходе первого анализатора 16, но и подачей импульса на второй установочньм вход блока 17 управления. Таким образом, узел контроля синхросигнала осуществляет безынерционную проверку поступления синхросигнала на временных позициях цикла, неза висимо от состояния других цепей устройстваС в частности, фазы работы распределителя 4 иьтульсов), Отсутст вие синхросигнала по проверяемой позиции цикла приводит к поиску синхросигнала на других позициях цикла. Решение об обнаружении синхросигнала узел контроля синхросигнала принимае после 8. -кратного поступления импульса на информационный входы перво го анализатора 16 и блока 17 управления, приходящегося во времени на одну и ту же позицию цикла принимаемых сообщений. Если поступающая фазирующая комби нация является синхросигналом, то через i поступлений, т.е. пОсле заполнения первого накопителя 19 на его выходе формируется выходной импульс, который проходит через блок 3 совпадения. Сигнал с выхода блока 3 совпадения устанавливает распределитель 4 импульсов в новое исходное состояние и сбрасывает в ноль триггер 5, т.е. устройство принимает решение о вхождении в синхронизм. При этом сигналы с выхода последнего такта распределителя импульсов совпадают во времени с сигналами на выходе дешифратора 6, т.е. как и ранее производится заряд второго , накопителя 11. Если первый сигнал, выделенный дешифратором 6 не является синхросигналом, то узел контроля синхросиг нала последовательно производит анализ на всех упругих позициях цикла (совпадающих по времени с моментом выделения сигнала на выходе дешифратора 6) до тех пор, пока не будет обнаружен истинный синхросигнал. В случае сбоя в работе передающей части системы передачи (как и в слу1чае сбоя в работе приемной части аппаратуры, если он не связан с отключением напряжения питания), в момент поступления сигнала с выхода последнего такта распределителя 4 импульсов в регистре 2 сдвига оказывается записанной комбинация, значительно отличающаяся от фазирующей, а на втором вькоде второго анализатора 8 формируется сигнал несовпадения, заполняющий второй накопитель 11. Вследствие зтого решающий блок 7 (фиг.2) определяет насколько принятьй сигнал отличается от фазирующей комбинации, осуществляет усреднение этой величины за несколько циклов приема и в соответствии с полученной величиной формирует код определенного числа (формирует сигналы на определенных выходных шинах). При этом, чем меньше соответствует принятая комбинация фазирующей комбинации (т.е. чем вьШ1е вероятность того, что отсутствие фазирующей комбинации обусловлено не искажением фазирукицих комбинаций помехами в канале связи), тем на выходах решающего блока 7 формируется код меньшего числа. Блок 14 умножения осуществляет перемножение кодов чисел, присутствуюищх на выходах решающего блока 7 и блока 13 измерения рассогласования. Код числа на выходах блока 14 умножения посредством первого коммутатора 9 устанавливает требуемьй коэффициент накопления второго накопителя 11 (требуемое время поддержания синхронизма на прежних временных позициях цикла) путем подключения выхода первого коммутатора 9 к выходу определенного разряда второго накопителя 11. Блок 13 измерения рассогласования (фиг.З) определяет величину расфазирования синхросигнала (обнаруженного узлом контроля синхросигнала) относительно импульсов на выходе распределителя 4. I Блок 13 работает следующим образом. Сигнал, свидетельствующий об обнаружении синхросигнала и поступающий на инфо1 1ационный вход блока 13 измерения рассогласования, совпадает во времени с одним из тактов распределителя 4 импульсов,поступающих на выходы блока 13 измерения рассогласовследствие чего через соотвания, 9 ветствующий элемент И 23 в определе ный разряд регистра 24 памяти записьгоается единица. В момент формирования импульса на управляющем входе блока 13 измер ния рассогласования (который поступает с выхода последнего такта распределителя А импульсов) осуществля ся ввод показаний регистра 24 памят в комбинационный дешифратор 25, вследствие чего на его выходах формируется код определенного числа. Кроме того, сигнал, поступающий на управляющий вход блока 13 измерения рассогласования и задержанный в элементе 26 задержки на время, приб лизительно равное его длительности, возвращает регистр 24 памяти в исходное (нулевое) состояние. В случае отсутствия обнаружения синхросигнала узлом контроля синхросигнала на новых временньк позициях цикла высока вероятность тог что отсутствие фазирующей комбинации на прежних временньк позициях цикла обусловлено искажением фазирующей комбинации помехами в канале связи. При этом на вькодах блока 13 измерение рассогласования формируется код максимального числа. Если узлом контроля синхросигнала вьщелена комбинация, аналогичная фазирующей (повторяющаяся на новой временной позиции цикла не менее чем - раз), то блок 13 измерения рассогласования определяет на сколь ко временное положение выделенной комбинации отличается от прежнего положения синхрокомбинации, совпадаю щей до ее пропадания с импульсом на выходе последнего такта распределителя 4 импульсов. При малых временны рассогласованиях (в пределах одноготрех элементов,сообщения) возрастает вероятность того, что произошел временный сбой в приемнике (из-за сбоев Б тактовой синхронизации, вста вок или пропадания отдельных симвоЛ Л.. ч .f..At.4:Ui Х « ,,-.А.4 LtLI Я tJ.U fj X лов в принимаемом цикле сообщения) п отношению к вероятности исчезновения фазирующей комбинации на прежней вре менной позиции цикла из-за искажений помехами. Вследствие этого на выходе блока 13 измерения рассогласования формируется код минимаяьного числа (код тем меньще, чем меньше величина временного сдвига). 17 При более значительных временных рассогласованиях вероятность временного сбоя в работе приемника уменьшается и становится независимой от величины рассогласования. Вследствие этого на выходах блока 13 измерения рассогласования формируется код некоторого промежуточного числа, большего чем при малых рассогласованиях, но меньшего, чем при отсутствии сигнала на выходе первого накопителя 19. В результате перемножения входных чисел на выходах блока 14 умножения формируется код числа, который учитывает вероятность временного сбоя в работе устройства. Этот код числа определяет время поддержания синхронизма на прежних временных позициях цикла. Сигнал с выхода первого коммутатора 9 устанавливает триггер 5 в единич ное состояние, разрешая установку распределителя 4 импульсов в новое исходное состояние и записьтает показания решающего блока 7 в блок 15 памяти. При формировании на выходе первого накопителя 19 импульса он проходит на выход блока 3 совпадения, устанавливая распределитель 4 импульсов в новое исходное состояние. Одновременно с этим производится сброс в ноль решающего блока 7, третьего накопителя 12 и установка в ноль триггера 5. Если данное состояние распределителя 4 импульсов является синхронным с циклом принимаемых элементов сообщения, то сигналы на вькоде дешифратора 6 совпадают во времени с сигналами на выходе последнего разряда распределителя 4 импульсов, вследствие чего устройство цикловой синхронизагдии сохраняет состояние синхронизма. Если же данное состояние устройства цикловой синхронизации не явяется синхронными, то на втором вьгоде второго анализатора 8 формируются импульсы несовпадения, заряжающие Л Л второй накопитель 11, и процесс поиса синхронизма повторяется вьппеоп ианным образом. Для обеспечения высокой достоверости сигналов на выходе узла контроя синхросигнала число проверок, существляющихся им, выбирается досаточно большим. По этой причине озрастает вероятность того, что при установке триггера 5 в единичное состояние (при принятии устройством решения о потере синхронизма) в течение большого промежутка времени узлом контроля синхросигнала фазирующая комбинация на новой временной позиции обнаружена не будет. Это может иметь место как в случае реальных временных сбоев в работе устройства, так и в случае, если решение о потере синхронизма принято ошибочно за счет длительных искажений фазирунэдих комбинаций помехами. Во втором случае спустя некоторое время на прежних временных позициях цикла будет обнаружена фазирующая комбинация, вследствие чего на первом выходе второго анализатора 8 будут формироваться импульсы, осуществляющие заряд третьего накопителя 12. При этом код числа на выходе блока 15 памяти, управляя вторым коммутатором 10, ус танавливает соединение выхода второ го коммутатора tO с выходом определенного разряда третьего накопителя 12, т.е. определяет время вхождения в синхронизм. При этом, чем вьш1е ко числа на выходе блока 15 памяти, т.е. чем меньше вероятность временного сбоя, тем через меньшее число поступлений синхросигнала на прежни временных позициях на выходе второг коммутатора 10 формируется импульс, устанавливающий блок 15 памяти в ноль и переводящий триггер 5 в нуле вое состояние, что запрещает устано ку распределителя 4 импульсов в новое исходное состояние. Таким образом, устройство для цикловой синхронизации принимает решение о восстановлении синхронизма на прежней временной позиции цикла. Устройство для цикловой синхронизации при отсутствии связи между выходом блока 3 совпадения и объединенными вторыми сбросовьми входами решающего блока 7 и триггера 5 работает аналогичным образом. Отличие заключается в том, что установка распределителя 4 импульсов в каждое новое состояние неэквивалентно принятию решения о вхождении в синхронизм, так как не сопровождается сбросом триггера 5 в нулевое состояние. Принятие решения о вхождении в синхронизм (сброс триггера 5 в ноль) осуществляется при этом только через второй коммутатор 10 сигналом с выхода третьего накопителя 12 аналогично рассмотренному выше случаю первоначального включения аппаратуры, когда момент включения совпадает во времени с поступлением из канала связи фазирующей комбинации. Предложенное устройство для цикловой синхронизации обеспечивает повышение помехоустойчивости и быстродействия по сравнению с известным устройством для цикловой синхронизации при сбоях в работе устройства для цикловой синхронизации и в условиях помех канала связи путем уменьшения вероятности ложного фазирования и ошибочного декодирования информации.

Фиг1

fpuz. г

I

23

23

/ Ф

23

23

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство цикловой синхронизации | 1977 |

|

SU623260A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-08-07—Публикация

1981-08-04—Подача