СО

ю

Изобретение относится-к технике связи и может использоваться в приемных устройствах систем передачи информации.

Цель изобретения повышение помехоустойчивости при большом уровне шума входного сигнала.

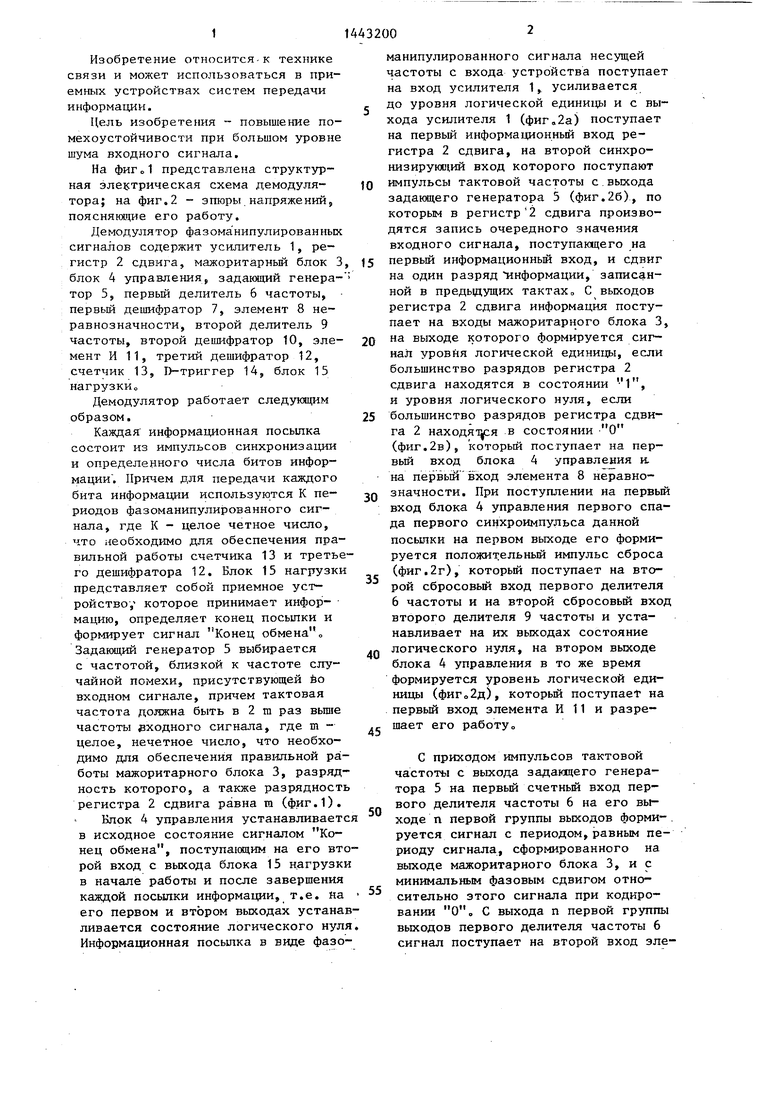

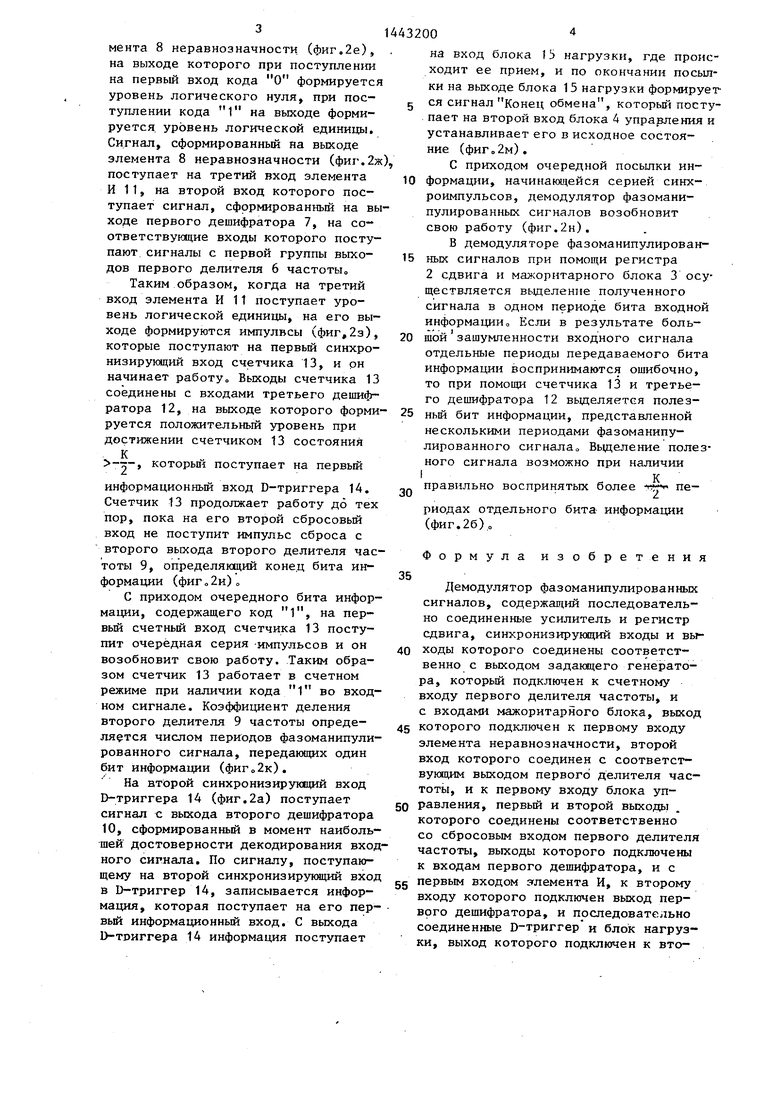

На фиг о 1 представлена структурная электрическая схема демодулятора; на фиг.2 - эпюры напряжений, поясняншдае его работу.

Демодулятор фазома нипулированных сигналов содержит усилитель 1, регистр 2 сдвига, мажоритарньй блок 3 блок 4 управления, задающий генератор 5, первый делитель 6 частоты, первый дешифратор 7, элемент 8 неравнозначности, второй делитель 9 частоты, второй дешифратор 10, элемент И 11, третий дешифратор 12, счетчик 13, 1)-триггер 14, блок 15 нагрузки

Демодулятор работает следующим образом.

Каждая информационная посылка состоит из импульсов синхронизации и определенного числа битов информации . Причем для передачи каждого бита информации используются К периодов фазоманипулированного сигнала, где К - целое четное число, что необходимо для обеспечения правильной работы счетчика 13 и третьего дешифратора 12. Блок 15 нагрузки представляет собой приемное устройство, которое принимает информацию, определяет конец посыпки и формирует сигнал Конец обмена Задающий генератор 5 выбирается с частотой, близкой к частоте случайной помехи, присутствующей йо входном сигнале, причем тактовая частота должна быть в 2 m раз выше частоты входного сигнала, где т - целое, нечетное число, что необходимо для обеспечения правильной работы мажоритарного блока 3, разрядность которого, а также разрядность регистра 2 сдвига равна m (фиг.1).

Блок 4 управления устанавливаетс в исходное состояние сигналом Конец обмена, поступающим на его второй вход с выхода блока 15 н.агрузки в начале работы и после заверщения каждой посылки информации, т.е. на его первом и втором выходах устанавливается состояние логического нуля Информационная посьшка в виде фазо

0

5

0

5

0

5

0

5

манипулированного сигнала несущей частоты с входа устройства поступает на вход усилителя 1, усиливается до уровня логической едини1Д.1 и с выхода усилителя 1 (фиг,2а) поступает на первый информационный вход регистра 2 сдвига, на второй синхро- низируюс1ий вход которого поступают импульсы тактовой частоты с.выхода задакидего генератора 5 (фиг.26), по которым в регистр 2 сдвига произво дятся запись очередного значения входного сигнала, поступающего на первый информационный вход, и сдвиг на один разряд информации, записанной в предыдущих тактахо С выходов регистра 2 сдвига информация поступает на входы мажоритарного блока 3, на выходе которого формируется сиг нал уровня логической единицы, если большинство разрядов регистра 2 сдвига находятся в состоянии 1, и уровня логического нуля, если большинство разрядов регистра сдвига 2 находятся в состоянии О (фиг.2в), который поступает на первый вход блока 4 управления и. на первый вход элемента 8 неравнозначности. При поступлении на первьш вход блока 4 управления первого спада первого синхроимпульса данной посыпки на первом выходе его формируется положительньй импульс сброса (фиг.2г), который поступает на второй сбросовый вход первого делителя 6 частоты и на второй сбросовый вход второго делителя 9 частоты и устанавливает на их выходах состояние логического нуля, на втором выходе блока 4 управления в то же время формируется уровень логической единицы (фиго2д), который поступает на первый вход элемента И 11 и разрешает его работуо

С приходом импульсов тактовой частоты с выхода задающего генератора 5 на первьш счетньй вход первого делителя частоты 6 на его выходе п первой группы выходов форми-. руется сигнал с периодом, равным периоду сигнала, сформированного на выходе мажоритарного блока 3, и с минимальным фазовым сдвигом относительно этого сигнала при кодировании О С выхода п первой группы выходов первого делителя частоты 6 сигнал поступает на второй вход элемента 8 неравнозначности (фиг.2е), на выходе которого при поступлении на первый вход кода О формируется уровень логического нуля, при поступлении кода 1 на выходе формируется, уровень логической единицы. Сигнал, сформированньй на выходе элемента 8 неравнозначности (фиг.2ж поступает на третий вход элемента И 11, на второй вход которого поступает сигнал, сформированный на выходе первого дешифратора 7, на соответствующие входы которого поступают сигналы с первой группы выходов первого делителя 6 частоты

Таким образом, когда на третий вход элемента И 11 поступает уровень логической единицы, на его выходе формируются импулвсы (фиг,2з), которые поступают на первый синхронизирующий вход счетчика 13, и рн начинает работуо Выходы счетчика 13 соединены с входами третьего дешифратора 12, на вькоде которого формируется положительный уровень при достижении счетчиком 13 состояния

К , которьп поступает на первый

информационный вход D-триггера 14. Счетчик 13 продолжает работу до тех пор, пока на его второй сбросовый вход не поступит импульс сброса с второго выхода второго делителя частоты 9, определяющий конед бита информации (фиг«2и)о

С приходом очередного бита информации, содержащего код 1, на первый счетный вход счетчика 13 поступит очерёдная серия -импульсов и он возобновит свою работу. Таким образом счетчик 13 работает в счетном режиме при наличии кода 1 во входном сигнале. Коэффициент деления второго делителя 9 частоты опреде- числом периодов фазоманипули- рованного сигнала, передающих один бит информации (фиго2к).

На второй синхронизирующий вход ЕЬтриггера 14 (фиг.2а) поступает сигнал с выхода второго дешифратора 10, сформированньй в момент наибольшей достоверности декодирования входного сигнала. По сигналу, поступающему на второй синхронизирунэдий вход в D-триггер 14, записывается информация, которая поступает на его первый информационный вход. С выхода 1 -тоиггера 14 информация поступает

на вход блока 13 нагрузки, где происходит ее прием, и по окончании посылки на выходе блока 15 нагрузки формирует- ся сигнал Конец обмена, которьпЧ поступает на второй вход блока 4 управления и устанавливает его в исходное состояние (фиг о 2м).

С приходом очередной посылки информации, начинающейся серией синхроимпульсов, демодулятор фазомани- пулированных сигналов возобновит свою работу (фиг.2н).

В демодуляторе фазоманипулированных сигналов при помощи регистра

2 сдвига и мажоритарного блока 3 осуществляется вьщеление полученного сигнала в одном периоде бита входной информациио Если в результате большой зашумленности входного сигнала отдельные периоды передаваемого бита информации воспринимаются ошибочно, то при помощи счетчика 13 и третьего дешифратора 12 вьщеляется полезньй бит информации, представленной несколькими периодами фазоманипу- лированного сигналао Выделение полезного сигнала возможно при наличии

I К

правильно воспринятых более -п пе-

риодах отдельного бита информации (фиг.26).о

Формула изобретения

Демодулятор фазоманипулированных сигналов, содержап;нй последовательно соединенные усилитель и регистр сдвига, синхронизирукщий входы и выходы которого соединены соответственно с выходом задакщего генератора, который подключен к счетному входу первого делителя частоты, и с входами мажоритарного блока, выход

которого подключен к первому входу элемента неравнозначности, второй вход которого соединен с соответствующим выходом первого делителя частоты, и к первому входу блока управления, первьй и второй выходы которого соединены соответственно со сбросовым входом первого делителя частоты, выходы которого подключены к входам первого дешифратора, и с

первым входом з лемента И, к второму входу которого подключен выход первого дешифратора, и пocлeдoвaтeJlьнo соединенные D-триггер и блок нагрузки, выход которого подключен к вто5 1443200 :6

рому входу блока управления, о т-ходы которого подключены к входам

личающийся тем, что, с цельювторого дешифратора, и с входами

повышения помехоустойчивости притретьего дешифратора, выход которого

большом уровне шума входного сигнала, подключен к информационному входу

введены второй и третий дешифраторы,D-триггера, синхронизирующий вход

второй делитель частоты и счетчик,которого соединен с в кодом второго

с етный и сбросовьй входы и выходыдешифратора, при этом дополнителькоторого соединены соответственно сный выход первого делителя частоты

в| 1ходом элемента И, к третьему входую и первый выход блока управления подкоторого подключен выход элементаключены соответственно к счетному

неравнозначности, с одним выходоми сбросовому входам второго делителя

второго делителя частоты, другие вы-частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Демодулятор фазоманипулированных сигналов | 1986 |

|

SU1356254A1 |

| Демодулятор фазоманипулированных сигналов | 1980 |

|

SU930645A1 |

| Устройство для сопряжения ЦВМ с магнитофоном | 1985 |

|

SU1317445A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном звукозаписи | 1985 |

|

SU1260969A2 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1984 |

|

SU1188745A1 |

| УСТРОЙСТВО ПРИЕМА И ПЕРЕДАЧИ ФАЗОМАНИПУЛИРОВАННЫХ КОДОВЫХ СИГНАЛОВ | 2002 |

|

RU2236086C2 |

| Преобразователь серии импульсов в прямоугольный импульс | 1986 |

|

SU1422382A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДВИЖЕНИЯ ТРАНСПОРТНЫХ СРЕДСТВ | 1992 |

|

RU2054198C1 |

| Синхронизирующее устройство | 1984 |

|

SU1213528A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА КОМАНД ТЕЛЕУПРАВЛЕНИЯ | 1991 |

|

RU2023309C1 |

Изобретение относится к технике связи. Цель изобретения - повьппение помехоустойчивости при большом уровне шума входного сигнала. Демодулятор содержит усилитель 1,регистр 2 сдвига, мажоритарный блок 3, блок управления 4, задающий г-р 5, делители 6 и 9 частоты, дешифраторы 7, 10 и 12, эл-т 8 неравнозначности,эл-т И 11, счетчик 13,, D-триггер 14 и блок нагрузки 15. В демодуляторе при помощи регистра 2 и мажо- ритарного блока 3 осуществляется вьщеление полученного сигнала в од- ном периоде бита входной информации. ЕСЛИ в результате большой зашумленности входного сигнала отдельные периоды передаваемого бита информации принимаются ошибочно, то при помощи счетчика 13 и дешифратора 12 выделяется полезный бит информации, представленной несколькими периодами фазоманипулированного сигнала Выделение полезного сигнала возможно при наличии правильно воспринятых более К/2 периодах отдельного бита информации (где К - целое четное число). Цель -достигается введением делителя 9, дешифраторов 10 и 12 и счетчика 13. 2 ил. (Л

О Утвмигашпжтмгш

Д111И1111И1М11111И111И1111111111111111111111111111Ш11111П1Н1Ш111111111111Н111IHIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII

e JlJTlTJlJTJlJElJrilTLiF Lr J lIlJTLr

:TLTiriJTJTITLnibnJlJlJlJlTlJlJlIimiiT

JI11

в i II я и II я П II |1,Д я в П и

в я Hi ц а п П

IIL II-

И-

И- ffJ.

| Демодулятор фазоманипулированных сигналов | 1986 |

|

SU1356254A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-12-07—Публикация

1987-04-09—Подача