Изобретение относится к вычислительной технике, в частности к устройствам для защиты информации в блоках памяти при отключении питания.

Цель изобретения - повышение надежности хранения записанной в блоках памяти информации.

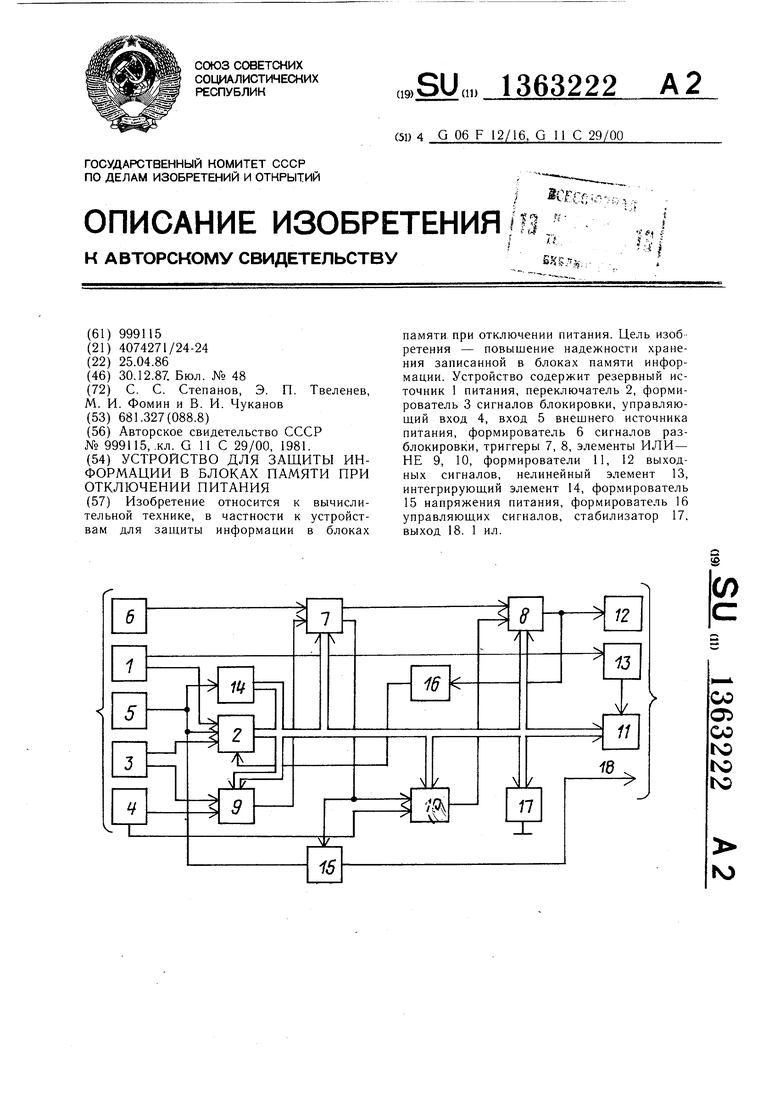

На чертеже изображена структурная схема устройства для защиты информации в блоках памяти.

разитныи тиристор до такой величины, что прямой ток прекращается после окончания помехи. В момент подачи напряжения от внещнего источника питания (не показан) с положительным выбросом напряжения и с большой скоростью изменения внещнего питающего напряжения ограничение напряжения питания с помощью стабилизатора 17 и одновременное интегрирование фронта напряжения питания интегрирующим элементом 14 возможно только при наличии формирователя 15, устраняющего прохождение положительного выброса питающего напряжения через выход 18 и защитные диодные структуры входов комУстройство содержит резервный источник 1 питания, переключатель 2, формирователь 3 сигналов блокировки, управляющий вход 4, вход 5 внешнего источника питания, формирователь 6 сигналов разблоки- плиментарнЪх микросхем пймяти(не п оказа- ровки, первый 7 и второй 8 триггеры,ны). Включение формирователя 15 начинает- первый 9 и второй 10 элементы ИЛИ-НЕ,ся после временной выдержки, определяемой первый формирователь И выходных сигна-формирователем 6 сигнала разблокировки, и лов, управляющий входом питания блокаснятия сигнала блокировки с триггера 7. памяти, второй формирователь 12 выходныхФормирователь 16 формирует плавный фронт сигналов, нелинейный элемент 13, выпол-20 напряжения внешнего источника питания, ненный, например, в виде последовательноПри наличии сигнала «Выбор схемы соединенных диода и резистора (не пока-„д управляющем входе 4 и при снятом заны), интегрирующий элемент 14, включаю-сигнале «Блокировка триггера 7 происходит разблок ировка триггера 8, который разщий в себя последовательно соединенные

диоды, времязадающий резистор и фильт- решает работу формирователю 12 и через формирователь 16 включает силовой транзистор переключателя 2, с помощью которого происходит коммутация входа 5 внешнего источника питания.

30Формула изобретения

рующие конденсаторы питания (не показаны), формирователь 15 напряжения питания, формирователь 16 управляющих сигналов, стабилизатор 17, выполненный например, на стабилитроне КС 167А, и выход 18 питания устройства.

Устройство работает следующим образом.

Если уровень напряжения питания, поступающего от внешнего источника питания на вход 5, становится ниже определенного уровня, формирователь 3 вырабатывает сигнал, который поступает на вход элемента ИЛИ-НЕ 9. Если в это время на входе 4 устройства присутствует сигнал «Выбор схемы, TQ блокировка первого триггера 7 происходит только после завершения действия данного сигнала. ОдновреУстройство для защиты информации в блоках памяти при отключении питания по авт. св. № 999115, отличающееся тем, что, с целью повышения надежности зс хранения записанной в блоках памяти информации,, в него введены интегрирующий элемент, формирователь напряжения питания, стабилизатор и формирователь управляющих сигналов, вход которого подключен к выходу второго триггера, выход формименно через элемент ИЛИ-НЕ 10 проис- 40 рователя управляющих сигналов соединен с

ходит блокировка триггера 8 .и запрещается выработка сигнала «Выбор схемы формирователем 12. При блокировке триггера 8 через формирователь 16 выключается силовой транзистор (не показан) переключателя 2 и блок памяти (не показан) переходит на питание от резервного источника 1 через формирователь 11, который управляет входом питания блока памяти. Для устранения тиристорногб эффекта в

управляющим входом переключателя, вход интегрирующего элемента соединен с входом внешнего источника питания, выход интегрирующего элемента соединен с выходом -с переключателя, первый вывод стабилизатора подключен к выходу переключателя, второй вывод переключателя соединен с шиной нулевого потенциала, управляющий вход формирователя напряжения питания подключен

к инверсному выходу первого триггера, вход момент отключения внещнего источника пи- Q питания формирователя напряжения пита- тания служит нелинейный элемент 13, кото-ния соединен с входом внещнего источрый при возникновении такого эффектаника питания, выход формирователя напрявследствие больщого внутреннего сопротив-жения питания является одним из выхоления ограничивает прямой ток через па- дов питания устройства.

Составитель В. Рудаков

Редактор Л. ПчолинскаяТехред И. ВересКорректор И. Муска

Заказ 5966/41Тираж 671Подписное

ВНИИПИ Государственного комитета СССР по де.лам изобретений и открытий

1 13035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, у.п. Проектная, 4

разитныи тиристор до такой величины, что прямой ток прекращается после окончания помехи. В момент подачи напряжения от внещнего источника питания (не показан) с положительным выбросом напряжения и с большой скоростью изменения внещнего питающего напряжения ограничение напряжения питания с помощью стабилизатора 17 и одновременное интегрирование фронта напряжения питания интегрирующим элементом 14 возможно только при наличии формирователя 15, устраняющего прохождение положительного выброса питающего напряжения через выход 18 и защитные диодные структуры входов комплиментарнЪх микросхем пймяти(не п оказа- ны). Включение формирователя 15 начинает- ся после временной выдержки, определяемой формирователем 6 сигнала разблокировки, и снятия сигнала блокировки с триггера 7. Формирователь 16 формирует плавный фронт напряжения внешнего источника питания, При наличии сигнала «Выбор схемы „д управляющем входе 4 и при снятом сигнале «Блокировка триггера 7 происходит разблок ировка триггера 8, который разУстройство для защиты информации в блоках памяти при отключении питания по авт. св. № 999115, отличающееся тем, что, с целью повышения надежности с хранения записанной в блоках памяти информации,, в него введены интегрирующий элемент, формирователь напряжения питания, стабилизатор и формирователь управляющих сигналов, вход которого подключен к выходу второго триггера, выход формиуправляющим входом переключателя, вход интегрирующего элемента соединен с входом внешнего источника питания, выход интегрирующего элемента соединен с выходом переключателя, первый вывод стабилизатора подключен к выходу переключателя, второй вывод переключателя соединен с шиной нулевого потенциала, управляющий вход формирователя напряжения питания подключен

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты информации в блоках памяти при отключении питания | 1981 |

|

SU955211A1 |

| Устройство для защиты информации в блоках памяти при отключении питания | 1981 |

|

SU999115A2 |

| Устройство для защиты информации в блоках памяти при отключении питания | 1988 |

|

SU1508286A1 |

| Устройство для защиты информации в блоках памяти при отключении питания | 1990 |

|

SU1716573A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1989 |

|

SU1695395A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1985 |

|

SU1259342A1 |

| УСТРОЙСТВО ОХРАННОЙ СИГНАЛИЗАЦИИ | 1991 |

|

RU2031445C1 |

| Устройство для передачи и приемаСигНАлОВ | 1979 |

|

SU830486A1 |

| Емкостное устройство для ввода данных | 1987 |

|

SU1647551A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ДЫХАНИЯ | 1990 |

|

RU2064777C1 |

Изобретение относится к вычислительной технике, в частности к устройствам для защиты информации в блоках памяти при отключении питания. Цель изобретения - повышение надежности хранения записанной в блоках памяти информации. Устройство содержит резервный источник 1 питания, переключатель 2, формирователь 3 сигналов блокировки, управляющий вход 4, вход 5 внешнего источника питания, формирователь 6 сигналов разблокировки, триггеры 7, 8, элементы ИЛИ - НЕ 9, 10, формирователи 11, 12 выходных сигналов, нелинейный элемент 13, интегрирующий элемент 14, формирователь 15 напряжения питания, формирователь 16 управляющих сигналов, стабилизатор 17. выход 18. 1 ил. сл со о: оо to го N5 ГО

| Устройство для защиты информации в блоках памяти при отключении питания | 1981 |

|

SU999115A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-12-30—Публикация

1986-04-25—Подача