Изобретение относится к запоминаЮЩИГ1 устройствам.

Известно устройство для защиты информации в блоках памяти при отключении питания, в котором используется вспомогательный батарейный источник питания, включенный по буферной схеме 1 .

Недостатком этого устройства яв.ляется низкая надежность.

Из известных -устройств наиболее близким техническим решением к предлагаемому является устройство для защиты информации в блоках памяти при отключении питания, содержащее резервный источник питания, схему переключения внешнего источника питания на резервный источник, вход сигнала Выбор микросхемы, и выполнено на интегральных схемах биполярнойи комплиментарной металл-диэлектрикполупроводник технологии 2.

Недостатком этого устройства является низкая надежность вследствие искажения информации в режиме разблокировки из-за прохождения сигнала помехи на вход сигнала Выбор микросхемы устройства.

Цель изобретения - повьпиение надежности устройства.

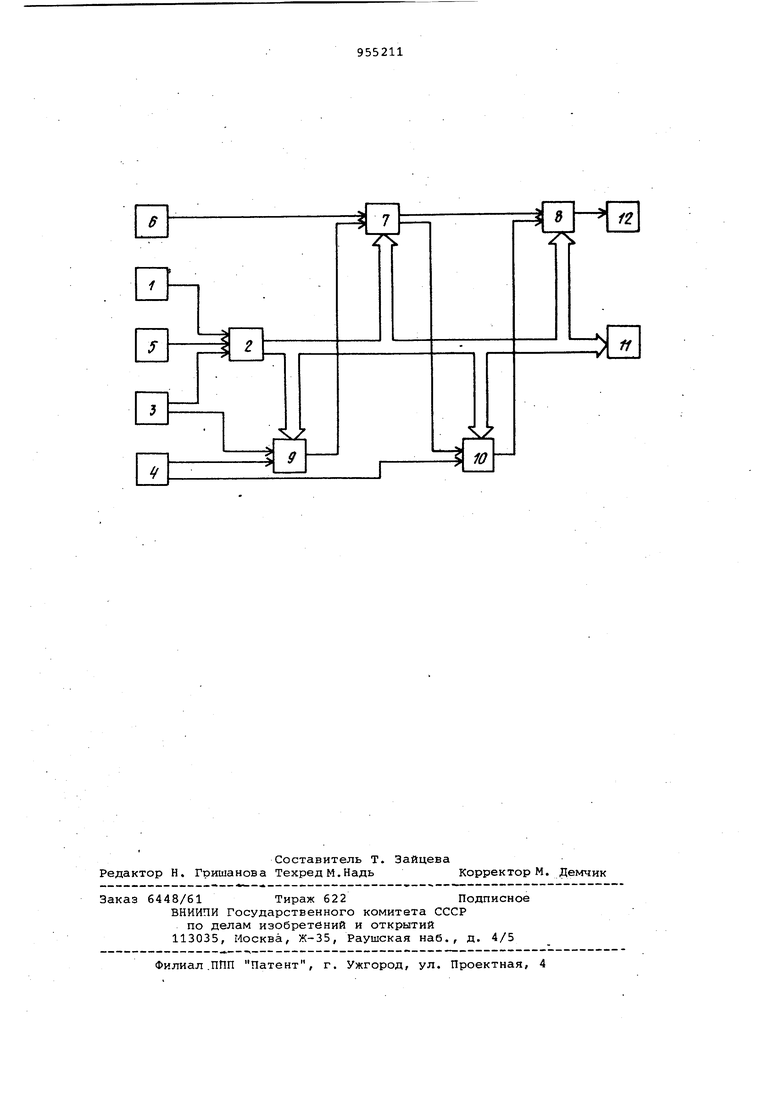

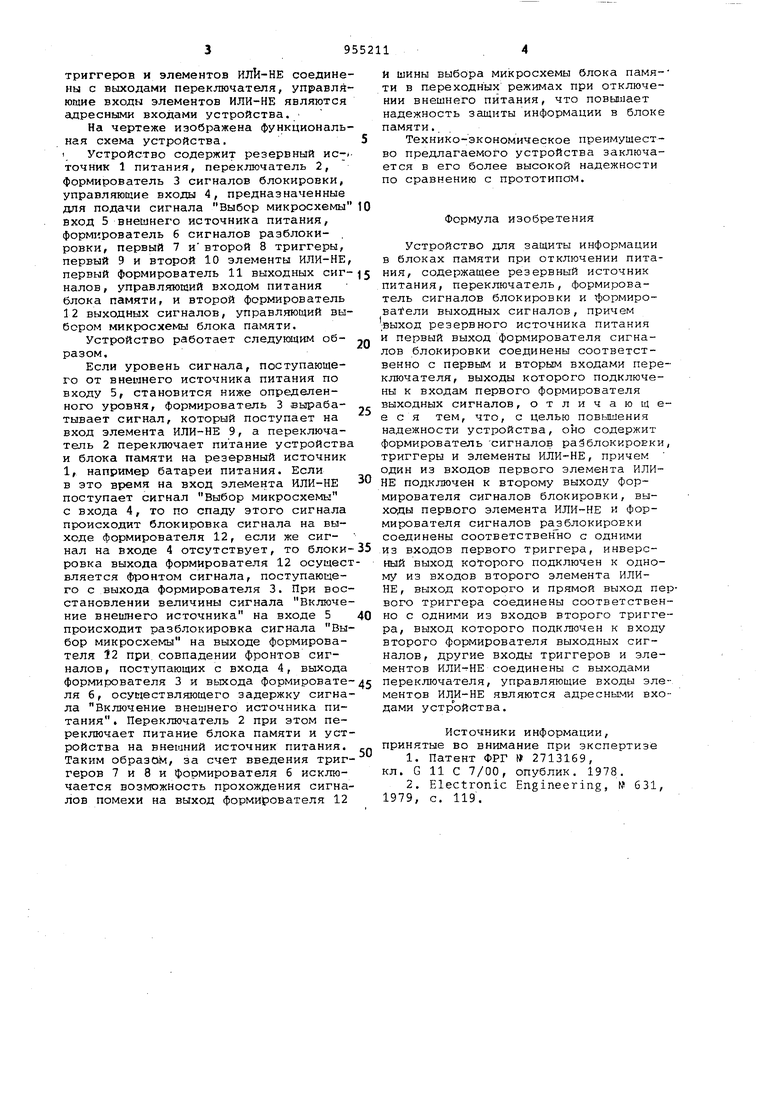

Поставленная цель достигается тем, что в устройство для защиты информации в блоках памяти при отключении питания, содержащее резервный источник питания, переключатель, формирователь сигналов блокировки и формирователи выходных сигналов, причем выход резервного источника питания и первый выход формирователя си налов блокировки соединены соответственно с первым и вторым входами переключателя, выходы которого подключены к входам первого формирователя выходных сигналов, введены формирователь сигналов разблокировки,- триггеры и элементы ИЛИ-НК, причем один из входов первого элемента ИЛИ-НЕ подключен к второму выходу формирователя сигналов блокировки, выходы первого элемента ИЛИ-НЕ и формирователя сигналов разблокировки соединены соответственно с одними из входов первого триггера, инверсный выход которого подключен к одному из входов второго элемента ИЛИ-НЕ, выход которого и прямой выход первого триггера соединены соответственно с одними из входов второго триггера, выход которого подключен к входу втооого формирователя выходных сигналов, другие входы триггеров и элементов ИЛЬ-НЕ соедине ны с выходами переключателя, управля ющие входы элементов ИЛИ-НЕ являются адресными вхоДами устройства. На чертеже изображена функциональная схема устройства. I Устройство содержит резервный ис- точник 1 питания, переключатель 2, формирователь 3 сигналов блокировки, управляющие входы 4, предназначенные для подачи сигнала Выбор микросхемы вход 5 внешнего источника питания, формирователь б сигналов разблоки- . ровки, первый 7 и второй 8 триггеры, первый 9 и второй 10 элементы ИЛИ-НЕ первый формирователь 11 выходных сигналов, управляющий входом питания блока памяти, и второй формирователь 12 выходных сигналов, управляющий выбором микросхемы блока памяти. Устройство работает следугацим образом. Если уровень сигнала, поступающего от внешнего источника питания по входу 5, становится ниже определенного уровня, формирователь 3 вырабатывает сигнал, который поступает на вход элемента ИЛИ-НЕ 9, а переключатель 2 переключает питание устройства и блока памяти на резервный источник 1, например батареи питания. Если в это время на вход элемента ИЛИ-НЕ поступает сигнал Выбор микросхемы с входа 4, то по спаду этого сигнала происходит блокировка сигнала на выходе формирователя 12, если же сигнал на входе 4 отсутствует, то блокировка выхода формирователя 12 осущест вляется фронтом сигнала, поступающего с выхода формирователя 3. При восстановлении величины сигнала Включение внешнего источника на входе 5 происходит разблокировка сигнала Выбор микросхемы на выходе формирователя 32 при, совпадении фронтов сигналов , поступающих с входа 4, выхода формирователя 3 и выхода формирователя б, осуществляющего задержку сигнала Включение внешнего источника питания . Переключатель 2 при этом переключает питание блока памяти и устройства на внешний источник питания. Таким образом, за счет введения триггеров 7 и 8 и формирователя 6 исключается возможность прохождения сигналов помехи на выход формирователя 12 и шины выбора микросхемы блока памя-ти в переходных режимах при отключении внешнего питания, что повышает надежность защиты информации в блоке памяти. Технико-экономическое преимущество предлагаемого устройства заключается в его более высокой надежности по сравнению с прототипам. Формула изобретения Устройство для защиты информации в блоках памяти при отключении питания, содержащее резервный источник питания, переключатель, формирователь сигналов блокировки и формироват ели выходных сигналов, причем .выход резервного источника питания и первый выход формирователя сигналов блокировки соединены соответственно с первым и вторым входами переключателя, выходы которого подключены к входам первого формирователя выходных сигналов, отличаю щее с я тем, что, с целью повышения надежности устройства, оно содержит формирователь сигналов раЗблоккронки, триггеры и элементы ИЛИ-НЕ, причем один из входов первого элемента ИЛИНЕ подключен к второму выходу формирователя сигналов блокировки, выходы первого элемента ИЛИ-НЕ и формирователя сигналов ра зблокировки соединены соответственно с одними из входов первого триггера, инверсгелй выход которого подключен к одному из входов второго элемента ИЛИНЕ , выход которого и прямой выход первого триггера соединены соответственно с одними из входов второго триггера, выход которого подключен к входу второго формирователя выходных сигналов, другие входы триггеров и элементов соединены с выходами переключателя, управляющие входы элементов ИЛИ-НЕ являются адресными входами устройства. Источники информации, принятые во внимание при экспертизе 1.Патент ФРГ № 2713169, кл. G 11 С 7/00, опублик. 1978. 2.Electronic Engineering, № 631, 1979, с. 119.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для защиты информации в блоках памяти при отключении питания | 1986 |

|

SU1363222A2 |

| Устройство для защиты информации в блоках памяти при отключении питания | 1981 |

|

SU999115A2 |

| Устройство для защиты информации в блоках памяти при отключении питания | 1990 |

|

SU1716573A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1985 |

|

SU1259342A1 |

| Устройство для защиты информации в блоках памяти при отключении питания | 1988 |

|

SU1508286A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1989 |

|

SU1695395A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1987 |

|

SU1448362A1 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2011 |

|

RU2494006C2 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ СОСТОЯНИЯ И УПРАВЛЕНИЯ КАНАЛАМИ И ТЕХНИЧЕСКИМИ СРЕДСТВАМИ В СИМПЛЕКСНЫХ СИСТЕМАХ СВЯЗИ | 1991 |

|

RU2007878C1 |

Авторы

Даты

1982-08-30—Публикация

1981-01-19—Подача