сл

Ivd

СО 1чЭ

САЭ 4

; Изобретение относится к вычисли- т|ельной технике и может быть исполь- з|овано при проектировании вычислительных систем на базе цифровых мат- р 1чных процессоров о I Цель изобретения - повьппение на- ежности устройства за счет его пе естраиваемости

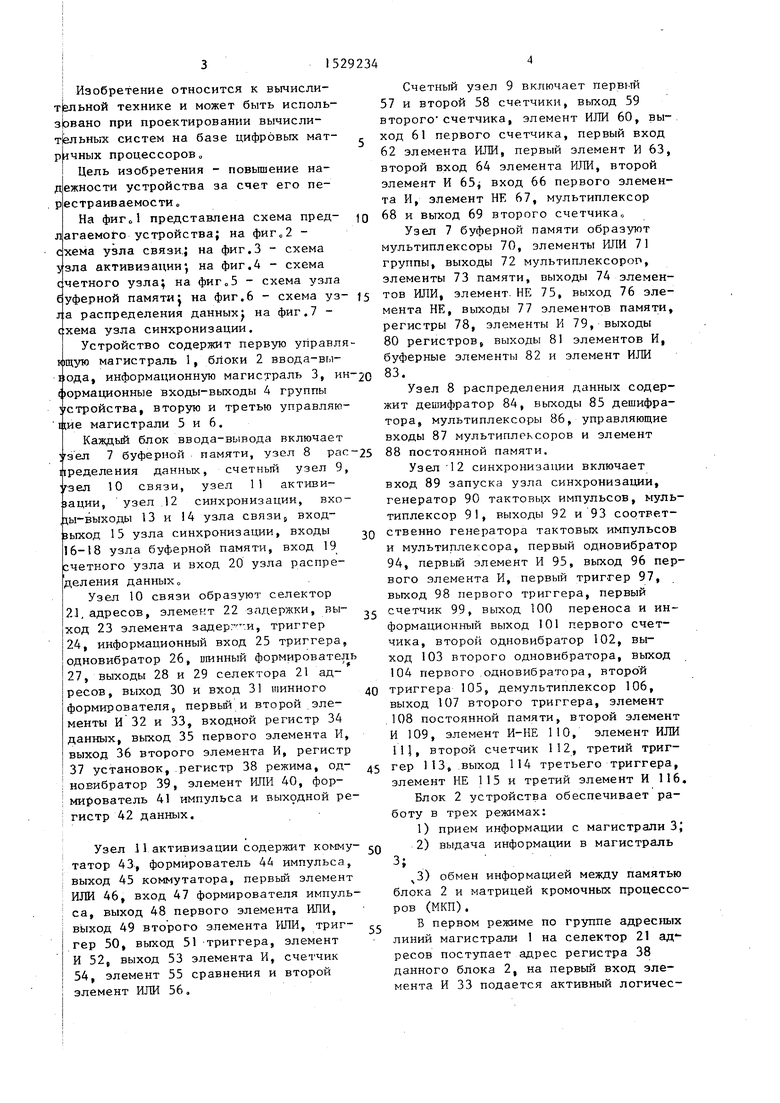

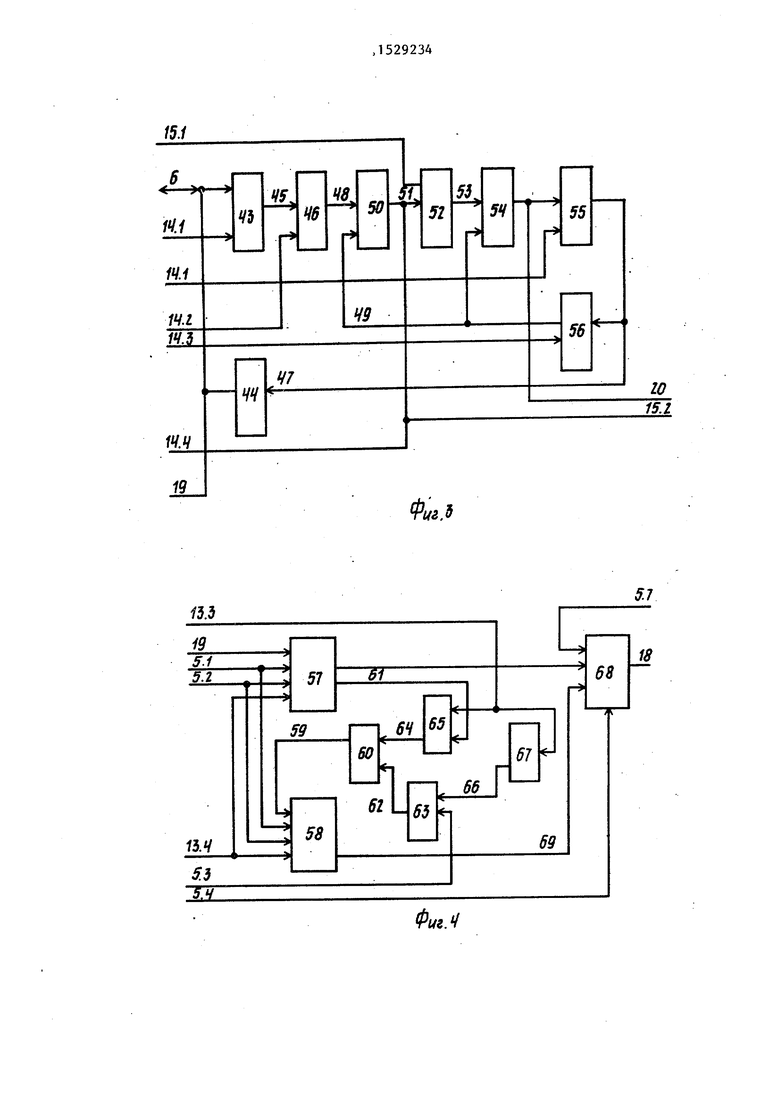

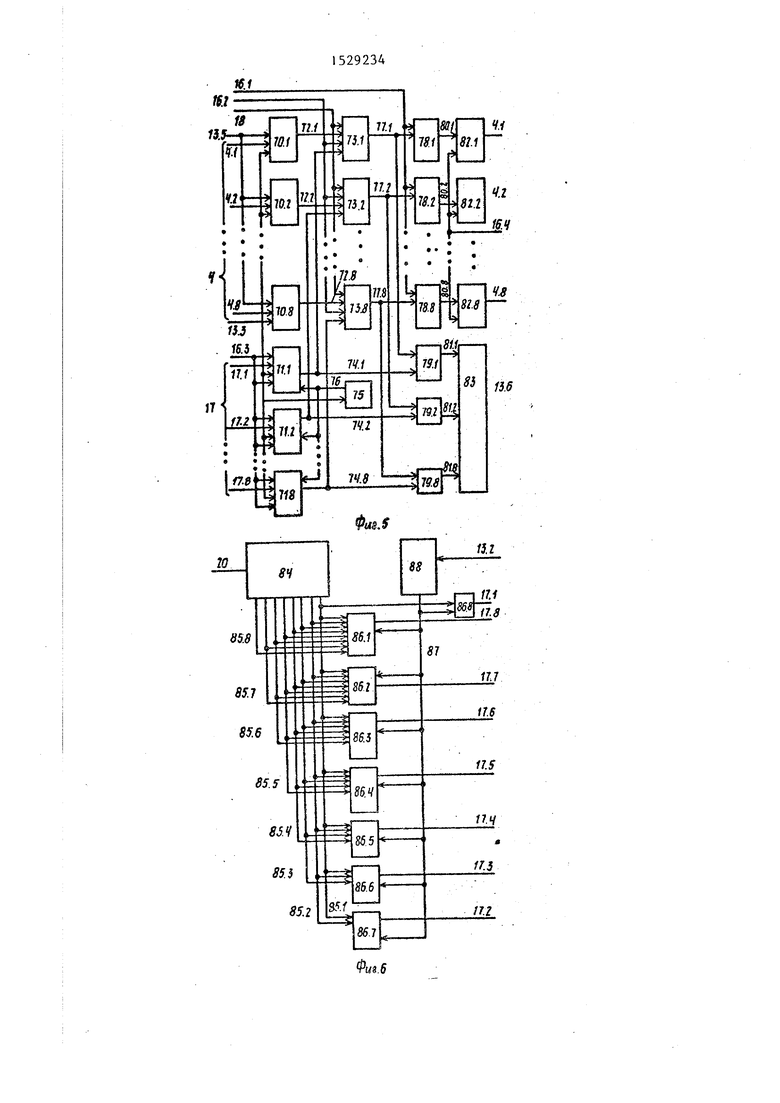

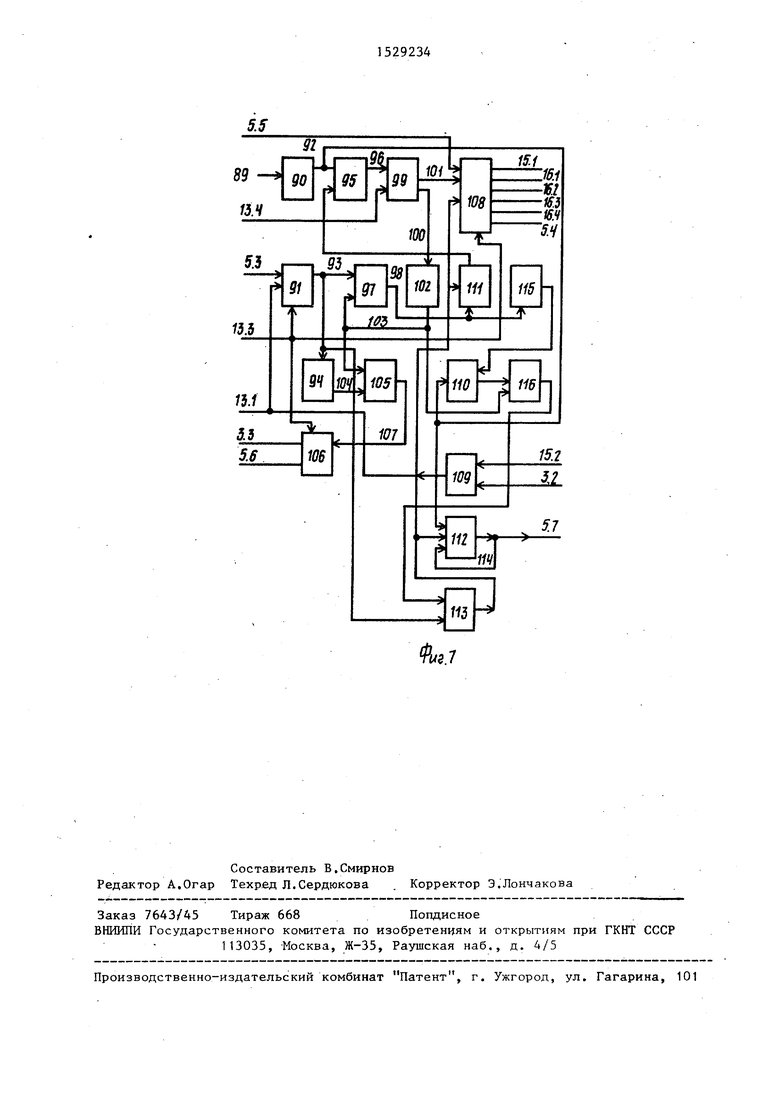

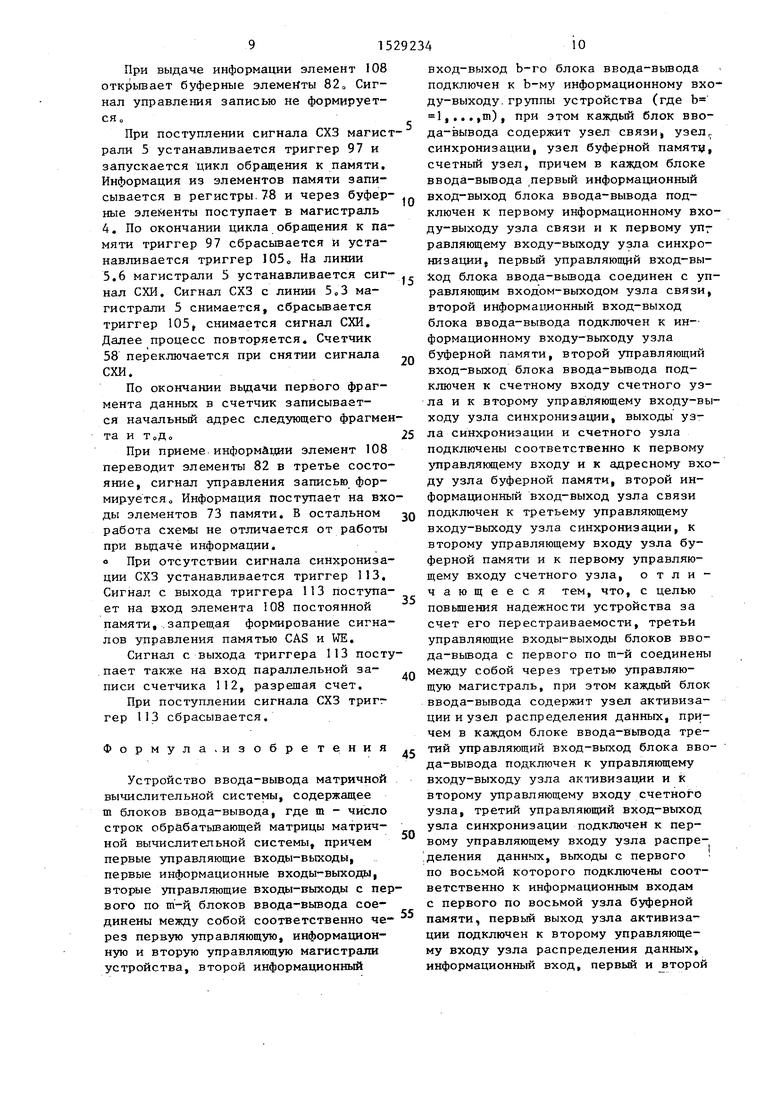

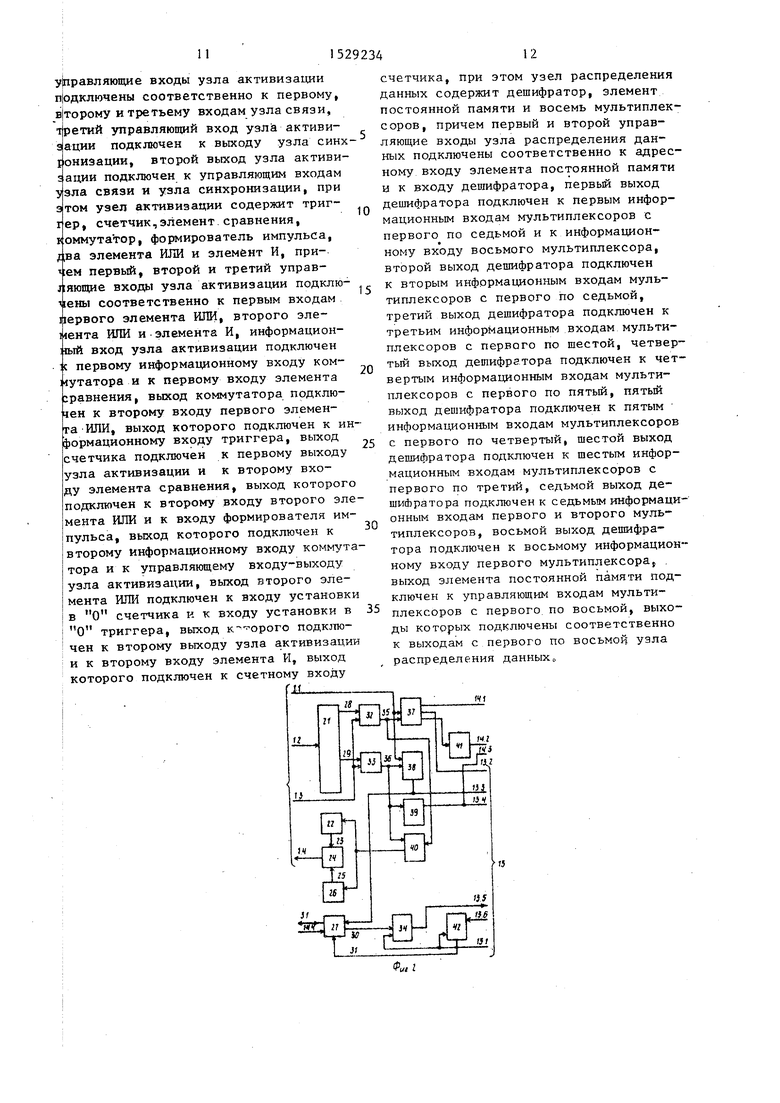

На фигс, представлена схема пред- агаемого устройства; на фиг,2 - хема узла связи.; на фиг.З - схема зла активизации , на фиг,4 - схема четного узла на фиг„5 - схема узла уферной памятиj на фиг,6 - схема уз- а распределения данныхj на фиг,7 - хема узла синхронизации.

Устройство содержит первую управля щую магистраль 1, блоки 2 ввода-вгл- ода, информационную магистраль 3, ин ормационные входы-выходы 4 группы стройства, вторую и третью управляю- ие магистрали 5 и 6,

Каждьй блок ввода-вывода включает з ел 7 буферной памяти, узел 8 рас ределения данных, счетный узел 9, зел 10 связи, узел 11 активи- ации, узел 12 синхронизации, вхо- ы-выходы 13 и 14 узла связи, вход- ыход 15 узла синхронизации, входы 6-18 узла буферной памяти, вход 19 четного узла и вход 20 узла распределения данных о

Узел 10 связи образуют селектор ., адресов, злемент 22 задержки, вы- ход 23 элемента задер:- .и,, триггер 24, информационный вход 25 триггера, одновибратор 26, игинный формировател 27, выходы 28 и 29 селектора 21 ад- jpecoB, выход 30 и вход 31 шинного I формирователя, первьм и второй элементы И 32 и 33, входной регистр 34 данных, выход 35 первого элемента И, выход 36 второго элемента И, регистр 37 установок, регистр 38 режима, од- ; новибратор 39, элемент ИЛИ 40, фор- ; мирователь 41 импульса и выходной ре i гистр 42 данных,

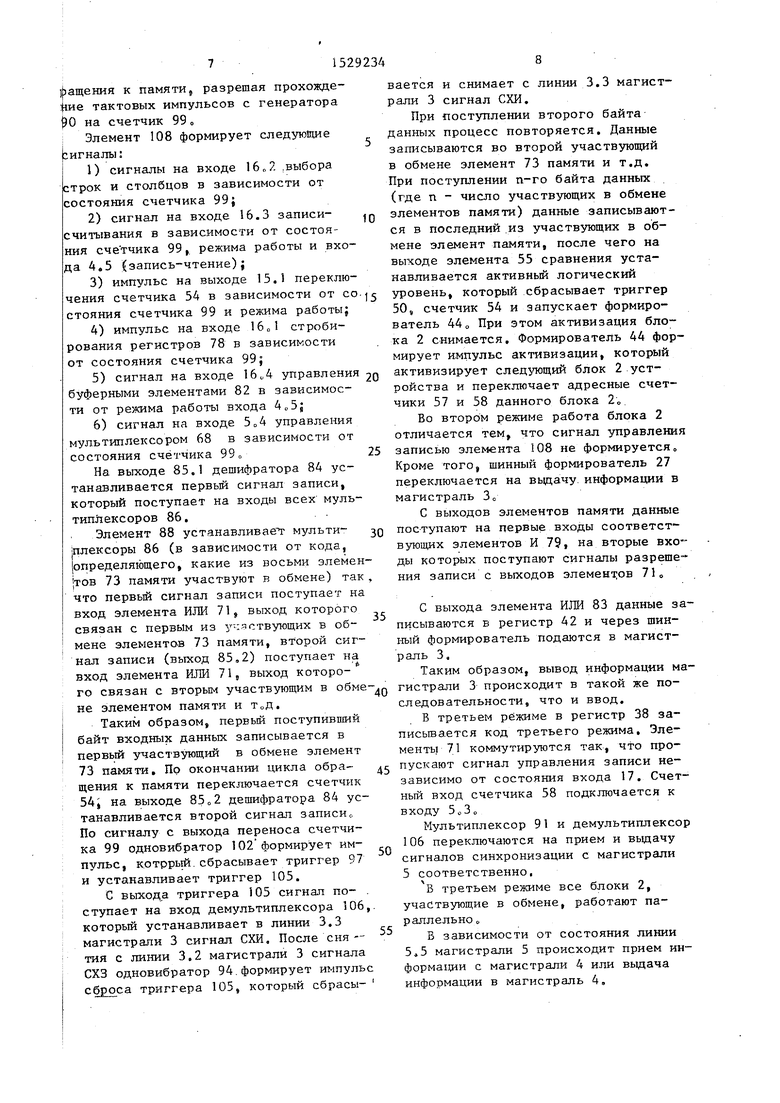

Узел 11 активизации содержит комму татор 43, формирователь 44 импульса, : выход 45 коммутатора, первый элемент

ИЛИ 46, вход 47 формирователя импуль : са, выход 48 первого элемента ИЛИ, I выход 49 второго элемента ИЛИ, триг- гер 50, выход 51 триггера, элемент И 52, выход 53 элемента И, счетчик 54, элемент 55 сравнения и второй элемент ИЛИ 56,

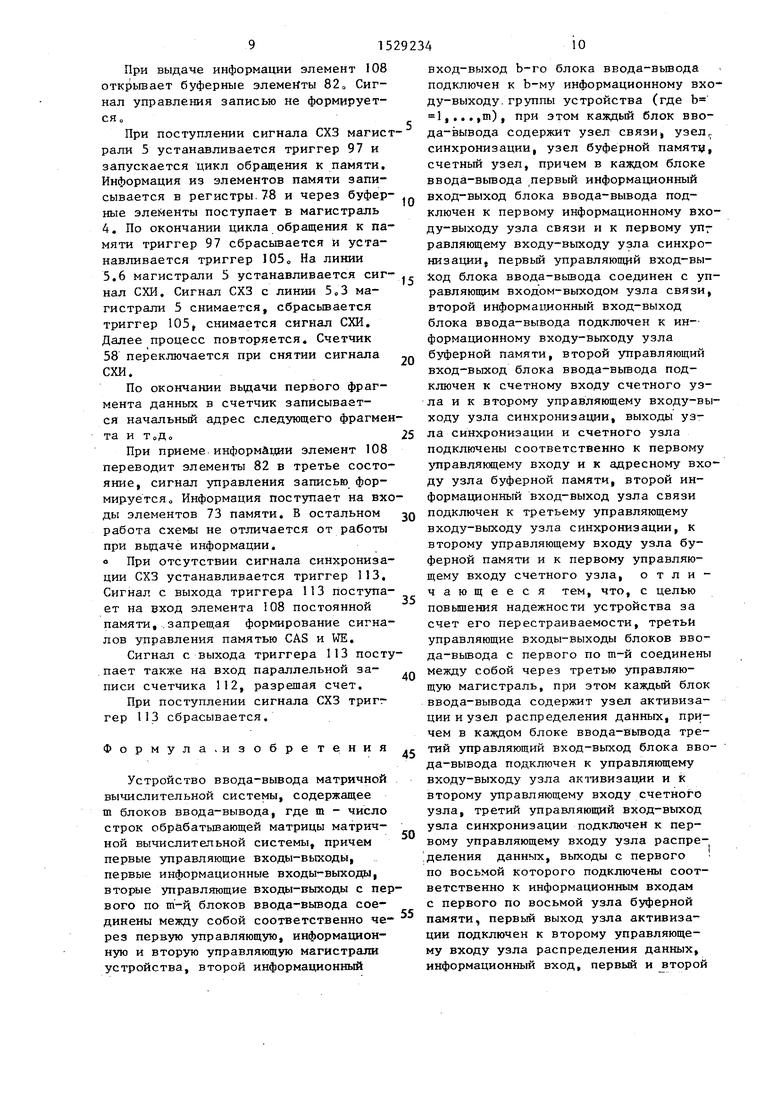

Счетный узел 9 включает первый 57 и второй 58 счетчики, выход 59 второго счетчика, элемент ИЛИ 60, выход 61 первого счетчика, первый вход 62 элемента ИЛИ, первый элемент И 63, второй вход 64 элемента ИЛИ, второй элемент И 65j вход 66 первого элемента И, злемент НЕ 67, мультиплексор 68 и выход 69 второго счетчика.

Узел 7 буферной памяти образуют мультиплексоры 70, элементы ИЛИ 71 группы, выходы 72 мультиплексороп, элементы 73 памяти, выходы 74 элементов ИЛИ, элемент. НЕ 75, выход 76 элемента НЕ, выходы 77 элементов памяти, регистры 78, элементы И 79, выходы 80 регистров, выходы 8 элементов И, буферные элементы 82 и элемент ИЛИ 83,

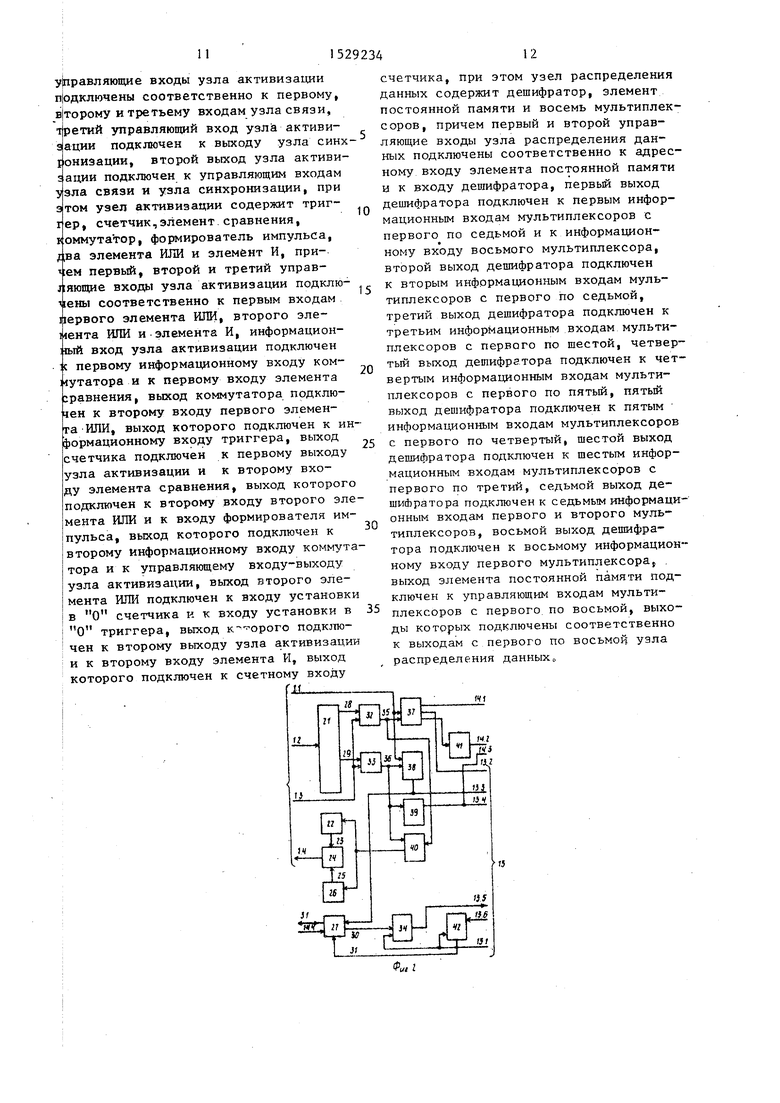

Узел 8 распределения данных содержит дешифратор 84, выходы 85 дешифратора, мультиплексоры 86, управляющие входы 87 мультиплексоров и элемент 88 постоянной памяти.

Узел 12 синхронизации включает вход 89 запуска узла синхронизации, генератор 90 тактовы.х импульсов, мультиплексор 91, выходы 92 и 93 соответственно генератора тактовых импульсов и мультиплексора, первый одновибратор 94, первый элемент И 95, выход 96 первого элемента И, первый триггер 97, выход 98 первого триггера, первый счетчик 99, выход 100 переноса и информационный выход 101 первого счетчика, второй одновибратор 102, выход 103 второго одновибратора, выход 104 первого одновибратора, второ й триггера 105, демультиплексор 106, выход 107 второго триггера, злемент 108 постоянной памяти, второй элемент И 109, элемент И-НЕ 110, элемент ИЛИ 11}, второй счетчик 112, третий триггер 113, выход 114 третьего триггера, элемент НЕ 115 и третий элемент И 116

Блок 2 устройства обеспечивает работу в трех режимах:

1)прием информации с магистрали 3J

2)выдача информации в магистраль

3; . .

3) обмен информацией между памятью блока 2 и матрицей кромочных процессоров (МКП),

В первом режиме по группе адресгшх линий магистрали 1 на селектор 21 ресов поступает адрес регистра 38 данного блока 2, на первый вход элемента И 33 подается активный логичес51529234 .6

кий уровень, разрешающий стробирование 4) сигнал активизации, регистра 38. По сигналу синхронизации Код передачи эстафеты активности задатчика (СХЗ) магистрали 1 в регистр поступает на управляющие входы комму- 38 записывается код первого режима татора 43.

работыо С выхода элемента И 33 сиг- Кх)д, определяющий число участвую- нал синхронизации поступает также и щих в обмене элементов памяти, подана одновибратор 39, вырабатывающий ется на элемент 55 сравнения и опре- короткий импульс предустановки, кото- деляет коэффициент пересчета счет- рый устанавливает в исходное состоя- ю чика 54 (от О до 8).

ние триггеры и счетчики блока 2 Код Код, определяющий, какие из элемен- режима подключает шинный формирователь тов 73 памяти участвуют в обмене, по- 27 на прием информации с магистрали дается с регистра 37 на вход элемен- 3,подключает к входу стробирования I та 88 постоянной памяти, счетчика 59 выход переноса счетчика 15 На вход коммутатора 43 заведены 57, поступает на управляющий вход - линии активизации с выходов одновиб- мультиплексоров 70, которые подключа- раторов 44 всех блоков 2 устройст- ют информационные входы памяти к ре- . за.

гистру 34, проходит на вход элемента Число блоков 2, участвующих в дан- 108 и на управляющие входы мультиплек-20 ном.обмене, и последовательность их сора 91 и демультиплексора 106„ Муль- активизации задаются кодом эстафе- типлексор 91 подключает к входу триг- ты передачи активизации, который под- гера 97 сигнал СХЗ магистрали 3 через ключает к выходу коммутатора 43 линию элемент И 109. На второй вход элемен- активизации того модуля, который акта И 109 поступает уровень активиза- 25 тивизируется перед данным. ции с выхода триггера 50. Благодаря

этому триггер 97 устанавливается толь- Если блок 2 активизируется первым ко при условии активизации данного данном обмене, то на выход комму- блока 2. Демультиплексор 106 прдклю- татора 43 подключается линия активи- чает выход триггера 105 к линии 3.3 30 зации с последнего блока 2, участвую- синхронизации исполнителя магистра- щего в данном обмене, ли 3 (СХИ).Если в обмене участвует только

Сигнал синхронизации с выхода эле- один блок 2, то на выход коммутатора мента И 33 через элемент ШШ 40 и 43 подключается линия активизации с элемент 22 задержки устанавливает эс одновибратора 44 этого же блока 2. триггер 24, который выставляет актив- Сигнал активизации поступает в регистр ный логический уровень в линий 1.4 ма- 37 только того блока 2, который ак.ти- гистрали U Элемент 22 обеспечивает .. визируется первым в данном обмене, задержку, вьщачи сигнала СХИ на время. Этот сигнал через элемент ИЛИ 46 ус- необходимое для настройки схемы бло- 40 танавливает триггер 50. ка 2. Если блок 2 не является первым, то

После снятия сигнала СХЗ с линии триггер 50 устанавливается сигналом

1.3магистрали 1 триггер 24 сбрасы- активизации с выхода предьщущего бло- вается импульсом сброса с выхода од- ка 2„ Активный логический уровень на новибратора 26. Сигнал СХИ с линии 45 выходе триггера 50 разрешает прием

1.4магистрали 1 снимается сигнала СХЗ магистрали 3, прохожде- На селектор адресов поступает ад- ние импульсов стробирования на счет- рее регистра 37 данного блока 2. По чик 54 и поступает на вход CS шинно- сигналу СХЗ в регистр 37 записьюает- го формирователя 27, открьшая его, ся уставкао 50 Входные данные поступают байтами по

Уставка содержит:магистрали 3 на входы шинных форми1)код эстафеты передачи активное- рователей всех блоков 2 устройства, ти; По сигналу СХЗ входные данные записы2)код, определяющий число участ- ваются в регистр 34 активизированного вующих в обмене элементов 73 памя- ее блока 2, С выхода регистра 34 данные ти; подаются через мультиплексоры 70 на

3)код, определяющий, какие из входы элементов 73 памяти. Кроме то- элементов 73 памяти участвуют в об- го, по сигналу СХЗ устанавливается мене;триггер 97, которьй запускает цикл об

фащения к памяти, разрешая прохожде- 1ие тактовых импульсов с генератора 00 на счетчик 99

; Элемент 108 формирует следующие |г иг налы:

1)сигналы на входе 16о. .выбора строк и столбцов в зависимости от состояния счетчика 99;

2)сигнал на входе 16.3 записи- считывания в зависимости от состояния счетчика 99, режима работы и входа 4.5 {запись-чтение);

3)импульс на выходе 15.1 переключения счетчика 54 в зависимости от co стояния счетчика 99 и режима работы;

4)импульс на входе 16,1 строби- рования регистров 78 в зависимости от состояния счетчика 99;

5)сигнал на входе 16„4 управления буферными элементами 82 в зависимости от режима работы входа 4„5;

6)сигнал на входе 5„4 управления мультиплексором 68 в зависимости от состояния счётчика 99„

На выходе 85.1 дешифратора 84 устанавливается первьй сигнал записи, который поступает на входы всех мультиплексоров 86,

Элемент 88 устанавливаем мульти- |плексоры 86 (в зависимости от кода, определяющего, какие из восьми элемен JTOB 73 памяти участвуют в обмене) так что первьй сигнал записи поступает на вход элемента ИЛИ 71, выход которого связан с первым из учяствутощих в обмене элементов 73 памяти, второй сигнал записи (вьгход 85,2) поступает на вход элемента ИЛИ 71, выход которого связан с вторым участвующим в обме не элементом памяти и т„д.

Таким образом, первый поступивший байт входных данных записывается в первый участвующий в обмене элемент 73 памяти. По окончании цикла обращения к памяти переключается счетчик 54i на выходе 85„2 дешифратора 84 устанавливается второй сигнал записи,, По сигналу с выхода переноса счетчика 99 одновибратор 102 формирует им

пульс, который.сбрасывает триггер 97 и устанавливает триггер 105.

С выхода триггера 105 сигнал по- . ступает на вход демультиплексора 106,. которьй устанавливает в линии 3.3 магистрали 3 сигнал СХИ. После сня - тия с линии 3.2 магистрали 3 сигнала СХЗ одновибратор 94.формирует импульс сброса триггера 105, который сбрасы-

0

5

о

д

0

5

5

0

5

вается и снимает с линии 3.3 магистрали 3 сигнал СХИ.

При поступлении второго байта данных процесс повторяется. Данные записываются во второй участвующий в обмене элемент 73 памяти и т.д. При поступлении п-го байта данных (где п - число участвующих в обмене элементов памяти) данные записываются в последний .из участвующих в обмене элемент памяти, после чего на выходе элемента 55 сравнения устанавливается активньш логический уровень, который сбрасывает триггер 50, счетчик 54 и запускает формирователь 44 , При этом активизация блока 2 снимается. Формирователь 44 формирует имцульс активизации, который активизирует след тощий блок 2 устройства и переключает адресные счетчики 57 и 58 данного блока 2„

Во втором режиме работа блока 2 отличается тем, что сигнал управления записью элемента 108 не формируется. Кроме того, шинный формирователь 27 переключается на вьщачу. информации в магистраль 3

С выходов элементов памяти данные поступают на первые входы соответствующих элементов И 79, на вторые входы которых поступают сигналы разрешения записи с выходов элемен 1;ов 71 „

С выхода элемента ИЛИ 83 данные записываются в регистр 42 и через шинный формирователь подаются в магистраль 3,

Таким образом, вывод информации магистрали 3 происходит в такой же последовательности, что и ввод.

В третьем режиме в регистр 38 за- письшается код третьего режима. Элементы 71 коммутируются так, что пропускают сигнал управления записи независимо от состояния входа 17. Счетный вход счетчика 58 подключается к входу 5„3о

Мультиплексор 91 и демультиплексор 106 переключаются на прием и вьщачу сигналов синхронизации с магистрали 5 соответственно,

Б третьем режиме все блоки 2, участвующие в обмене, работают параллельно

В зависимости от состояния линии магистрали 5 происходит прием ин- формахщи с магистрали 4 или выдача информации в магистраль 4,

При выдаче информации элемент 108 открьшает буферные элементы 82„ Сигнал управления записью не формирует- ся„

При поступлении сигнала СХЗ магистрали 5 устанавливается триггер 97 к запускается цикл обращения к памяти. Информация из элементов памяти записывается в регистры.78 и через буфер- ные элементы поступает в магистраль 4. По окончании цикла обращения к памяти триггер 97 сбрасьшается и устанавливается триггер 105о На линии 5.6 магистрали 5 устанавливается сиг- нал СХИ. Сигнал СХЗ с линии 5,3 магистрали 5 снимается, сбрасьтается триггер 105, снимается сигнал СХИ. Далее процесс повторяется. Счетчик 58 переключается при снятии сигнала СХИ.

По окончании выдачи первого фрагмента данных в счетчик записывается начальный адрес следующего фрагмента и т

При приеме информации элемент 108 переводит элементы 82 в третье состояние, сигнал управления записью формируется Информация поступает на входы элементов 73 памяти. В остальном работа схемы не отличается от работы при вьщаче информации. в При отсутствии сигнала синхронизации СХЗ устанавливается триггер 113. Сигнал с выхода триггера 113 постзша- ет на вход элемента 108 постоянной памяти,.запрещая формирование сигналов управления памятью CAS и WE.

Сигнал с выхода триггера 113 поступает также на вход параллельной записи счетчика 112, разрешая счет.

При поступлении сигнала СХЗ тригг гер 113 сбрасывается.

Формула, изобретения

Устройство ввода-вывода матричной вычислительной системы, содержащее m блоков ввода-вывода, где m - число строк обрабатьюающей матрицы матричной вычислительной системы, причем первые управляющие входы-выходы, первые информационные входы-выходы, вторые управляющие входы-выходы с первого по т-ц блоков ввода-вывода сое,динены между собой соответственно че рез первую управляющую, информационную и вторую управляющую магистрали устройства, второй информационный

,

т- , - . j-

25

40

45

50

55

вход-выход Ь-го блока ввода-вьшода подключен к Ь-му информационному входу-выходу, группы устройства (где Ь 1,...,т), при этом каждый блок ввода-вывода содержит узел связи, уэел,. синхронизации, узел буферной памяту, счетный узел, причем в каждом блоке ввода-вьтода первый информационный вход-выход блока ввода-вывода подключен к первому информационному входу-выходу узла связи и к первому управляющему входу-выходу узла синхронизации, первьй управляющий вход-вы- koд блока ввода-вьтода соединен с управляющим входом-выходом узла связи, второй информаиконный вход-выход блока ввода-вывода подключен к ин-- формационному входу-выходу узла буферной памяти, второй управляющий вход-выход блока ввода-вьгаода подключен к счетному входу счетного узла и к второму управляющему входу-выходу узла синхронизации, выходы узла синхронизации и счетного узла подключены соответственно к первому управлякмцему входу и к адресному входу узла буферной памяти, второй информационный вход-выход узла связи подключен к третьему управляющему входу-выходу узла синхронизации, к второму управляющему входу узла буферной памяти и к первому управляющему входу счетного узла, отличающееся тем, что, с целью повышения надежности устройства за счет его перестраиваемости, третьи управляющие входы-выходы блоков ввода-вьшода с первого по т-й соединены между собой через третью управляющую магистраль, при этом каждый блок ввода-вывода содержит узел активизации и узел распределения данных, причем в каждом блоке ввода-вывода третий управляющий вход-выход блока ввода-вывода подключен к управляющему входу-выходу узла актонизации и к второму управляющему входу счетного узла, третий управляющий вход-выход узла синхронизации подключен к первому управляющему входу узла распре- ;деления данных, выходы с первого по восьмой которого подключены соответственно к информационным входам с первого по восьмой узла буферной памяти, первый выход узла активизации подключен к второму управляющему входу узла распределения данных, информационный вход, первый и второй

.

управляющие входы узла активизации подключены соответственно к первому, BJTopoMy и третьему входам узла связи, третий управляющий вход узла активизации подключен к выходу узла синх рониэации, второй выход узла активи- S ации подключен к управляющим входам узла связи и узла синхронизации, при этом узел активизации содержит триггер, счетчик,элемент сравнения, коммутатор, формирователь импульса, ;,ва элемента ИЛИ и элемент И, при- :ем первый, второй и третий управ- ; яющие входа узла активизации подкпю- метл соответственно к первым входам первого элемента ШШ, второго эле- }1ента ИЛИ и-элемента И, информацион- :1ый вход узла активизации подключен :с первому информационному входу ком- нутатора и к первому входу элемента :равнения, выход коммутатора подключен к второму входу первого элемента ИЛИ, выход которого подключен к информационному входу триггера, выход счетчика подключен к первому выходу узла активизации и к второму входу элемента сравнения, выход которого подключен к второму входу второго эле |мента ИЛИ и к входу формирователя им- Iпульса, выход которого подключен к второму информационному входу коммутатора и к управляющему входу-выходу I узла активизации, выход второго эле- I мента ИЛИ подключен к входу установки I в О счетчика к к входу установки в О триггера, выход к- - орого подклю- чен к второму выходу узла активизации : и к второму входу элемента И, выход которого подключен к счетному входу

11

5

10

15

20

-30

35

счетчика, при этом узел распределения данных содержит дешифратор, элемент постоянной памяти и восемь мультиплексоров, причем первый и второй управляющие входы узла распределения данных подключены соответственно к адресному входу элемента постоянной памяти и к входу дешифратора, первьй выход дешифратора подключен к первым инфор- мационньт входам мультиплексоров с первого по седьмой и к информационному входу восьмого мультиплексора, второй выход дешифратора подключен к вторым информационным входам мультиплексоров с первого по седьмой, третий выход дешифратора подключен к третьим информационным входам мультиплексоров с первого по шестой, четвертый выход девшфратора подключен к четвертым информационным входам мультиплексоров с первого по пятьм, пятый выход дешифратора подключен к пятым информационным входам мультиплексоров с первого по четвертый, шестой выход дешифратора подключен к шестым информационным входам мультиплексоров с первого по третий, седьмой выход дешифратора подключен к седьмым информационным входам первого и второго мультиплексоров, восьмой выход дешифратора подключен к восьмому информацион ному входу первого мультиплексора . выход элемента постоянной памяти подключен к управляющим входам мультиплексоров с первого по восьмой, выходы которых подключены соответственно к выходам с первого по восьмой узла распределения данных

V5

Vf.

V5

W.

/V.f

52

5J.

5V

Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для обработки данных | 1987 |

|

SU1536396A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| Устройство для сопряжения многоблочной памяти с процессором и вводно-выводными устройствами | 1984 |

|

SU1280645A1 |

| Устройство для сопряжения вычислительных машин с магистралью | 1988 |

|

SU1647576A1 |

| Устройство для сопряжения двух магистралей | 1984 |

|

SU1241249A1 |

| Устройство для сопряжения ЭВМ с магистралью внешних устройств | 1985 |

|

SU1408440A1 |

| Устройство для формирования сигнала идентификации начала команды ЭВМ | 1985 |

|

SU1352493A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для отладки программ | 1984 |

|

SU1223236A1 |

Изобретение относится к вычислительной технике, в частности к устройствам обработки информации на базе матричных процессов. Цель изобретения - повышение надежности устройства за счет его перестраиваемости. Цель достигается за счет того, что устройство содержит M блоков 2 ввода-вывода, где M - число строк обрабатывающей матрицы матричной вычислительной системы, каждый из которых содержит узел 7 буферной памяти, узел 8 распределения данных, счетный узел 9, узел 10 связи, узел 11 активизации, узел 12 синхронизации. 7 ил.

1Ч.1

ш.

VV

У7

49

55

W

fe,5

Фиг.Ч

| Специализированные сверхбыстро- действукяцие ЭВМ для обработки изображений | |||

| - Вычислительная техника, 1982, № 47, с | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

Авторы

Даты

1989-12-15—Публикация

1987-11-19—Подача